Ulrich Uwer LHCb Electronics Workshop University of Heidelberg

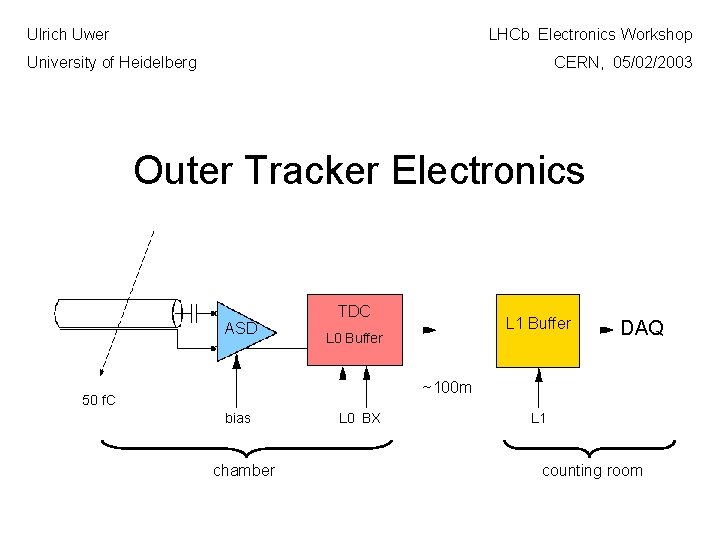

Ulrich Uwer LHCb Electronics Workshop University of Heidelberg CERN, 05/02/2003 Outer Tracker Electronics ASD TDC L 1 Buffer L 0 Buffer DAQ ~100 m 50 f. C bias chamber L 0 BX L 1 counting room

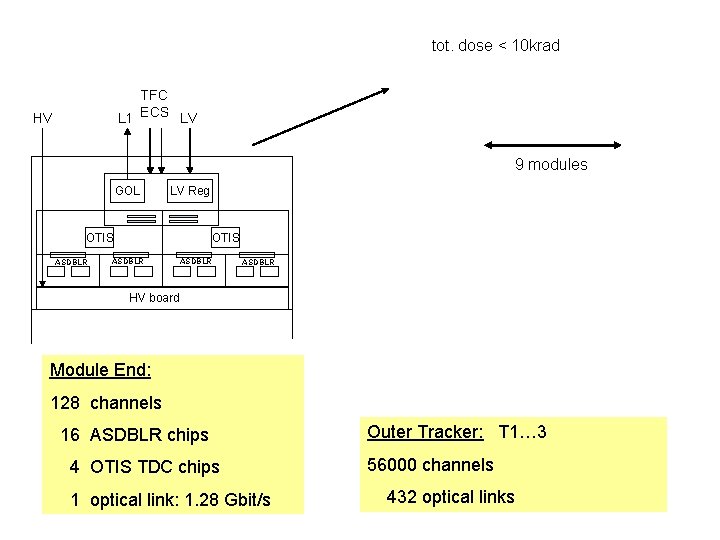

tot. dose < 10 krad TFC L 1 ECS LV HV 9 modules GOL LV Reg OTIS ASDBLR HV board Module End: 128 channels 16 ASDBLR chips 4 OTIS TDC chips 1 optical link: 1. 28 Gbit/s Outer Tracker: T 1… 3 56000 channels 432 optical links

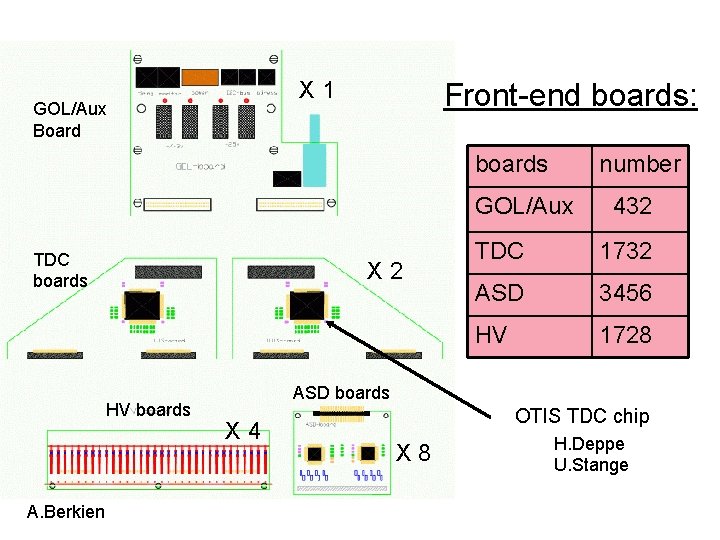

X 1 GOL/Aux Board Front-end boards: boards number GOL/Aux TDC boards X 2 HV boards A. Berkien 432 TDC 1732 ASD 3456 HV 1728 ASD boards X 4 OTIS TDC chip X 8 H. Deppe U. Stange

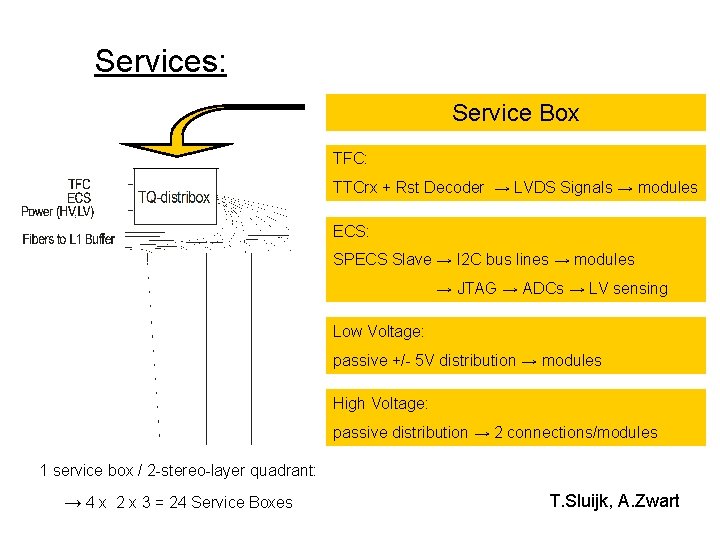

Services: Service Box TFC: TTCrx + Rst Decoder → LVDS Signals → modules ECS: SPECS Slave → I 2 C bus lines → modules → JTAG → ADCs → LV sensing Low Voltage: passive +/- 5 V distribution → modules High Voltage: passive distribution → 2 connections/modules 1 service box / 2 -stereo-layer quadrant: → 4 x 2 x 3 = 24 Service Boxes T. Sluijk, A. Zwart

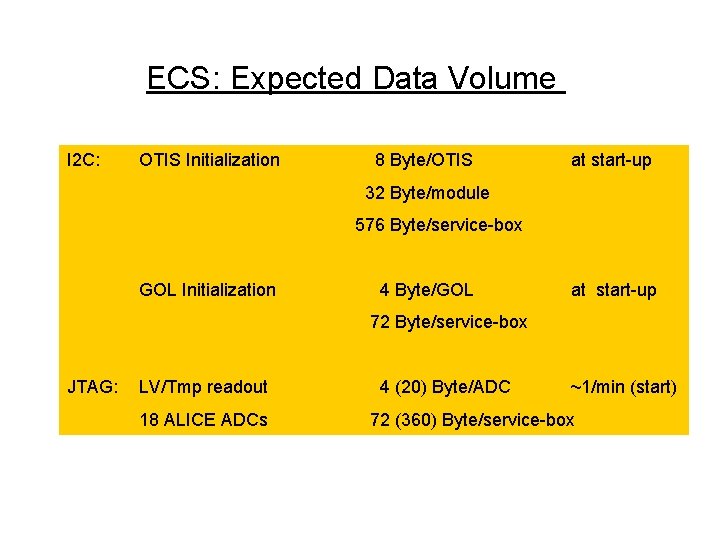

ECS: Expected Data Volume I 2 C: OTIS Initialization 8 Byte/OTIS at start-up 32 Byte/module 576 Byte/service-box GOL Initialization 4 Byte/GOL at start-up 72 Byte/service-box JTAG: LV/Tmp readout 18 ALICE ADCs 4 (20) Byte/ADC ~1/min (start) 72 (360) Byte/service-box

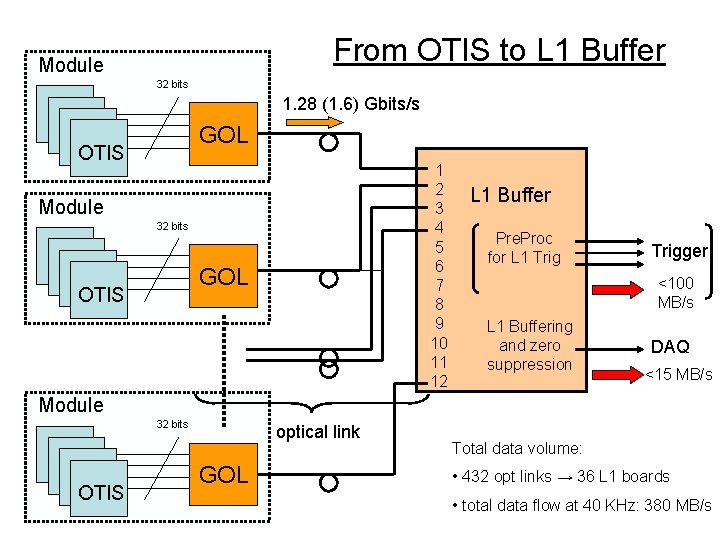

From OTIS to L 1 Buffer Module 32 bits 1. 28 (1. 6) Gbits/s GOL OTIS 1 2 3 4 5 6 7 8 9 10 11 12 Module 32 bits GOL OTIS L 1 Buffer Pre. Proc for L 1 Trigger <100 MB/s L 1 Buffering and zero suppression DAQ <15 MB/s Module 32 bits OTIS optical link GOL Total data volume: • 432 opt links → 36 L 1 boards • total data flow at 40 KHz: 380 MB/s

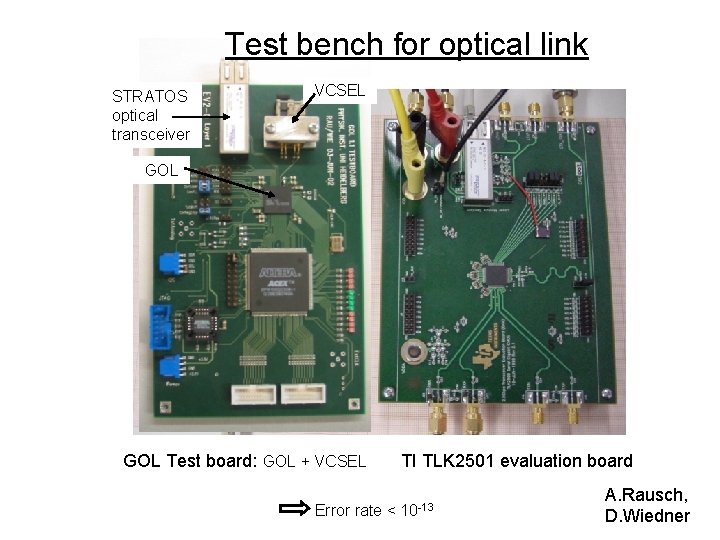

Test bench for optical link STRATOS optical transceiver VCSEL GOL Test board: GOL + VCSEL TI TLK 2501 evaluation board Error rate < 10 -13 A. Rausch, D. Wiedner

L 1 Buffer Board: t c je Outer Tracker on m C om o r p T O , T I , o l e V G. Haefeli et al.

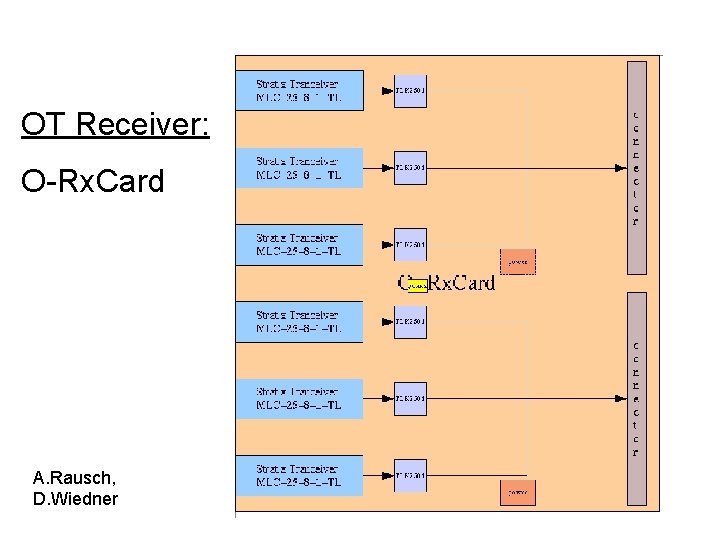

OT Receiver: O-Rx. Card A. Rausch, D. Wiedner

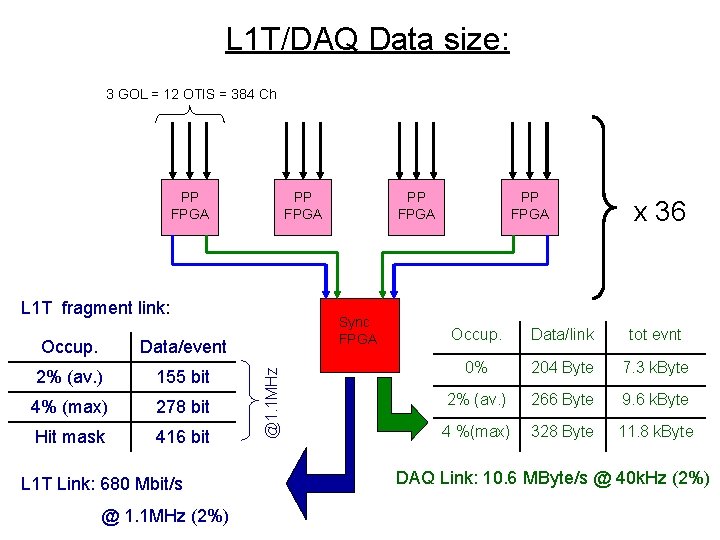

L 1 T/DAQ Data size: 3 GOL = 12 OTIS = 384 Ch PP FPGA L 1 T fragment link: Data/event 2% (av. ) 155 bit 4% (max) 278 bit Hit mask 416 bit L 1 T Link: 680 Mbit/s @ 1. 1 MHz (2%) Sync FPGA @1. 1 MHz Occup. PP FPGA x 36 Occup. Data/link tot evnt 0% 204 Byte 7. 3 k. Byte 2% (av. ) 266 Byte 9. 6 k. Byte 4 %(max) 328 Byte 11. 8 k. Byte DAQ Link: 10. 6 MByte/s @ 40 k. Hz (2%)

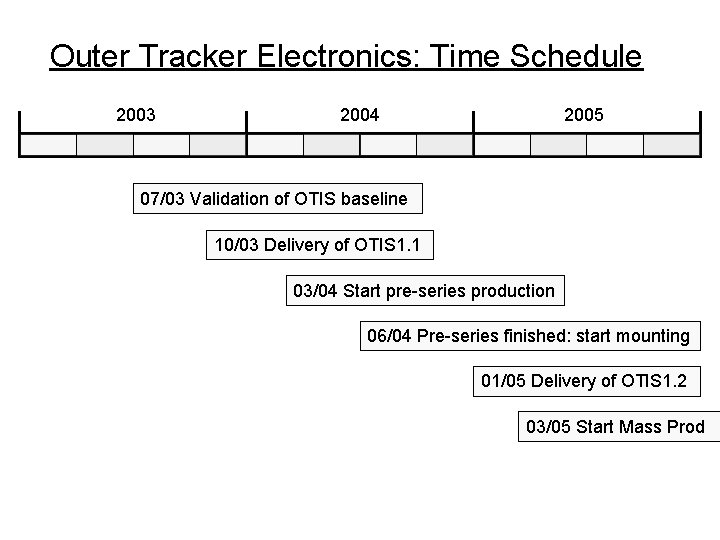

Outer Tracker Electronics: Time Schedule 2003 2004 2005 07/03 Validation of OTIS baseline 10/03 Delivery of OTIS 1. 1 03/04 Start pre-series production 06/04 Pre-series finished: start mounting 01/05 Delivery of OTIS 1. 2 03/05 Start Mass Prod

- Slides: 11