U Uwer Electronics Review April 22 2004 FE

- Slides: 15

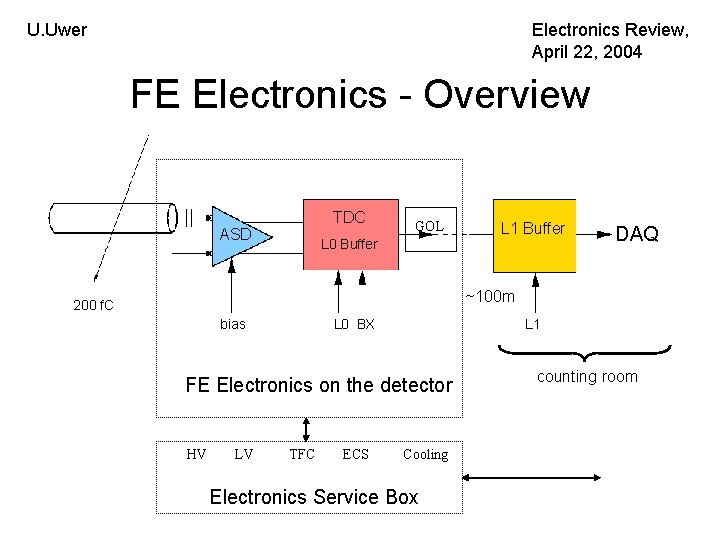

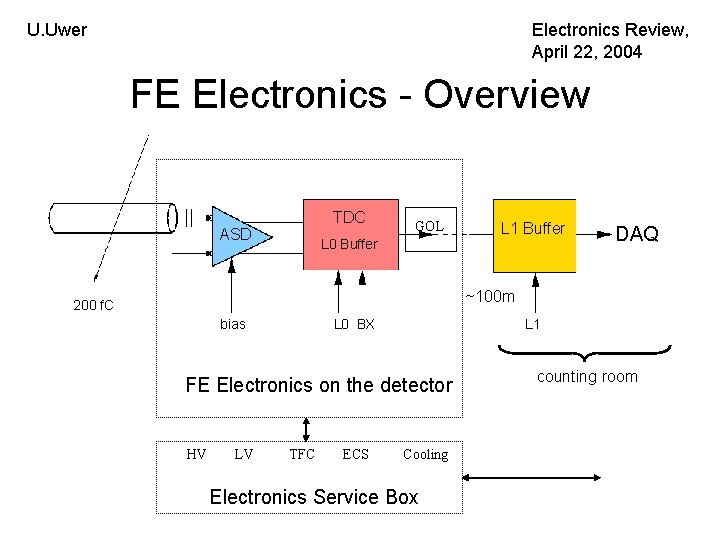

U. Uwer Electronics Review, April 22, 2004 FE Electronics - Overview TDC ASD GOL L 0 Buffer L 1 Buffer DAQ ~100 m 200 f. C bias L 0 BX L 1 FE Electronics on the detector HV LV TFC ECS Cooling Electronics Service Box counting room

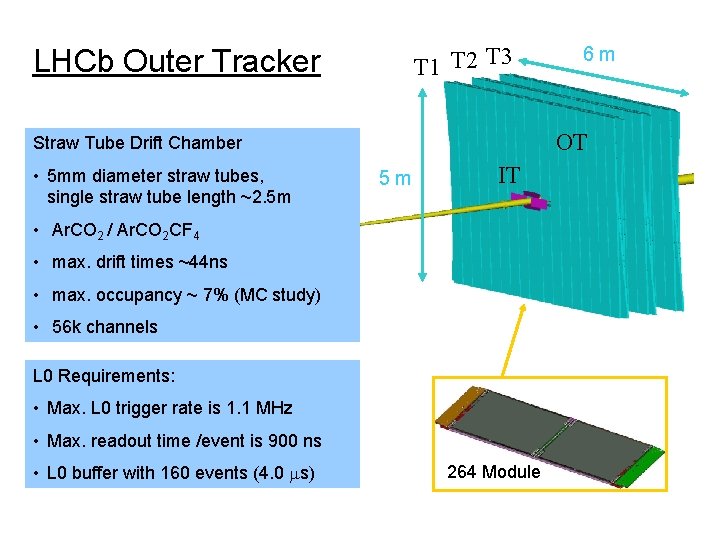

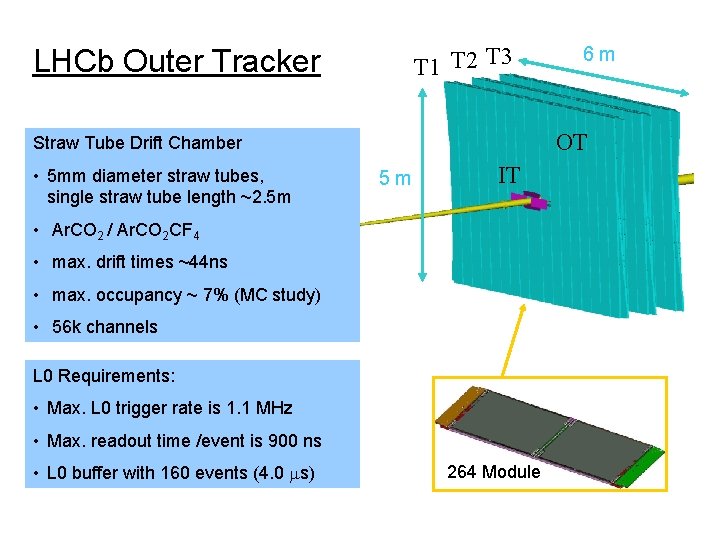

T 1 T 2 T 3 LHCb Outer Tracker OT Straw Tube Drift Chamber • 5 mm diameter straw tubes, single straw tube length ~2. 5 m 5 m IT • Ar. CO 2 / Ar. CO 2 CF 4 • max. drift times ~44 ns 6 m TT • max. occupancy ~ 7% (MC study) • 56 k channels L 0 Requirements: • Max. L 0 trigger rate is 1. 1 MHz • Max. readout time /event is 900 ns • L 0 buffer with 160 events (4. 0 s) 264 Module

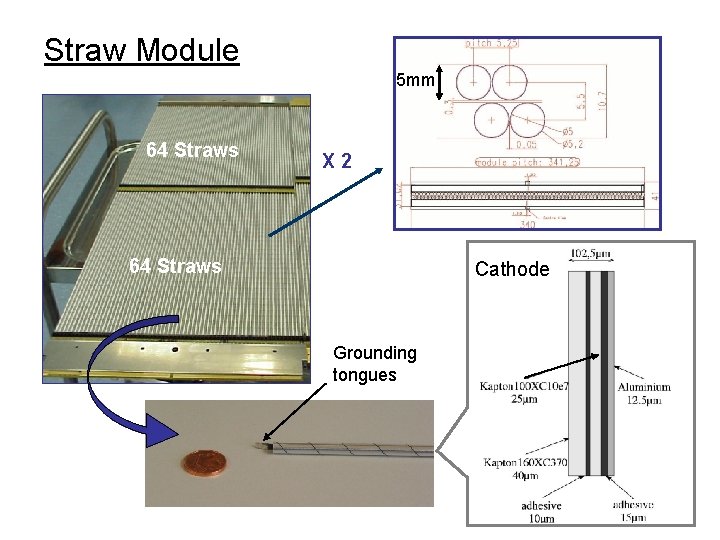

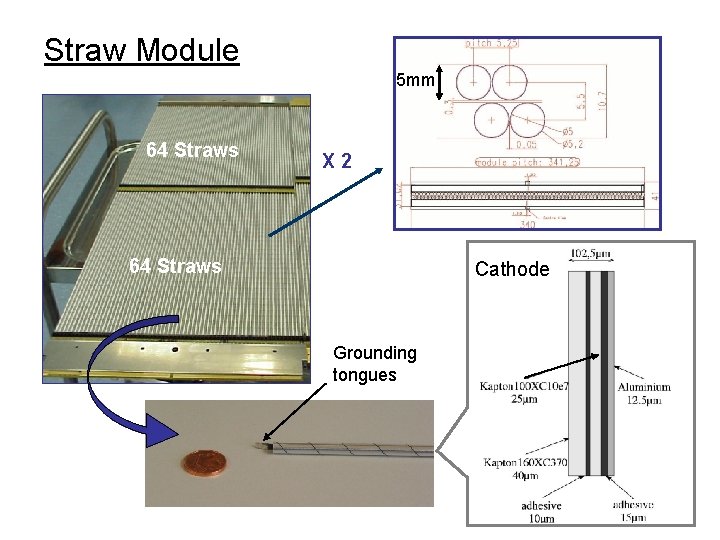

Straw Module 5 mm 64 Straws X 2 64 Straws Cathode Grounding tongues

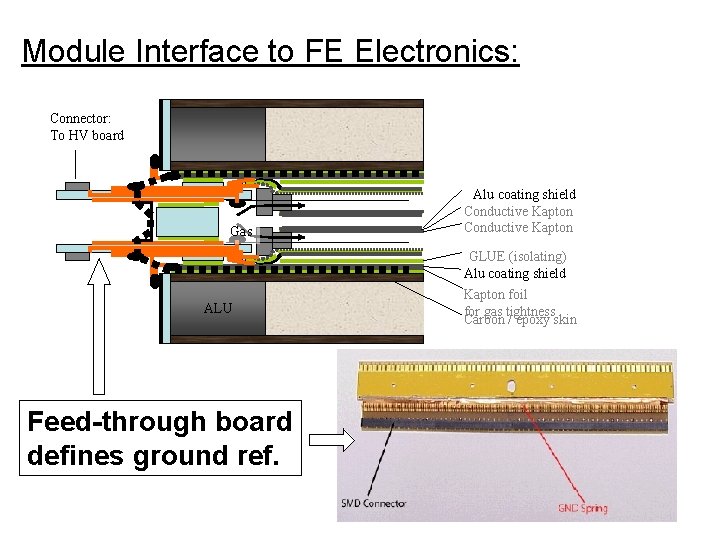

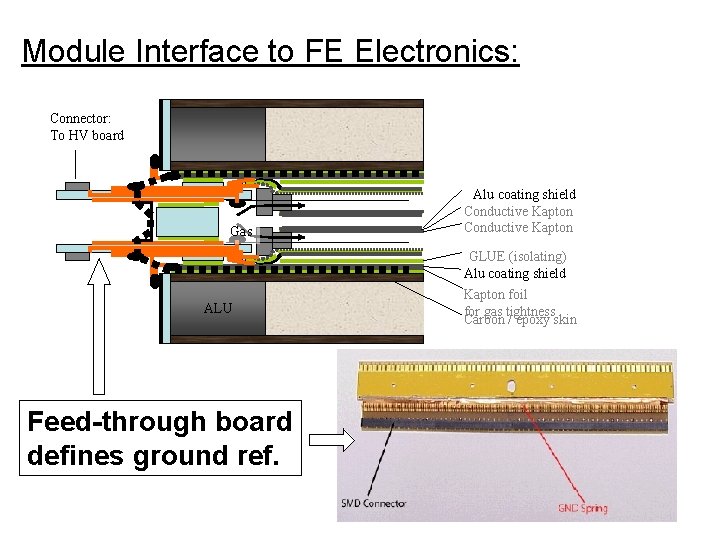

Module Interface to FE Electronics: Connector: To HV board Gas ALU Feed-through board defines ground ref. Alu coating shield Conductive Kapton GLUE (isolating) Alu coating shield Kapton foil for gas tightness Carbon / epoxy skin

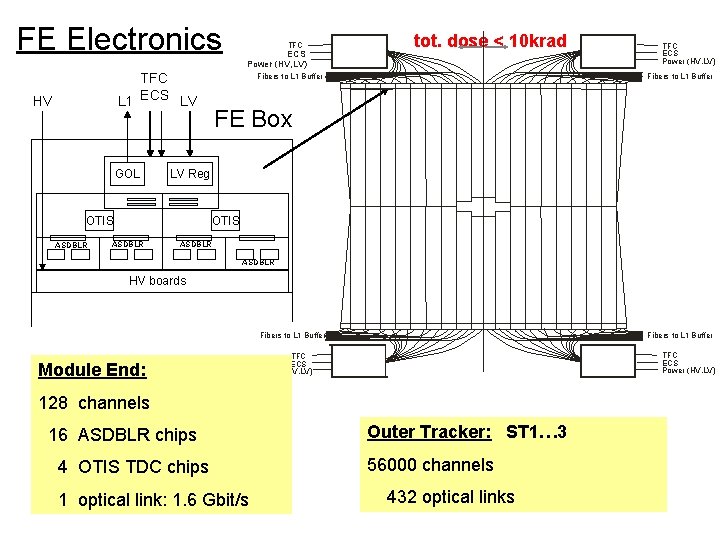

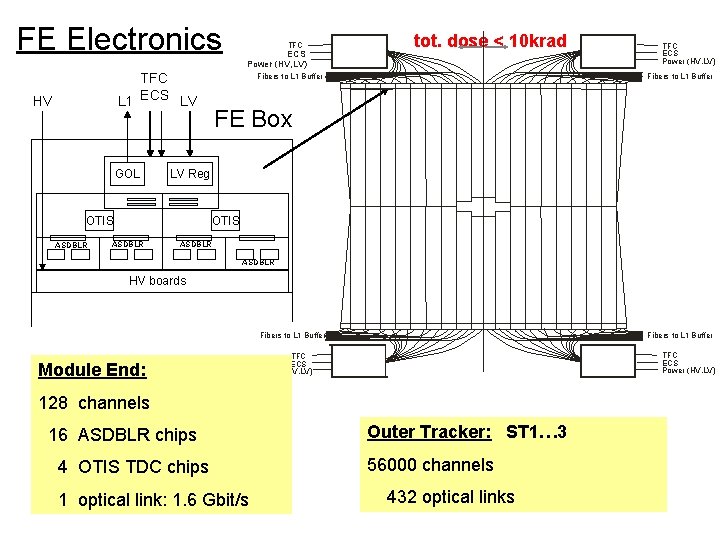

FE Electronics TFC L 1 ECS LV HV GOL tot. dose < 10 krad Fibers to L 1 Buffer TFC ECS Power (HV, LV) Fibers to L 1 Buffer FE Box LV Reg OTIS ASDBLR TFC ECS Power (HV, LV) OTIS ASDBLR HV boards Fibers to L 1 Buffer Module End: Fibers to L 1 Buffer TFC ECS Power (HV, LV) 128 channels 16 ASDBLR chips 4 OTIS TDC chips 1 optical link: 1. 6 Gbit/s Outer Tracker: ST 1… 3 56000 channels 432 optical links

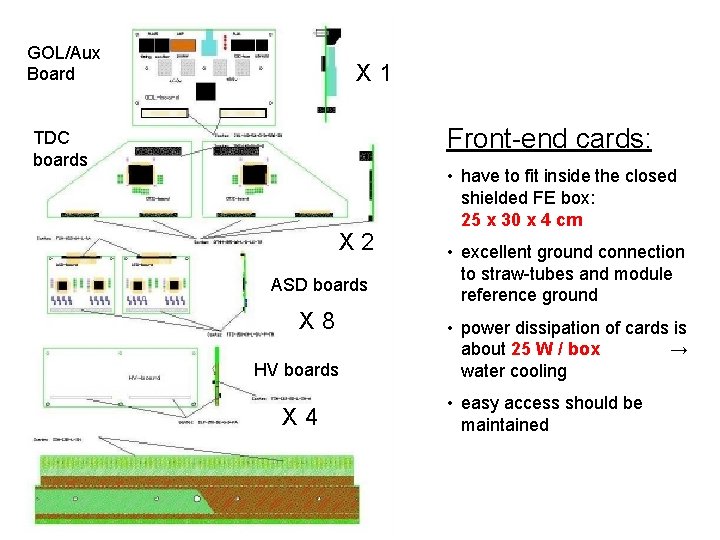

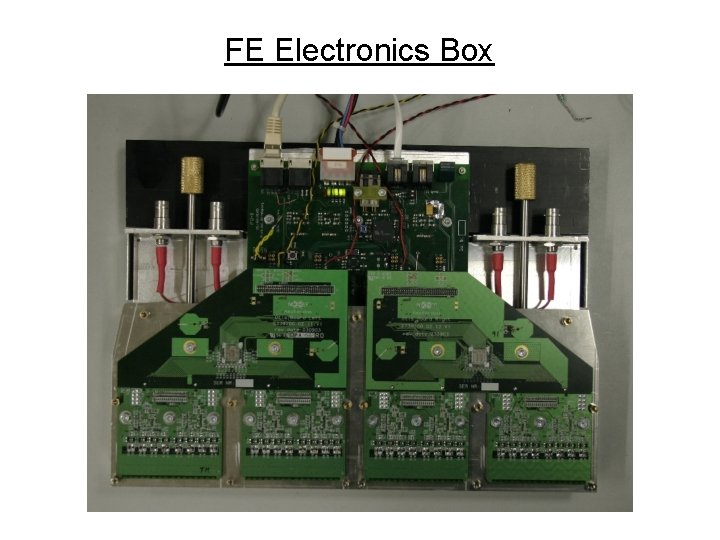

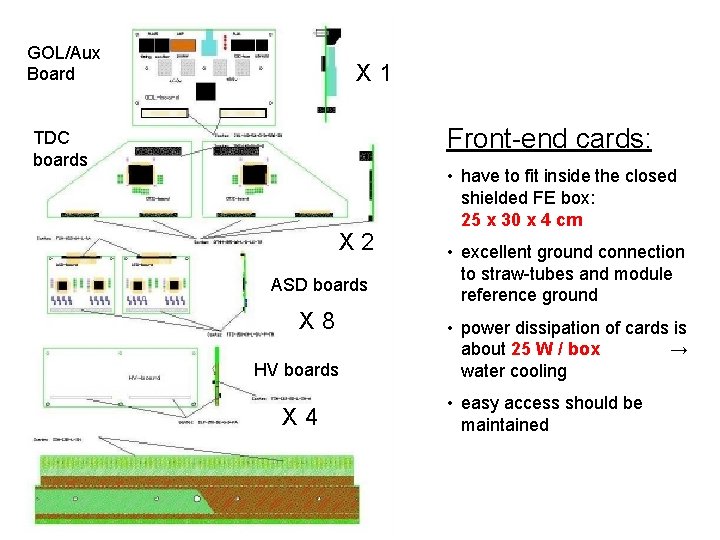

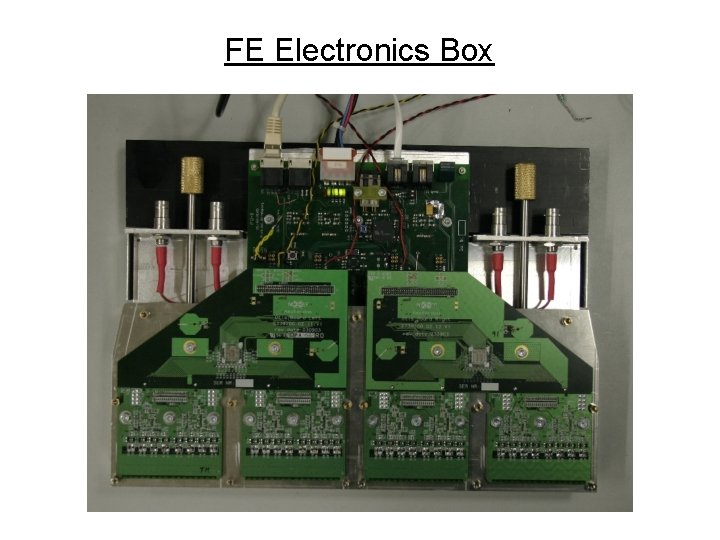

GOL/Aux Board X 1 Front-end cards: TDC boards X 2 ASD boards X 8 HV boards X 4 • have to fit inside the closed shielded FE box: 25 x 30 x 4 cm • excellent ground connection to straw-tubes and module reference ground • power dissipation of cards is about 25 W / box → water cooling • easy access should be maintained

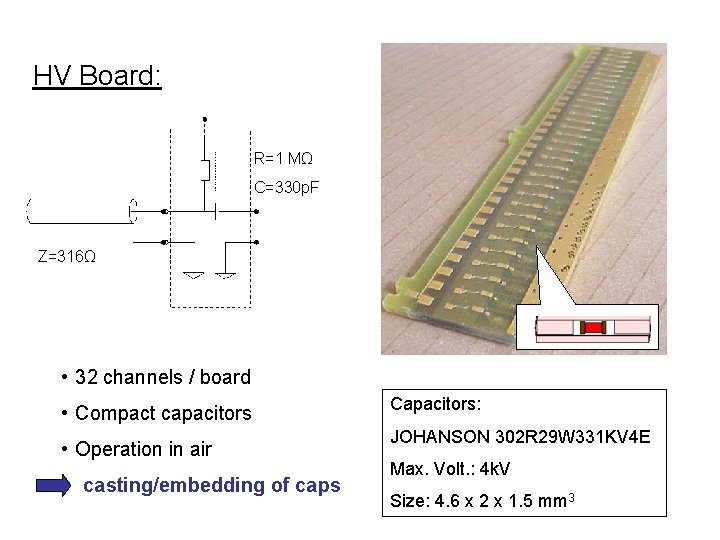

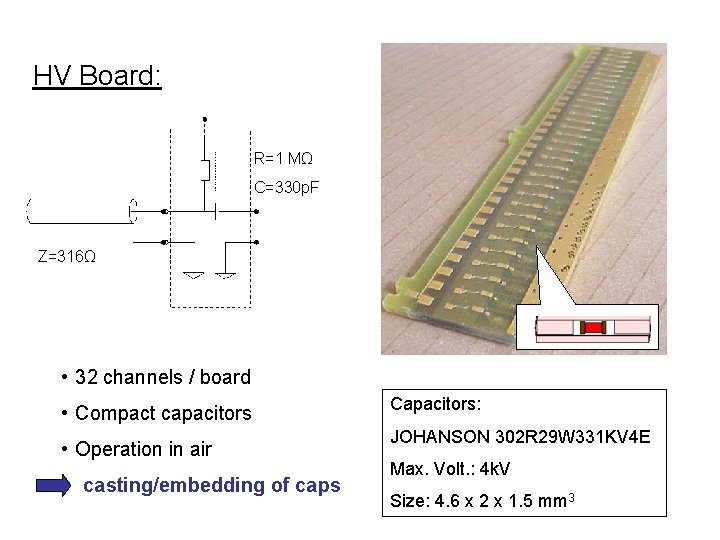

HV Board: R=1 MΩ C=330 p. F Z=316Ω • 32 channels / board • Compact capacitors • Operation in air casting/embedding of caps Capacitors: JOHANSON 302 R 29 W 331 KV 4 E Max. Volt. : 4 k. V Size: 4. 6 x 2 x 1. 5 mm 3

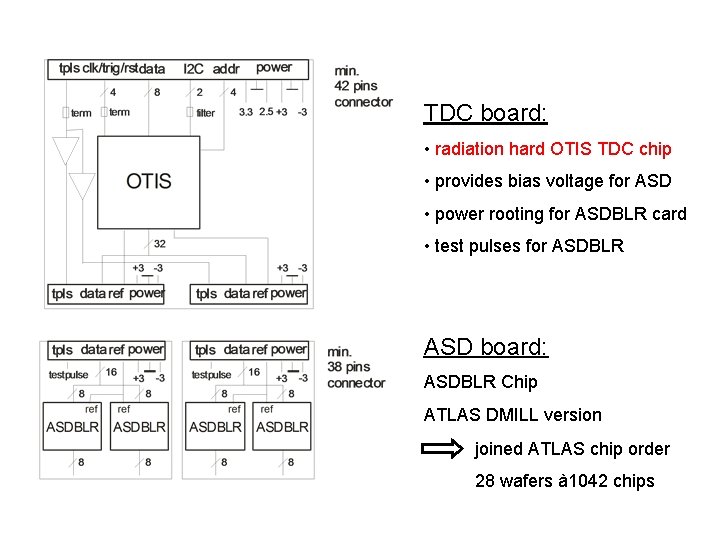

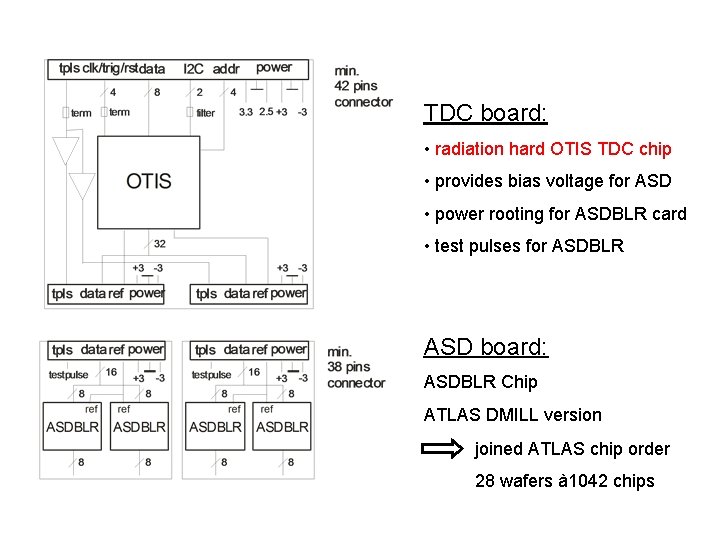

TDC board: • radiation hard OTIS TDC chip • provides bias voltage for ASD • power rooting for ASDBLR card • test pulses for ASDBLR ASD board: ASDBLR Chip ATLAS DMILL version joined ATLAS chip order 28 wafers à 1042 chips

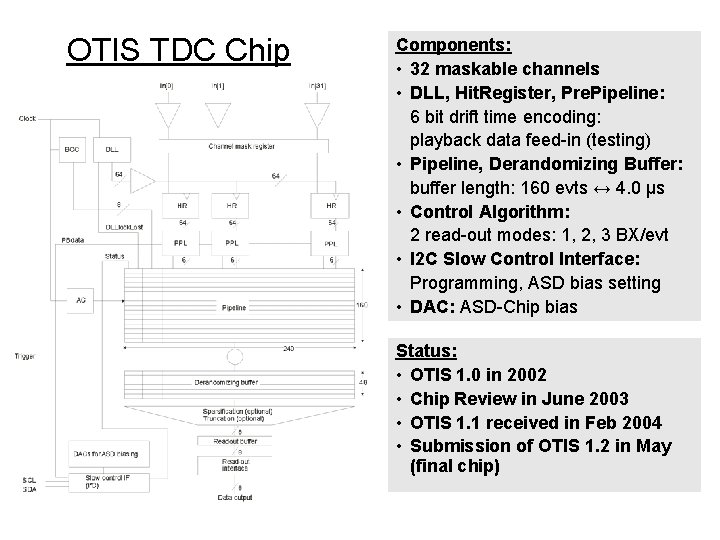

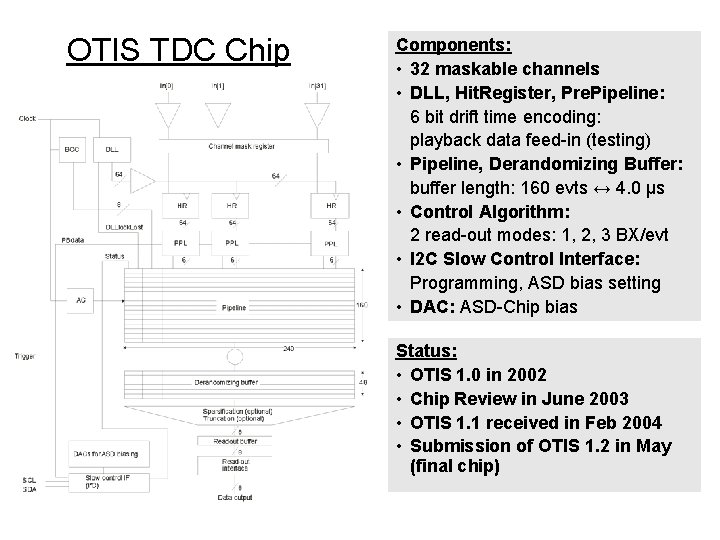

OTIS TDC Chip Components: • 32 maskable channels • DLL, Hit. Register, Pre. Pipeline: 6 bit drift time encoding: playback data feed-in (testing) • Pipeline, Derandomizing Buffer: buffer length: 160 evts ↔ 4. 0 μs • Control Algorithm: 2 read-out modes: 1, 2, 3 BX/evt • I 2 C Slow Control Interface: Programming, ASD bias setting • DAC: ASD-Chip bias Status: • OTIS 1. 0 in 2002 • Chip Review in June 2003 • OTIS 1. 1 received in Feb 2004 • Submission of OTIS 1. 2 in May (final chip)

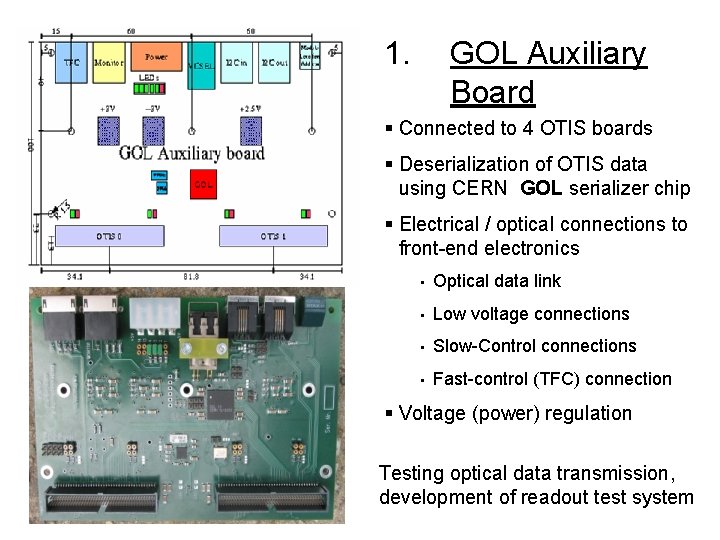

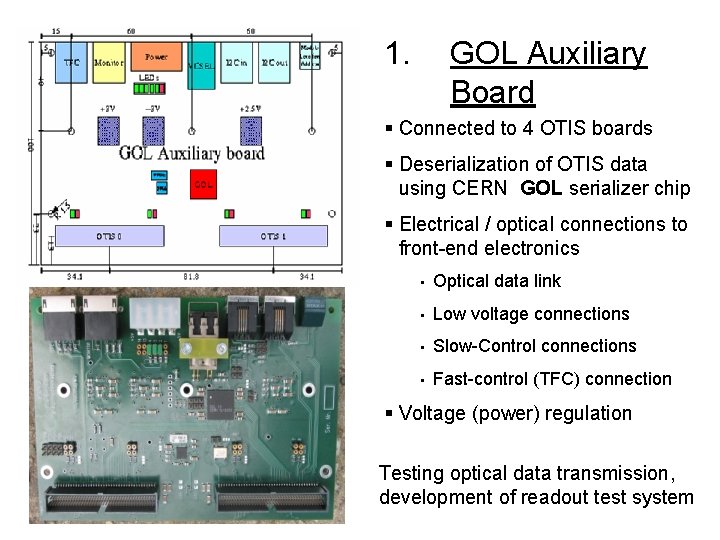

1. GOL Auxiliary Board § Connected to 4 OTIS boards § Deserialization of OTIS data using CERN GOL serializer chip § Electrical / optical connections to front-end electronics • Optical data link • Low voltage connections • Slow-Control connections • Fast-control (TFC) connection § Voltage (power) regulation Testing optical data transmission, development of readout test system

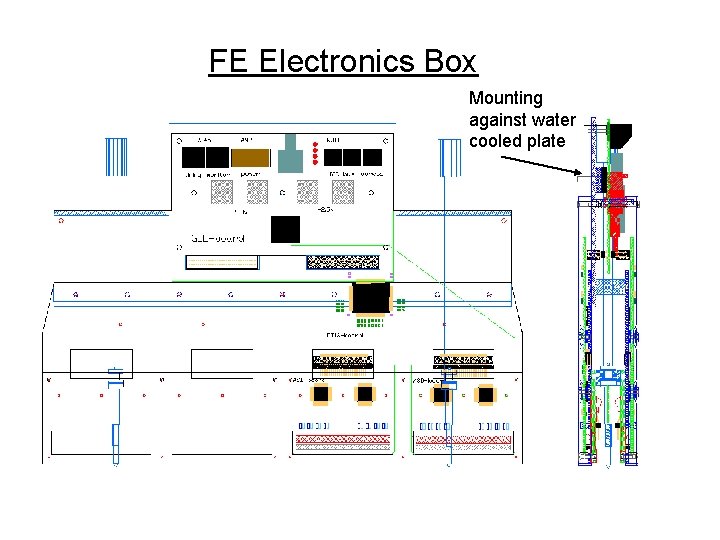

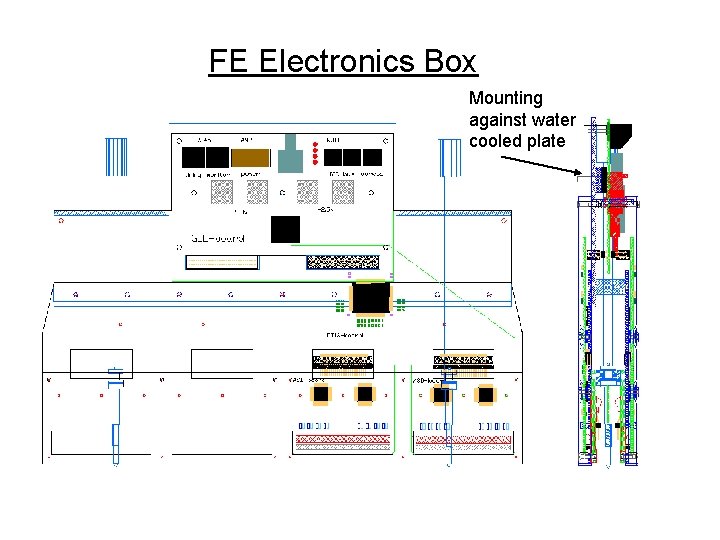

FE Electronics Box Mounting against water cooled plate

FE Electronics Box

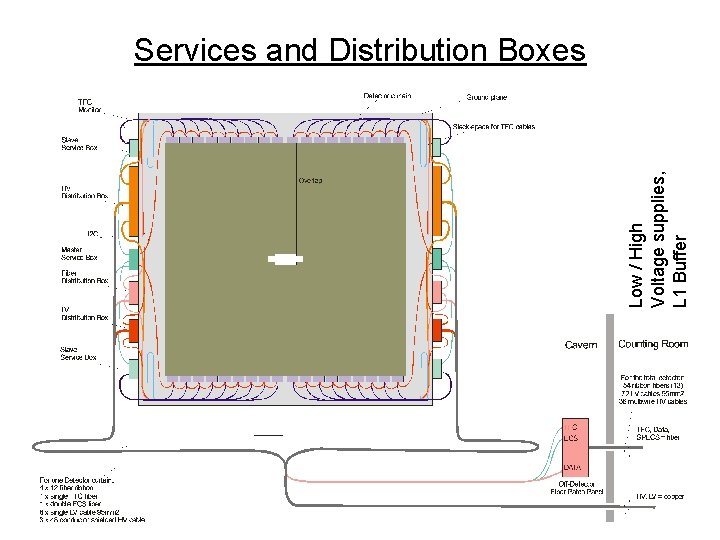

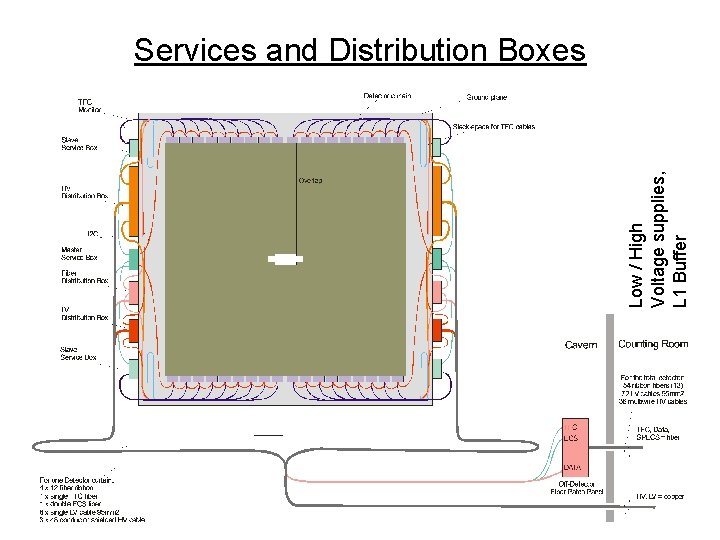

Low / High Voltage supplies, L 1 Buffer Services and Distribution Boxes

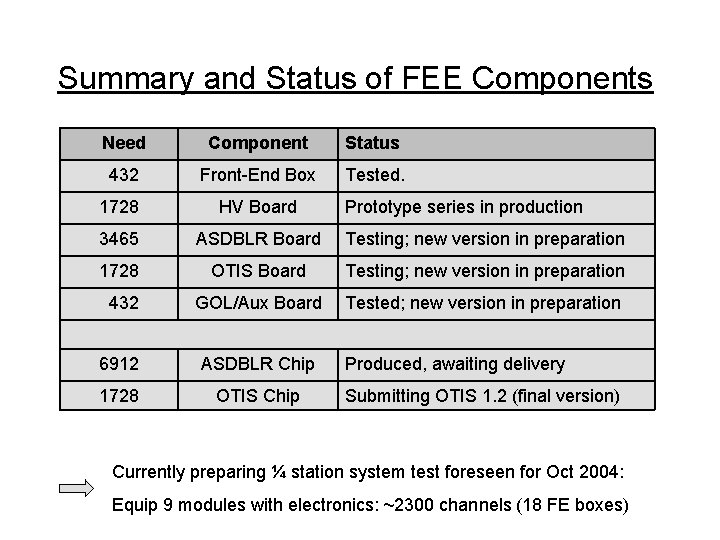

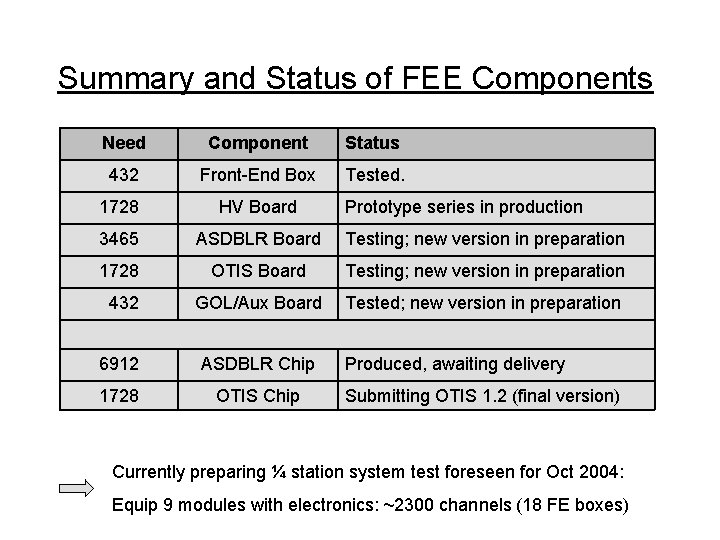

Summary and Status of FEE Components Need Component Status 432 Front-End Box Tested. 1728 HV Board 3465 ASDBLR Board Testing; new version in preparation 1728 OTIS Board Testing; new version in preparation 432 GOL/Aux Board Tested; new version in preparation 6912 ASDBLR Chip 1728 OTIS Chip Prototype series in production Produced, awaiting delivery Submitting OTIS 1. 2 (final version) Currently preparing ¼ station system test foreseen for Oct 2004: Equip 9 modules with electronics: ~2300 channels (18 FE boxes)

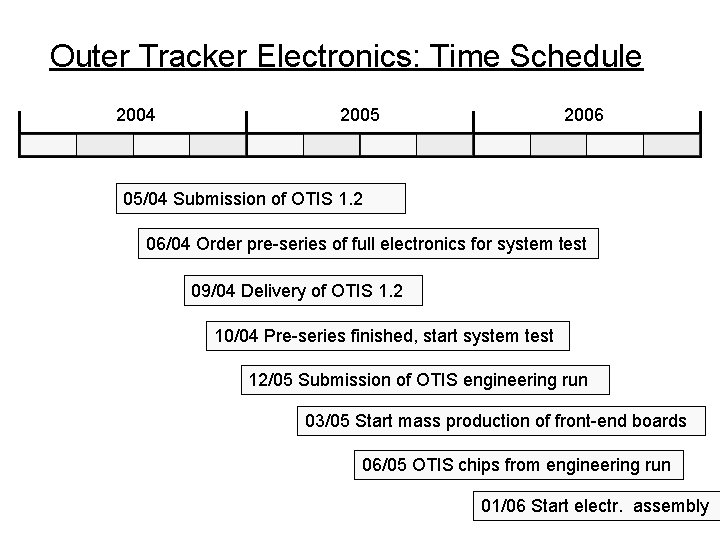

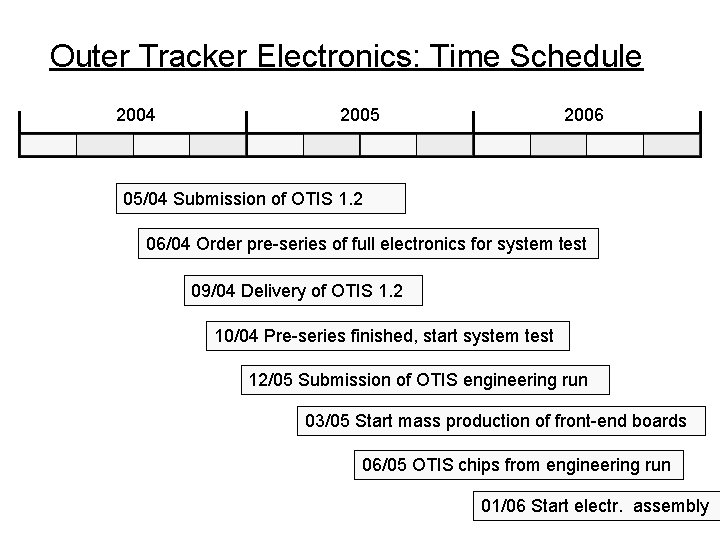

Outer Tracker Electronics: Time Schedule 2004 2005 2006 05/04 Submission of OTIS 1. 2 06/04 Order pre-series of full electronics for system test 09/04 Delivery of OTIS 1. 2 10/04 Pre-series finished, start system test 12/05 Submission of OTIS engineering run 03/05 Start mass production of front-end boards 06/05 OTIS chips from engineering run 01/06 Start electr. assembly