u Cache A UtilityAware Multilevel SSD Cache Management

- Slides: 25

u. Cache: A Utility-Aware Multilevel SSD Cache Management Policy 2013 IEEE International Conference on High Performance Computing and Communications

Outline • Introduction • Motivation • System Design • Evaluation • Conclusion

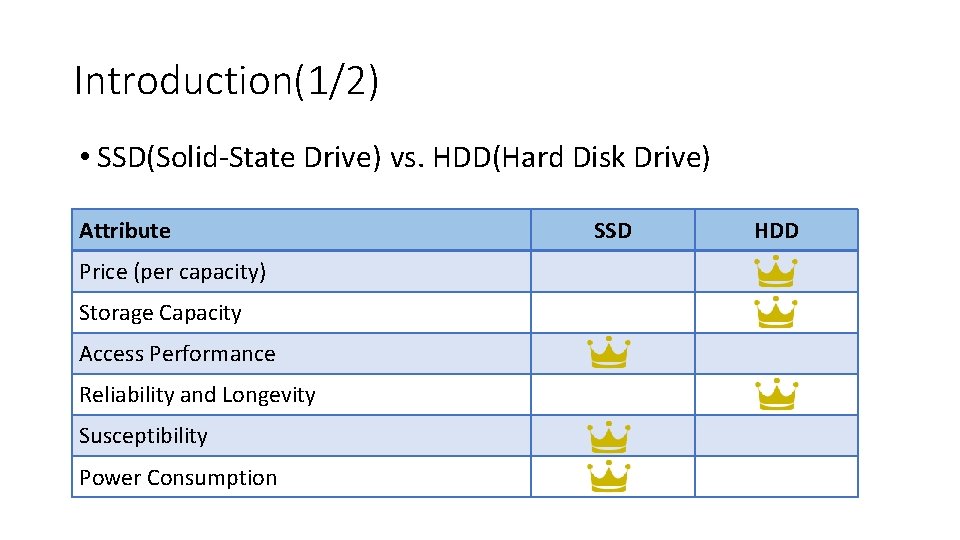

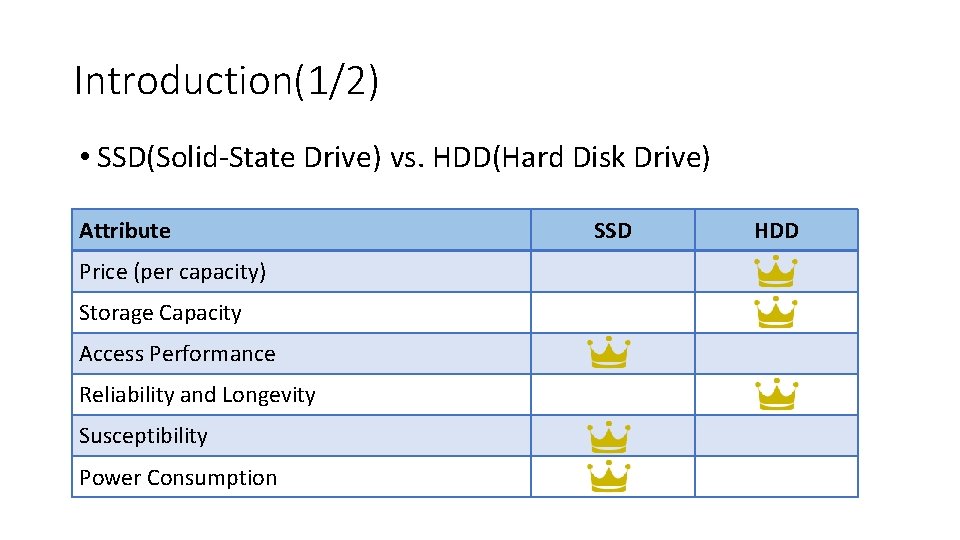

Introduction(1/2) • SSD(Solid-State Drive) vs. HDD(Hard Disk Drive) Attribute Price (per capacity) Storage Capacity Access Performance Reliability and Longevity Susceptibility Power Consumption SSD HDD

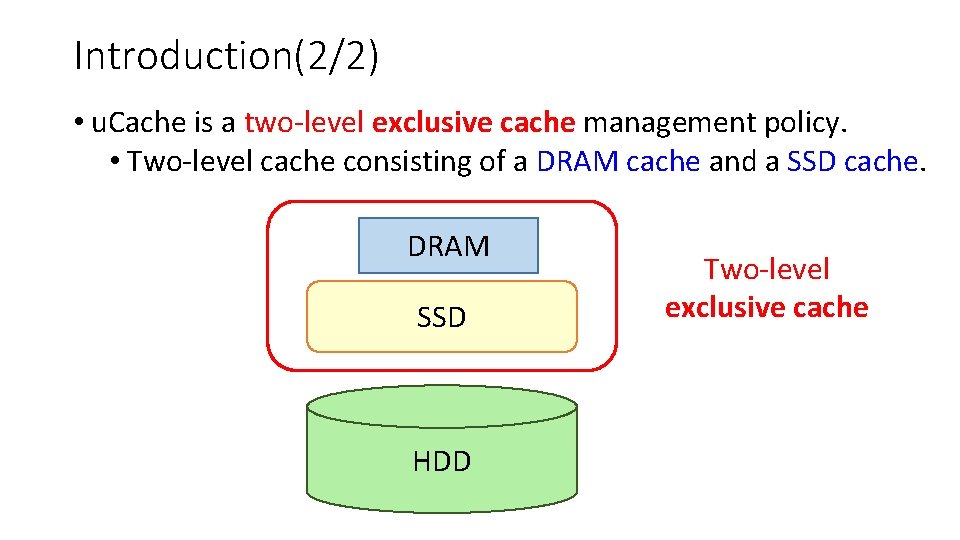

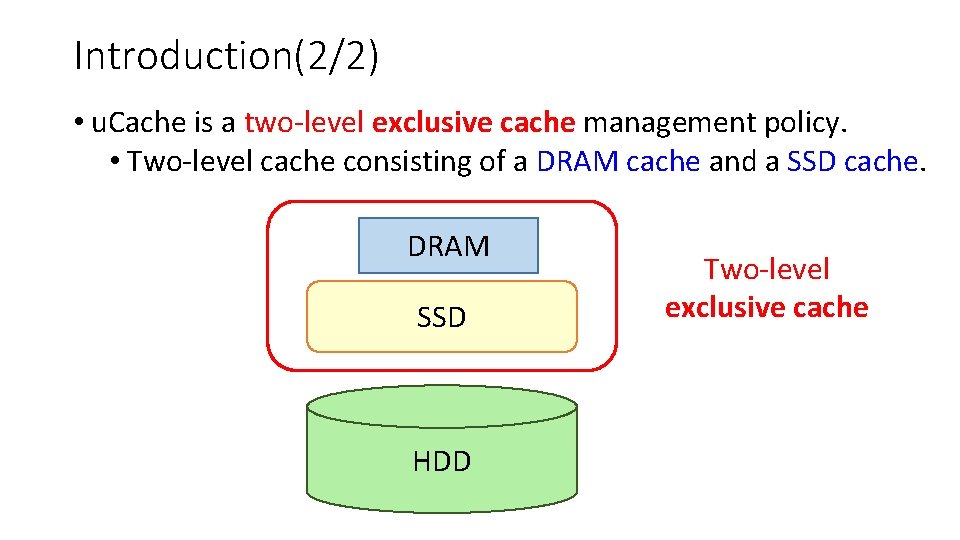

Introduction(2/2) • u. Cache is a two-level exclusive cache management policy. • Two-level cache consisting of a DRAM cache and a SSD cache. DRAM SSD HDD Two-level exclusive cache

Outline • Introduction • Motivation • System Design • Evaluation • Conclusion

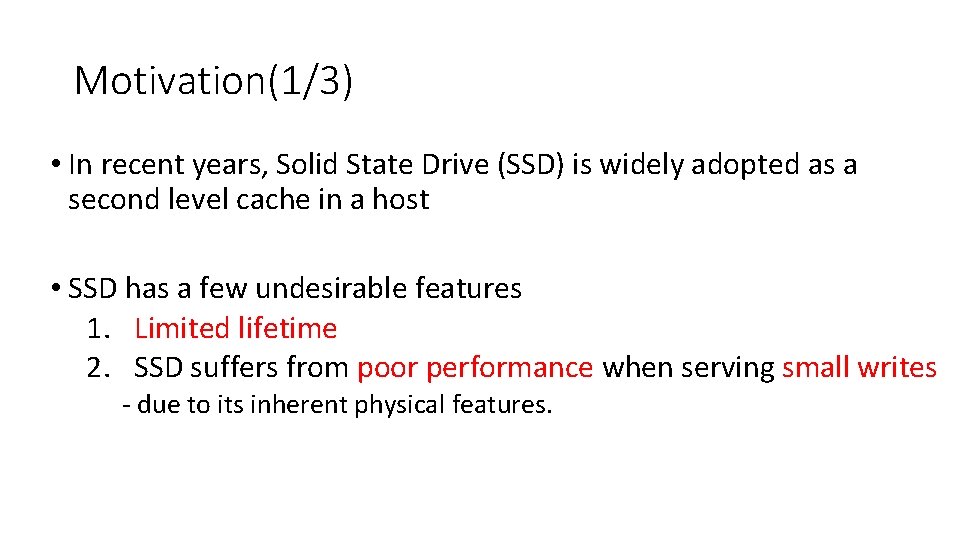

Motivation(1/3) • In recent years, Solid State Drive (SSD) is widely adopted as a second level cache in a host • SSD has a few undesirable features 1. Limited lifetime 2. SSD suffers from poor performance when serving small writes - due to its inherent physical features.

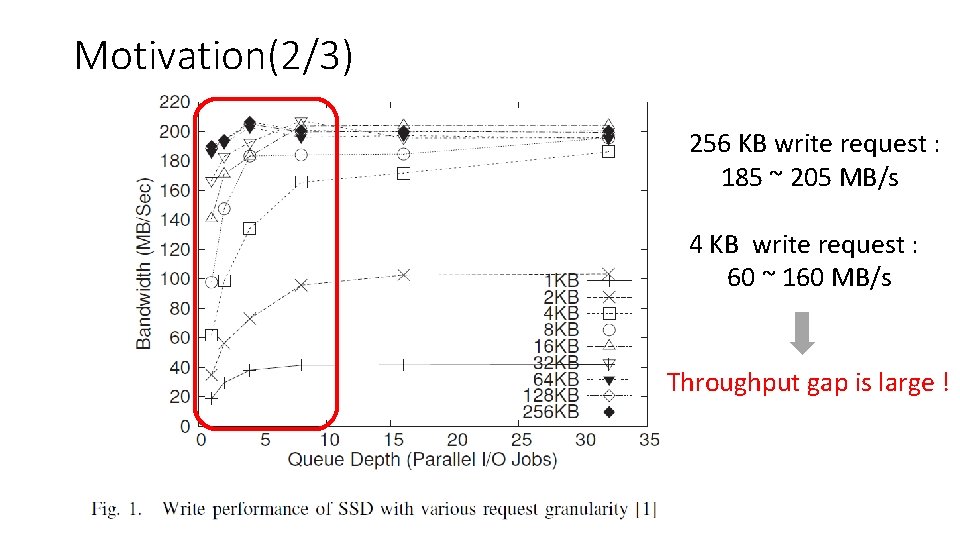

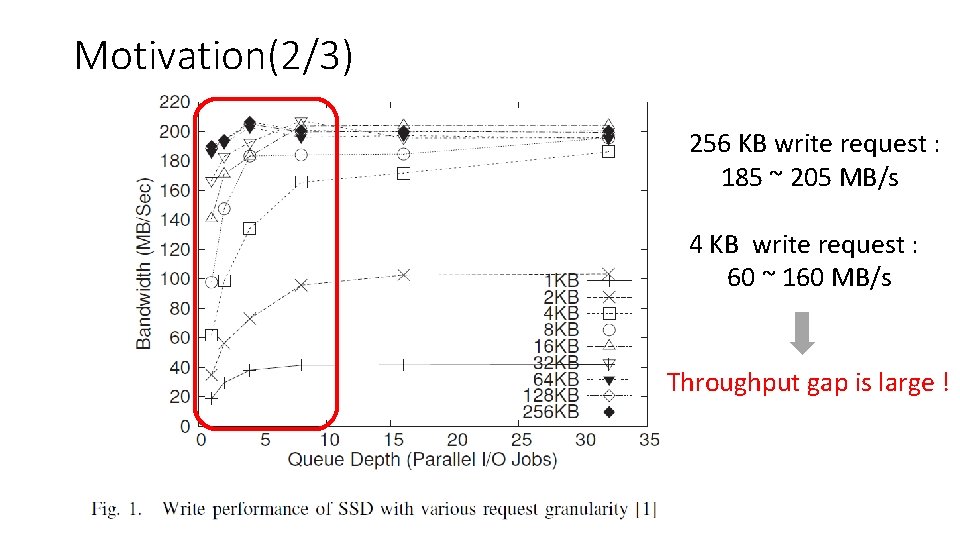

Motivation(2/3) 256 KB write request : 185 ~ 205 MB/s 4 KB write request : 60 ~ 160 MB/s Throughput gap is large !

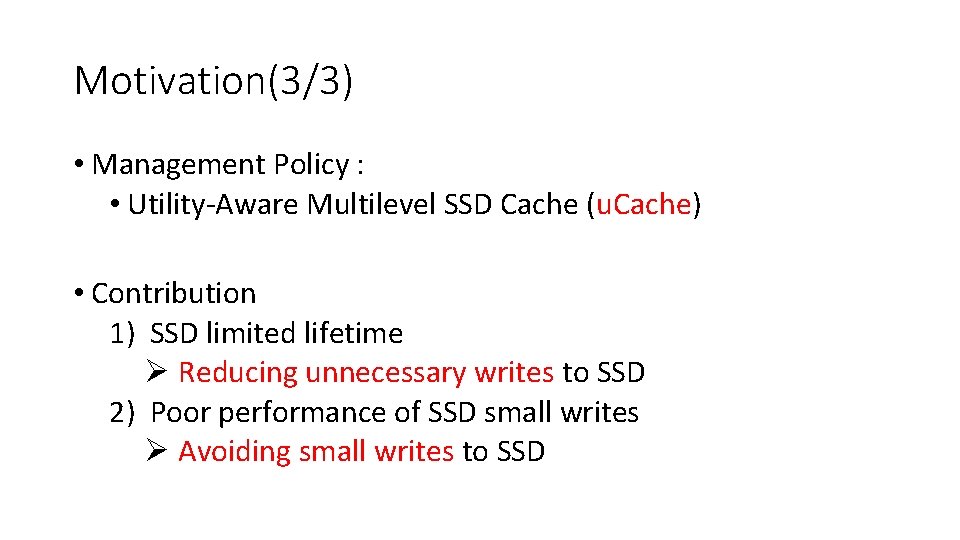

Motivation(3/3) • Management Policy : • Utility-Aware Multilevel SSD Cache (u. Cache) • Contribution 1) SSD limited lifetime Ø Reducing unnecessary writes to SSD 2) Poor performance of SSD small writes Ø Avoiding small writes to SSD

Outline • Introduction • Motivation • System Design • Evaluation • Conclusion

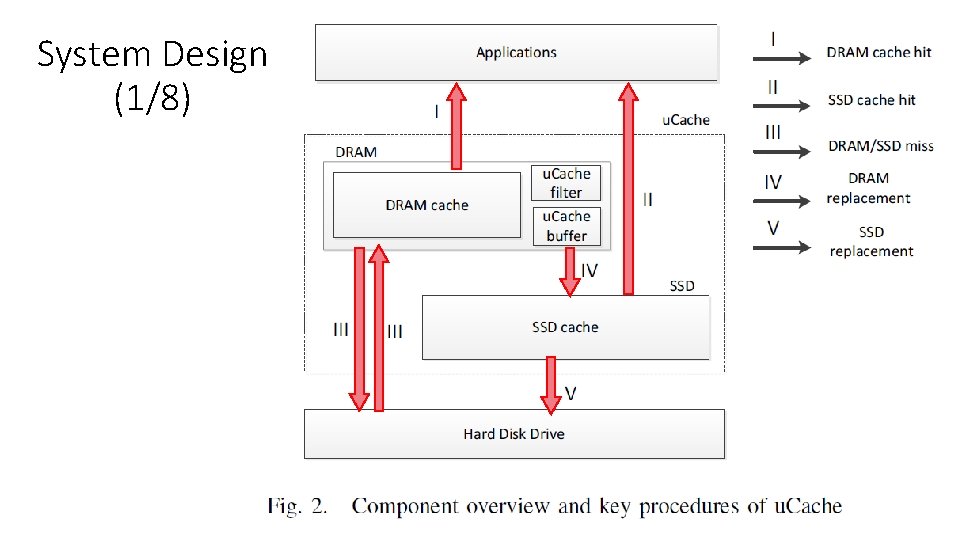

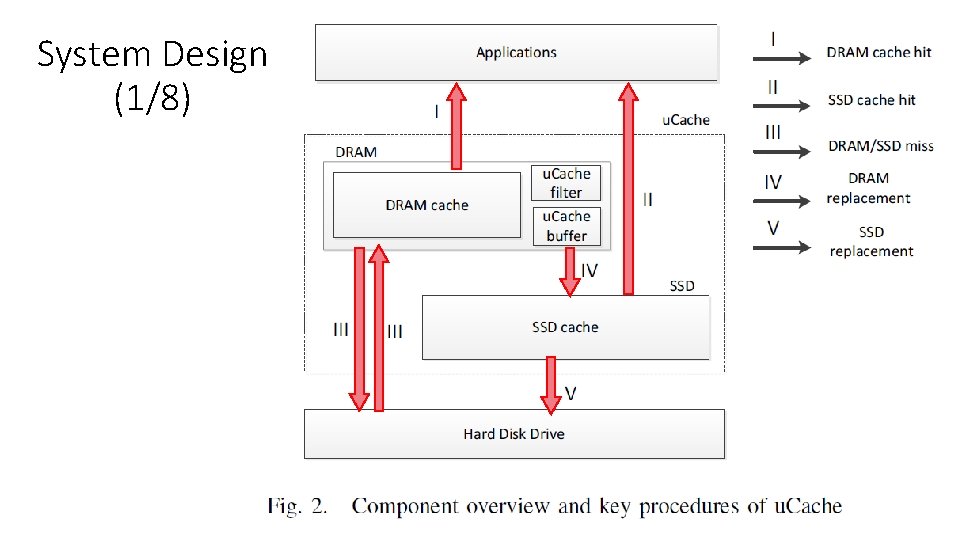

System Design (1/8)

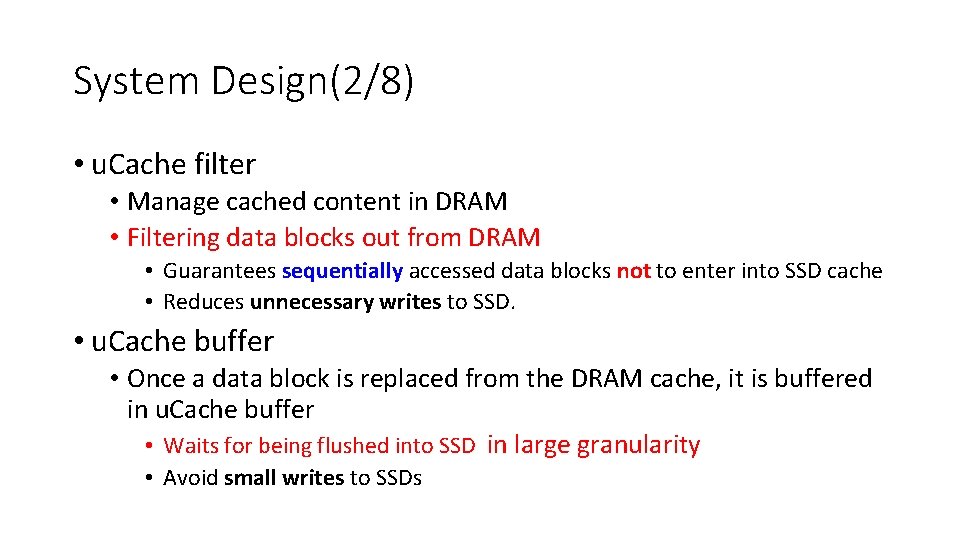

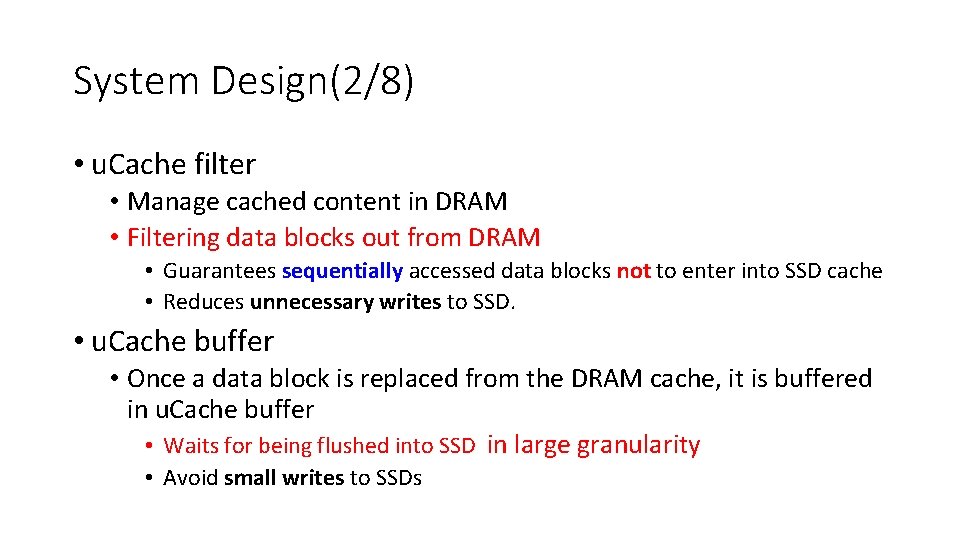

System Design(2/8) • u. Cache filter • Manage cached content in DRAM • Filtering data blocks out from DRAM • Guarantees sequentially accessed data blocks not to enter into SSD cache • Reduces unnecessary writes to SSD. • u. Cache buffer • Once a data block is replaced from the DRAM cache, it is buffered in u. Cache buffer • Waits for being flushed into SSD in large granularity • Avoid small writes to SSDs

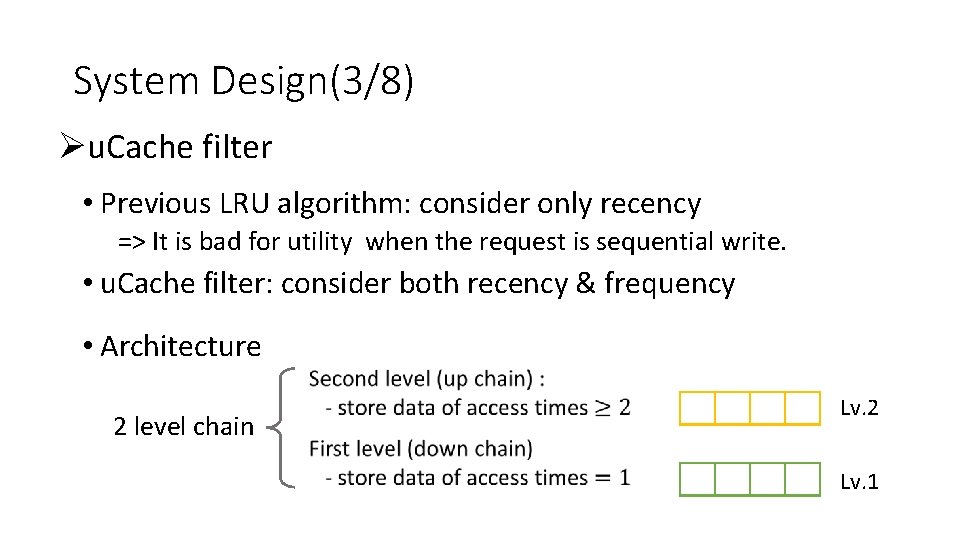

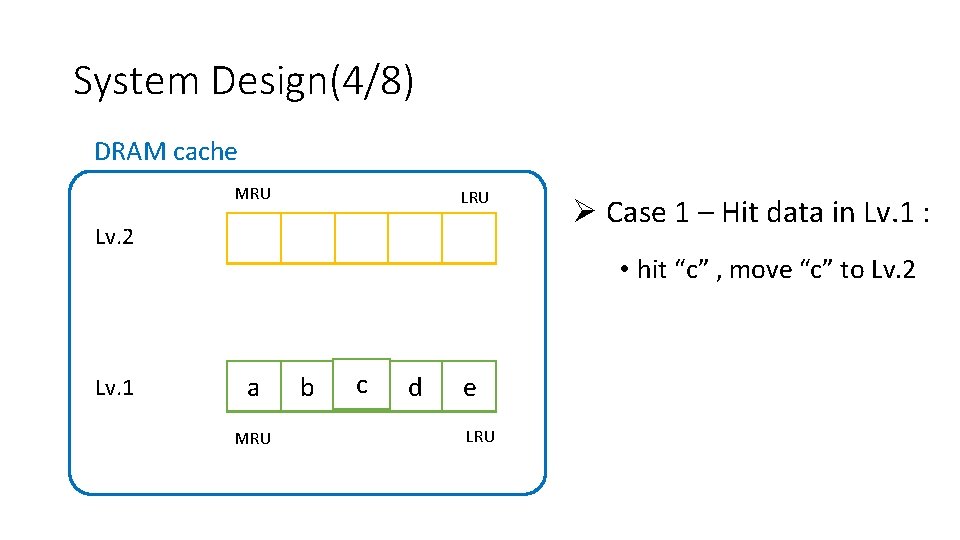

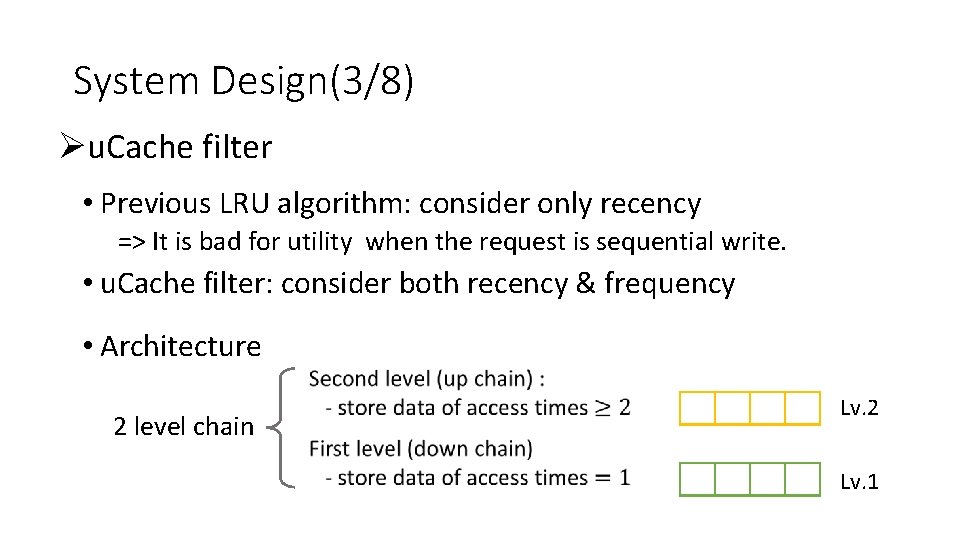

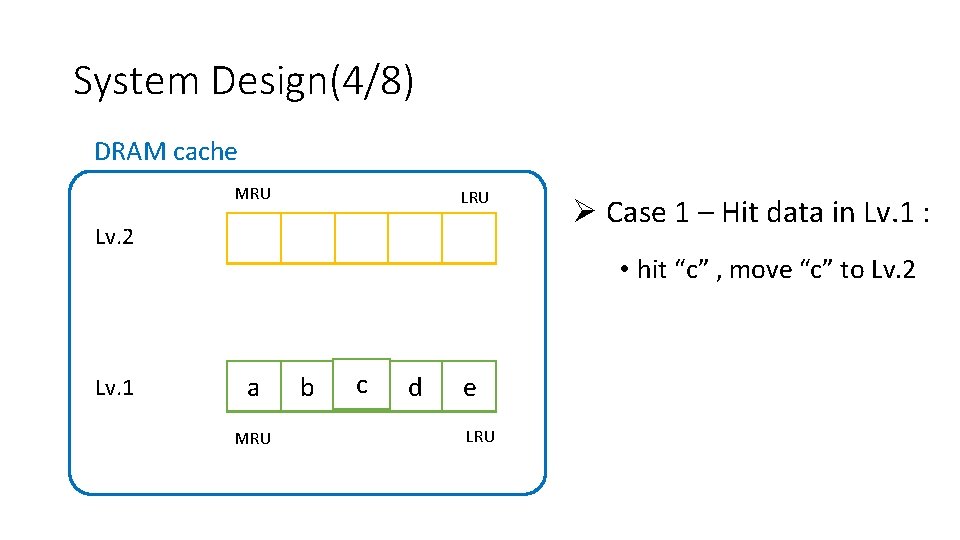

System Design(3/8) Øu. Cache filter • Previous LRU algorithm: consider only recency => It is bad for utility when the request is sequential write. • u. Cache filter: consider both recency & frequency • Architecture 2 level chain Lv. 2 Lv. 1

System Design(4/8) DRAM cache MRU Lv. 2 Ø Case 1 – Hit data in Lv. 1 : • hit “c” , move “c” to Lv. 2 Lv. 1 a MRU b c d e LRU

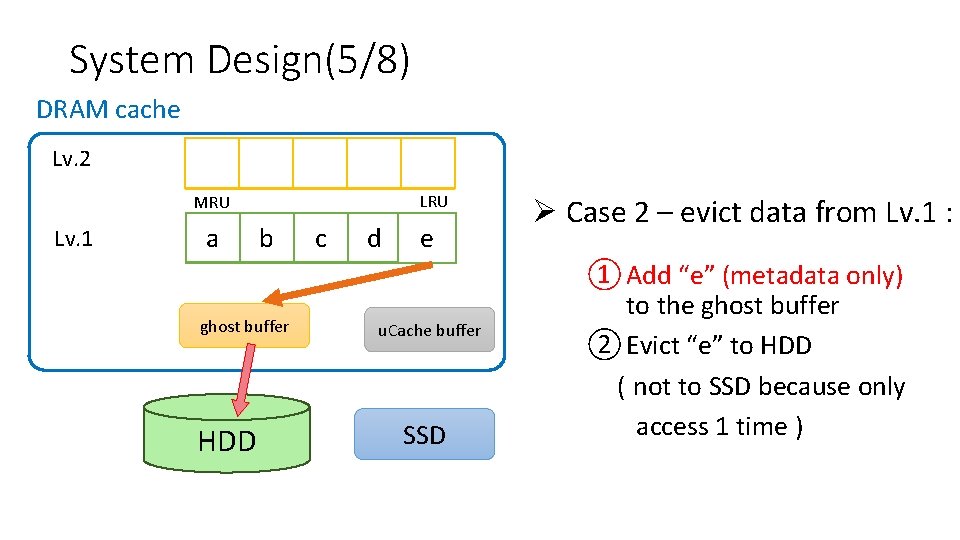

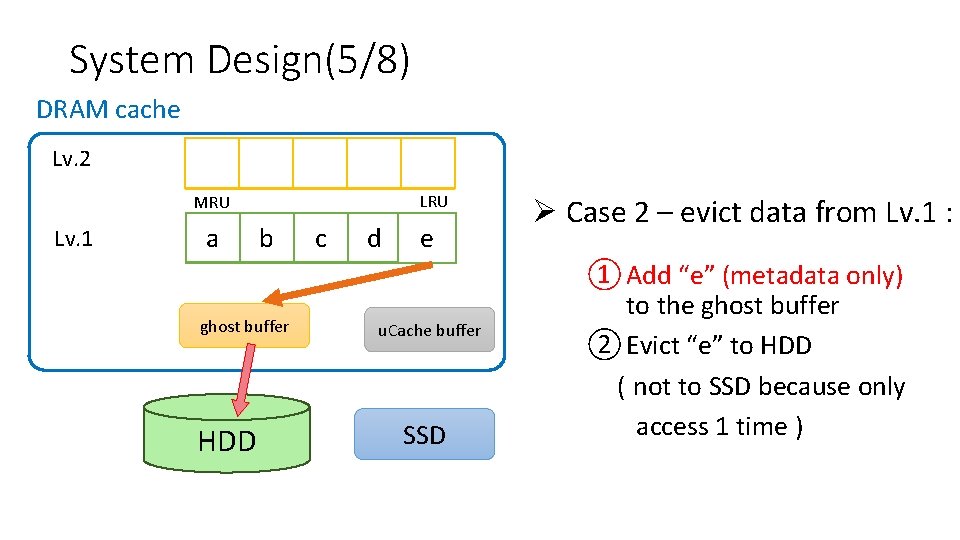

System Design(5/8) DRAM cache Lv. 2 LRU MRU Lv. 1 a b ghost buffer HDD c d e u. Cache buffer SSD Ø Case 2 – evict data from Lv. 1 : ① Add “e” (metadata only) to the ghost buffer ② Evict “e” to HDD ( not to SSD because only access 1 time )

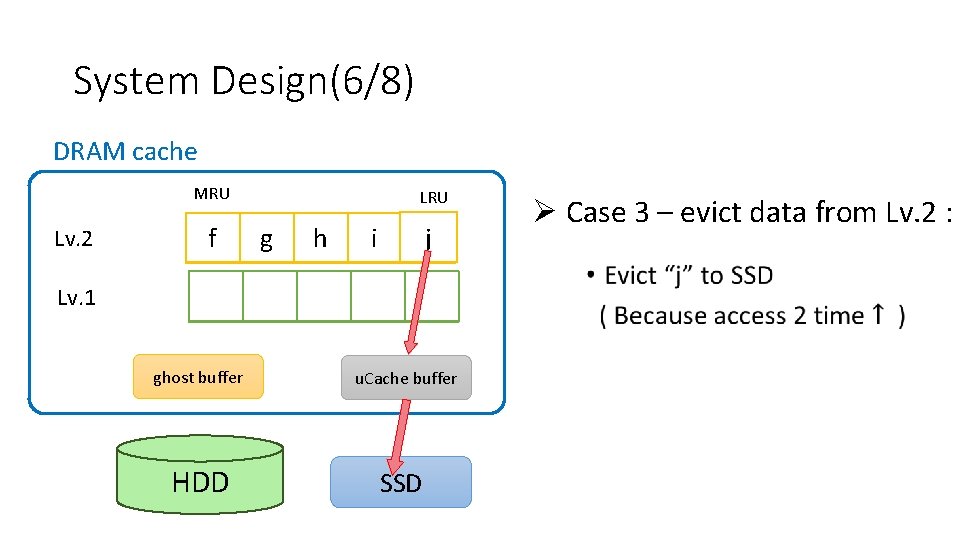

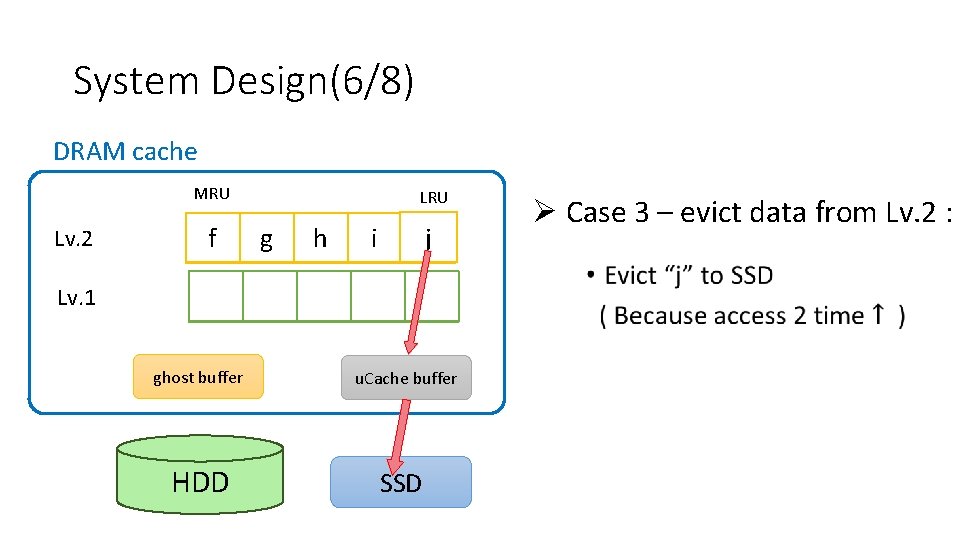

System Design(6/8) DRAM cache MRU Lv. 2 f LRU g h j i Lv. 1 ghost buffer u. Cache buffer HDD SSD Ø Case 3 – evict data from Lv. 2 :

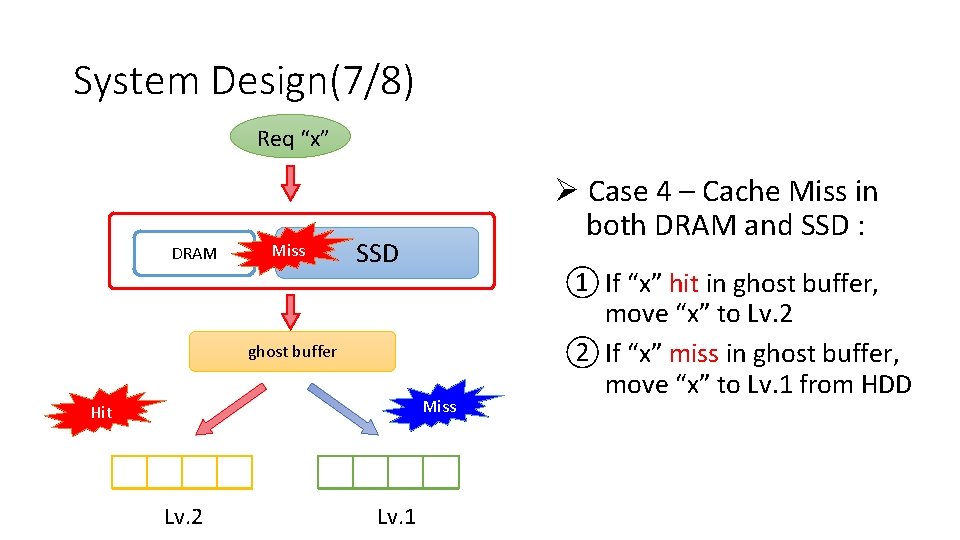

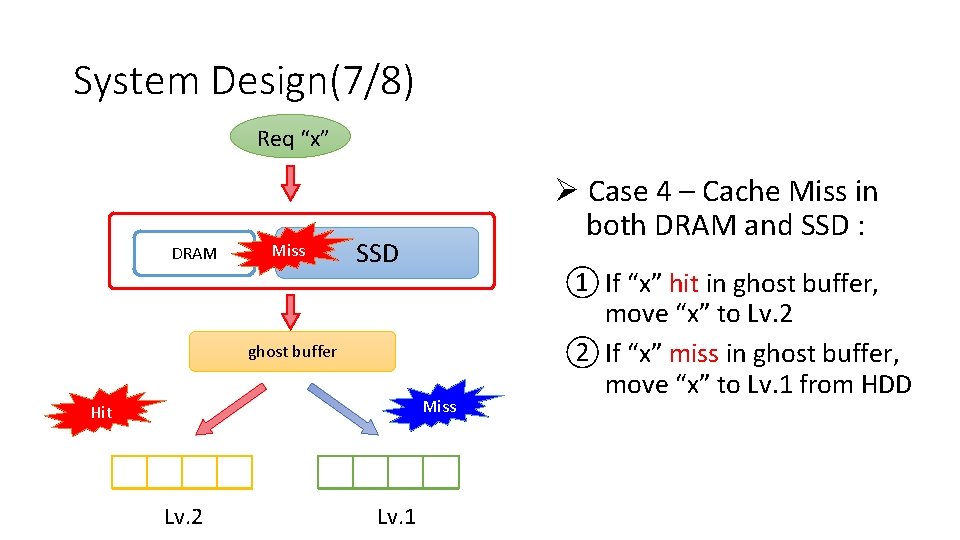

System Design(7/8) Req “x” DRAM Miss Ø Case 4 – Cache Miss in both DRAM and SSD : SSD ghost buffer Miss Hit Lv. 2 Lv. 1 ① If “x” hit in ghost buffer, move “x” to Lv. 2 ② If “x” miss in ghost buffer, move “x” to Lv. 1 from HDD

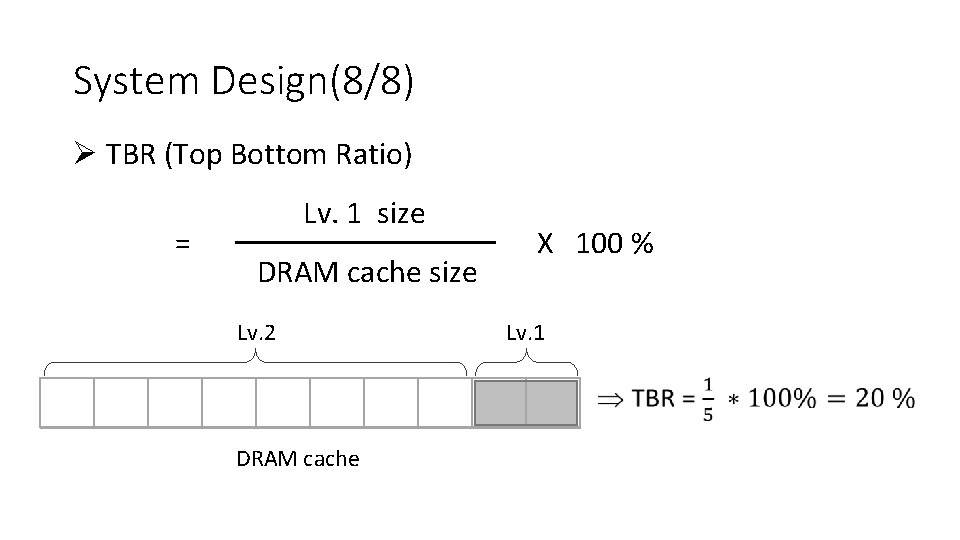

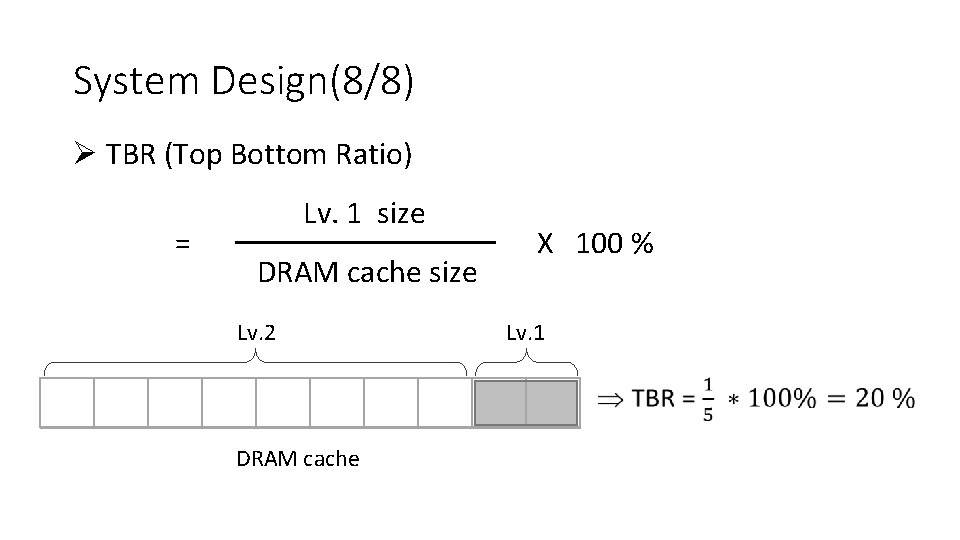

System Design(8/8) Ø TBR (Top Bottom Ratio) = Lv. 1 size DRAM cache size Lv. 2 DRAM cache X 100 % Lv. 1

Outline • Introduction • Motivation • System Design • Evaluation • Conclusion

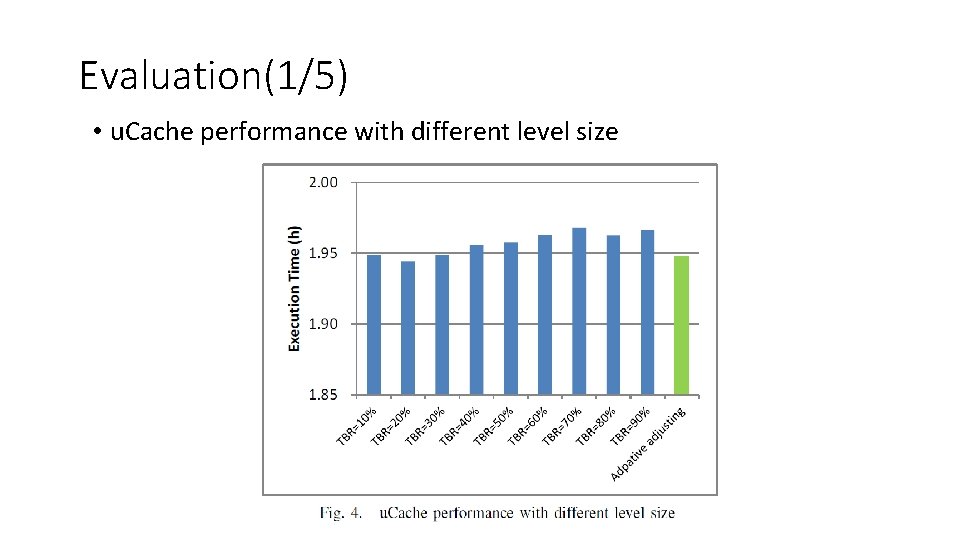

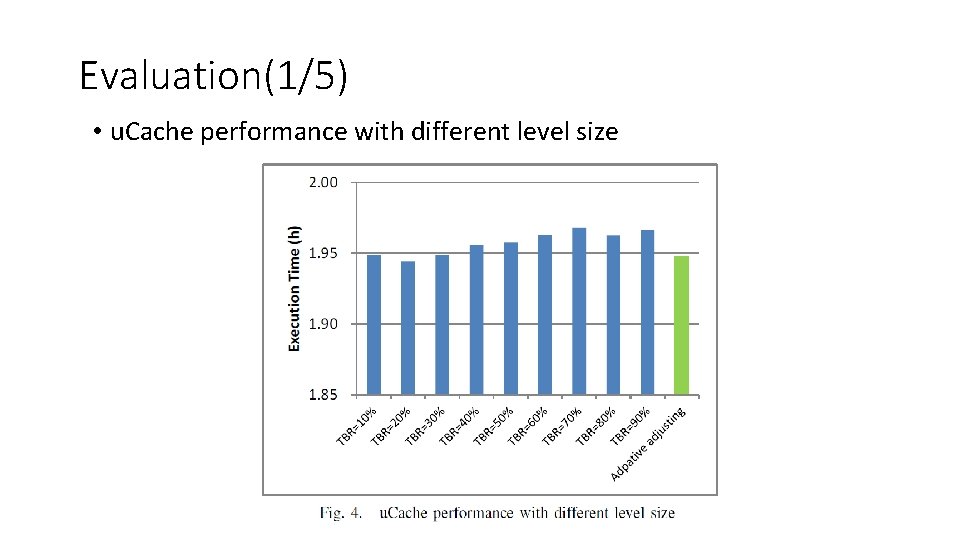

Evaluation(1/5) • u. Cache performance with different level size

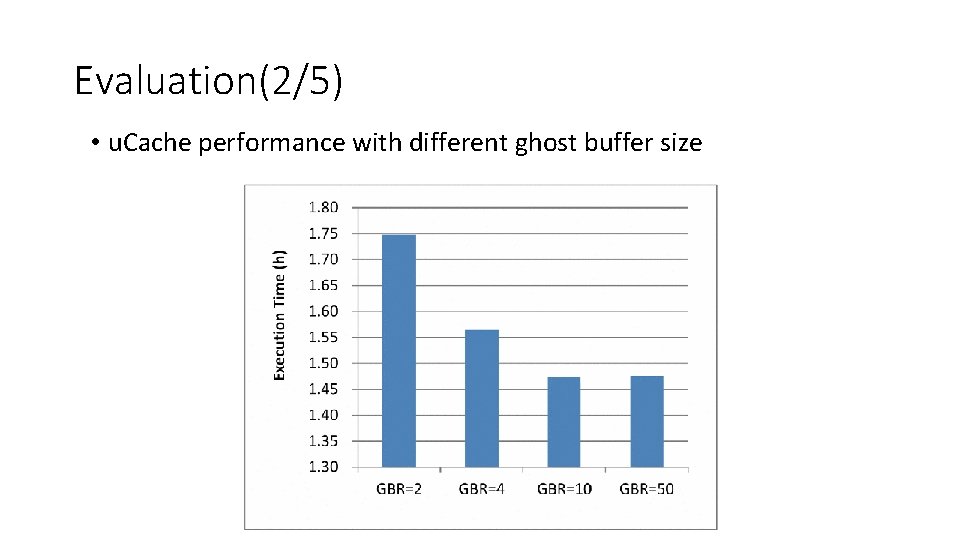

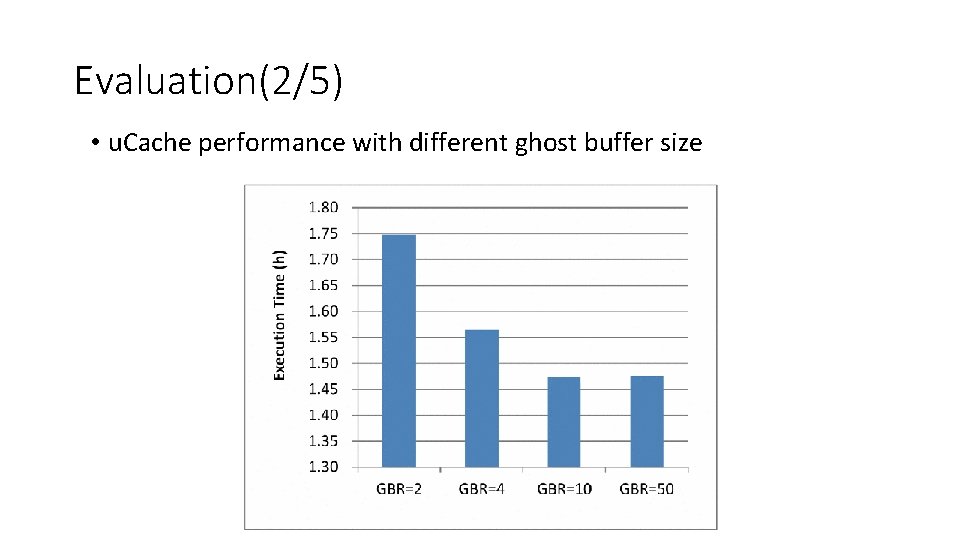

Evaluation(2/5) • u. Cache performance with different ghost buffer size

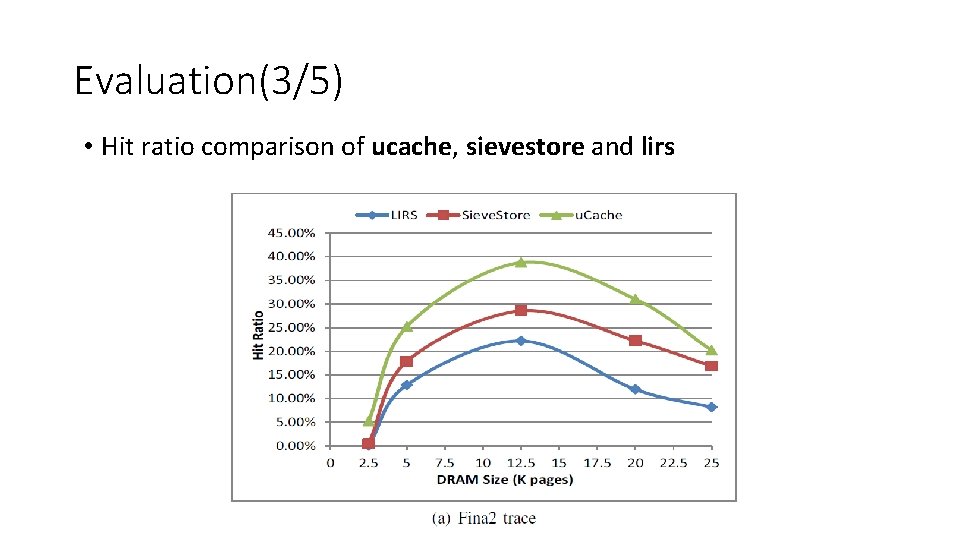

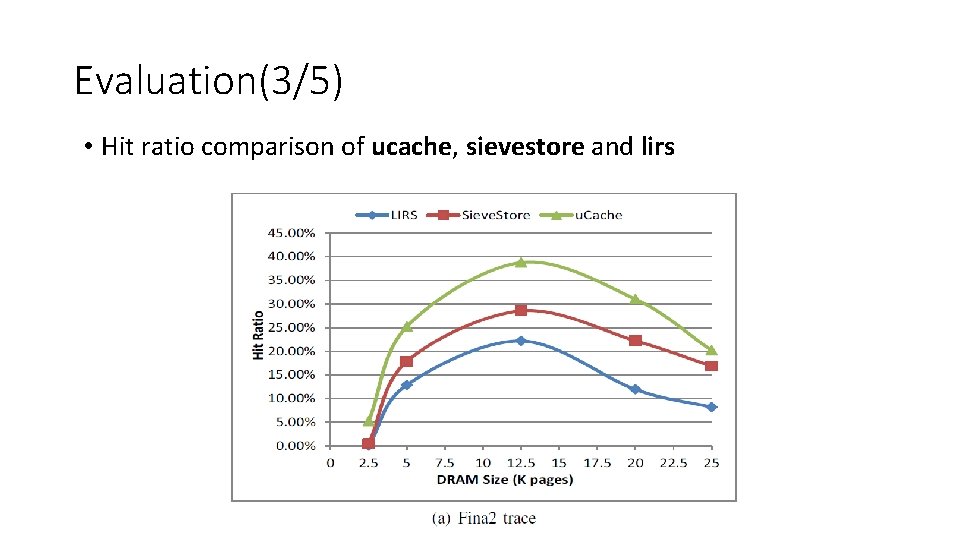

Evaluation(3/5) • Hit ratio comparison of ucache, sievestore and lirs

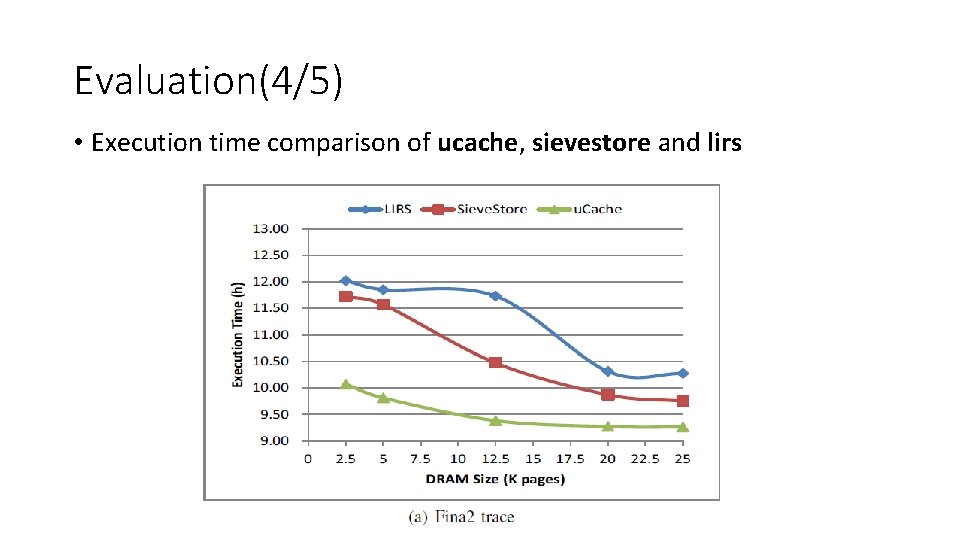

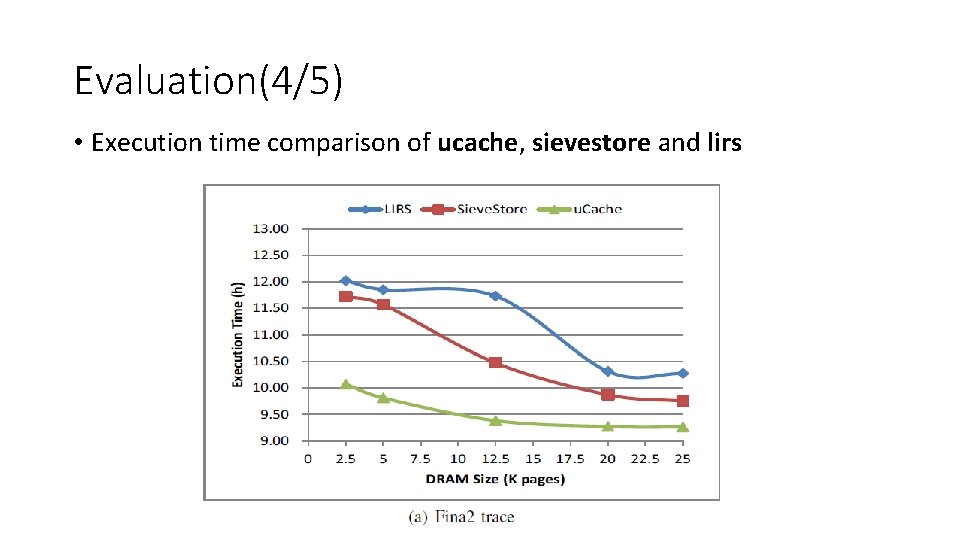

Evaluation(4/5) • Execution time comparison of ucache, sievestore and lirs

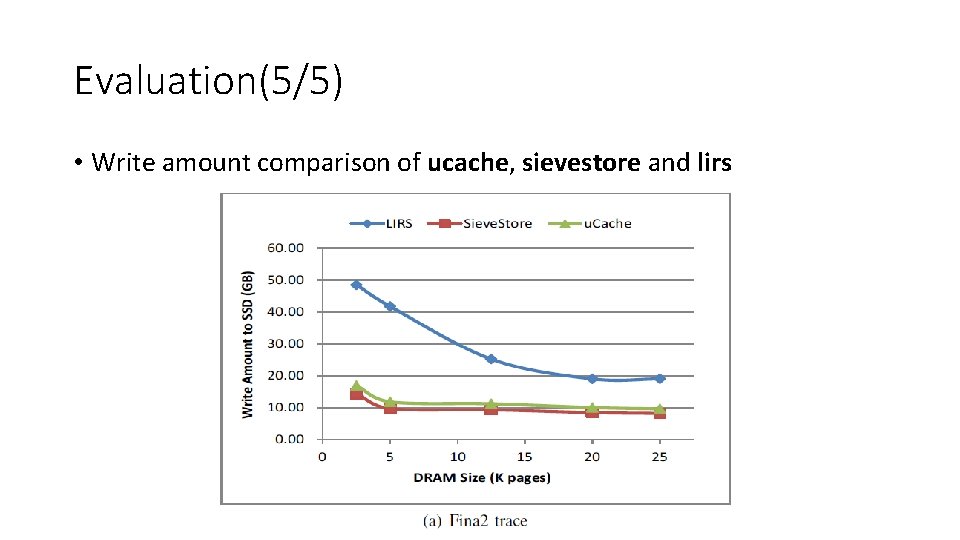

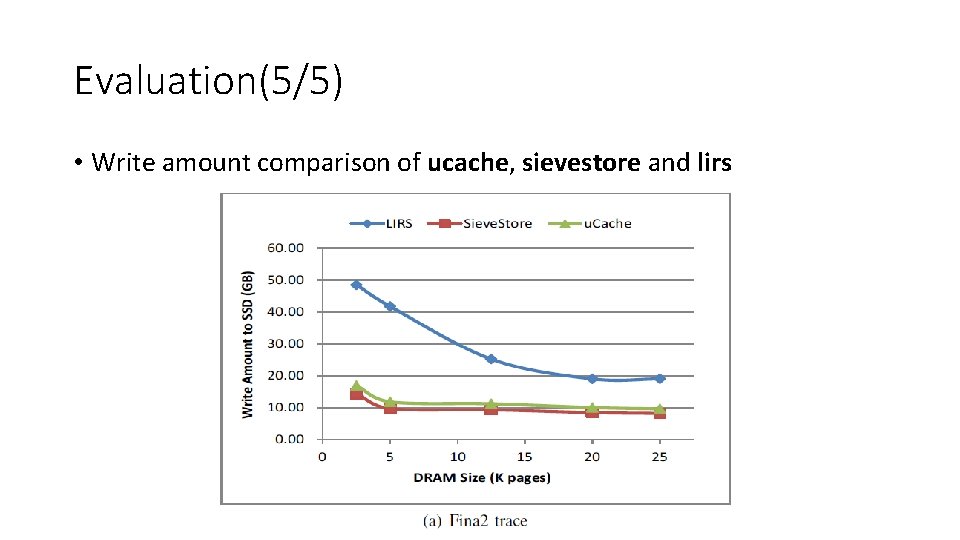

Evaluation(5/5) • Write amount comparison of ucache, sievestore and lirs

Outline • Introduction • Related Work • System Design • Evaluation • Conclusion

Conclusion • Propose u. Cache, a utility aware multilevel SSD cache management policy • reducing unnecessary writes to SSDs • avoiding small writes to SSDs • Achieve high utility of SSD by reducing the negative impact of its disadvantages