Twos Complement Operations Numbers 1 Negating a twos

Two's Complement Operations Numbers 1 Negating a two's complement number: invert all bits and add 1, ignoring final carry remember: “negate” and “invert” are quite different! Converting n bit numbers into numbers with more than n bits: MIPS 16 bit immediate gets converted to 32 bits for arithmetic copy the most significant bit (the sign bit) into the other bits: 0010 -> 0000 0010 1010 -> 1111 1010 "sign extension" (lbu vs. lb) Set of representable integers is asymmetric about 0. There is only one representation of 0. Intro Computer Organization

MIPS 32 -bit Signed Integers Numbers 2 0000 0000 two = 0 ten 0000 0000 0001 two = +1 ten 0000 0000 0010 two = +2 ten. . . 0111 1111 1111 1110 two = +2, 147, 483, 646 ten 0111 1111 1111 two = +2, 147, 483, 647 ten 1000 0000 0000 two = – 2, 147, 483, 648 ten 1000 0000 0000 0001 two = – 2, 147, 483, 647 ten 1000 0000 0000 0010 two = – 2, 147, 483, 646 ten. . . 1111 1111 1101 two = – 3 ten 1111 1111 1110 two = – 2 ten 1111 1111 two = – 1 ten Intro Computer Organization

Subtraction Numbers 3 Subtraction is dull and boring, since we know from elementary school that: x – y = x + (-y) Intro Computer Organization

Detecting Overflow Numbers 4 No overflow when adding a positive and a negative number No overflow when signs are the same for subtraction Overflow occurs when the value affects the sign: overflow when adding two positives yields a negative or, adding two negatives gives a positive or, subtract a negative from a positive and get a negative or, subtract a positive from a negative and get a positive Consider the operations A + B, and A – B Can overflow occur if B is 0 ? - Can overflow occur if A is 0 ? Intro Computer Organization

Effects of Overflow Numbers 5 An exception (interrupt) occurs control jumps to predefined address for exception interrupted address is saved for possible resumption details based on software system / language example: flight control vs. homework assignment Don't always want to detect overflow new MIPS instructions: addu, addiu, subu Note: - addiu still sign-extends! sltu, sltiu for unsigned comparisons Intro Computer Organization

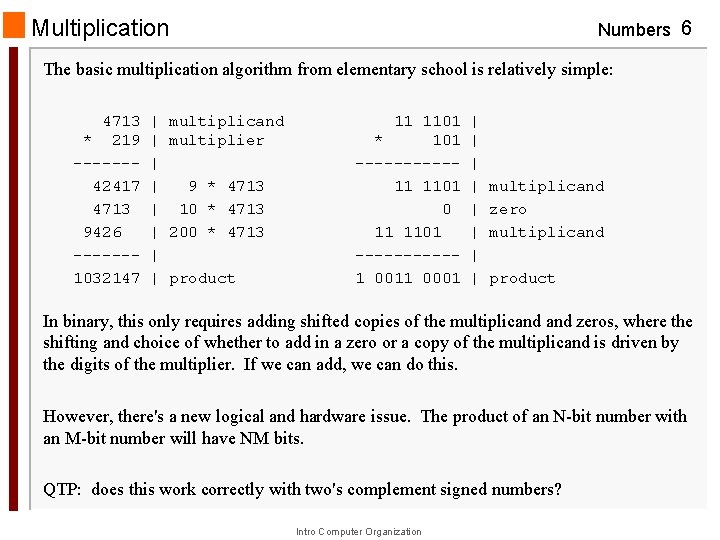

Multiplication Numbers 6 The basic multiplication algorithm from elementary school is relatively simple: 4713 * 219 ------42417 4713 9426 ------1032147 | | | | multiplicand multiplier 9 * 4713 10 * 4713 200 * 4713 product 11 1101 * 101 -----11 1101 0 11 1101 -----1 0011 0001 | | | | multiplicand zero multiplicand product In binary, this only requires adding shifted copies of the multiplicand zeros, where the shifting and choice of whether to add in a zero or a copy of the multiplicand is driven by the digits of the multiplier. If we can add, we can do this. However, there's a new logical and hardware issue. The product of an N-bit number with an M-bit number will have NM bits. QTP: does this work correctly with two's complement signed numbers? Intro Computer Organization

Basic Multiplication Algorithm Numbers 7 When we consider expressing this in hardware, we'll examine ways to optimize it further. Intro Computer Organization

Division Numbers 8 The basic division algorithm from elementary school is a bit more complex: 101010 +----101 |11010110 101 ----111 101 ----100 | quotient | dividend | remainder Decision-making is required to determine whether the next digit of the quotient will be 1 or 0. This will require an additional arithmetic operation at each step. Intro Computer Organization

Basic Division Algorithm Numbers 9 When we consider expressing this in hardware, we'll examine ways to optimize it further. Intro Computer Organization

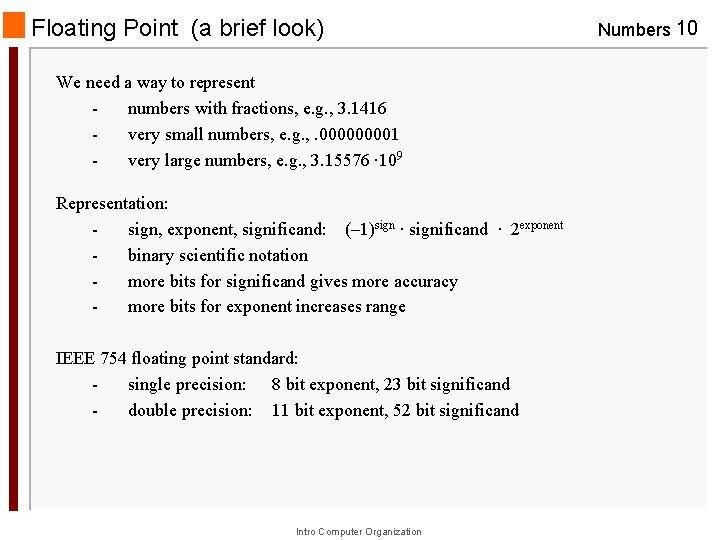

Floating Point (a brief look) We need a way to represent numbers with fractions, e. g. , 3. 1416 very small numbers, e. g. , . 00001 very large numbers, e. g. , 3. 15576 ∙ 109 Representation: sign, exponent, significand: (– 1)sign ∙ significand ∙ 2 exponent binary scientific notation more bits for significand gives more accuracy more bits for exponent increases range IEEE 754 floating point standard: single precision: 8 bit exponent, 23 bit significand double precision: 11 bit exponent, 52 bit significand Intro Computer Organization Numbers 10

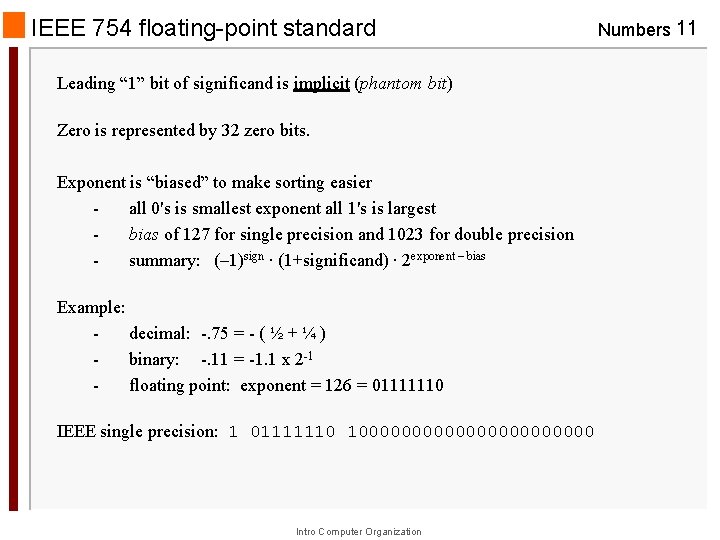

IEEE 754 floating-point standard Leading “ 1” bit of significand is implicit (phantom bit) Zero is represented by 32 zero bits. Exponent is “biased” to make sorting easier all 0's is smallest exponent all 1's is largest bias of 127 for single precision and 1023 for double precision summary: (– 1)sign ∙ (1+significand) ∙ 2 exponent – bias Example: decimal: -. 75 = - ( ½ + ¼ ) binary: -. 11 = -1. 1 x 2 -1 floating point: exponent = 126 = 01111110 IEEE single precision: 1 01111110 100000000000 Intro Computer Organization Numbers 11

Floating Point Multiplication Numbers 12 Multiplication: - multiply the mantissas - add the exponents - normalize the result 32. 2510 = 100000. 012 1. 0000001 · 25 0. 187510 = 0. 00112 1. 1 · 2 -3 in IEEE single format 1. 0000001 · 1. 1 = 1. 10000011 Exponent would be 2, so the product equals: 1. 10000011 · 22 = 110. 0000112 6. 04687510 In this case, the result is already normalized to the IEEE format. Computer Science Dept Va Tech February 2006 Intro Computer Organization © 2006 Mc. Quain & Ribbens

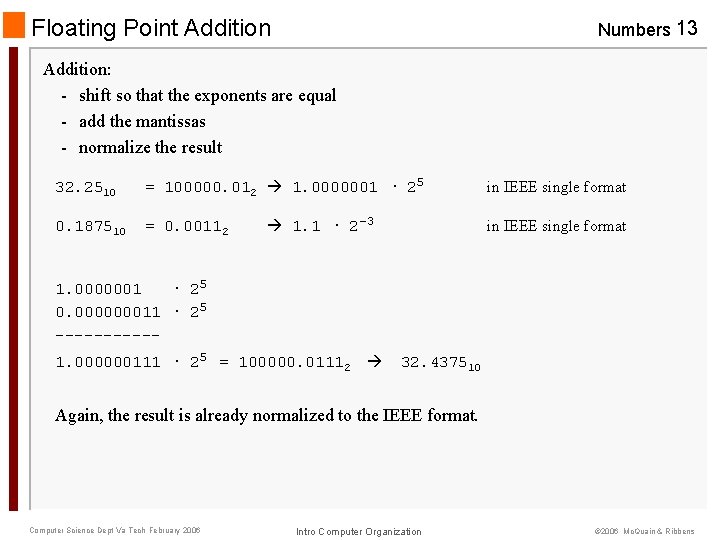

Floating Point Addition Numbers 13 Addition: - shift so that the exponents are equal - add the mantissas - normalize the result 32. 2510 = 100000. 012 1. 0000001 · 25 0. 187510 = 0. 00112 1. 1 · 2 -3 in IEEE single format 1. 0000001 · 25 0. 000000011 · 25 -----1. 000000111 · 25 = 100000. 01112 32. 437510 Again, the result is already normalized to the IEEE format. Computer Science Dept Va Tech February 2006 Intro Computer Organization © 2006 Mc. Quain & Ribbens

Floating Point Complexities Operations are somewhat more complicated (see text) In addition to overflow we can have “underflow” Representable values are "relatively" equally spaced Accuracy can be a big problem IEEE 754 keeps two extra bits, guard and round four rounding modes positive divided by zero yields “infinity” zero divide by zero yields “not a number” other complexities Implementing the standard can be tricky Not using the standard can be even worse see text for description of 80 x 86 and Pentium bug! Intro Computer Organization Numbers 14

Some Floating Point Issues Numbers 15 Machine epsilon is defined to be ε = 2 -t, where t is the number of bits in the mantissa. This is the smallest distinguishable relative difference between two numbers that have different floating-point representations. Storage errors are inevitable since finitely-many bits are used in the representation. The most we can expect is that: fl(x) = x(1 + δ), where |δ| <= ε Round-off errors are also inevitable, and may be magnified in interesting ways. Take Numerical Analysis or Numerical Methods to learn more… Intro Computer Organization

- Slides: 15