Tutorial to Correct Unwanted Silk Screen Overlaps in

- Slides: 14

Tutorial to Correct Unwanted Silk Screen Overlaps in the Final PCB st Robu Low Robust er Pow LSI V Power VLSI Arijit Banerjee

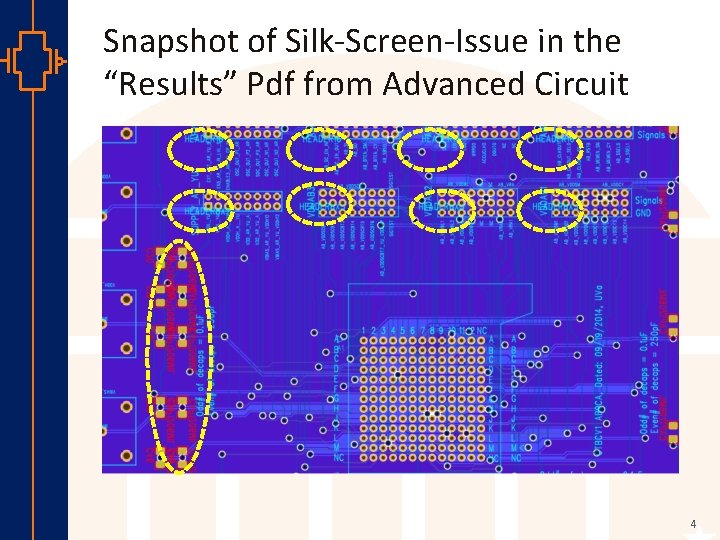

The Issue § When you see the routed layout it looks OK § After you submit in the Advanced Circuit and have the “results” email, if you look into the PDF attached full Layout view you may see some unwanted Silk Screen texts are overlapping with your documentation st Robu Low er Pow VLSI 2

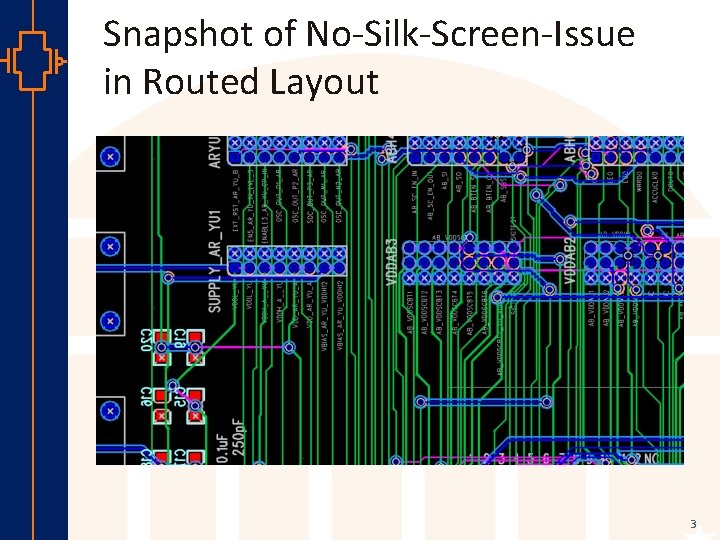

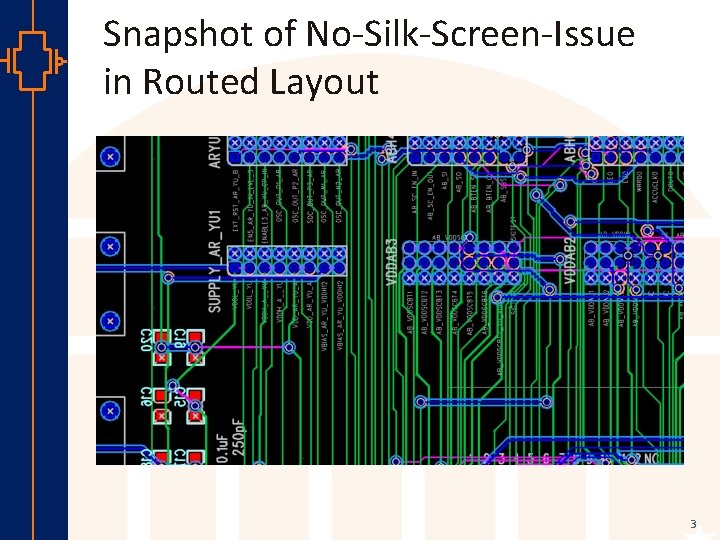

Snapshot of No-Silk-Screen-Issue in Routed Layout st Robu Low er Pow VLSI 3

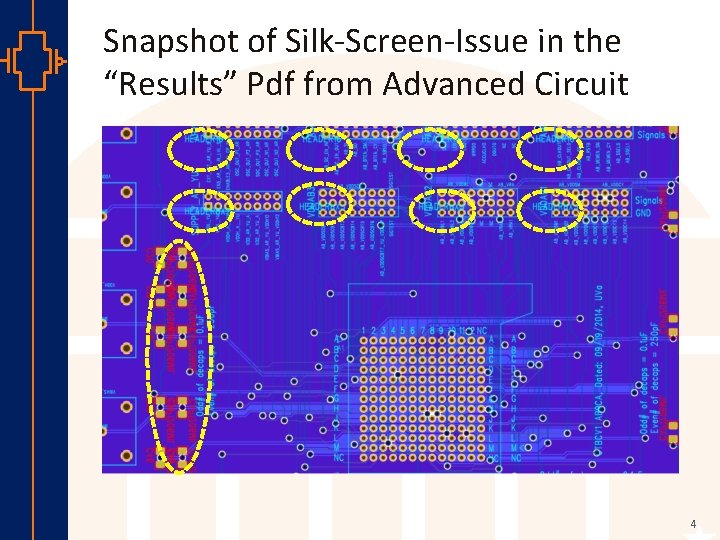

Snapshot of Silk-Screen-Issue in the “Results” Pdf from Advanced Circuit st Robu Low er Pow VLSI 4

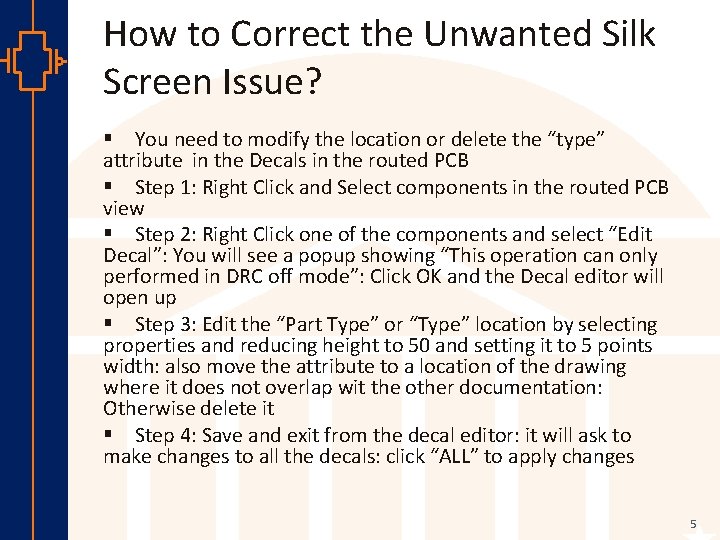

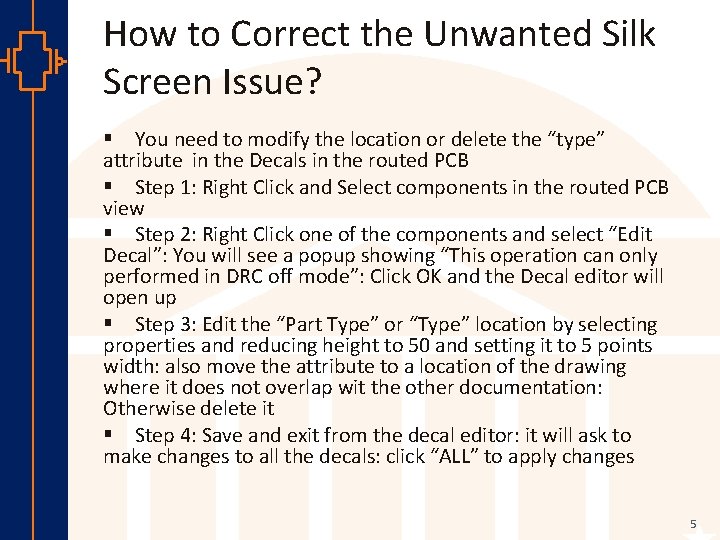

How to Correct the Unwanted Silk Screen Issue? st Robu Low er Pow VLSI § You need to modify the location or delete the “type” attribute in the Decals in the routed PCB § Step 1: Right Click and Select components in the routed PCB view § Step 2: Right Click one of the components and select “Edit Decal”: You will see a popup showing “This operation can only performed in DRC off mode”: Click OK and the Decal editor will open up § Step 3: Edit the “Part Type” or “Type” location by selecting properties and reducing height to 50 and setting it to 5 points width: also move the attribute to a location of the drawing where it does not overlap wit the other documentation: Otherwise delete it § Step 4: Save and exit from the decal editor: it will ask to make changes to all the decals: click “ALL” to apply changes 5

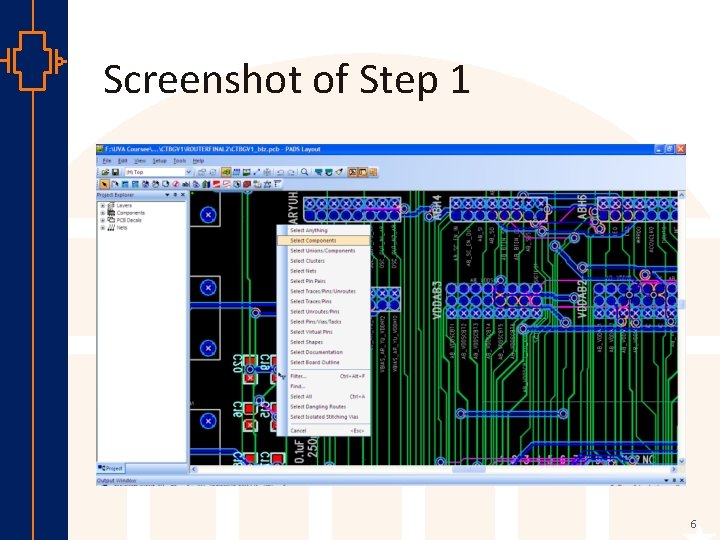

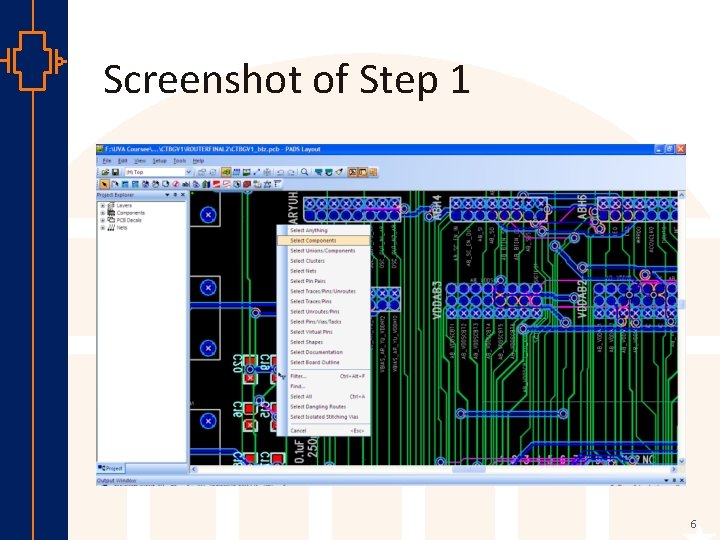

Screenshot of Step 1 st Robu Low er Pow VLSI 6

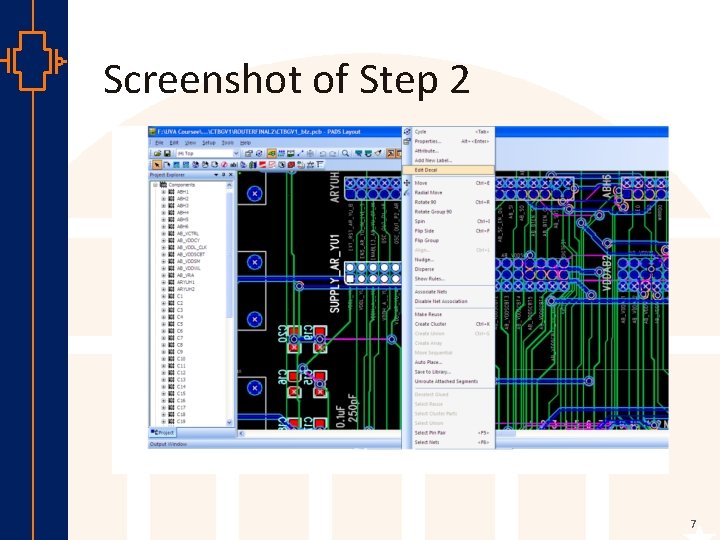

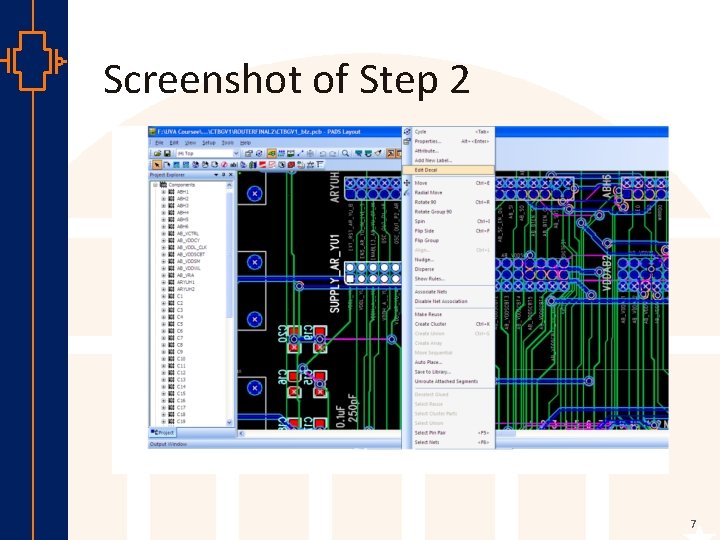

Screenshot of Step 2 st Robu Low er Pow VLSI 7

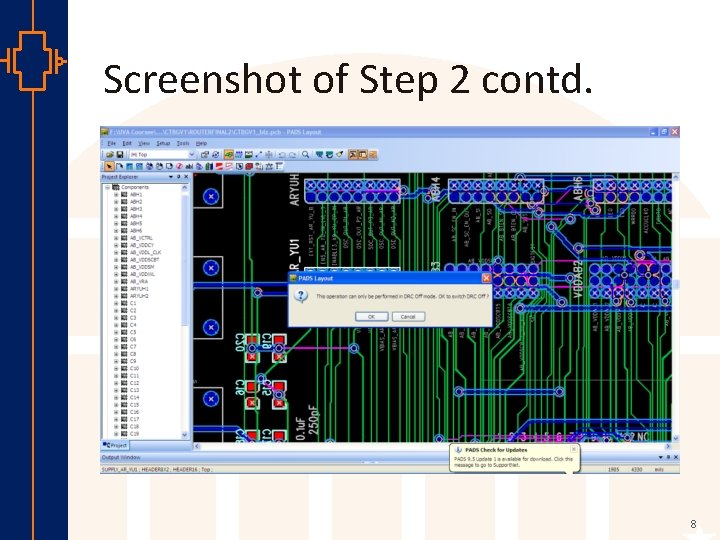

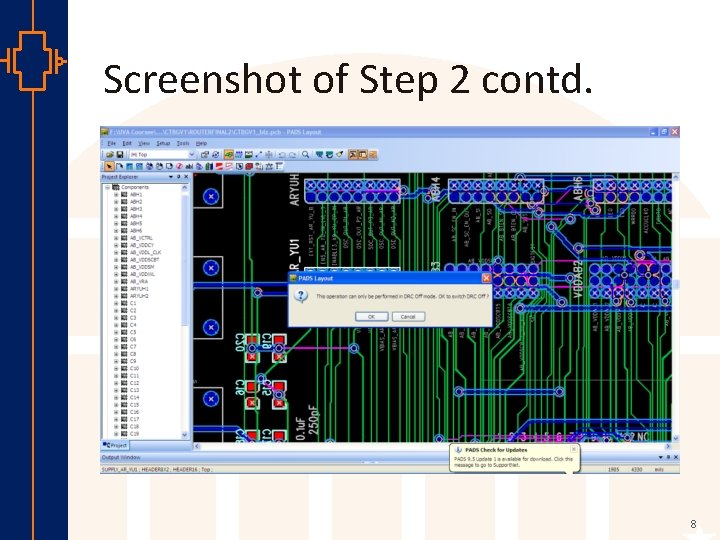

Screenshot of Step 2 contd. st Robu Low er Pow VLSI 8

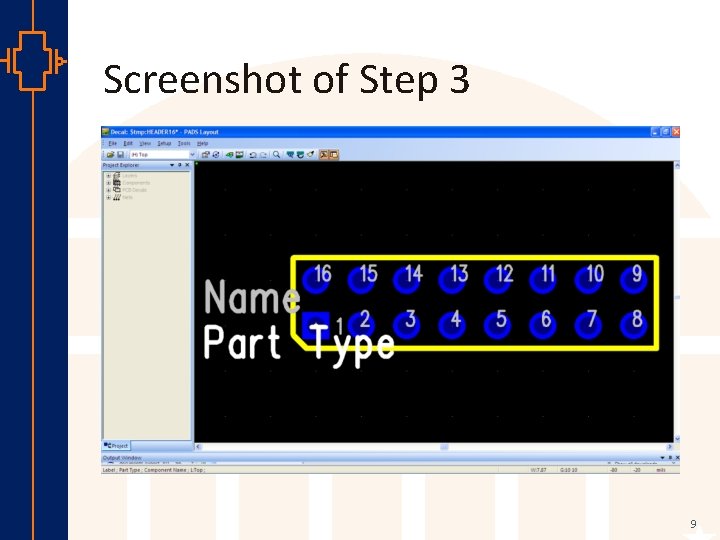

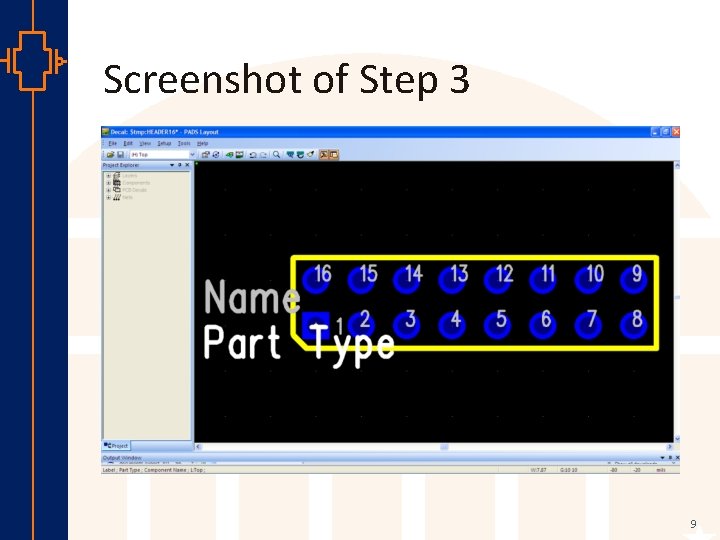

Screenshot of Step 3 st Robu Low er Pow VLSI 9

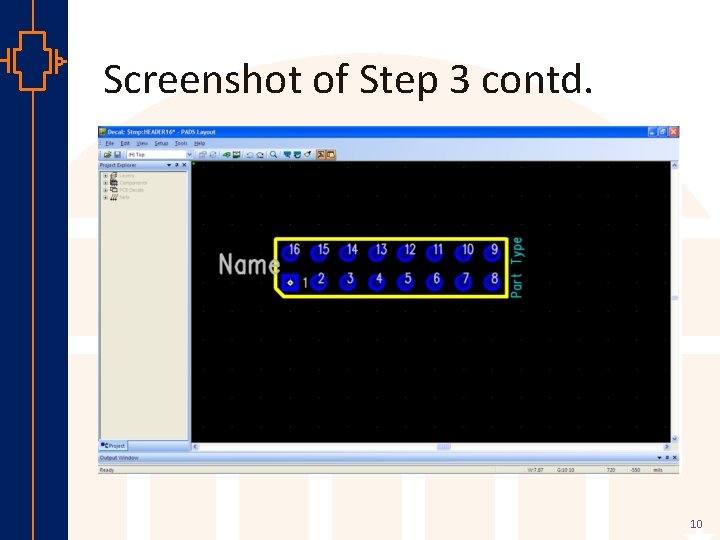

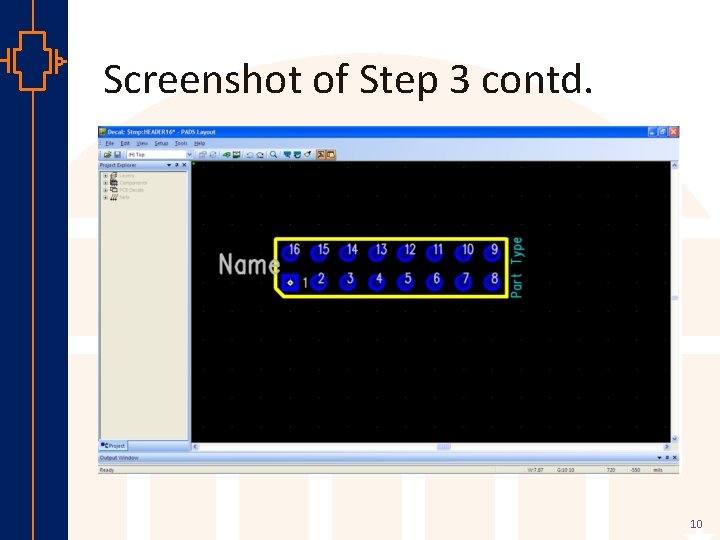

Screenshot of Step 3 contd. st Robu Low er Pow VLSI 10

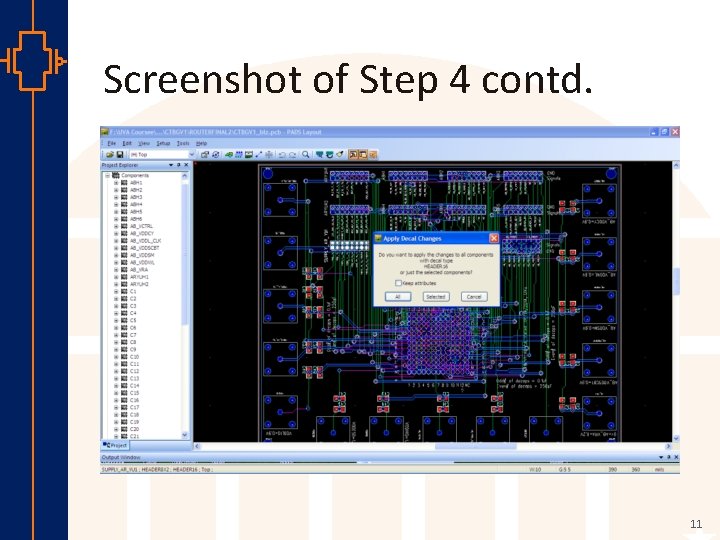

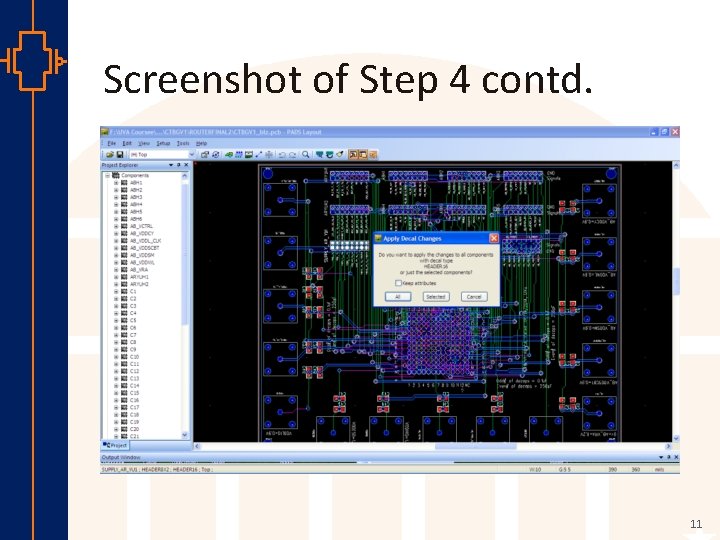

Screenshot of Step 4 contd. st Robu Low er Pow VLSI 11

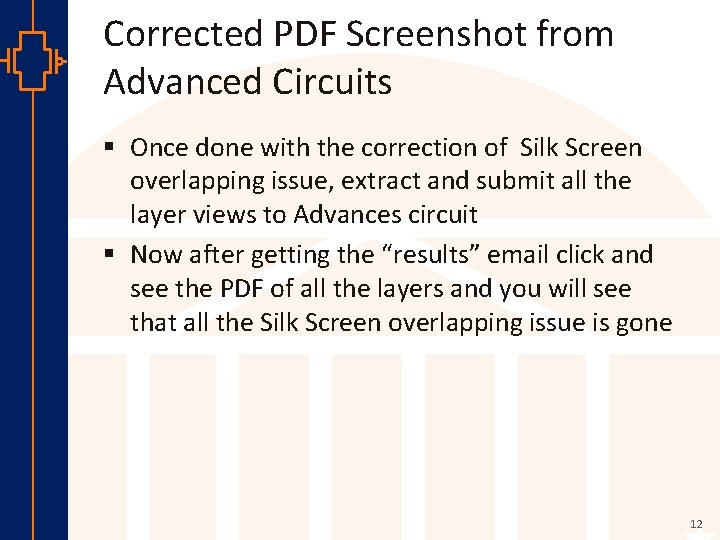

Corrected PDF Screenshot from Advanced Circuits § Once done with the correction of Silk Screen overlapping issue, extract and submit all the layer views to Advances circuit § Now after getting the “results” email click and see the PDF of all the layers and you will see that all the Silk Screen overlapping issue is gone st Robu Low er Pow VLSI 12

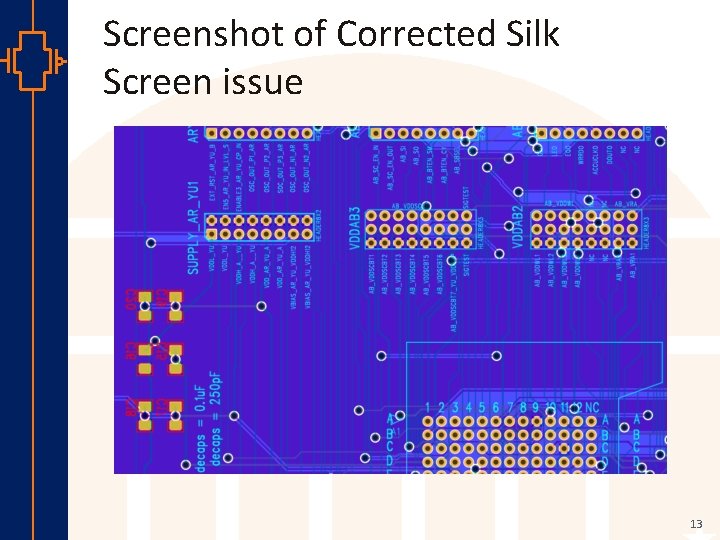

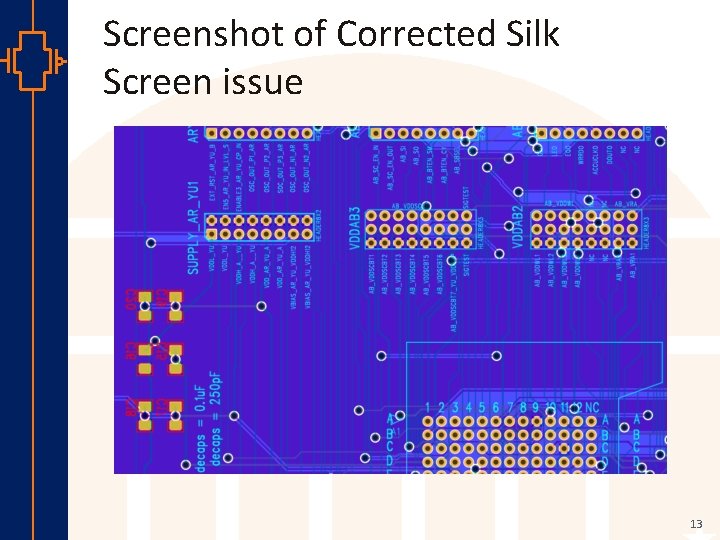

Screenshot of Corrected Silk Screen issue st Robu Low er Pow VLSI 13

Thank You § If you have any questions email at ab 9 ca@virginia. edu st Robu Low er Pow VLSI 14