Tutorial on SIS A System for Sequential Circuit

- Slides: 7

Tutorial on SIS: A System for Sequential Circuit Synthesis EE 201 A @ UCLA Spring 2004

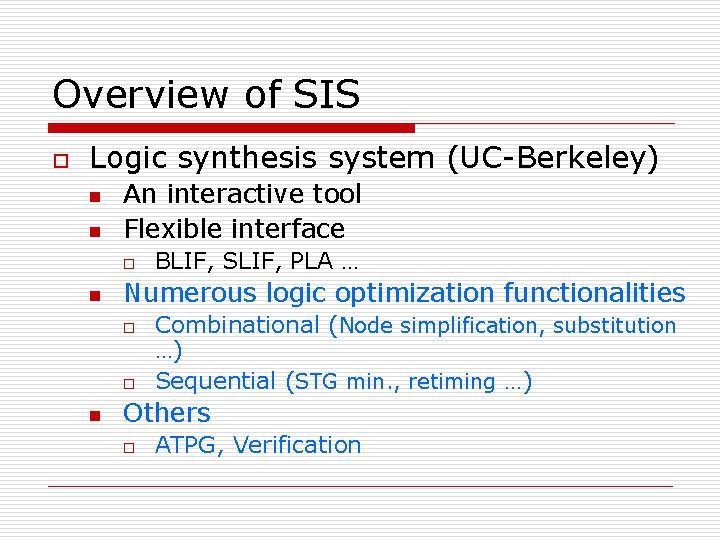

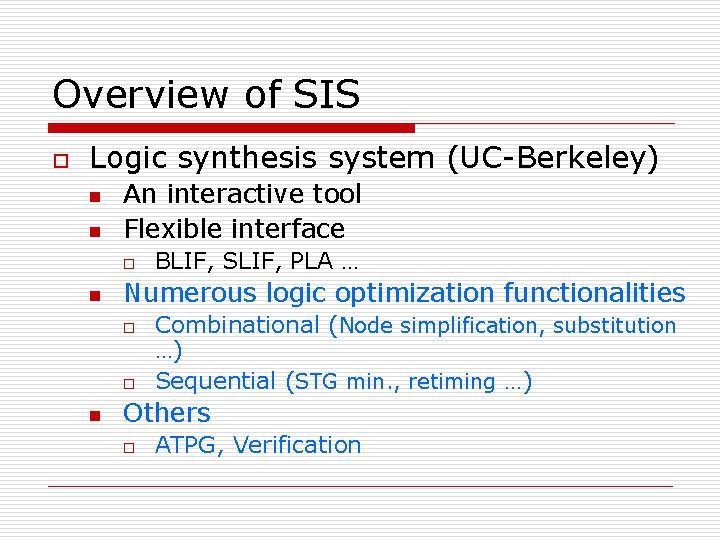

Overview of SIS o Logic synthesis system (UC-Berkeley) n n An interactive tool Flexible interface o n Numerous logic optimization functionalities o o n BLIF, SLIF, PLA … Combinational (Node simplification, substitution …) Sequential (STG min. , retiming …) Others o ATPG, Verification

How to Run SIS? o Read/write files n n o Run scripts n o sis> source script. optimize Exit n o sis> read_blif C 499. blif sis> write_blif C 499_new. blif sis> quit Help n sis> help

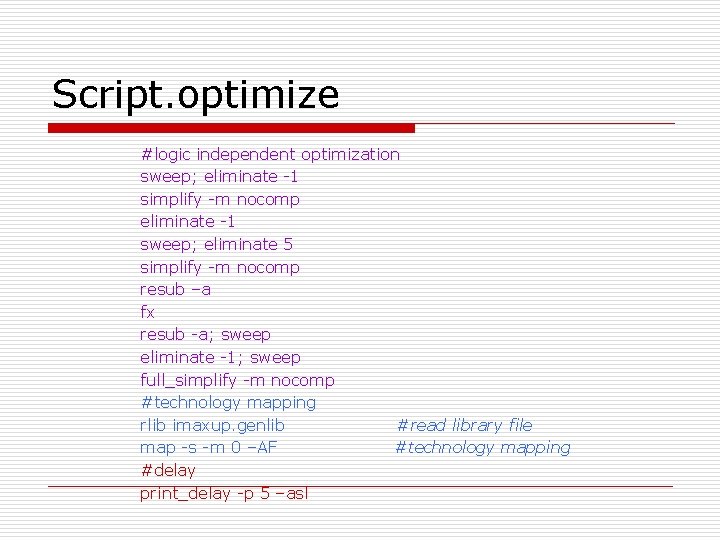

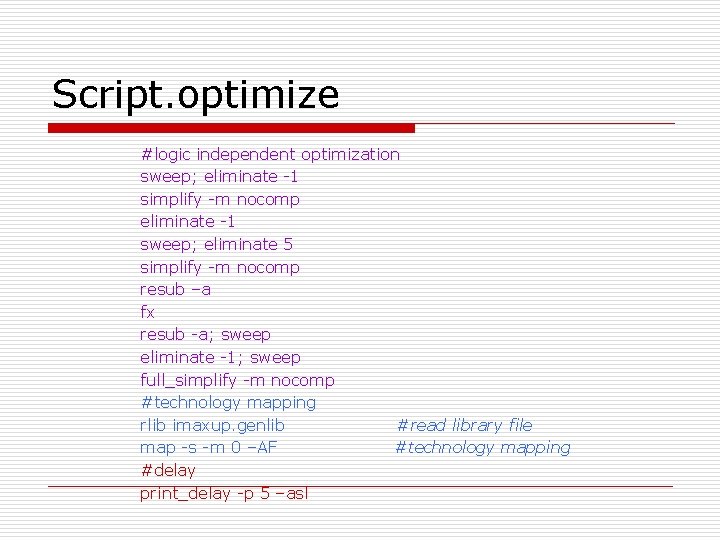

Script. optimize #logic independent optimization sweep; eliminate -1 simplify -m nocomp eliminate -1 sweep; eliminate 5 simplify -m nocomp resub –a fx resub -a; sweep eliminate -1; sweep full_simplify -m nocomp #technology mapping rlib imaxup. genlib #read library file map -s -m 0 –AF #technology mapping #delay print_delay -p 5 –asl

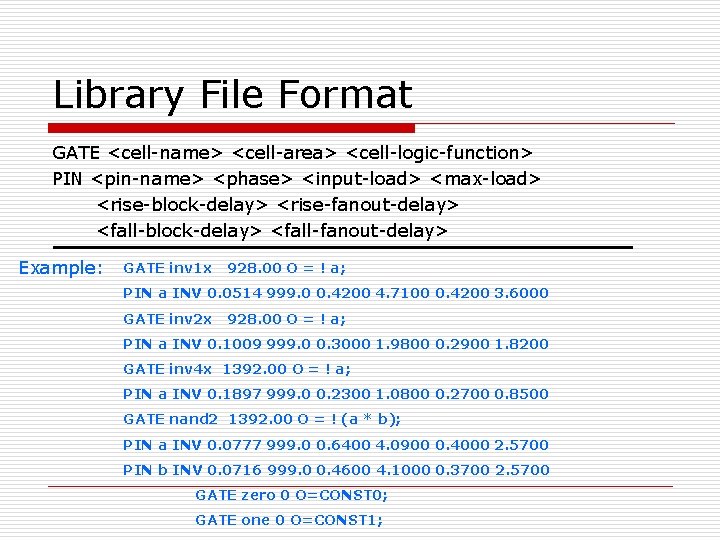

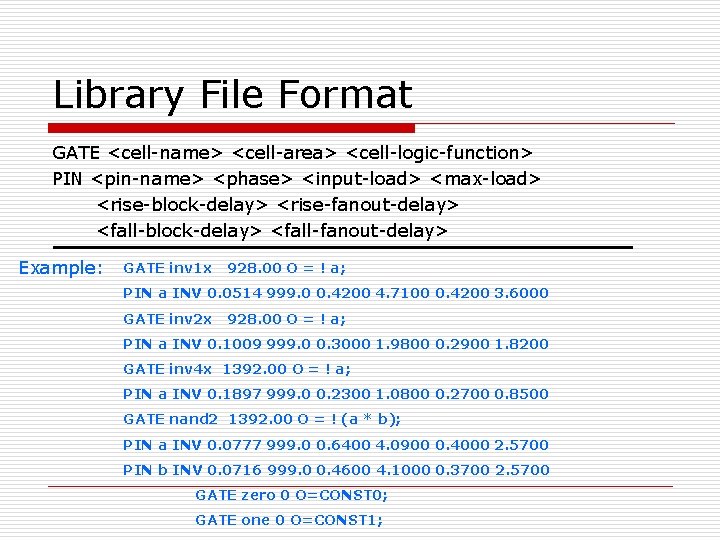

Library File Format GATE <cell-name> <cell-area> <cell-logic-function> PIN <pin-name> <phase> <input-load> <max-load> <rise-block-delay> <rise-fanout-delay> <fall-block-delay> <fall-fanout-delay> Example: GATE inv 1 x 928. 00 O = ! a; PIN a INV 0. 0514 999. 0 0. 4200 4. 7100 0. 4200 3. 6000 GATE inv 2 x 928. 00 O = ! a; PIN a INV 0. 1009 999. 0 0. 3000 1. 9800 0. 2900 1. 8200 GATE inv 4 x 1392. 00 O = ! a; PIN a INV 0. 1897 999. 0 0. 2300 1. 0800 0. 2700 0. 8500 GATE nand 2 1392. 00 O = ! (a * b); PIN a INV 0. 0777 999. 0 0. 6400 4. 0900 0. 4000 2. 5700 PIN b INV 0. 0716 999. 0 0. 4600 4. 1000 0. 3700 2. 5700 GATE zero 0 O=CONST 0; GATE one 0 O=CONST 1;

How to integrate new function? /* init_RTL() * * initialize RTL estimation package */ void init_RTL(void) { com_add_command("write_verilog", com_write_verilog, 1); } /* end_RTL() * * destructor of RTL estimation package */ void end_RTL(void) {} /* com_write_verilog() * * Write the circuit into structural verilog code (either gate-level * or circuit level) */ int com_write_verilog(network_t **network, int argc, char **argv) { } /* file: sis/main/sis_init. c */ void init_sis(graphics_flag) int graphics_flag; { … init_RTL(); /* init for RTL estimation */ } end_sis(){ …; end_RTL(); }

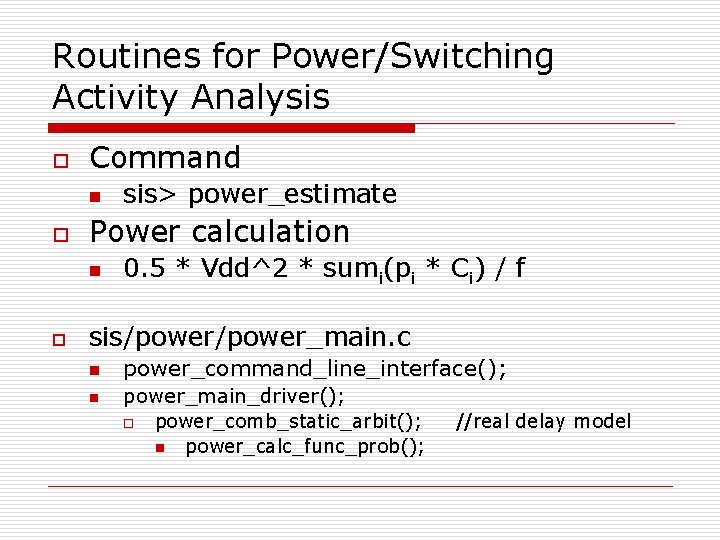

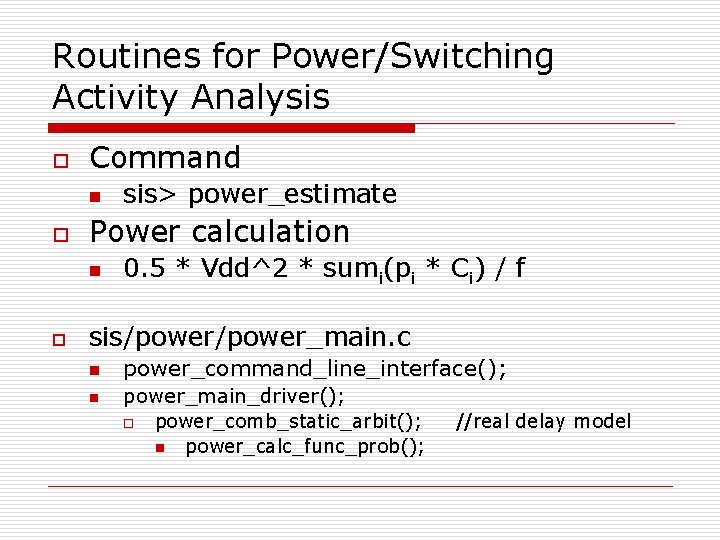

Routines for Power/Switching Activity Analysis o Command n o Power calculation n o sis> power_estimate 0. 5 * Vdd^2 * sumi(pi * Ci) / f sis/power_main. c n power_command_line_interface(); n power_main_driver(); o power_comb_static_arbit(); n power_calc_func_prob(); //real delay model