TUTORIAL DIGITAL ONTOP Alberto Stabile CONVENTIONAL FLOW 1

TUTORIAL: DIGITAL -ON-TOP Alberto Stabile

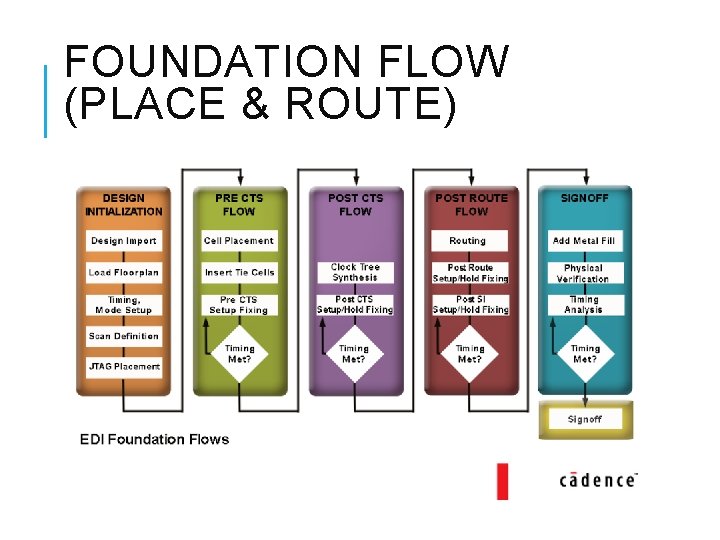

CONVENTIONAL FLOW 1. Write a behavioral design (VDHL or Verilog) 2. Set-up of input files for the synthesis 3. Synthesis (generation of RTL Verilog) 4. Set-up of input files for the P&R Encounter floorplan (requires a lot of time depending on the complexity of design) Liberty files from analog block (to describe timing arc and power consumption) LEF file from analog block (to describe the layout geometries) 5. Foundation Flow in Encounter See next slide

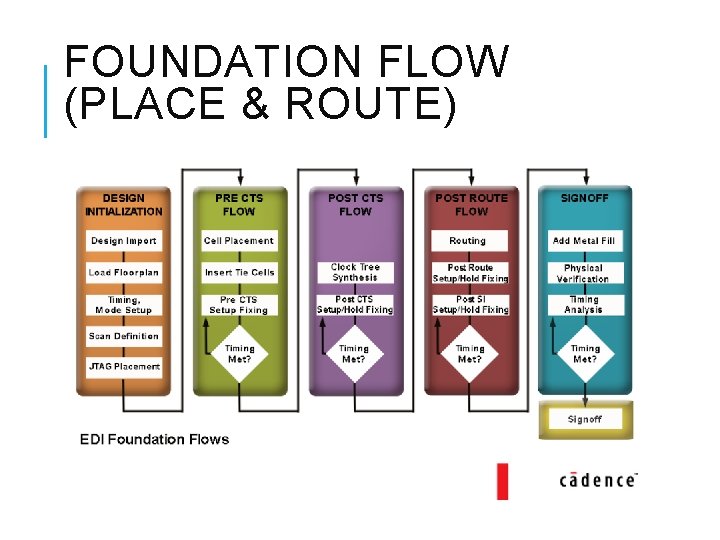

FOUNDATION FLOW (PLACE & ROUTE)

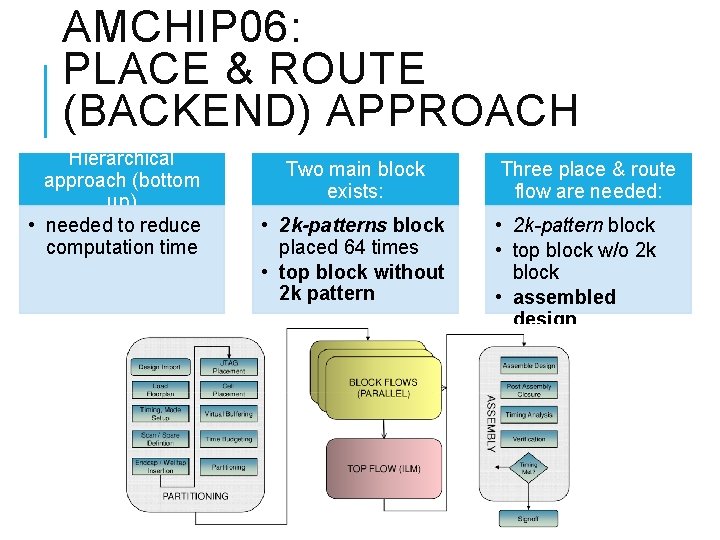

AMCHIP 06: PLACE & ROUTE (BACKEND) APPROACH Hierarchical approach (bottom up) • needed to reduce computation time Two main block exists: • 2 k-patterns block placed 64 times • top block without 2 k pattern Three place & route flow are needed: • 2 k-pattern block • top block w/o 2 k block • assembled design

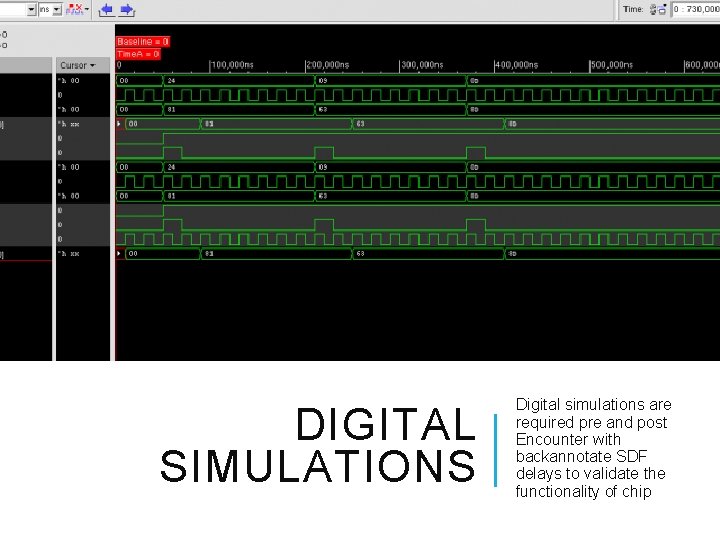

DIGITAL SIMULATIONS Digital simulations are required pre and post Encounter with backannotate SDF delays to validate the functionality of chip

SIGNOFF VERIFICATION Timing MUST be improved with Tempus IR drop must be check with Voltus Verify. Connectivity and Verify. Geometries are two useful function to check the final layout LVS & DRC must be runned with Virtuoso

STRONG APPROACH Repetitive block design by hand Complex logic or timing design with automatic systems

SYNTHESIS EXAMPLE WITH RC Alberto Stabile

SET UP THE INPUT FILE 1. First, we have to decide which LEF and LIB file use of the technology The chose is not simple because there a large number of option (for more detail please ask off-line) 2. Create a tcl file (a script) to use for the synthesis Here we have to create «pointers» to the technologies files (LIB and LEF) and also, if we have, our LIB & LEF files.

LAB EXERCISE Please connect to our account on olorin. fisica. unimi. it via VNC We have different VNC Navigate on Front. End folder Open the file named run_synthesis_with. Rc. tcl

SYNOPYS DESIGN CONSTRAINT FILE It is a standard to limit the design within same pre-decided constraints. Also used for the FPGA timing A lot of user manual online: http: //www. microsemi. com/document-portal/doc_view/131597 design-constraints-guide

LAB EXERCISE If you run correctly the RC you will have a folder named output* Inside this folder we will check the. sdc and the. v files These files will be used to the P&R

FOUNDATION FLOW A. Stabile

FOUNDATION FLOW (PLACE & ROUTE)

LAB EXERCISE Open encounter and generate all files need to generate the scripts The setup. tcl file is the core of settings Check out the EDI folder Questions?

LAB EXERCISE Run make init Open cadence at the end of init step Start the design of floorplan Questions?

- Slides: 17