Tutorial 1 An Introduction to VerilogA Transitioning from

![Parameters • Example: Parameter real gain = 1 from [1: 1000]; • Second keyword Parameters • Example: Parameter real gain = 1 from [1: 1000]; • Second keyword](https://slidetodoc.com/presentation_image/c4673d8dfe5d72b648af48996c41ae8a/image-5.jpg)

- Slides: 20

Tutorial 1 An Introduction to Verilog-A: Transitioning from Verilog

Lesson Plan (Tentative) • Week 1: Transitioning from VHDL to Verilog, Introduction to Cryptography • Week 2: A 5 Cipher Implementaion, Transitioning from Verilog to Verilog-A • Week 3: Verilog-A Mixer Analysis

Analog Verilog (Verilog-AMS) • Verilog introduced as IEEE Standard 1364 • Dire need for analog circuits to be modelled as a language • VHDL and Verilog come up with analog equivalents: AHDL and Verilog-AMS (Analog and Mixed Signal)

New Types in Verilog-A • • Integer/Real (same as Verilog) Electrical (electrical wire) Parameter (parameter constants) Genvar (local variables eg for loops and such)

![Parameters Example Parameter real gain 1 from 1 1000 Second keyword Parameters • Example: Parameter real gain = 1 from [1: 1000]; • Second keyword](https://slidetodoc.com/presentation_image/c4673d8dfe5d72b648af48996c41ae8a/image-5.jpg)

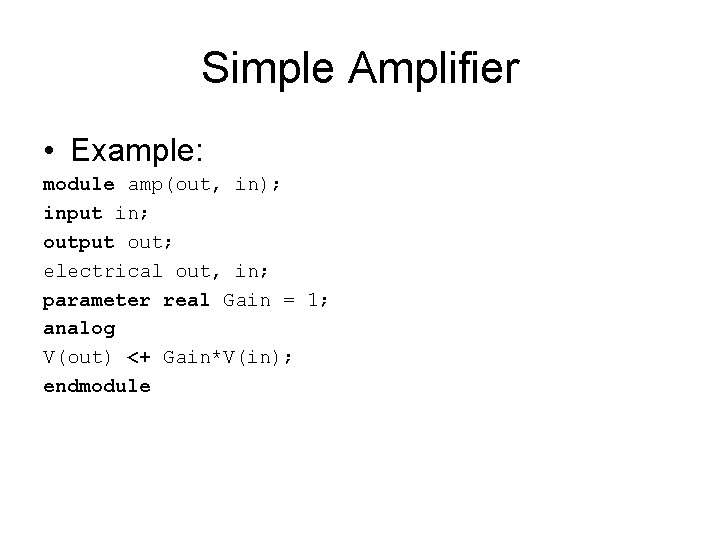

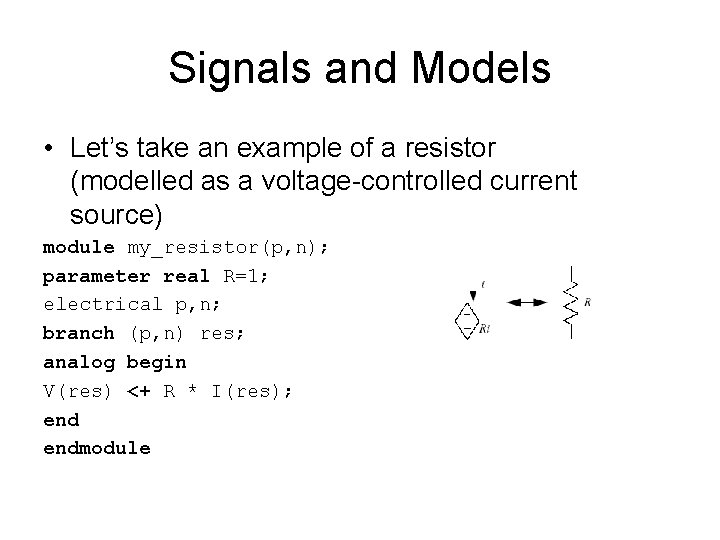

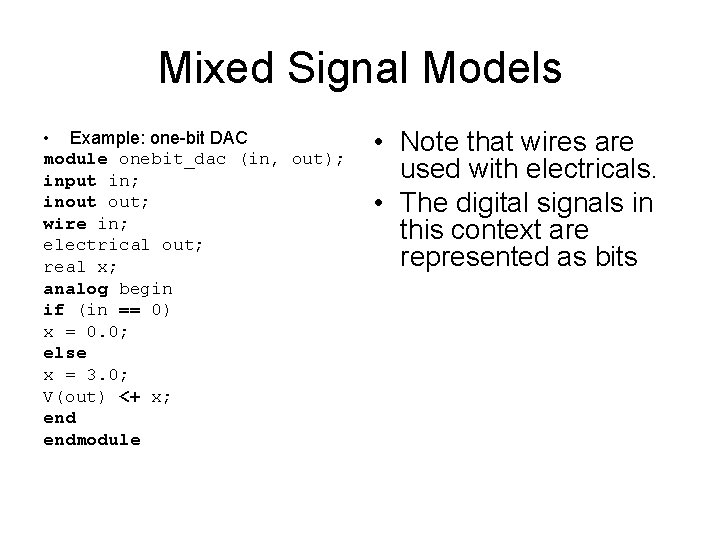

Parameters • Example: Parameter real gain = 1 from [1: 1000]; • Second keyword real specifies optional type (real or integer) • From is used to specifies optional range of the parameter. [] is used to indicate that the end values are allowable while () means end values are not.

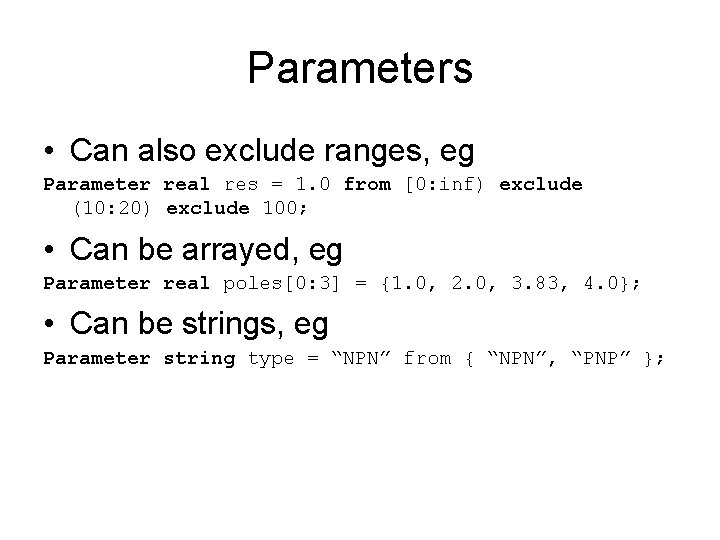

Parameters • Parameters cannot be changed at run time, but can be changed at compile time using defparam • Example: module annotate; defparam tgate. m 1. gate_width = 5 e-6, tgate. m 2. gate_width = 10 e-6; endmodule

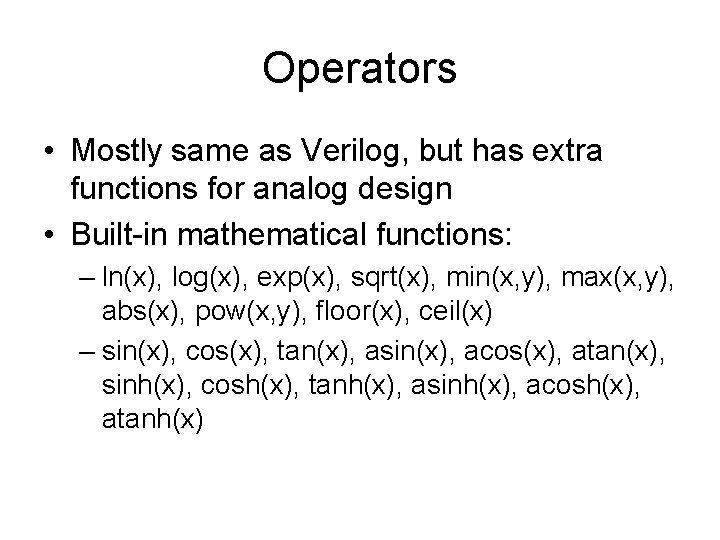

Parameters • Can also exclude ranges, eg Parameter real res = 1. 0 from [0: inf) exclude (10: 20) exclude 100; • Can be arrayed, eg Parameter real poles[0: 3] = {1. 0, 2. 0, 3. 83, 4. 0}; • Can be strings, eg Parameter string type = “NPN” from { “NPN”, “PNP” };

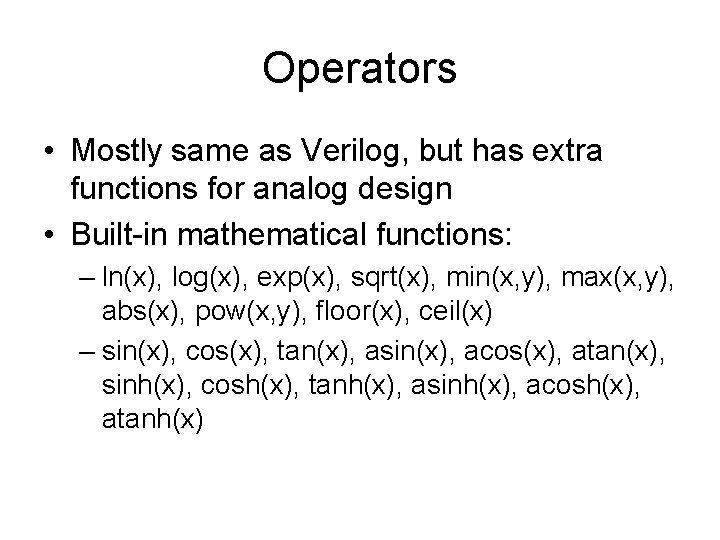

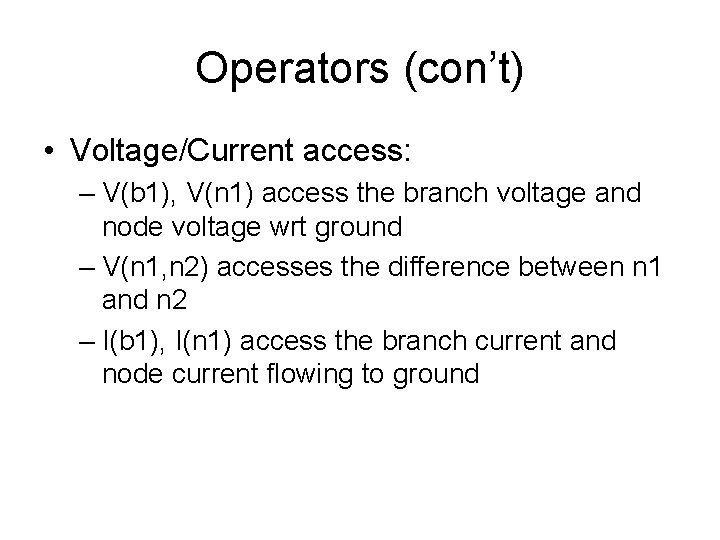

Operators • Mostly same as Verilog, but has extra functions for analog design • Built-in mathematical functions: – ln(x), log(x), exp(x), sqrt(x), min(x, y), max(x, y), abs(x), pow(x, y), floor(x), ceil(x) – sin(x), cos(x), tan(x), asin(x), acos(x), atan(x), sinh(x), cosh(x), tanh(x), asinh(x), acosh(x), atanh(x)

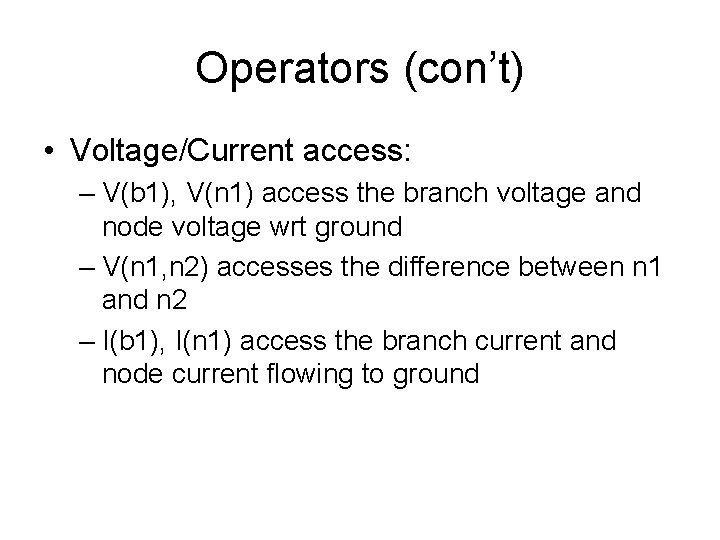

Operators (con’t) • Voltage/Current access: – V(b 1), V(n 1) access the branch voltage and node voltage wrt ground – V(n 1, n 2) accesses the difference between n 1 and n 2 – I(b 1), I(n 1) access the branch current and node current flowing to ground

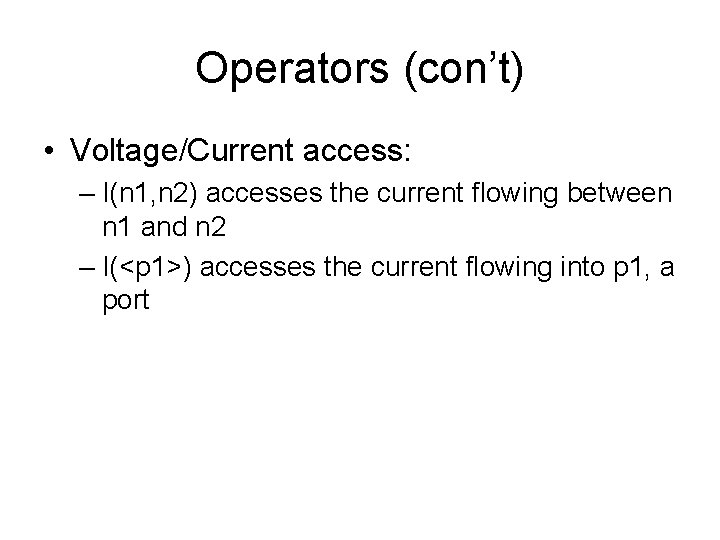

Operators (con’t) • Voltage/Current access: – I(n 1, n 2) accesses the current flowing between n 1 and n 2 – I(<p 1>) accesses the current flowing into p 1, a port

Analog Operators (Filters) • Cannot be placed in any loop or conditional (for, while, if, case, repeat) because internal state must be maintained • Only in an analog block • Argument list cannot be null

Analog Operators • ddt(x), calculates the time derivative of x • idt(x, opt_ic), calculates the time integral of x (with or without initial condition) • laplace_zp, laplace_zd, laplace_np, laplace_nd (various laplace transforms)

Analog Operators • Analysis types – Analysis() returns true(1) if analysis done is of that type (AC, DC, tran, noise, etc) • Noise models – Can use white_noise, flicker_noise, noise_table

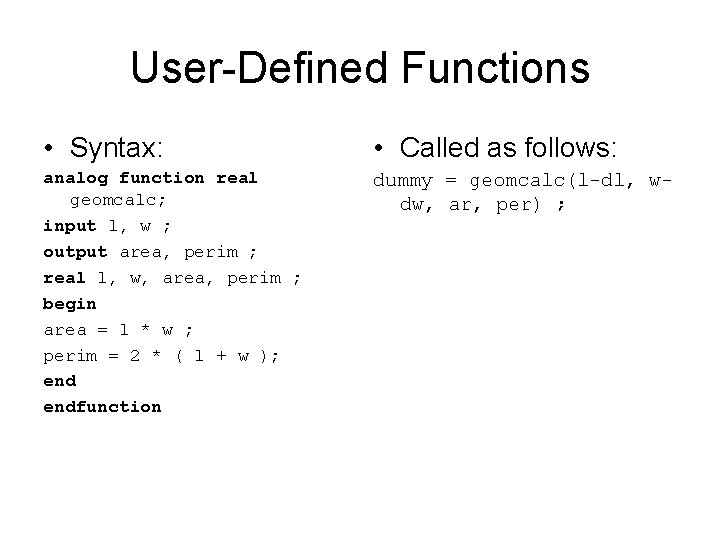

User-Defined Functions • Syntax: • Called as follows: analog function real geomcalc; input l, w ; output area, perim ; real l, w, area, perim ; begin area = l * w ; perim = 2 * ( l + w ); endfunction dummy = geomcalc(l-dl, wdw, ar, per) ;

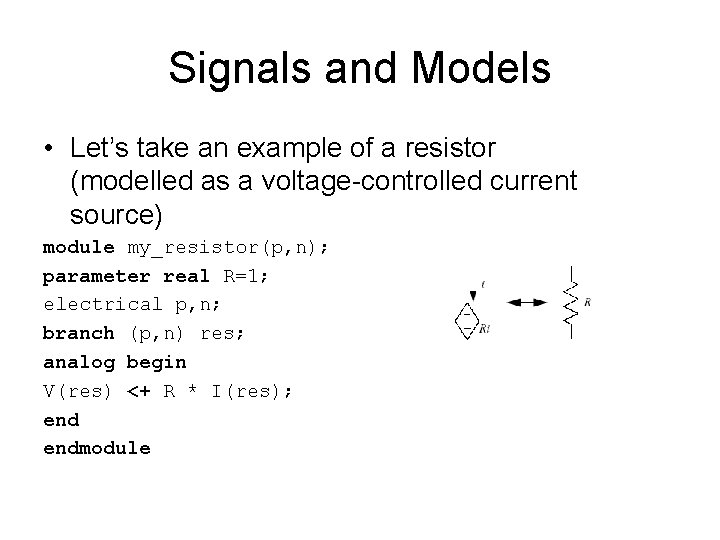

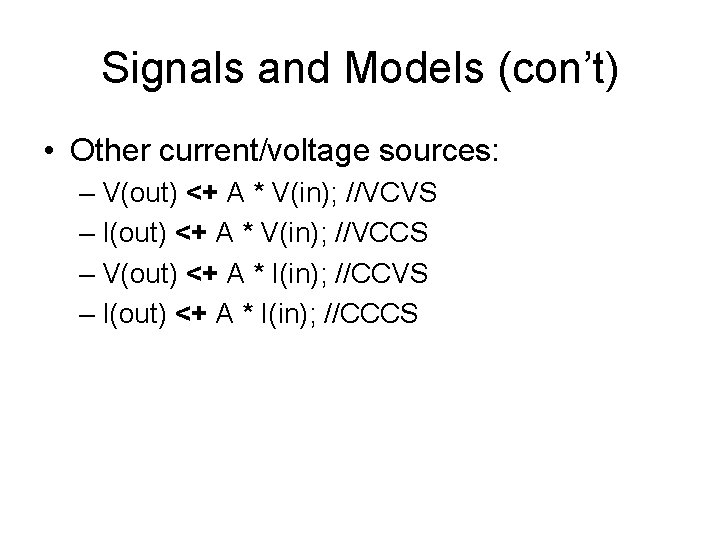

Signals and Models • Let’s take an example of a resistor (modelled as a voltage-controlled current source) module my_resistor(p, n); parameter real R=1; electrical p, n; branch (p, n) res; analog begin V(res) <+ R * I(res); endmodule

Signals and Models (con’t) • Other current/voltage sources: – V(out) <+ A * V(in); //VCVS – I(out) <+ A * V(in); //VCCS – V(out) <+ A * I(in); //CCVS – I(out) <+ A * I(in); //CCCS

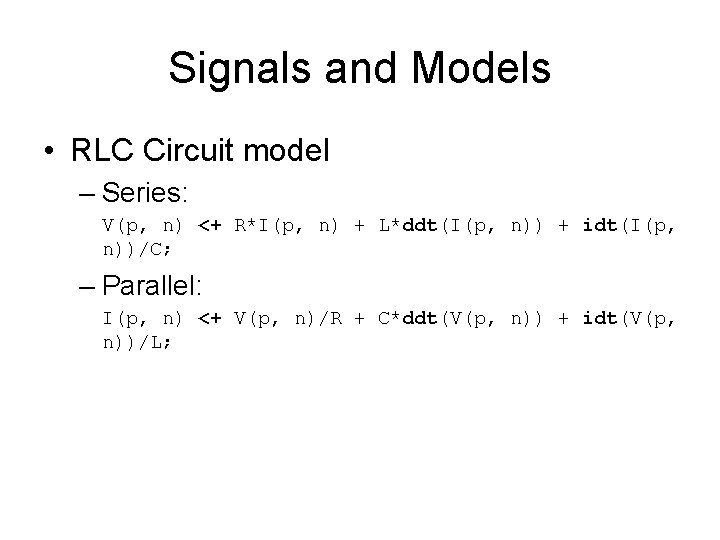

Signals and Models • RLC Circuit model – Series: V(p, n) <+ R*I(p, n) + L*ddt(I(p, n)) + idt(I(p, n))/C; – Parallel: I(p, n) <+ V(p, n)/R + C*ddt(V(p, n)) + idt(V(p, n))/L;

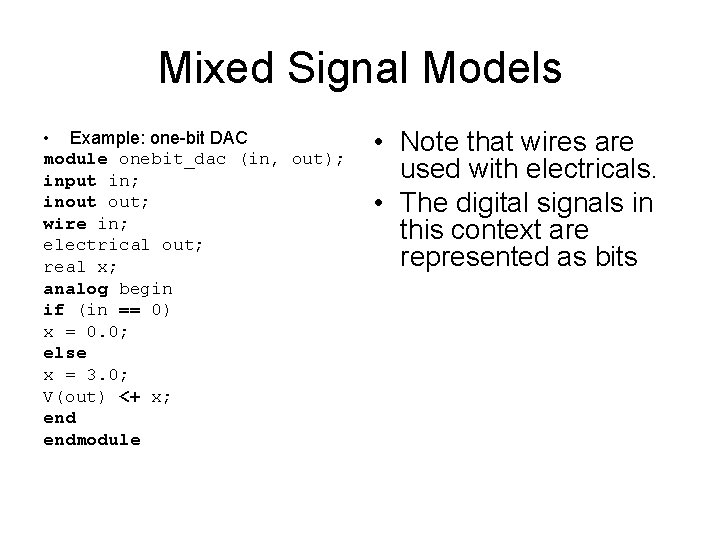

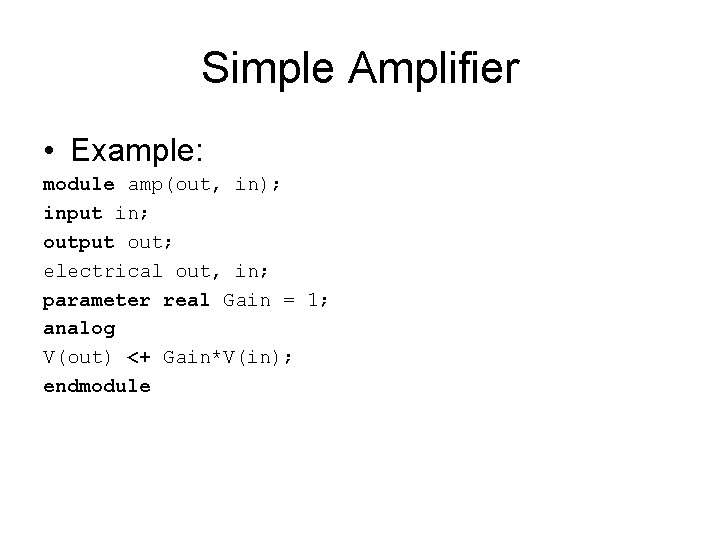

Simple Amplifier • Example: module amp(out, in); input in; output out; electrical out, in; parameter real Gain = 1; analog V(out) <+ Gain*V(in); endmodule

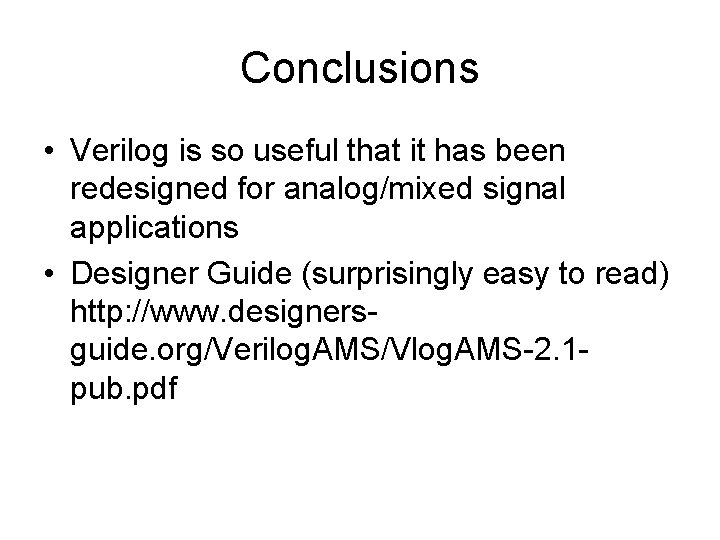

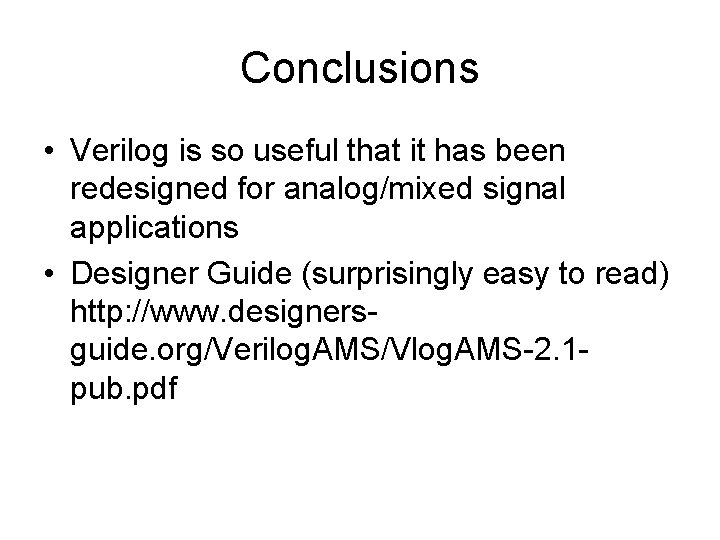

Mixed Signal Models • Example: one-bit DAC module onebit_dac (in, out); input in; inout out; wire in; electrical out; real x; analog begin if (in == 0) x = 0. 0; else x = 3. 0; V(out) <+ x; endmodule • Note that wires are used with electricals. • The digital signals in this context are represented as bits

Conclusions • Verilog is so useful that it has been redesigned for analog/mixed signal applications • Designer Guide (surprisingly easy to read) http: //www. designersguide. org/Verilog. AMS/Vlog. AMS-2. 1 pub. pdf