TSMC Open Innovation Platform Ecosystem Forum 2012 Design

- Slides: 15

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Design Methodology for Silicon-Accurate Jitter Analysis for 28 nm Interface IP for 100 GBASE-LR 4 Applications Alan Rogers - Analog Bits Nandu Bhagwan – GHz Circuits, Inc Ravi Subramanian - Berkeley Design Automation October 16, 2012 © 2012 Berkeley Design Automation and Analog Bits Space for affiliation logo 1

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Introduction • Presenting verification results of Integer-N PLL IP • Three way collaboration between: – Analog Bits: 28 nm IP macro for 100 Gigabit Ethernet – TSMC: Reference flow development and 28 nm process – BDA: Device Noise Analysis in the AFS Platform © 2012 Berkeley Design Automation and Analog Bits 2

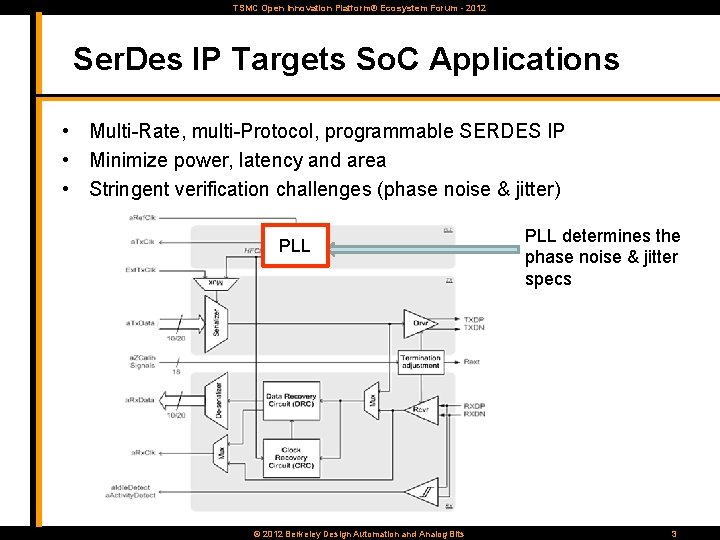

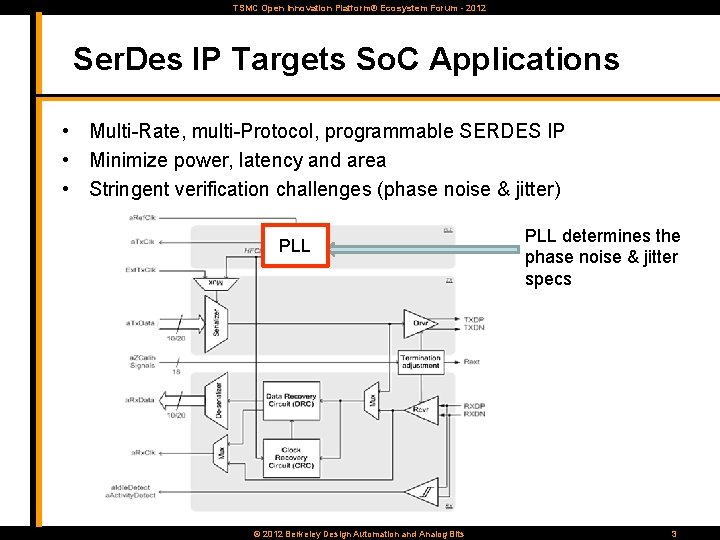

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Ser. Des IP Targets So. C Applications • Multi-Rate, multi-Protocol, programmable SERDES IP • Minimize power, latency and area • Stringent verification challenges (phase noise & jitter) PLL © 2012 Berkeley Design Automation and Analog Bits PLL determines the phase noise & jitter specs 3

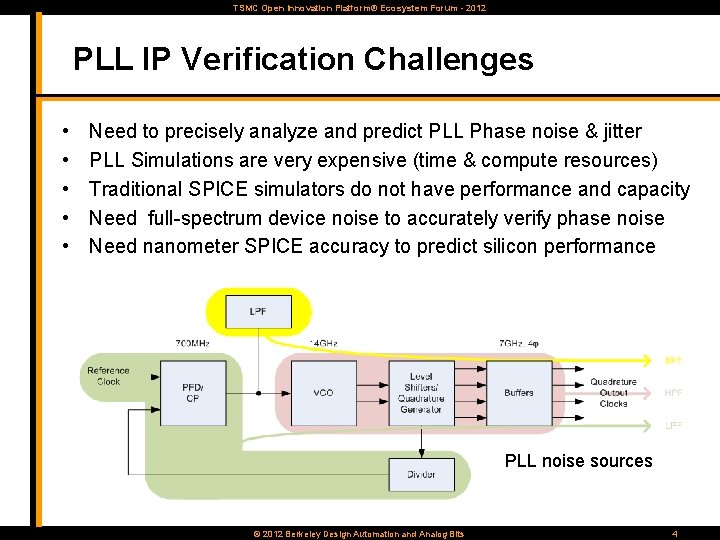

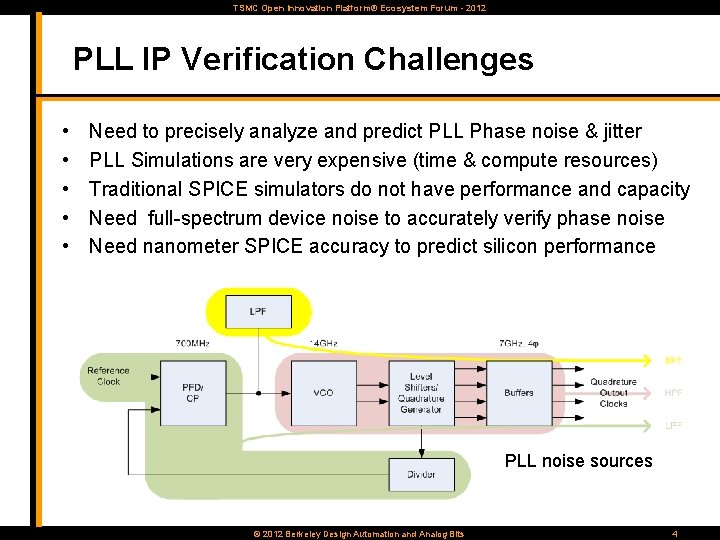

TSMC Open Innovation Platform® Ecosystem Forum - 2012 PLL IP Verification Challenges • • • Need to precisely analyze and predict PLL Phase noise & jitter PLL Simulations are very expensive (time & compute resources) Traditional SPICE simulators do not have performance and capacity Need full-spectrum device noise to accurately verify phase noise Need nanometer SPICE accuracy to predict silicon performance PLL noise sources © 2012 Berkeley Design Automation and Analog Bits 4

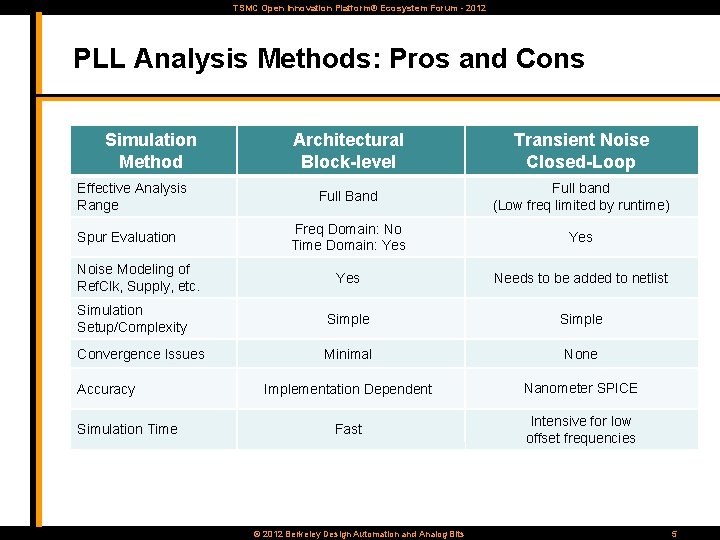

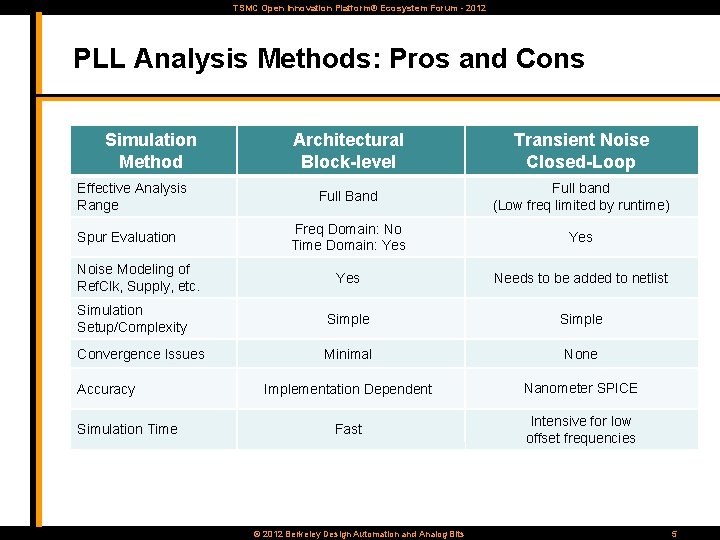

TSMC Open Innovation Platform® Ecosystem Forum - 2012 PLL Analysis Methods: Pros and Cons Simulation Method Architectural Block-level Transient Noise Closed-Loop Full Band Full band (Low freq limited by runtime) Freq Domain: No Time Domain: Yes Yes Needs to be added to netlist Simulation Setup/Complexity Simple Convergence Issues Minimal None Implementation Dependent Nanometer SPICE Fast Intensive for low offset frequencies Effective Analysis Range Spur Evaluation Noise Modeling of Ref. Clk, Supply, etc. Accuracy Simulation Time © 2012 Berkeley Design Automation and Analog Bits 5

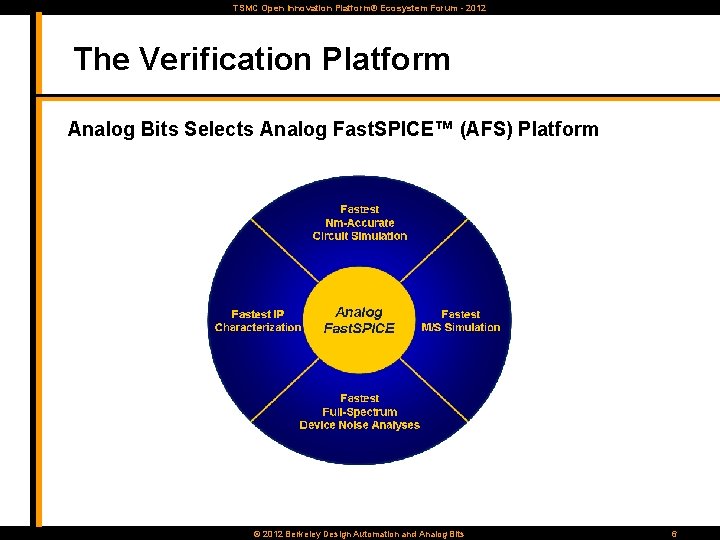

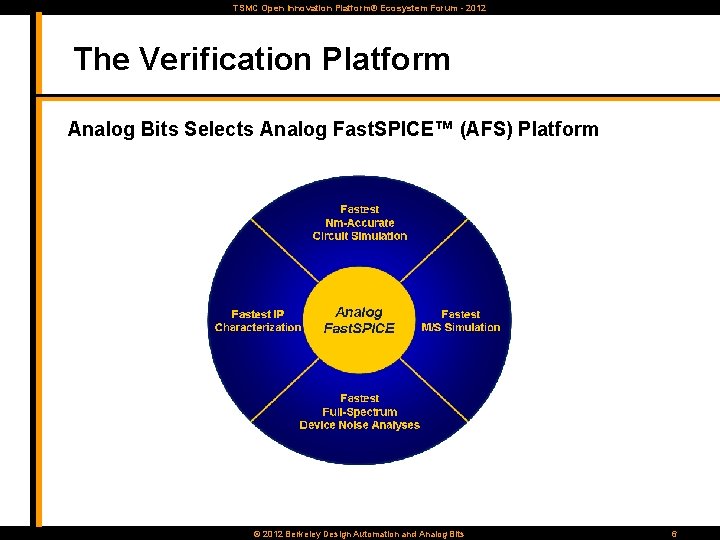

TSMC Open Innovation Platform® Ecosystem Forum - 2012 The Verification Platform Analog Bits Selects Analog Fast. SPICE™ (AFS) Platform © 2012 Berkeley Design Automation and Analog Bits 6

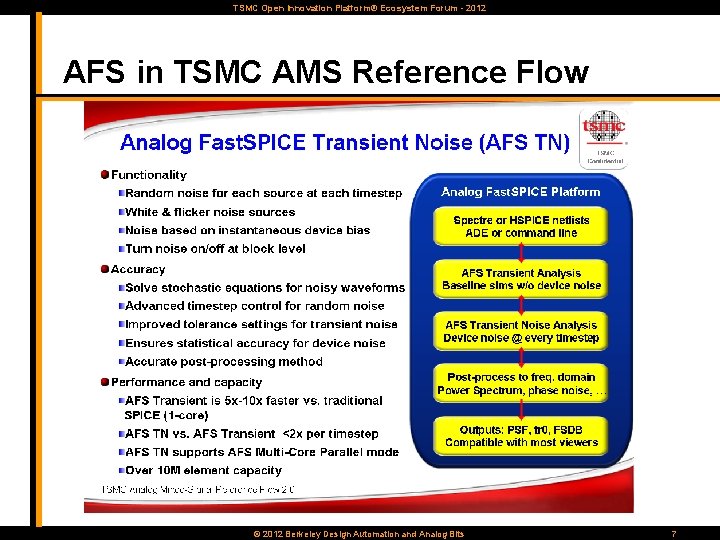

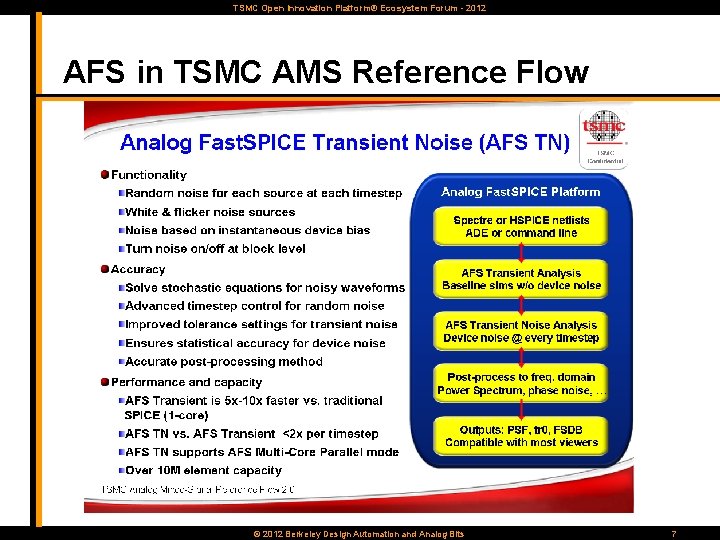

TSMC Open Innovation Platform® Ecosystem Forum - 2012 AFS in TSMC AMS Reference Flow © 2012 Berkeley Design Automation and Analog Bits 7

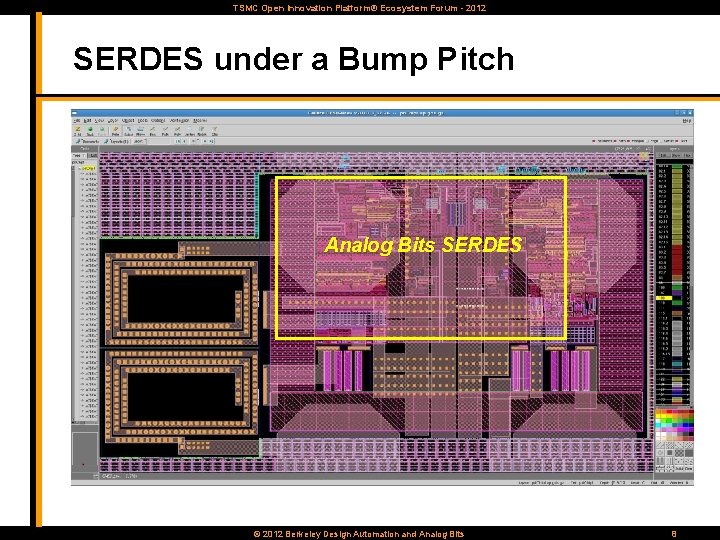

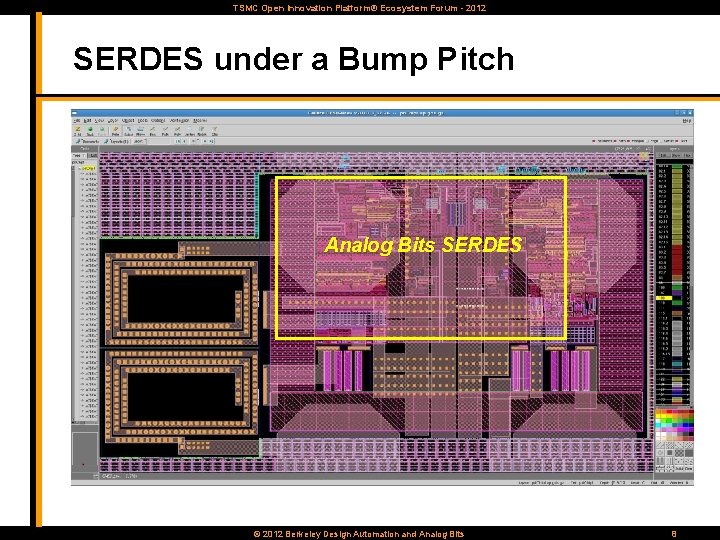

TSMC Open Innovation Platform® Ecosystem Forum - 2012 SERDES under a Bump Pitch Analog Bits SERDES © 2012 Berkeley Design Automation and Analog Bits 8

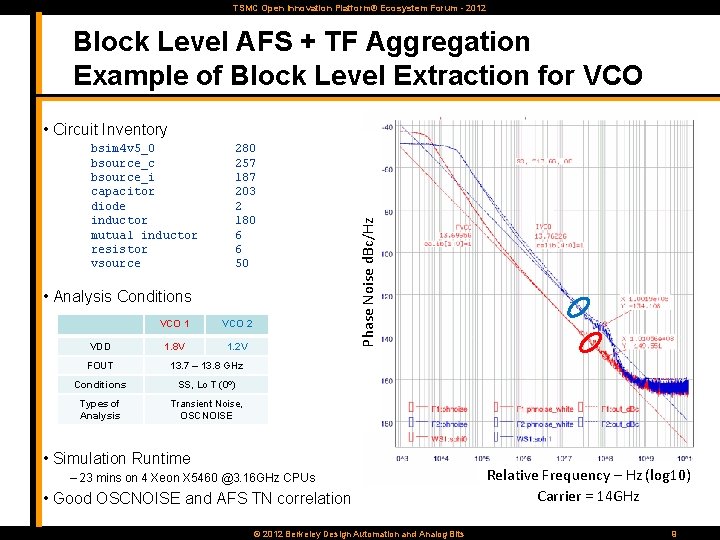

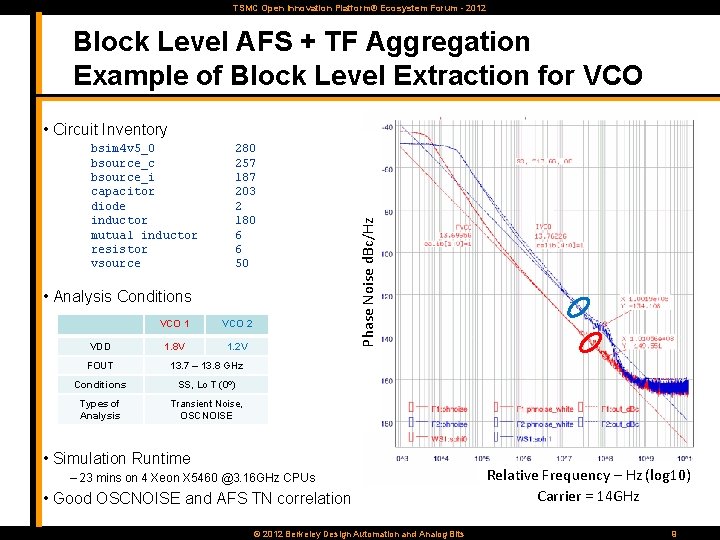

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Block Level AFS + TF Aggregation Example of Block Level Extraction for VCO bsim 4 v 5_0 bsource_c bsource_i capacitor diode inductor mutual inductor resistor vsource 280 257 187 203 2 180 6 6 50 • Analysis Conditions VDD VCO 1 VCO 2 1. 8 V 1. 2 V FOUT 13. 7 – 13. 8 GHz Conditions SS, Lo T (0º) Types of Analysis Transient Noise, OSCNOISE Phase Noise d. Bc/Hz • Circuit Inventory • Simulation Runtime – 23 mins on 4 Xeon X 5460 @3. 16 GHz CPUs • Good OSCNOISE and AFS TN correlation © 2012 Berkeley Design Automation and Analog Bits Relative Frequency – Hz (log 10) Carrier = 14 GHz 9

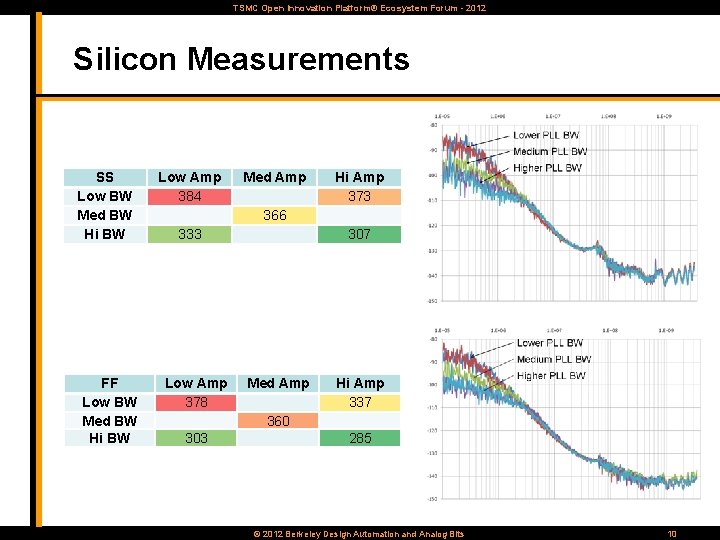

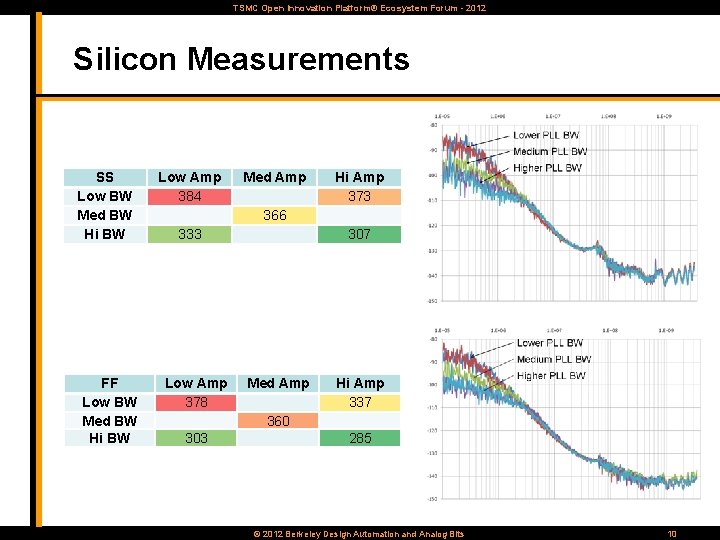

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Silicon Measurements SS Low BW Med BW Hi BW FF Low BW Med BW Hi BW Low Amp 384 Med Amp Hi Amp 373 366 333 Low Amp 378 307 Med Amp Hi Amp 337 360 303 285 © 2012 Berkeley Design Automation and Analog Bits 10

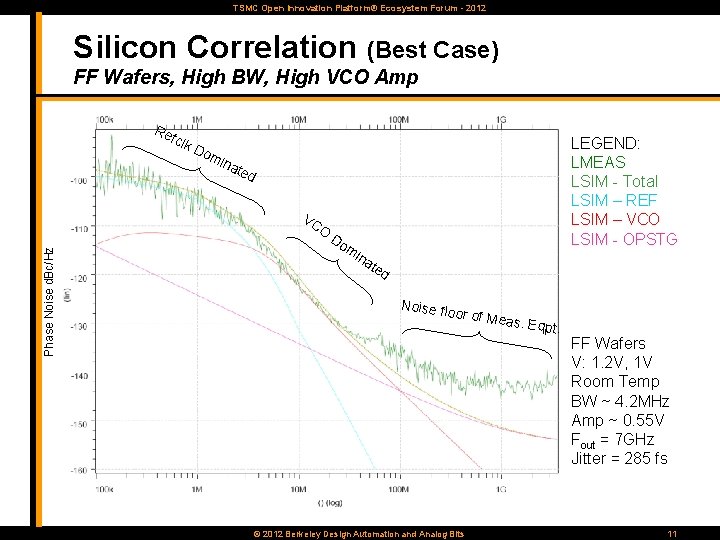

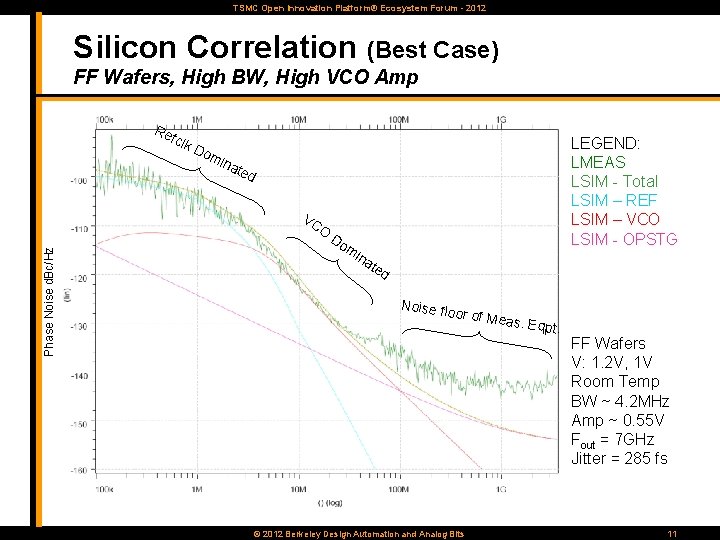

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Silicon Correlation (Best Case) FF Wafers, High BW, High VCO Amp Re fclk Do min ate d VC O Phase Noise d. Bc/Hz LEGEND: LMEAS LSIM - Total LSIM – REF LSIM – VCO LSIM - OPSTG Do mi na ted Noise flo or of Me a © 2012 Berkeley Design Automation and Analog Bits s. Eqpt. FF Wafers V: 1. 2 V, 1 V Room Temp BW ~ 4. 2 MHz Amp ~ 0. 55 V Fout = 7 GHz Jitter = 285 fs 11

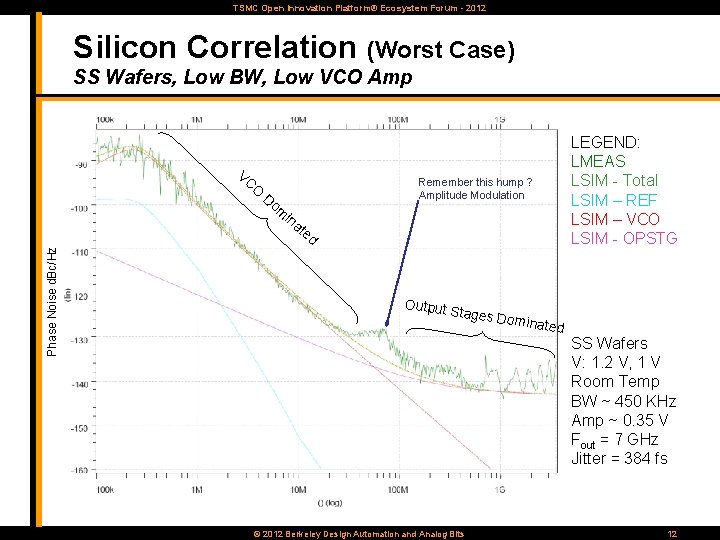

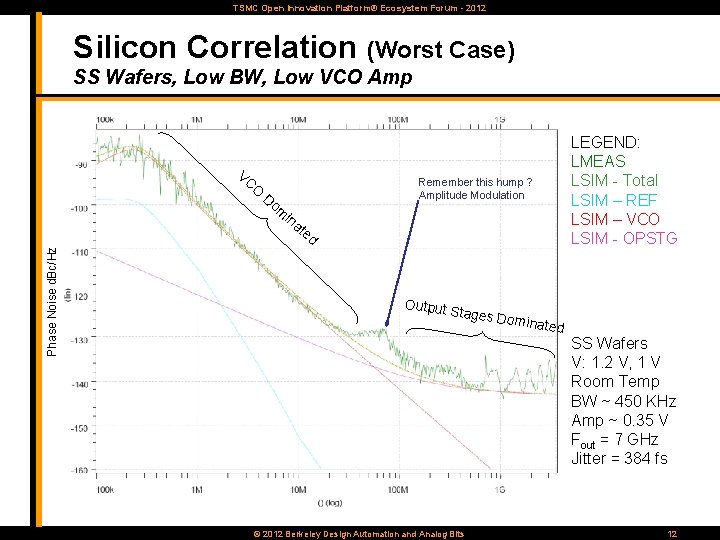

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Silicon Correlation (Worst Case) SS Wafers, Low BW, Low VCO Amp VC O Do LEGEND: LMEAS LSIM - Total LSIM – REF LSIM – VCO LSIM - OPSTG Remember this hump ? Amplitude Modulation m in at Phase Noise d. Bc/Hz ed Output S tages D © 2012 Berkeley Design Automation and Analog Bits ominate d SS Wafers V: 1. 2 V, 1 V Room Temp BW ~ 450 KHz Amp ~ 0. 35 V Fout = 7 GHz Jitter = 384 fs 12

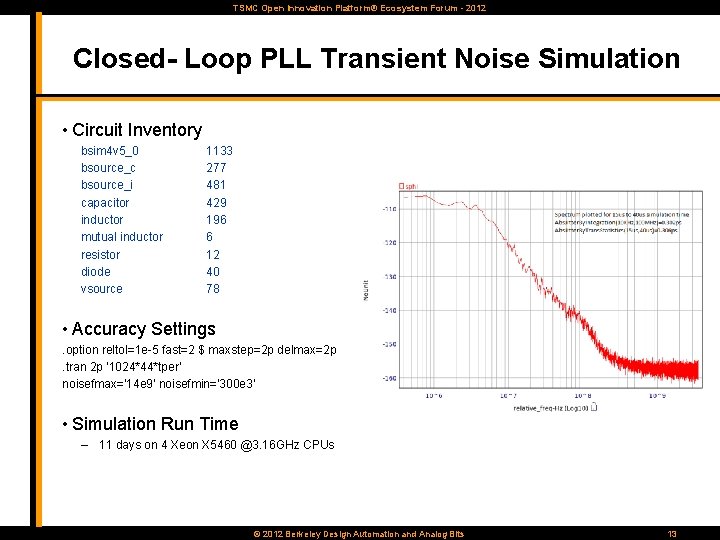

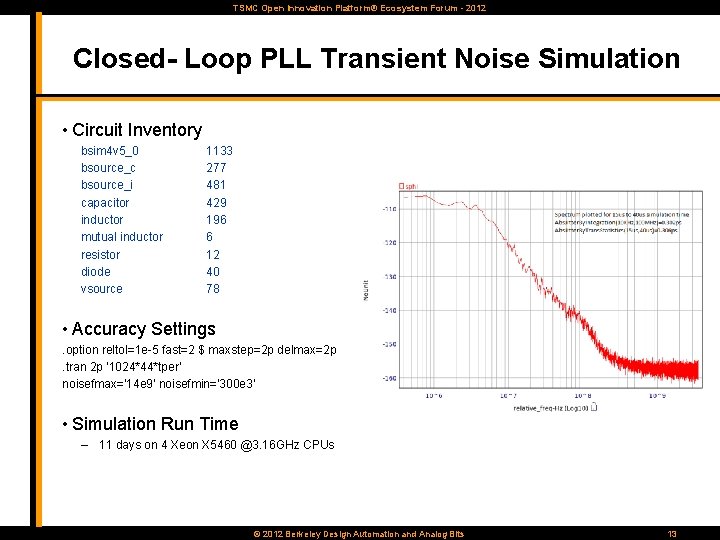

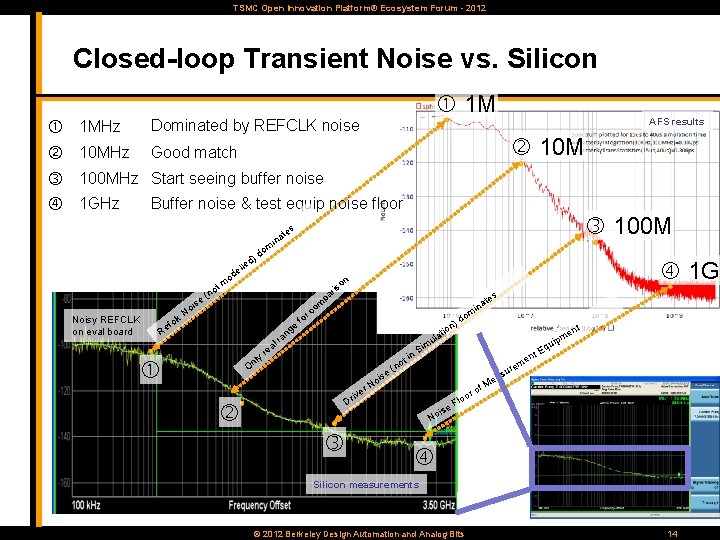

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Closed- Loop PLL Transient Noise Simulation • Circuit Inventory bsim 4 v 5_0 bsource_c bsource_i capacitor inductor mutual inductor resistor diode vsource 1133 277 481 429 196 6 12 40 78 • Accuracy Settings. option reltol=1 e-5 fast=2 $ maxstep=2 p delmax=2 p. tran 2 p '1024*44*tper' noisefmax='14 e 9' noisefmin='300 e 3’ • Simulation Run Time – 11 days on 4 Xeon X 5460 @3. 16 GHz CPUs © 2012 Berkeley Design Automation and Analog Bits 13

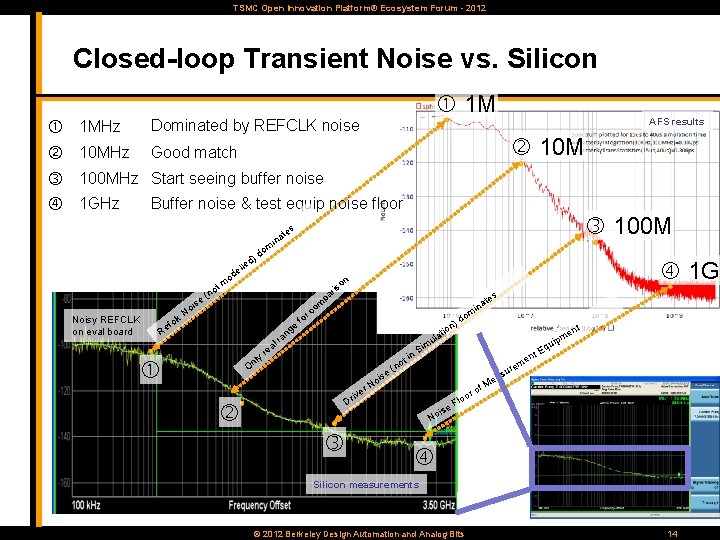

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Closed-loop Transient Noise vs. Silicon 1 MHz Dominated by REFCLK noise 10 MHz Good match AFS results 10 M 100 MHz Start seeing buffer noise 1 GHz Buffer noise & test equip noise floor om ina 100 M s te d d) 1 G lle e od Noisy REFCLK on eval board k fcl Re ise No n iso r pa m ot (n ge y nl r fo m co an lr a e r in ot O ) ion t a ul tes na i m do m Si n e( is o r. N ive ise No f ro Dr o Flo t en m e ur as e M t en m uip Eq Silicon measurements © 2012 Berkeley Design Automation and Analog Bits 14

TSMC Open Innovation Platform® Ecosystem Forum - 2012 Conclusion • Lowest jitter PLL with 100 Gbps data transfer rates • Silicon-proven in TSMC’s 28 nm process • Performance characterized with AFS Platform enabling – – – Rapid and accurate block-level and top-level analysis Good simulation-to-silicon correlation Leveraging new full-spectrum device-noise analysis technology Improved analog Ser. Des sign-off flow Increased design productivity and reduced risk • BDA-TSMC Device Noise Analysis Sub-flow provided good results in reasonable run-times © 2012 Berkeley Design Automation and Analog Bits 15