Tript and TFB status Tript schematics Tript operation

Trip-t and TFB status Trip-t schematics Trip-t operation at T 2 K Si. PM connection and gain considerations Latest results from version 2 – the final version TFB conceptual layout interfaces components electronic calibration data volumes plans for this year Mark Raymond - 28/04/06

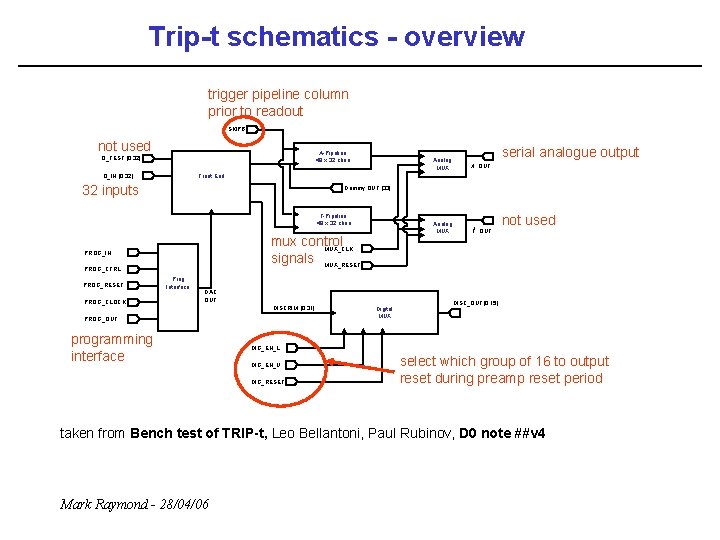

Trip-t schematics - overview trigger pipeline column prior to readout SKIPB not used A-Pipeline 48 x 32 chan Q_TEST [0: 32] 32 inputs Analog MUX t OUT Dummy OUT [33] t-Pipeline 48 x 32 chan mux control MUX_CLK signals MUX_RESET PROG_IN PROG_CTRL PROG_CLOCK A OUT Front End Q_IN [0: 32] PROG_RESET serial analogue output Analog MUX Prog Interface DAC OUT DISCRIM [0: 31] PROG_OUT programming interface Digital MUX not used DISC_OUT[0: 15] DIG_EN_L DIG_EN_U DIG_RESET select which group of 16 to output reset during preamp reset period taken from Bench test of TRIP-t, Leo Bellantoni, Paul Rubinov, D 0 note ##v 4 Mark Raymond - 28/04/06

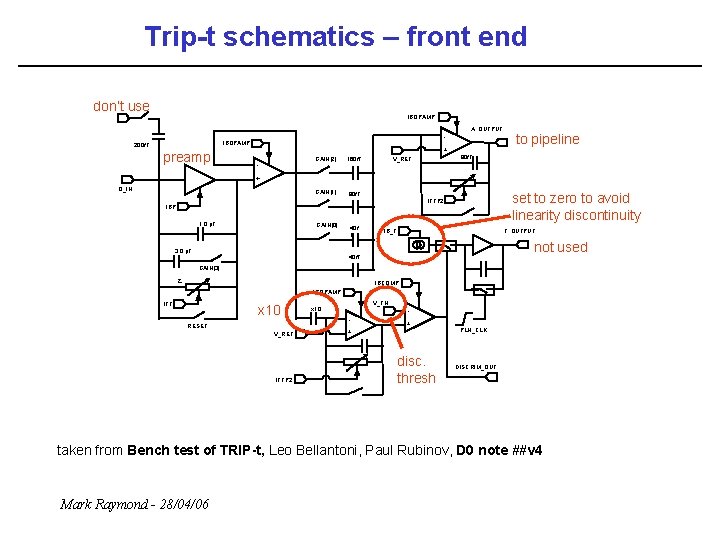

Trip-t schematics – front end don’t use IBOPAMP - IBOPAMP 200 f. F preamp A OUTPUT + - GAIN[2] 160 f. F GAIN[1] 80 f. F to pipeline 80 f. F V_REF + Q_IN 1. 0 p. F GAIN[0] 3. 0 p. F 40 f F set to zero to avoid linearity discontinuity IFFP 2 IBP IB_T t OUTPUT not used 40 f. F GAIN[3] Z IBCOMP IBOPAMP IFF x 10 RESET V_REF IFFP 2 V_TH x 10 - + + disc. thresh PLN_CLK DISCRIM_OUT taken from Bench test of TRIP-t, Leo Bellantoni, Paul Rubinov, D 0 note ##v 4 Mark Raymond - 28/04/06

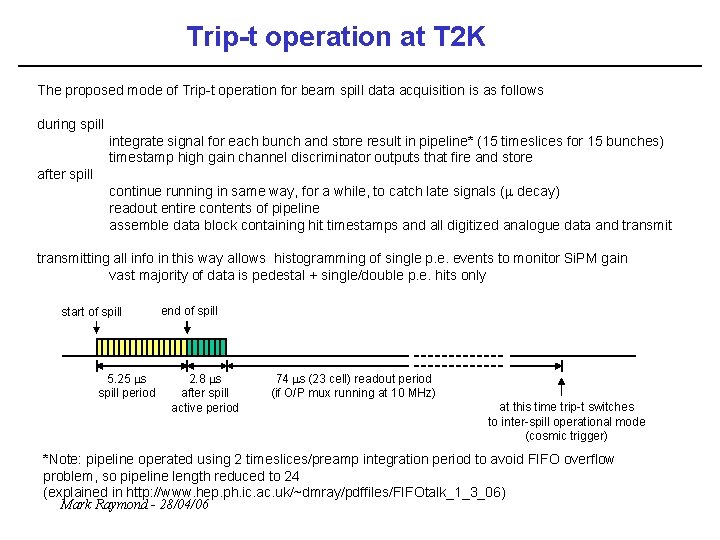

Trip-t operation at T 2 K The proposed mode of Trip-t operation for beam spill data acquisition is as follows during spill integrate signal for each bunch and store result in pipeline* (15 timeslices for 15 bunches) timestamp high gain channel discriminator outputs that fire and store after spill continue running in same way, for a while, to catch late signals (m decay) readout entire contents of pipeline assemble data block containing hit timestamps and all digitized analogue data and transmitting all info in this way allows histogramming of single p. e. events to monitor Si. PM gain vast majority of data is pedestal + single/double p. e. hits only start of spill 5. 25 ms spill period end of spill 2. 8 ms after spill active period 74 ms (23 cell) readout period (if O/P mux running at 10 MHz) at this time trip-t switches to inter-spill operational mode (cosmic trigger) *Note: pipeline operated using 2 timeslices/preamp integration period to avoid FIFO overflow problem, so pipeline length reduced to 24 (explained in http: //www. hep. ph. ic. ac. uk/~dmray/pdffiles/FIFOtalk_1_3_06) Mark Raymond - 28/04/06

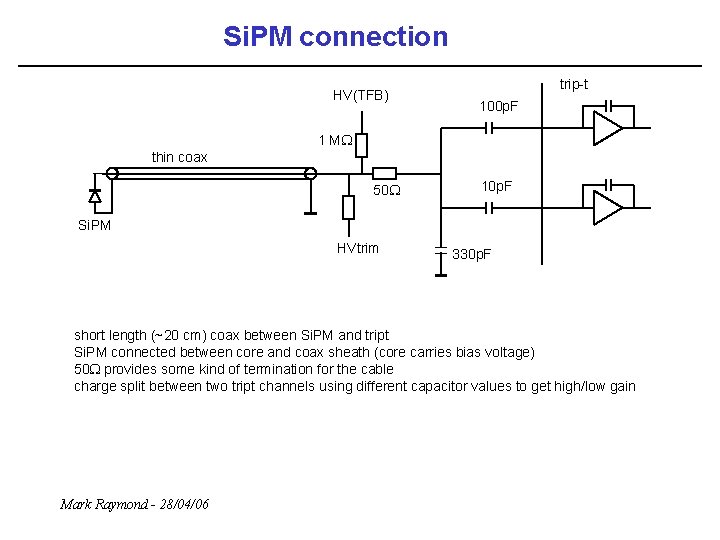

Si. PM connection HV(TFB) trip-t 100 p. F 1 MW thin coax 50 W 10 p. F Si. PM HVtrim 330 p. F short length (~20 cm) coax between Si. PM and tript Si. PM connected between core and coax sheath (core carries bias voltage) 50 W provides some kind of termination for the cable charge split between two tript channels using different capacitor values to get high/low gain Mark Raymond - 28/04/06

Gain considerations don’t know what final Si. PM gain will be, but assume production devices will be quite well matched in any case will have individual channel gain adjustment by HVtrim. DACs Signal shared between Cadd, Chi and Clo (also some strays) Choose Cadd to match final Si. PM gain (330 p. F about right for 5 x 105) Cadd also helps with gain discontinuity when hi gain channel saturates (see http: //www. hep. ph. ic. ac. uk/~dmray/pdffiles/tript_talk_1_3_06) HV(TFB) Chi 100 p. F 1 MW thin coax 50 W Clo 10 p. F Si. PM HVtrim Mark Raymond - 28/04/06 Cadd 330 p. F trip-t

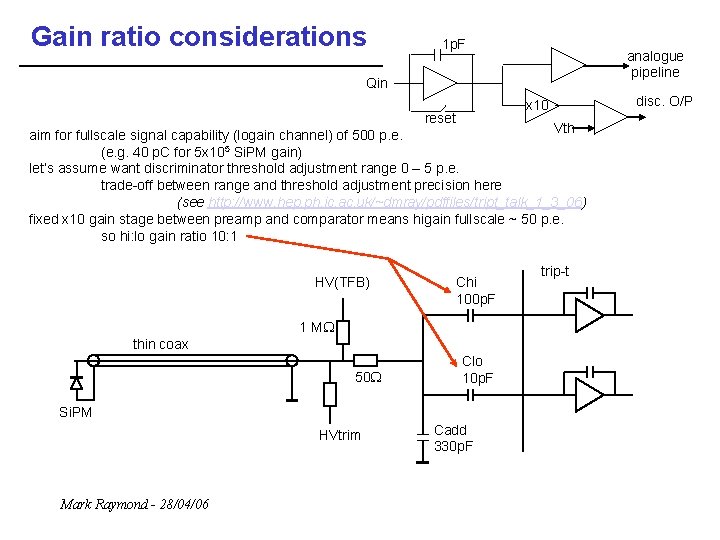

Gain ratio considerations 1 p. F analogue pipeline Qin x 10 reset Vth aim for fullscale signal capability (logain channel) of 500 p. e. (e. g. 40 p. C for 5 x 105 Si. PM gain) let’s assume want discriminator threshold adjustment range 0 – 5 p. e. trade-off between range and threshold adjustment precision here (see http: //www. hep. ph. ic. ac. uk/~dmray/pdffiles/tript_talk_1_3_06) fixed x 10 gain stage between preamp and comparator means higain fullscale ~ 50 p. e. so hi: lo gain ratio 10: 1 HV(TFB) Chi 100 p. F 1 MW thin coax 50 W Clo 10 p. F Si. PM HVtrim Mark Raymond - 28/04/06 Cadd 330 p. F trip-t disc. O/P

Latest Trip-t test results from final version Lab. VIEW VME Programmable Digital Pattern Generator prog. attenuator ck and trig. ADC ~14 control lines preamp int. /reset pipeline, multiplexer, programming level shift d. ECL -> 2. 5 V CMOS Qinj Mark Raymond - 28/04/06 Trip-t Scope

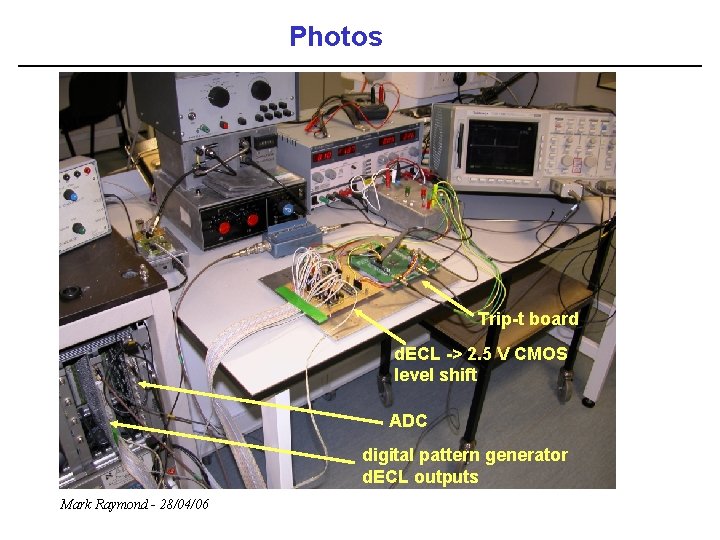

Photos Trip-t board d. ECL -> 2. 5 V CMOS level shift ADC digital pattern generator d. ECL outputs Mark Raymond - 28/04/06

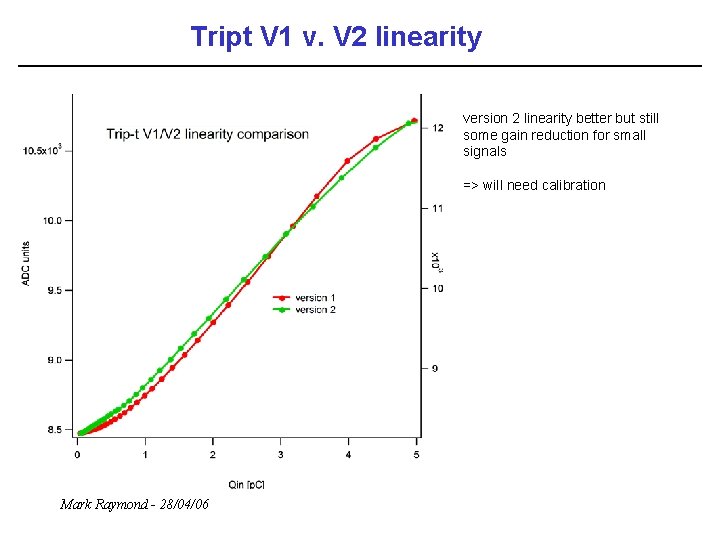

Tript V 1 v. V 2 linearity version 2 linearity better but still some gain reduction for small signals => will need calibration Mark Raymond - 28/04/06

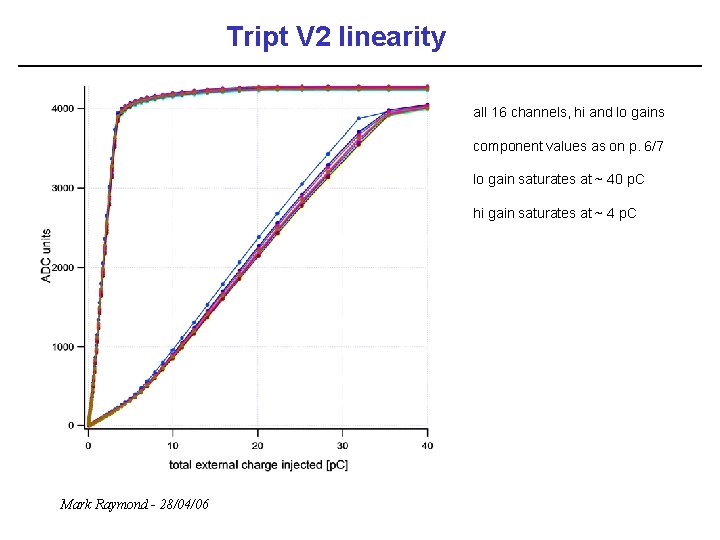

Tript V 2 linearity all 16 channels, hi and lo gains component values as on p. 6/7 lo gain saturates at ~ 40 p. C hi gain saturates at ~ 4 p. C Mark Raymond - 28/04/06

Tript V 2 linearity log-log plot of same data 10: 1 gain ratio means gain range change occurs where logain signal size already large so no S/N problems Mark Raymond - 28/04/06

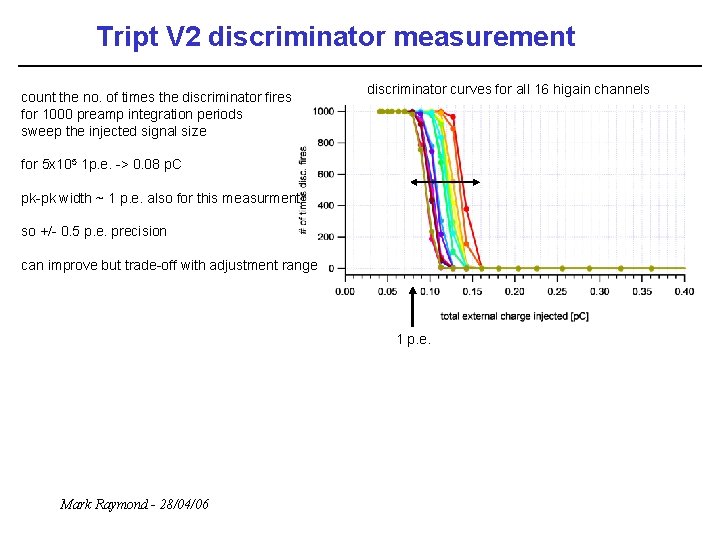

Tript V 2 discriminator measurement count the no. of times the discriminator fires for 1000 preamp integration periods sweep the injected signal size discriminator curves for all 16 higain channels for 5 x 105 1 p. e. -> 0. 08 p. C pk-pk width ~ 1 p. e. also for this measurment so +/- 0. 5 p. e. precision can improve but trade-off with adjustment range 1 p. e. Mark Raymond - 28/04/06

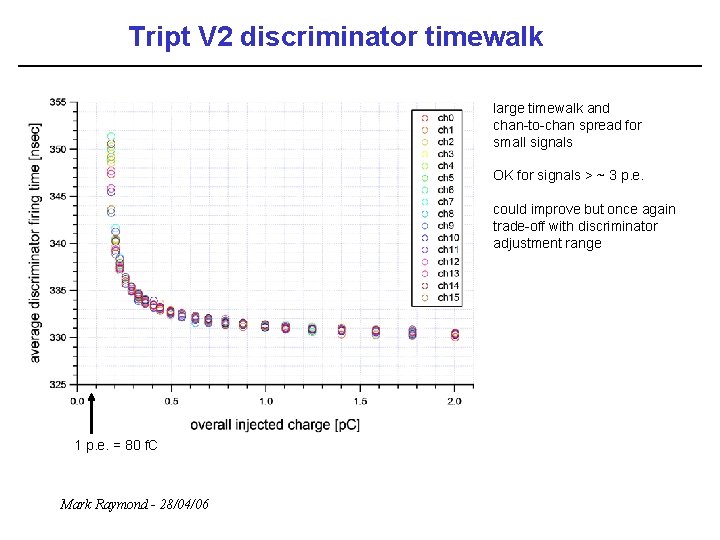

Tript V 2 discriminator timewalk large timewalk and chan-to-chan spread for small signals OK for signals > ~ 3 p. e. could improve but once again trade-off with discriminator adjustment range 1 p. e. = 80 f. C Mark Raymond - 28/04/06

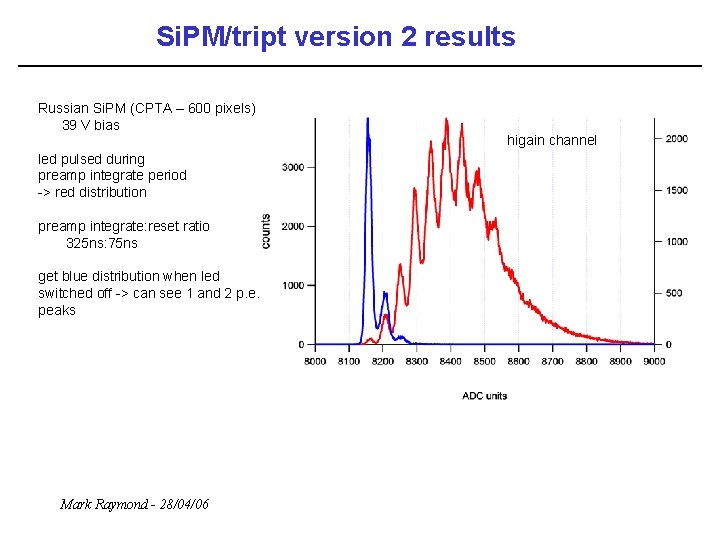

Si. PM/tript version 2 results Russian Si. PM (CPTA – 600 pixels) 39 V bias led pulsed during preamp integrate period -> red distribution preamp integrate: reset ratio 325 ns: 75 ns get blue distribution when led switched off -> can see 1 and 2 p. e. peaks Mark Raymond - 28/04/06 higain channel

TFB – Trip-t Front end Board aiming for 10 cm x 15 cm cal dac trip-t HVtrim 16 x Si. PM connectors HVtrim trip-t ADC HVtrim DAQ I/F FE-FPGA this picture is conceptual – reality will be different – but we need to decide what the reality should be in the near future power HVtrim trip-t HVtrim Mark Raymond - 28/04/06 16 x Si. PM connectors ADC trip-t cal dac HVtrim real layout only just beginning on analogue front end interface need to keep component density high here and take care of signals propose to use ultra-min. coax connectors Si. PM connection needs thought HVtrim local supply and T monitoring 16 x Si. PM connectors picture shows conceptual layout of main components need to consider cable routing, how connections can be made, cooling …

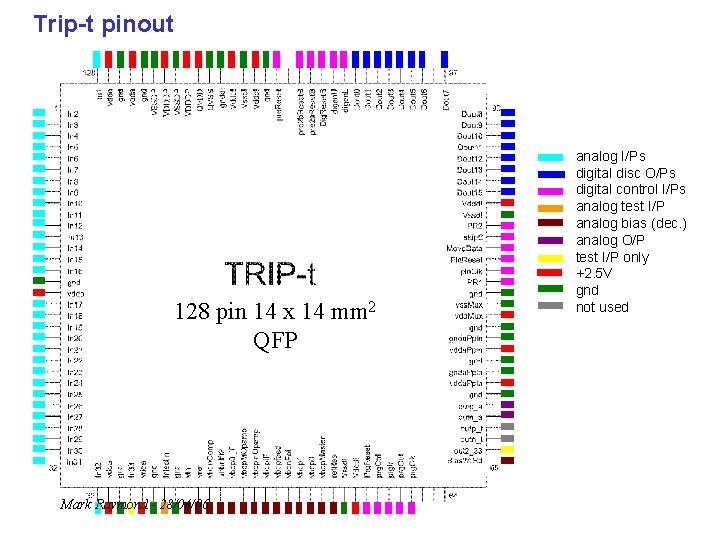

Trip-t pinout 128 pin 14 x 14 mm 2 QFP Mark Raymond - 28/04/06 analog I/Ps digital disc O/Ps digital control I/Ps analog test I/P analog bias (dec. ) analog O/P test I/P only +2. 5 V gnd not used

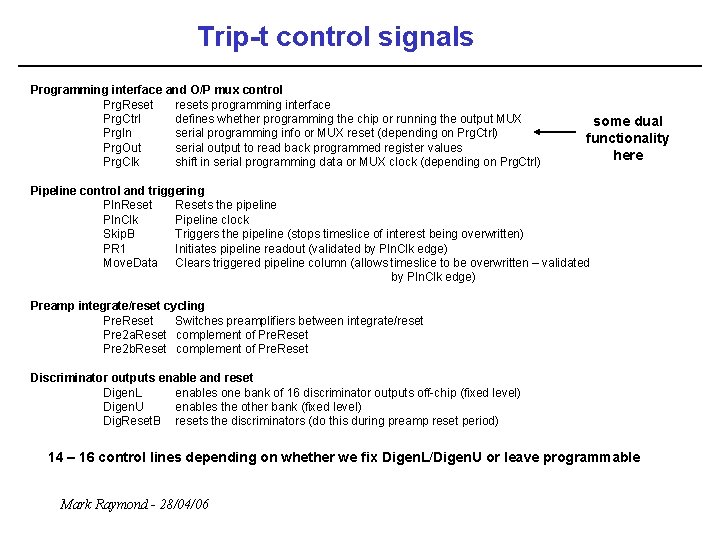

Trip-t control signals Programming interface and O/P mux control Prg. Reset resets programming interface Prg. Ctrl defines whether programming the chip or running the output MUX Prg. In serial programming info or MUX reset (depending on Prg. Ctrl) Prg. Out serial output to read back programmed register values Prg. Clk shift in serial programming data or MUX clock (depending on Prg. Ctrl) some dual functionality here Pipeline control and triggering Pln. Resets the pipeline Pln. Clk Pipeline clock Skip. B Triggers the pipeline (stops timeslice of interest being overwritten) PR 1 Initiates pipeline readout (validated by Pln. Clk edge) Move. Data Clears triggered pipeline column (allows timeslice to be overwritten – validated by Pln. Clk edge) Preamp integrate/reset cycling Pre. Reset Switches preamplifiers between integrate/reset Pre 2 a. Reset complement of Pre. Reset Pre 2 b. Reset complement of Pre. Reset Discriminator outputs enable and reset Digen. L enables one bank of 16 discriminator outputs off-chip (fixed level) Digen. U enables the other bank (fixed level) Dig. Reset. B resets the discriminators (do this during preamp reset period) 14 – 16 control lines depending on whether we fix Digen. L/Digen. U or leave programmable Mark Raymond - 28/04/06

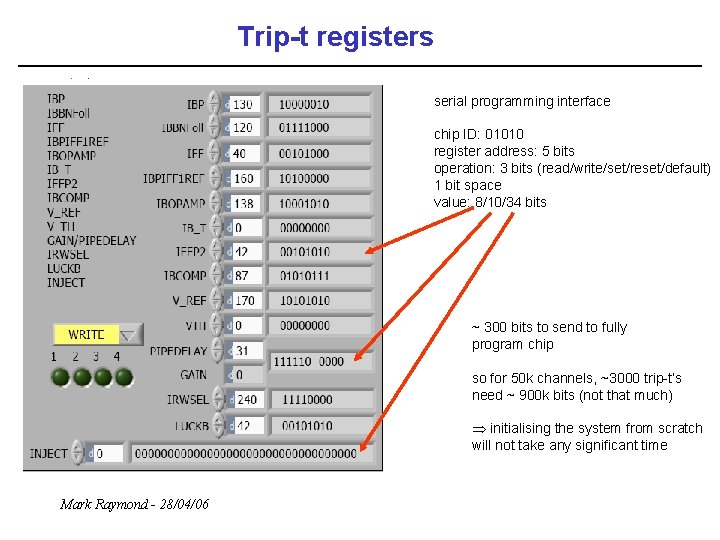

Trip-t registers serial programming interface chip ID: 01010 register address: 5 bits operation: 3 bits (read/write/set/reset/default) 1 bit space value: 8/10/34 bits ~ 300 bits to send to fully program chip so for 50 k channels, ~3000 trip-t’s need ~ 900 k bits (not that much) Þ initialising the system from scratch will not take any significant time Mark Raymond - 28/04/06

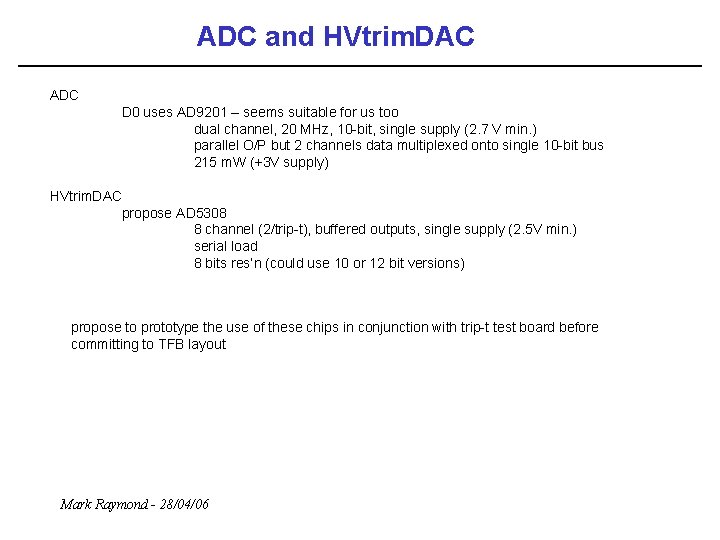

ADC and HVtrim. DAC ADC D 0 uses AD 9201 – seems suitable for us too dual channel, 20 MHz, 10 -bit, single supply (2. 7 V min. ) parallel O/P but 2 channels data multiplexed onto single 10 -bit bus 215 m. W (+3 V supply) HVtrim. DAC propose AD 5308 8 channel (2/trip-t), buffered outputs, single supply (2. 5 V min. ) serial load 8 bits res’n (could use 10 or 12 bit versions) propose to prototype the use of these chips in conjunction with trip-t test board before committing to TFB layout Mark Raymond - 28/04/06

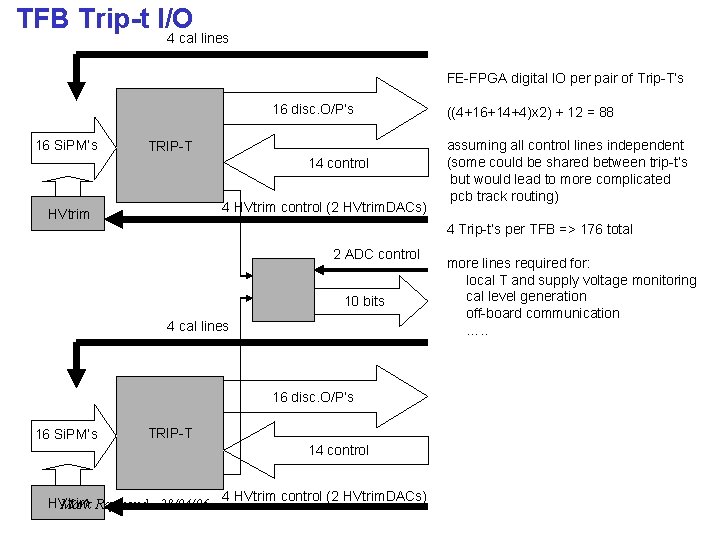

TFB Trip-t I/O 4 cal lines FE-FPGA digital IO per pair of Trip-T’s 16 disc. O/P’s 16 Si. PM’s TRIP-T 14 control 4 HVtrim control (2 HVtrim. DACs) HVtrim assuming all control lines independent (some could be shared between trip-t’s but would lead to more complicated pcb track routing) 4 Trip-t’s per TFB => 176 total 2 ADC control 10 bits 4 cal lines 16 disc. O/P’s 16 Si. PM’s ((4+16+14+4)x 2) + 12 = 88 TRIP-T 14 control 4 HVtrim control (2 HVtrim. DACs) HVtrim Mark Raymond - 28/04/06 more lines required for: local T and supply voltage monitoring cal level generation off-board communication …. .

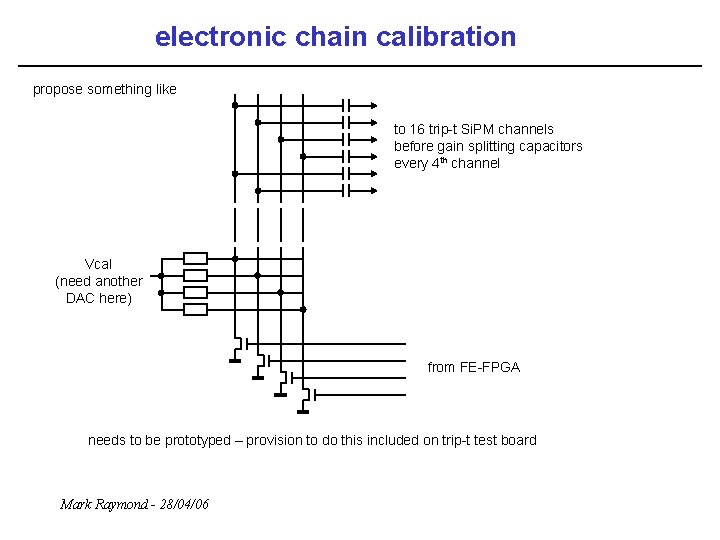

electronic chain calibration propose something like to 16 trip-t Si. PM channels before gain splitting capacitors every 4 th channel Vcal (need another DAC here) from FE-FPGA needs to be prototyped – provision to do this included on trip-t test board Mark Raymond - 28/04/06

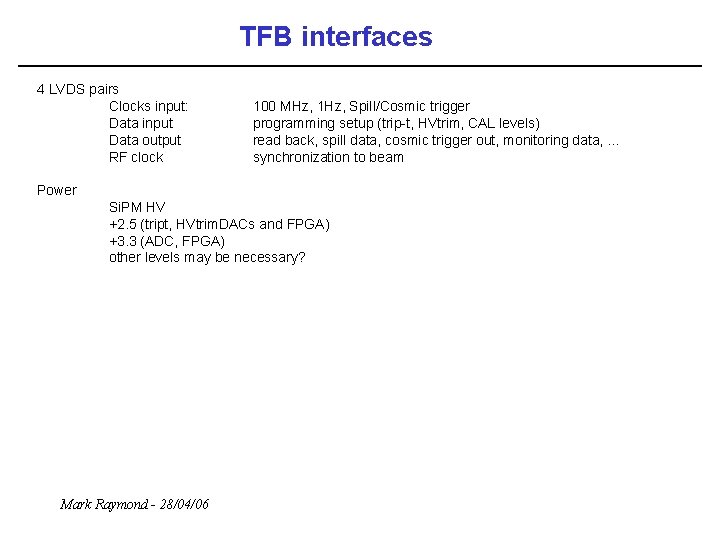

TFB interfaces 4 LVDS pairs Clocks input: Data input Data output RF clock 100 MHz, 1 Hz, Spill/Cosmic trigger programming setup (trip-t, HVtrim, CAL levels) read back, spill data, cosmic trigger out, monitoring data, … synchronization to beam Power Si. PM HV +2. 5 (tript, HVtrim. DACs and FPGA) +3. 3 (ADC, FPGA) other levels may be necessary? Mark Raymond - 28/04/06

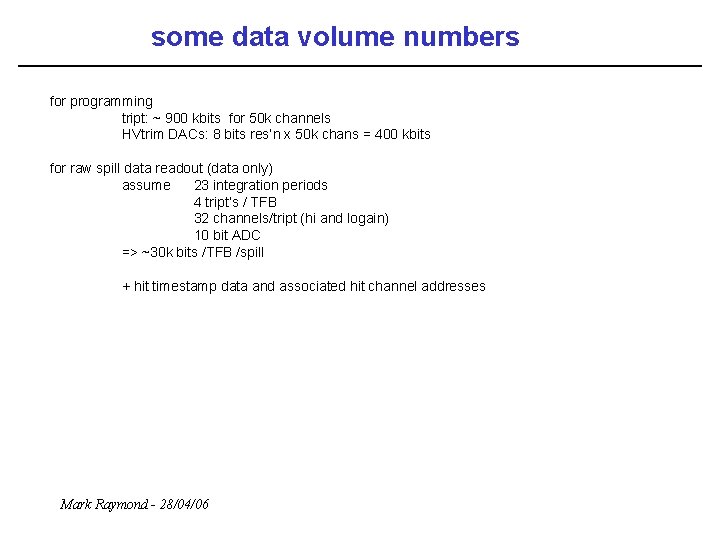

some data volume numbers for programming tript: ~ 900 kbits for 50 k channels HVtrim DACs: 8 bits res’n x 50 k chans = 400 kbits for raw spill data readout (data only) assume 23 integration periods 4 tript’s / TFB 32 channels/tript (hi and logain) 10 bit ADC => ~30 k bits /TFB /spill + hit timestamp data and associated hit channel addresses Mark Raymond - 28/04/06

TFB FE-FPGA tasks Clock and trigger recovery and synchronization - 100 MHz / RF clock / spill trigger / cosmic trigger Tript register programming Si. PM HV-trim - individual HV trim DACs on all Si. PM channels need programming Tript and ADC operation sequencing during spill - digital control signals for integrate/reset, pipeline write cycling, pipeline read, output mux cycling and ADC control and readout Hit timestamping (linked to above) - timestamp tript discriminator outputs to 2. 5 ns precision Data formatting and transmission - bundle up timestamp information and digitized analogue data into agreed fromat and transmit Cosmic trigger formation - during spill gaps (~ 3 secs) need to cycle chip, look for patterns of discriminator hits from neighbouring channels, transmit trigger off-board, respond with data if trigger returned local monitoring – temperature, local voltage levels electronic calibration – outside normal physics data taking Mark Raymond - 28/04/06

plans for this year complete tests with trip-t test board calibration cct ADC HVtrim. DAC other things to define what to monitor locally and how to implement it 1 st TFB prototype to be produced by October in parallel produce firmware to implement main functionality detailed electrical characterization by end of year Mark Raymond - 28/04/06

- Slides: 26