Transmitter Linearization for Portable Wireless Communication Systems Luns

Transmitter Linearization for Portable Wireless Communication Systems Luns Tee University of California, Berkeley Dissertation Talk May 18, 2006

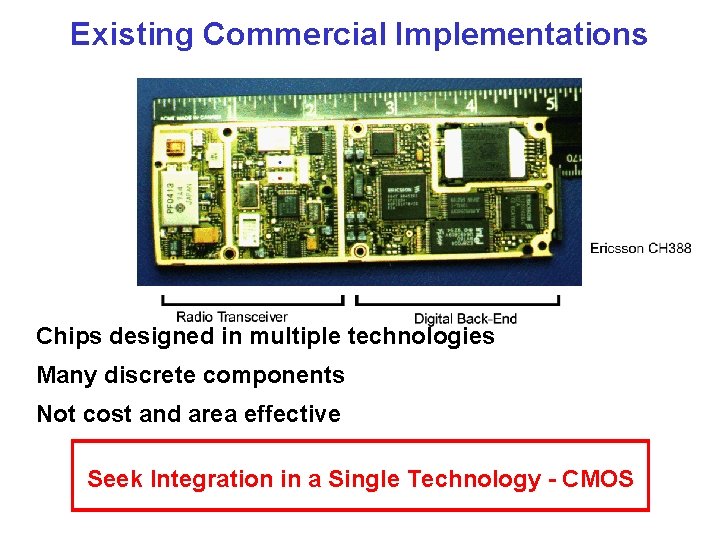

Existing Commercial Implementations Chips designed in multiple technologies Many discrete components Not cost and area effective Seek Integration in a Single Technology - CMOS

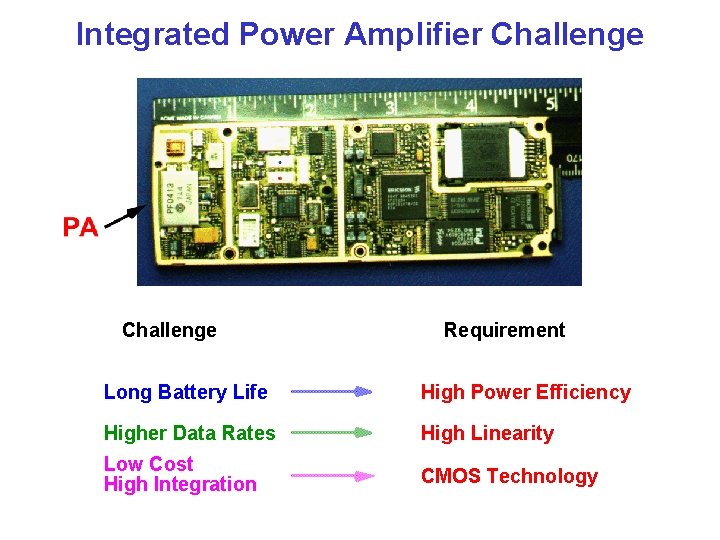

Integrated Power Amplifier Challenge Requirement Long Battery Life High Power Efficiency Higher Data Rates High Linearity Low Cost High Integration CMOS Technology

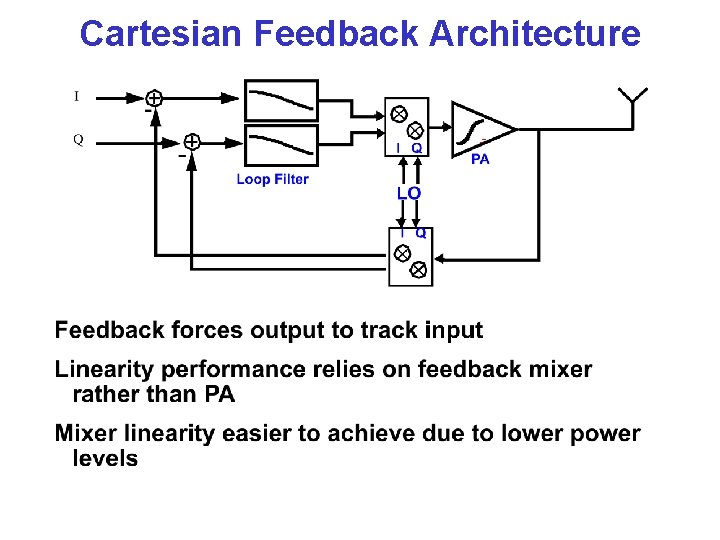

Research Goals Problem: How to meet High-Linearity Requirements in a High-Efficiency CMOS RF Power Amplifier Proposed Solution: Cartesian Feedback Understand system-level considerations and identify design guidelines Examine implementation issues for integration in CMOS

Outline

Outline Radio Transmitter Fundamentals Power Amplifier Basics - Efficiency/Linearity trade-off Spectral Regrowth - need for linearization Understanding distortion Linearization Techniques System-Level Analysis Circuit-Level Investigation

Radio Transmitter Fundamentals I(t) y(t) Q(t) I Q cos(wt) LO -sin(wt) Local Oscillator 0 Baseband I, Q f Ideal Modulator Power Amplifier wc RF y f

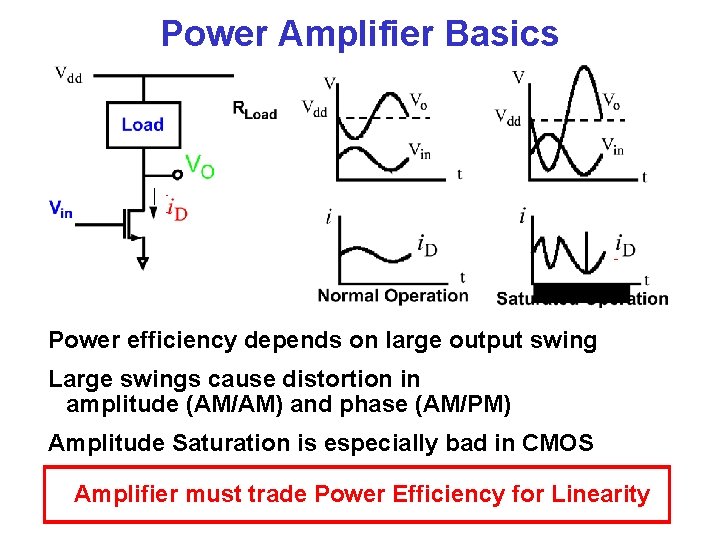

Power Amplifier Basics Power efficiency depends on large output swing Large swings cause distortion in amplitude (AM/AM) and phase (AM/PM) Amplitude Saturation is especially bad in CMOS Amplifier must trade Power Efficiency for Linearity

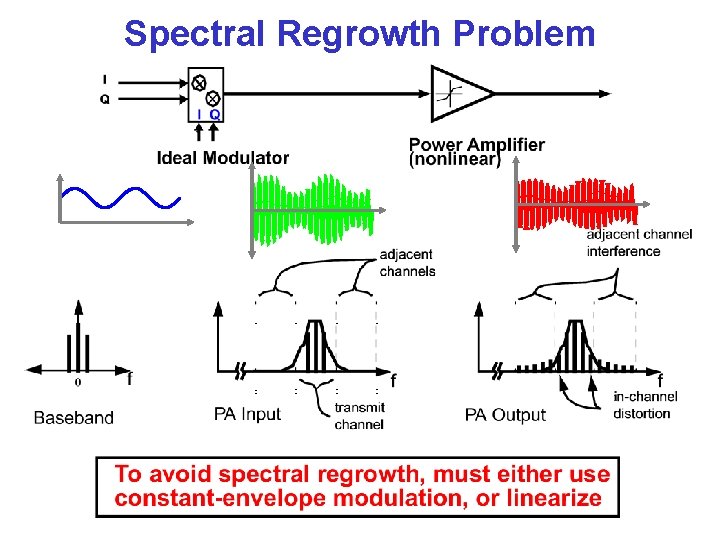

Spectral Regrowth Problem

Outline

Cartesian Feedback Architecture

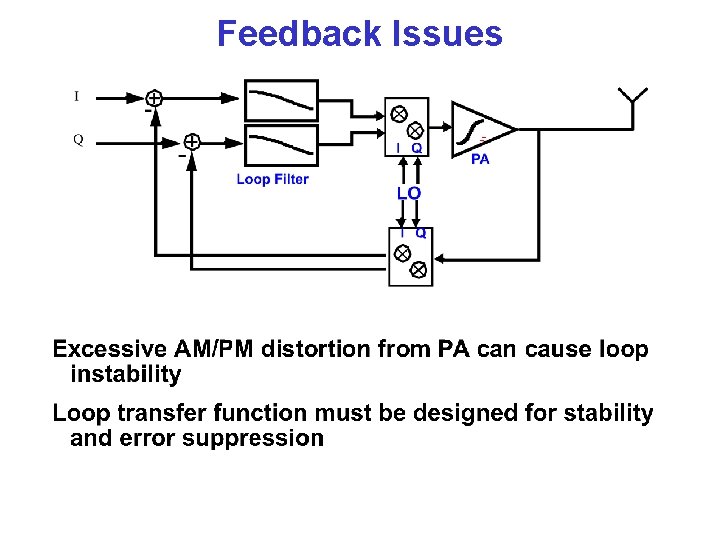

Feedback Issues

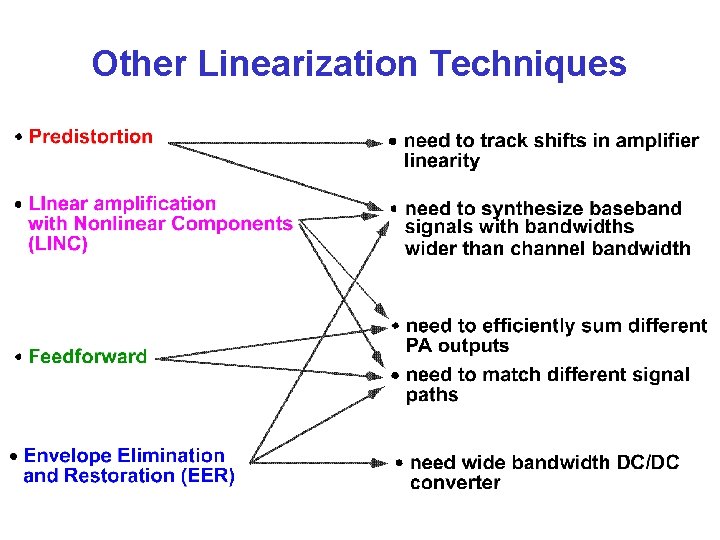

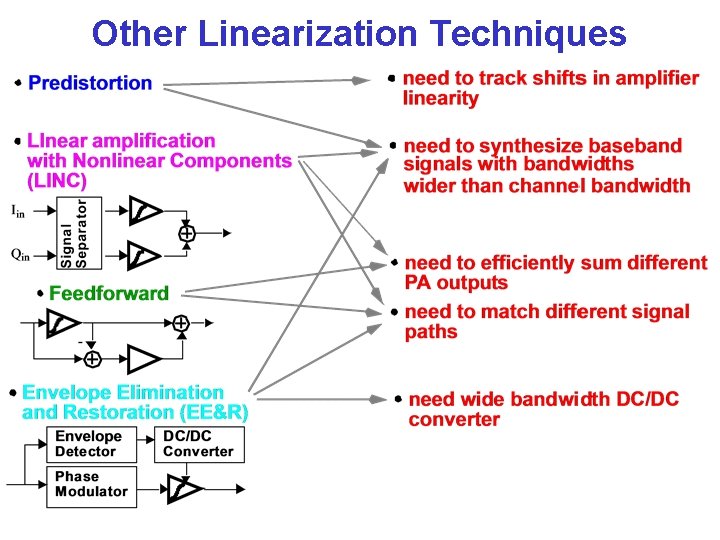

Other Linearization Techniques

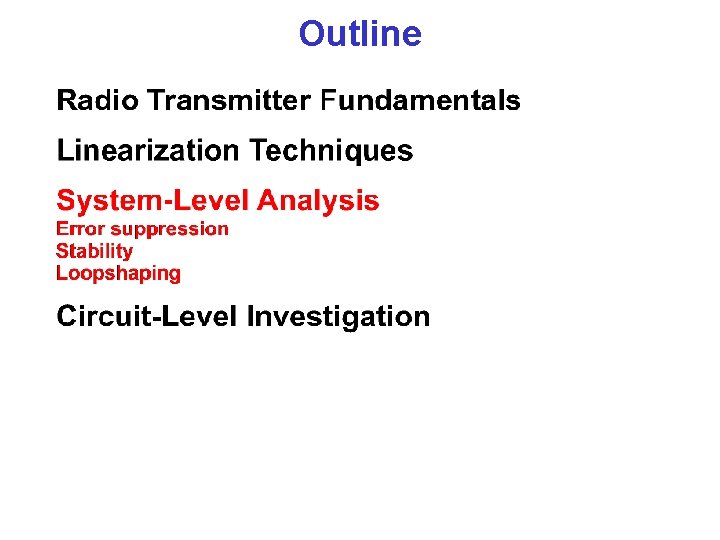

Outline

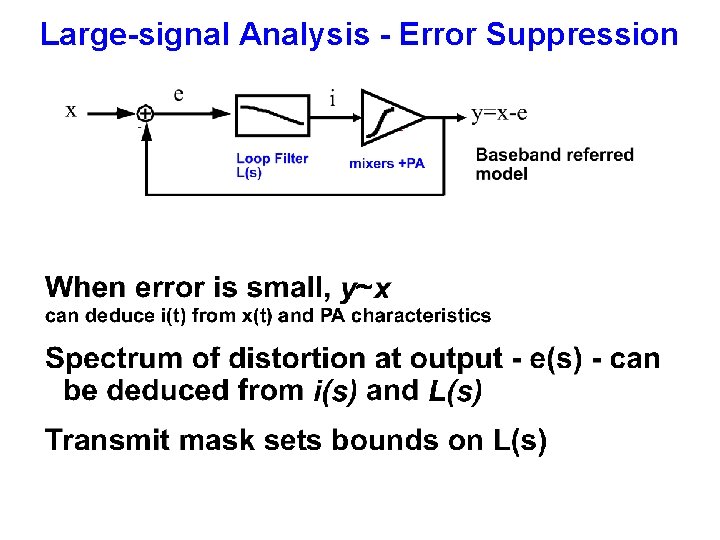

Large-signal Analysis - Error Suppression

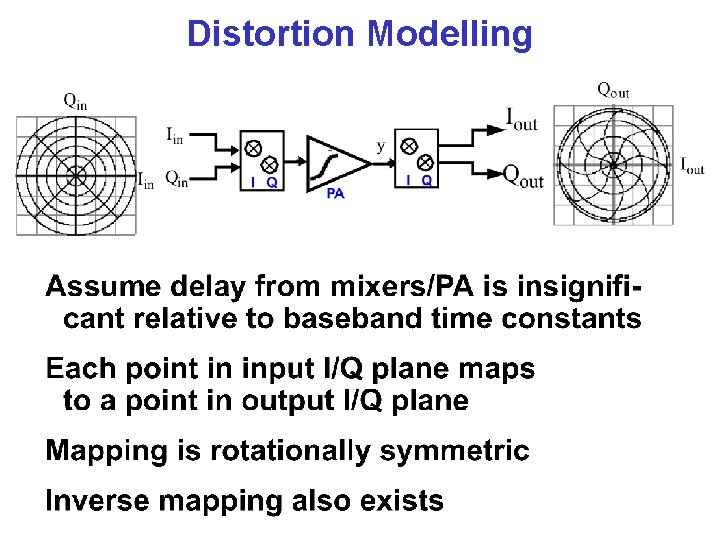

Distortion Modelling

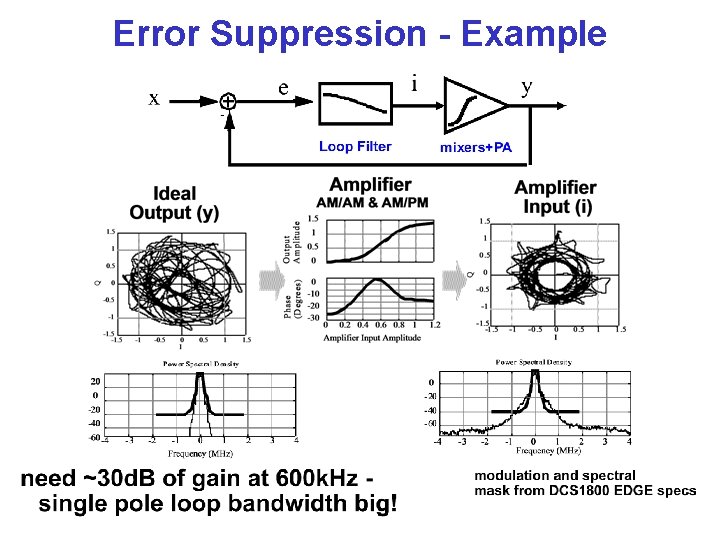

Error Suppression - Example

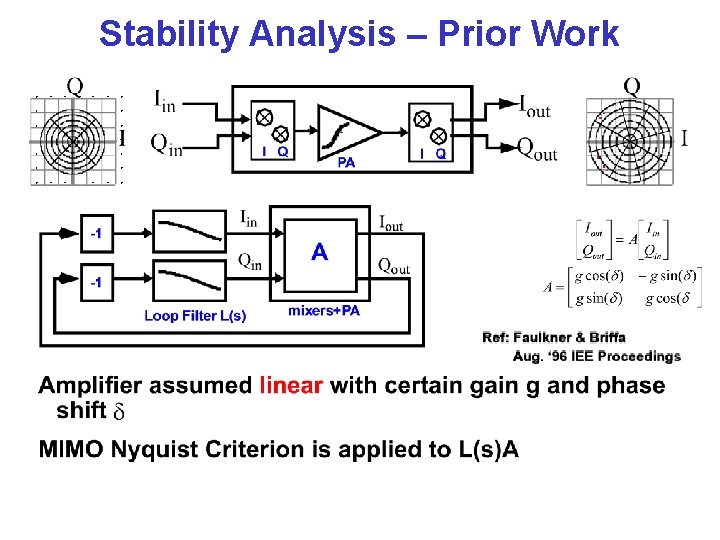

Stability Analysis – Prior Work

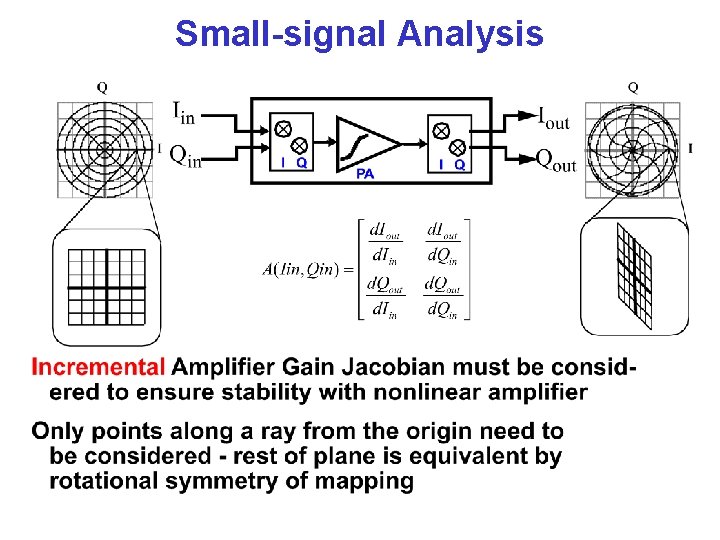

Small-signal Analysis

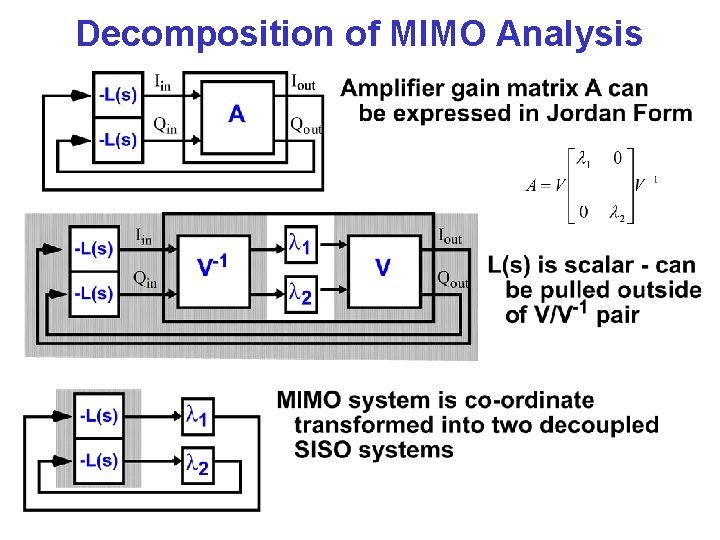

Decomposition of MIMO Analysis

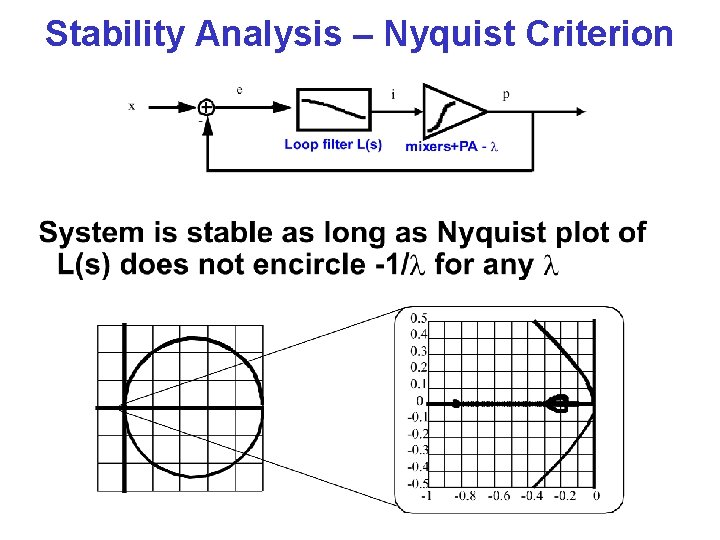

Stability Analysis – Nyquist Criterion

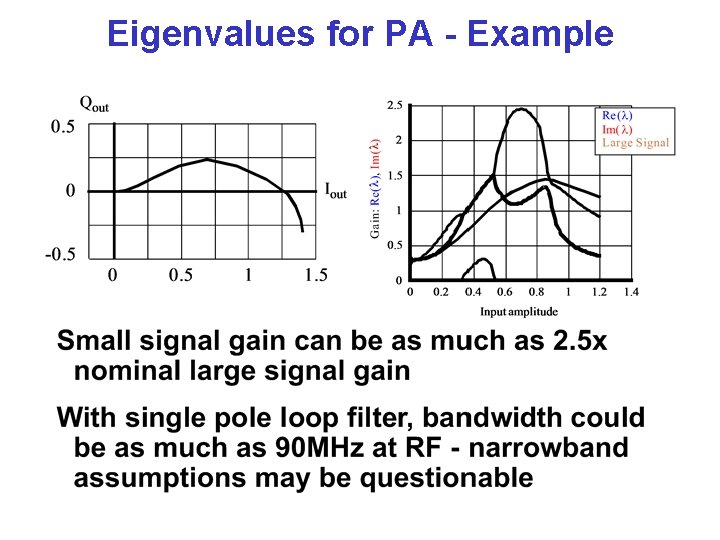

Eigenvalues for PA - Example

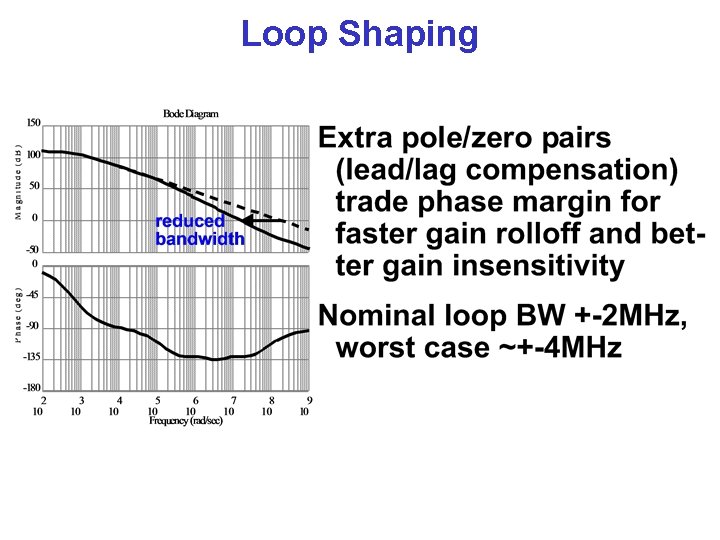

Loop Shaping

Outline

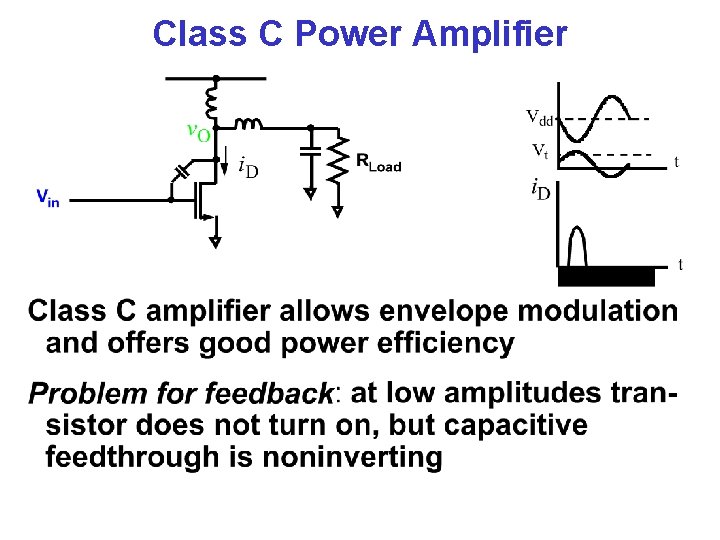

Class C Power Amplifier

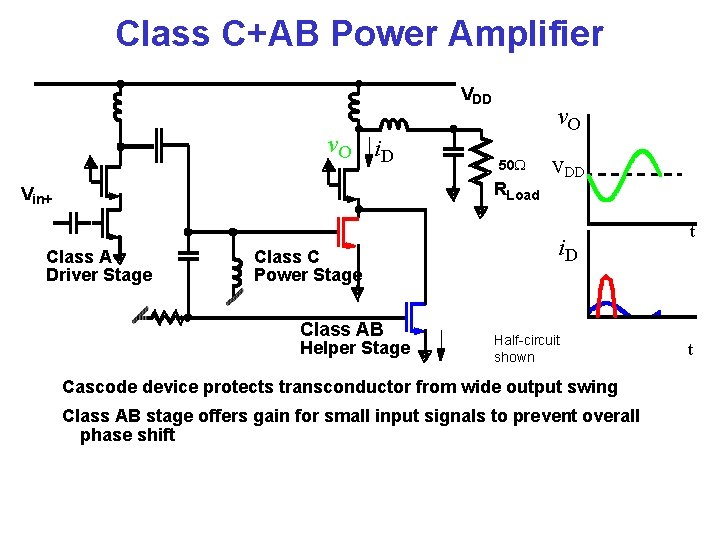

Class C+AB Power Amplifier VDD v. O i. D v. O 50 W RLoad Vin+ Class A Driver Stage Class C Power Stage Class AB Helper Stage VDD i. D Half-circuit shown Cascode device protects transconductor from wide output swing Class AB stage offers gain for small input signals to prevent overall phase shift t t

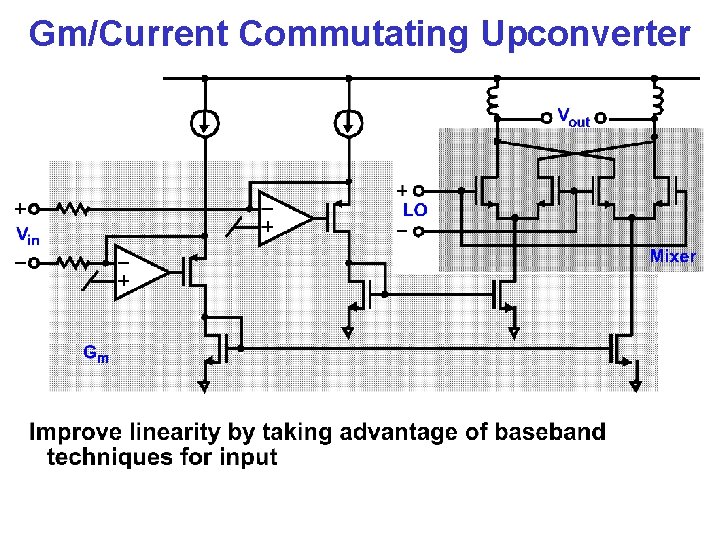

Gm/Current Commutating Upconverter

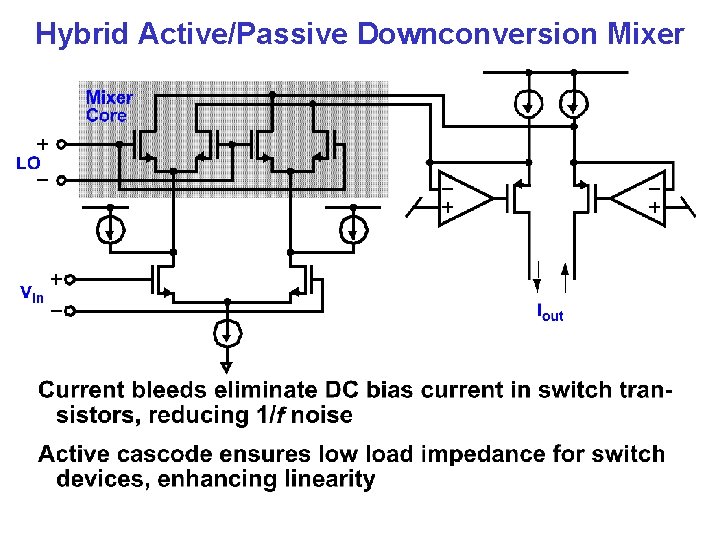

Hybrid Active/Passive Downconversion Mixer

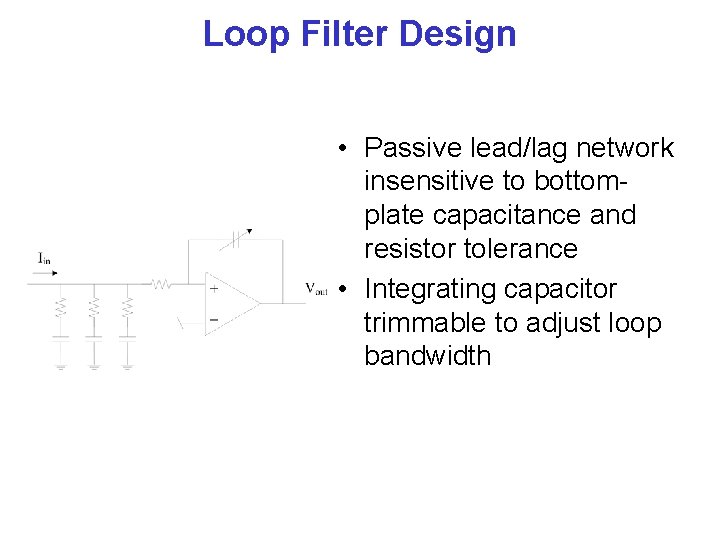

Loop Filter Design • Passive lead/lag network insensitive to bottomplate capacitance and resistor tolerance • Integrating capacitor trimmable to adjust loop bandwidth

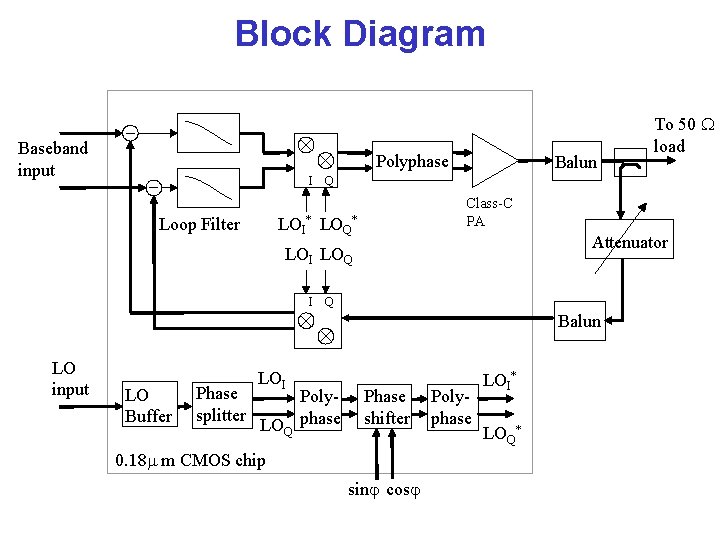

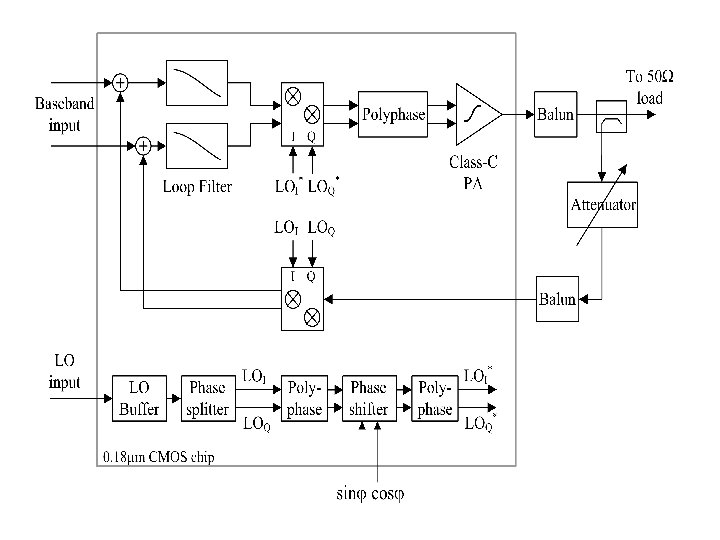

Block Diagram Baseband input Polyphase I Loop Filter Balun Q Class-C PA LOI* LOQ* Attenuator LOI LOQ I Q Balun LO input LO Buffer Phase splitter LOI To 50 W load Poly. LOQ phase Phase shifter 0. 18 m m CMOS chip sinj cosj Polyphase LOI* LOQ*

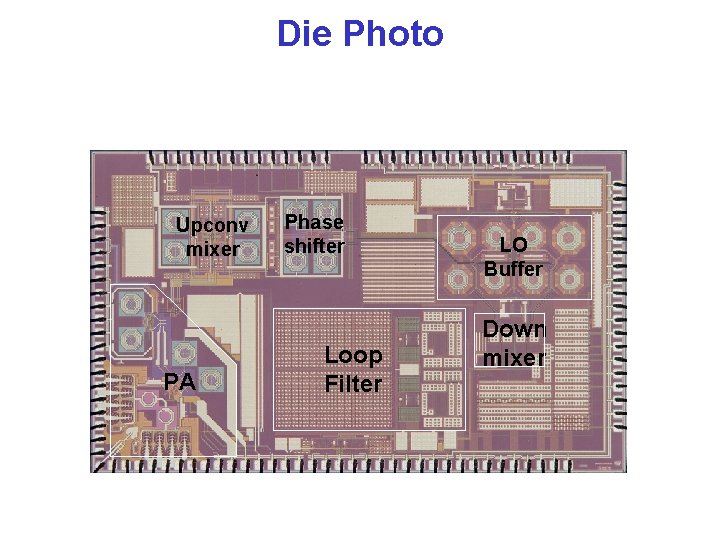

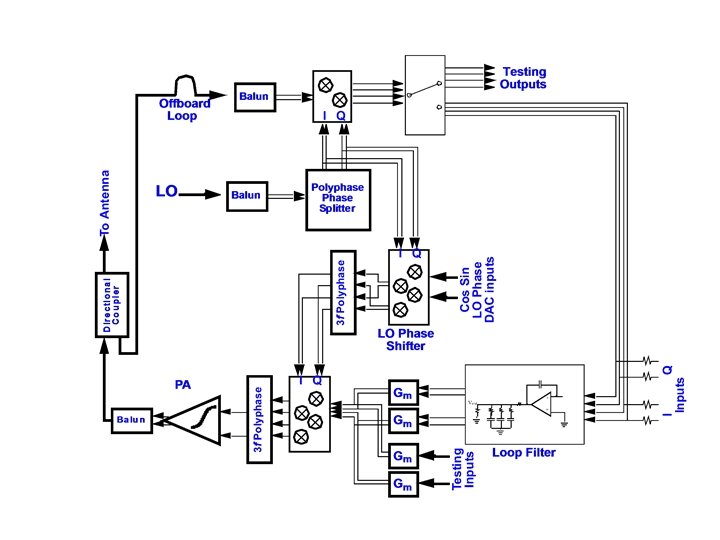

Die Photo Upconv mixer PA Phase shifter Loop Filter LO Buffer Down mixer

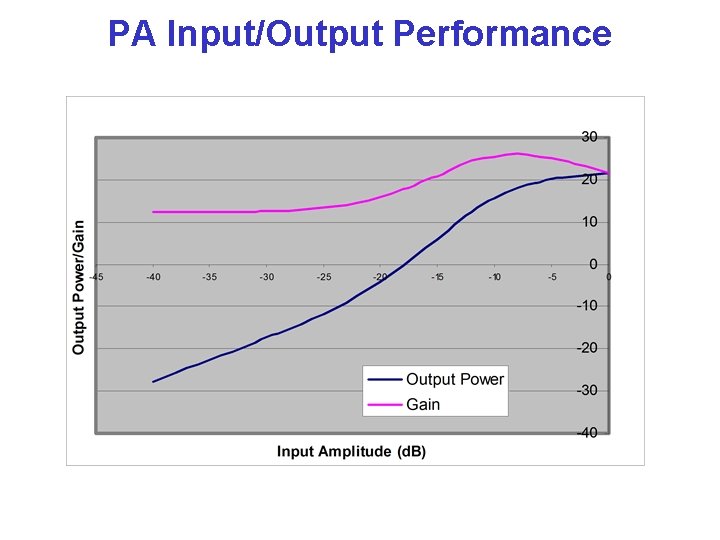

PA Input/Output Performance

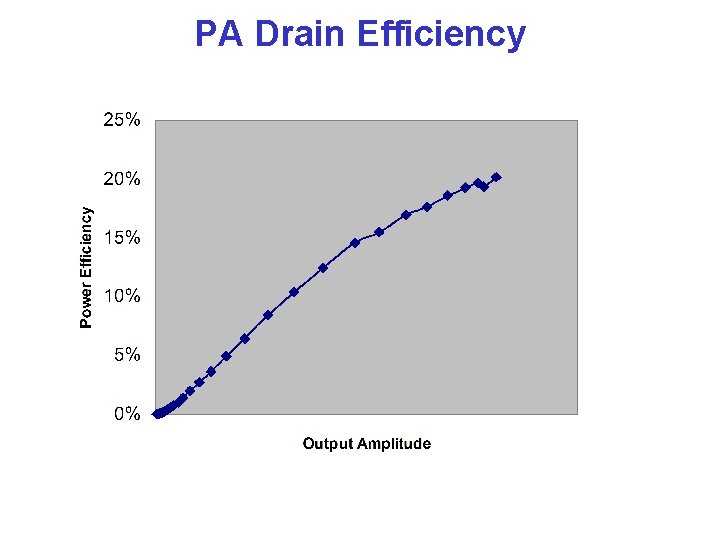

PA Drain Efficiency Power Efficiency 0. 25 0. 2 0. 15 0. 1 0. 05 0 0 5 10 Output Amplitude 15

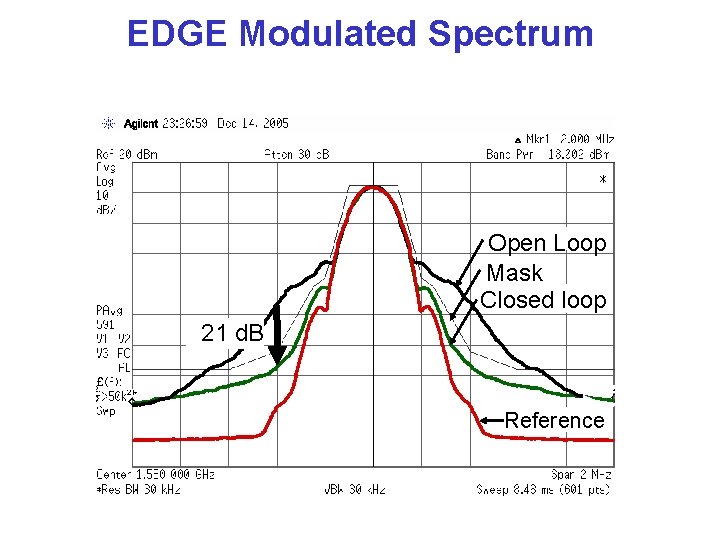

EDGE Modulated Spectrum Open Loop Mask Closed loop 21 d. B Reference

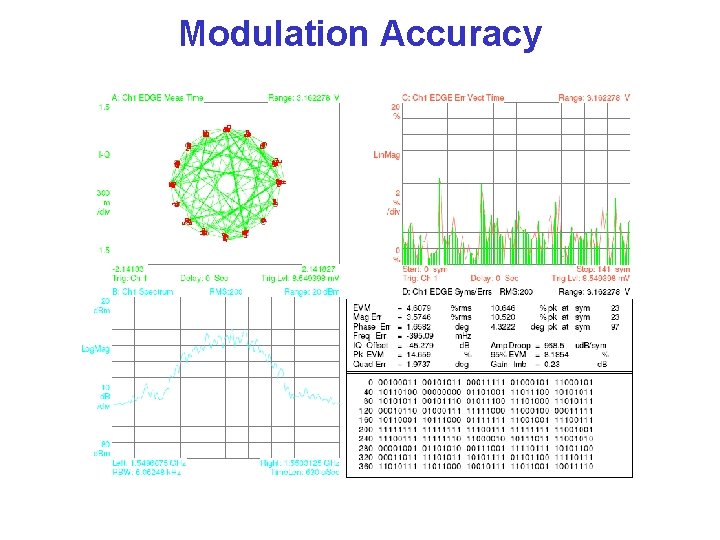

Modulation Accuracy

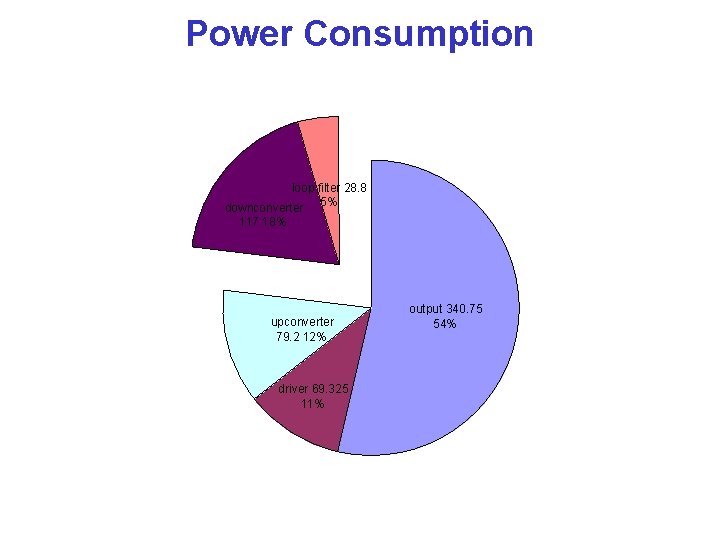

Power Consumption loop filter 28. 8 downconverter 5% 117 18% upconverter 79. 2 12% driver 69. 325 11% output 340. 75 54%

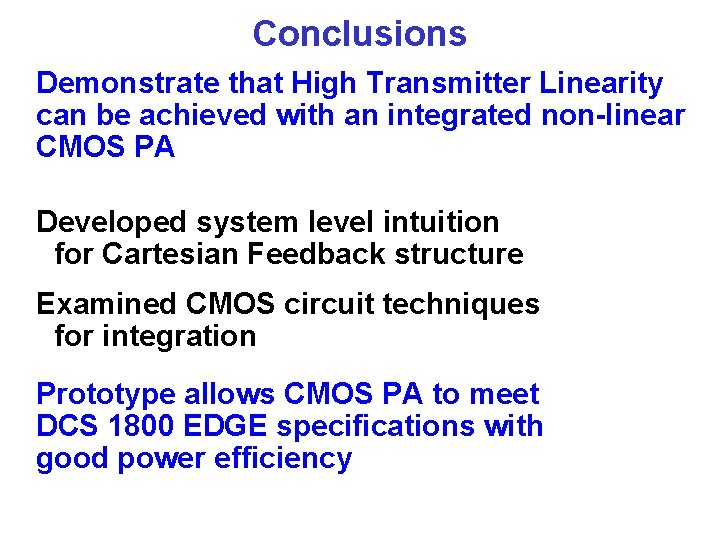

Conclusions Demonstrate that High Transmitter Linearity can be achieved with an integrated non-linear CMOS PA Developed system level intuition for Cartesian Feedback structure Examined CMOS circuit techniques for integration Prototype allows CMOS PA to meet DCS 1800 EDGE specifications with good power efficiency

Acknowledgements • • • STMicroelectronics California MICRO NSF grant #MIP 9412940 C 2 S 2 MARCO contract 2003 -CT-888 Marvell Semiconductor

Other Linearization Techniques

- Slides: 41