Transmetas New Processor Another way to design CPU

![Example of Alias ld %r 30, [%x] // first load from location x … Example of Alias ld %r 30, [%x] // first load from location x …](https://slidetodoc.com/presentation_image_h2/85b5f4f6945adf775f9c375ca9d88c65/image-12.jpg)

- Slides: 14

Transmeta’s New Processor Another way to design CPU By Wu Cheng Meng @csie. ccu. edu. tw

What’s Crusoe CPU • • • X 86 ISA Compatible Simple VLIW Hardware Software/Hardware Mixed Architecture Low Power Self-Turning of Clock & Voltage

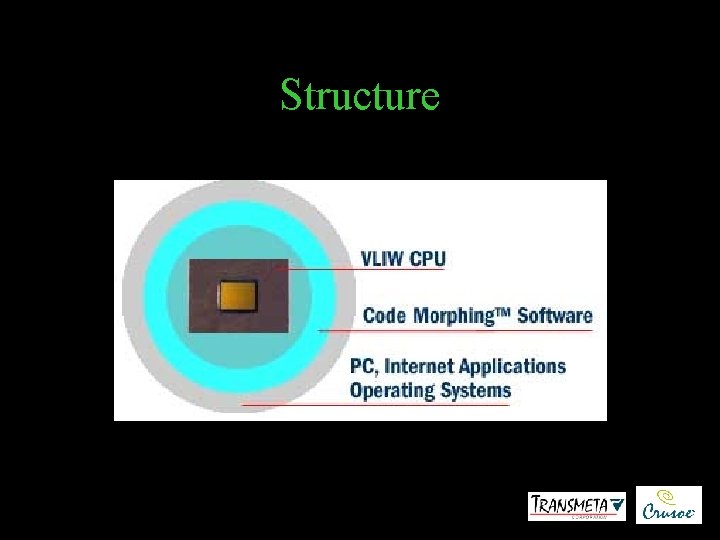

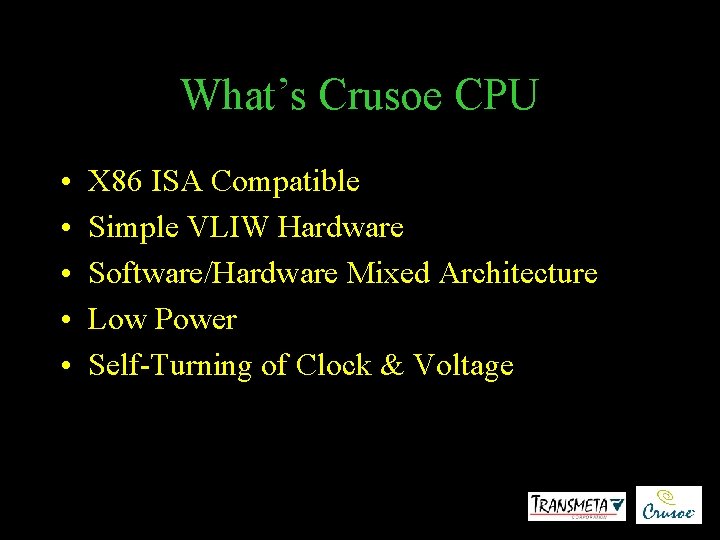

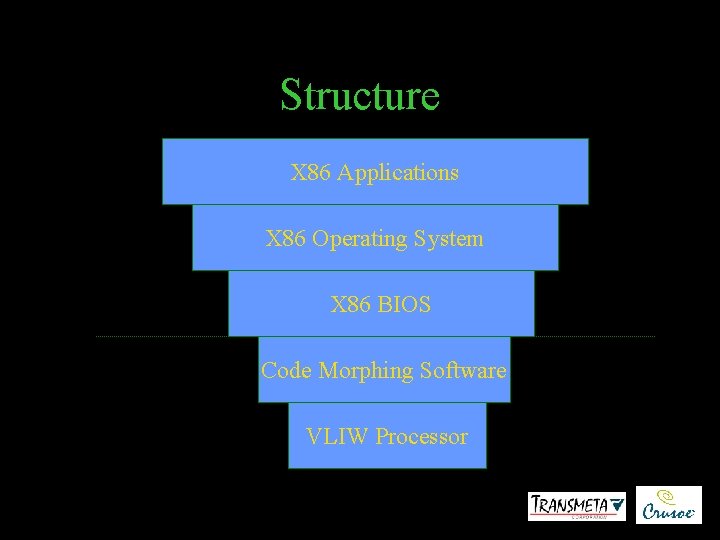

Structure

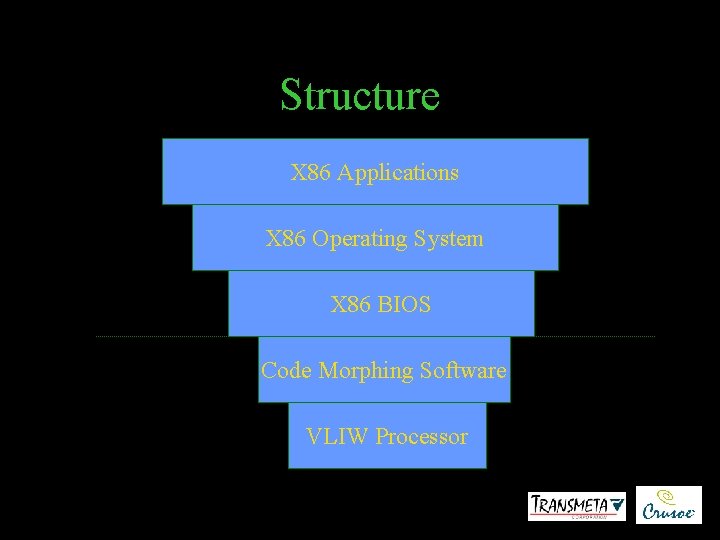

Structure X 86 Applications X 86 Operating System X 86 BIOS Code Morphing Software VLIW Processor

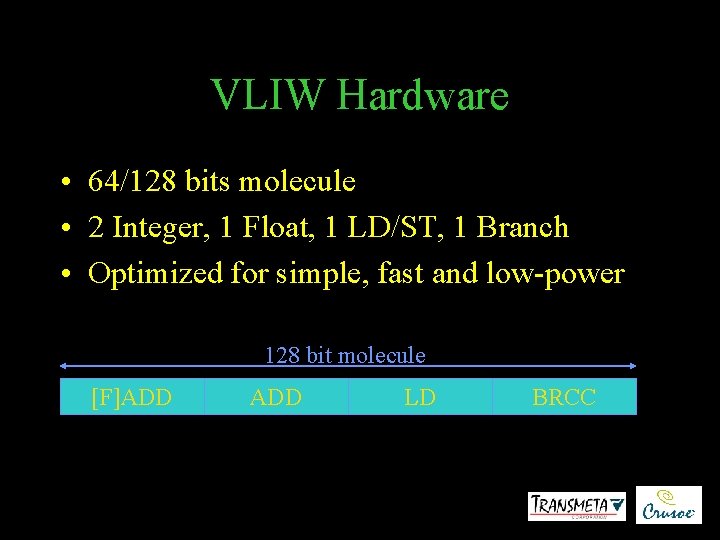

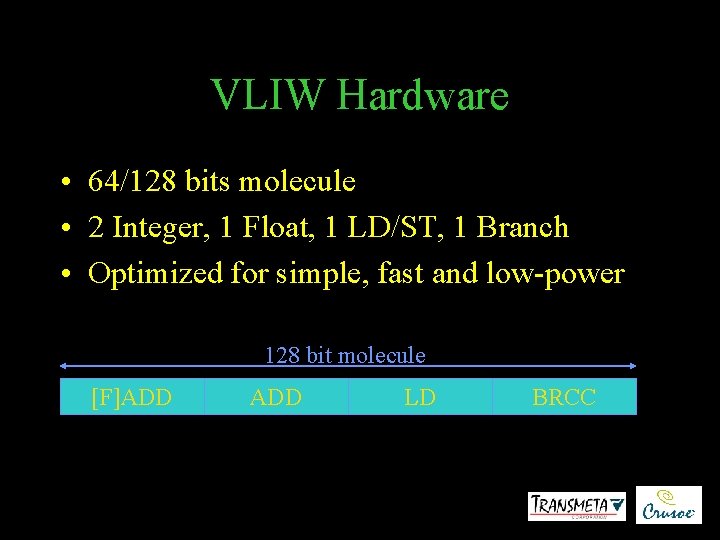

VLIW Hardware • 64/128 bits molecule • 2 Integer, 1 Float, 1 LD/ST, 1 Branch • Optimized for simple, fast and low-power 128 bit molecule [F]ADD LD BRCC

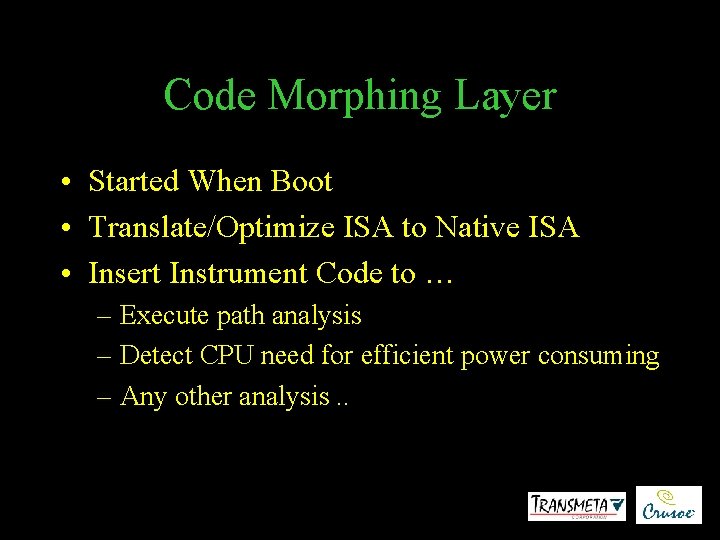

Code Morphing Layer • Started When Boot • Translate/Optimize ISA to Native ISA • Insert Instrument Code to … – Execute path analysis – Detect CPU need for efficient power consuming – Any other analysis. .

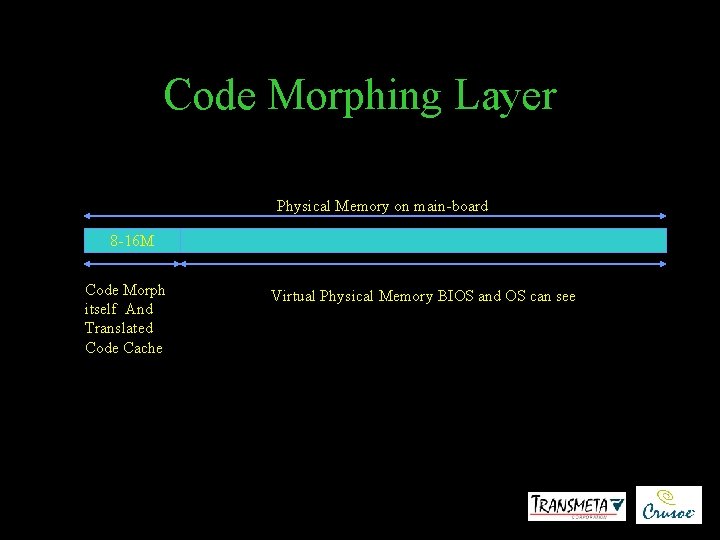

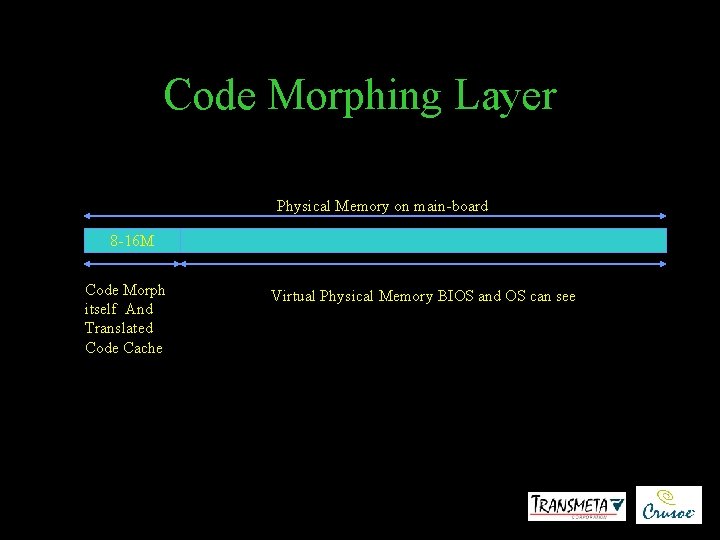

Code Morphing Layer Physical Memory on main-board 8 -16 M Code Morph itself And Translated Code Cache Virtual Physical Memory BIOS and OS can see

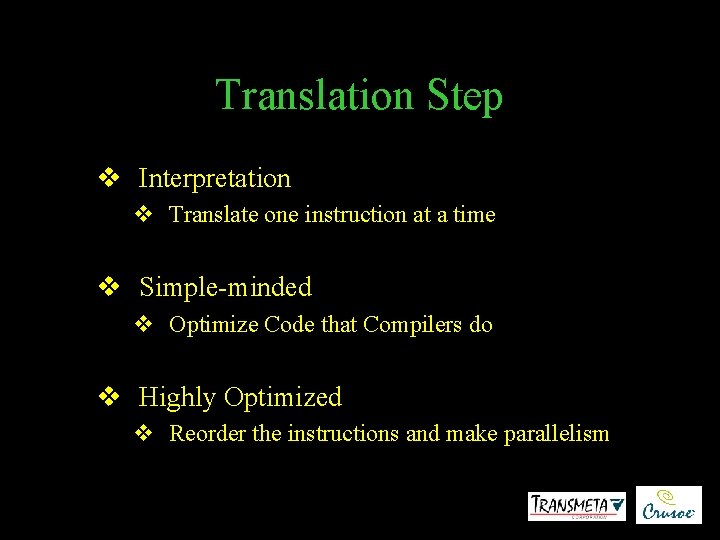

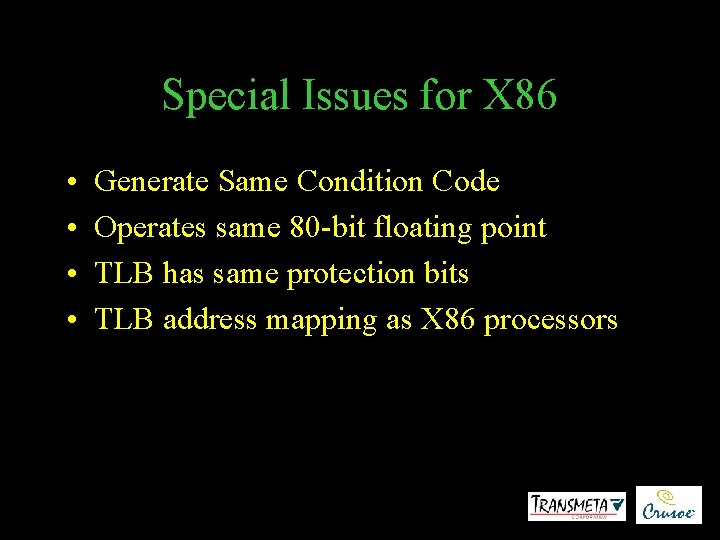

Translation Step v Interpretation v Translate one instruction at a time v Simple-minded v Optimize Code that Compilers do v Highly Optimized v Reorder the instructions and make parallelism

Special Issues for X 86 • • Generate Same Condition Code Operates same 80 -bit floating point TLB has same protection bits TLB address mapping as X 86 processors

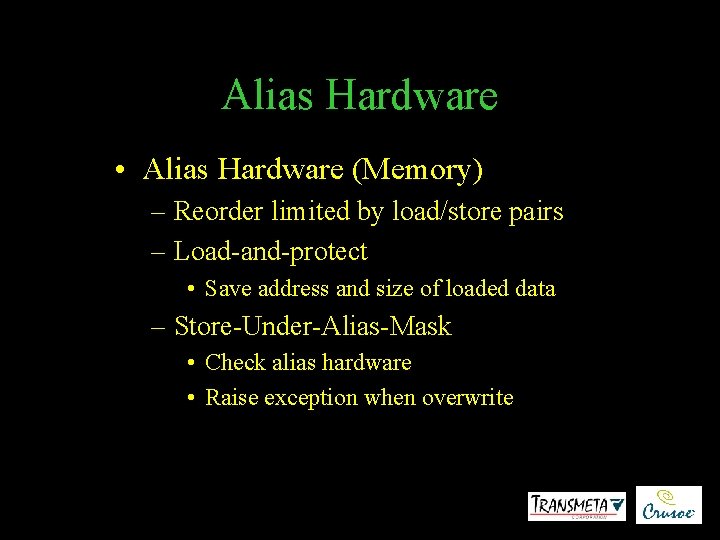

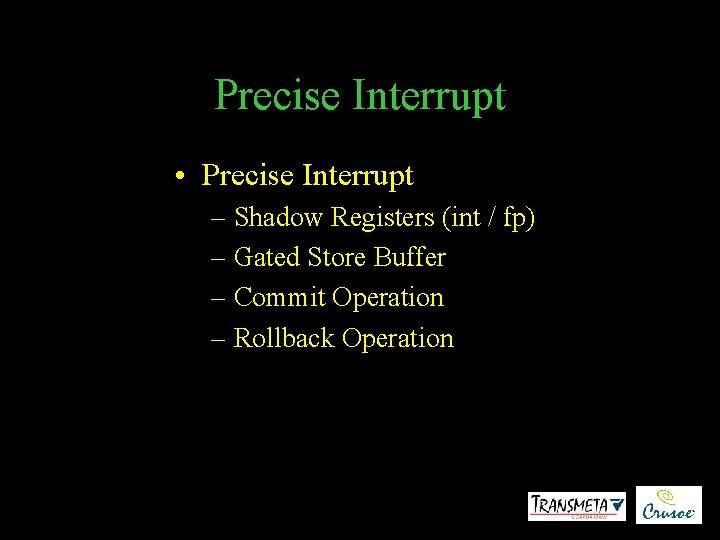

Precise Interrupt • Precise Interrupt – Shadow Registers (int / fp) – Gated Store Buffer – Commit Operation – Rollback Operation

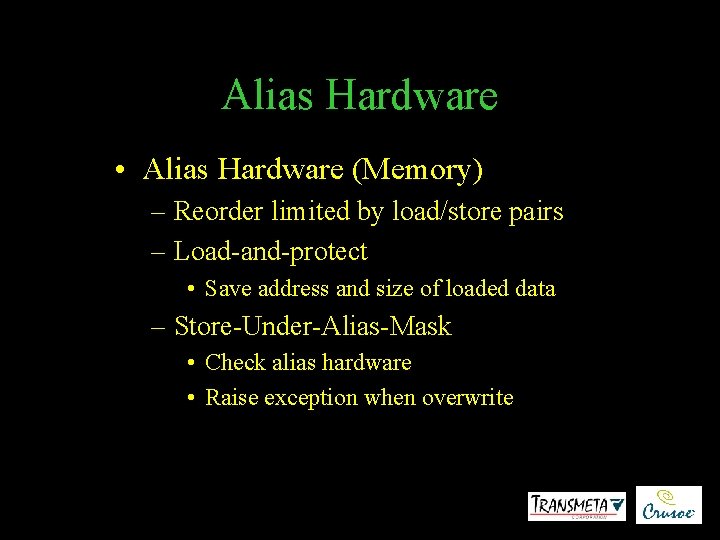

Alias Hardware • Alias Hardware (Memory) – Reorder limited by load/store pairs – Load-and-protect • Save address and size of loaded data – Store-Under-Alias-Mask • Check alias hardware • Raise exception when overwrite

![Example of Alias ld r 30 x first load from location x Example of Alias ld %r 30, [%x] // first load from location x …](https://slidetodoc.com/presentation_image_h2/85b5f4f6945adf775f9c375ca9d88c65/image-12.jpg)

Example of Alias ld %r 30, [%x] // first load from location x … st %data, [%y] // might overwrite location x ld %r 31, [%x] // this accesses location X again use %31 ldp %r 30, [%x] // load from location x and protect it … stam %data, [%y] // traps if it writes x use %30 // may use data from first load

Self-Modifying Code • Keep a “translated” bit in MMU • When a protected page is written – Invalidate the affected translation(s)

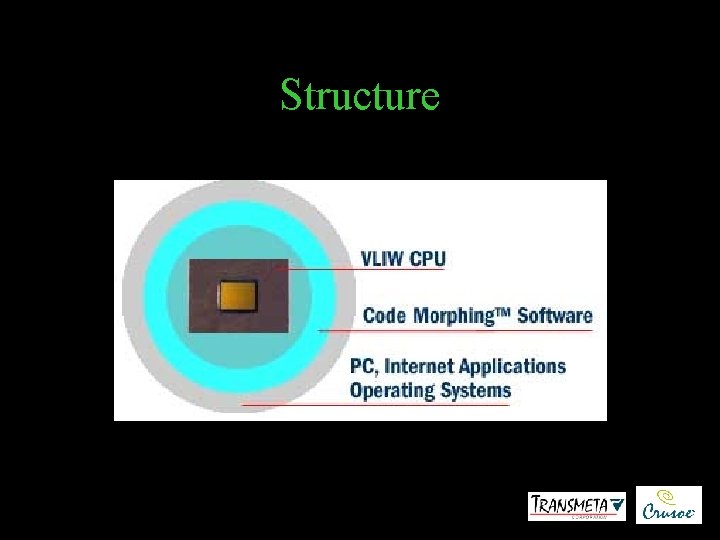

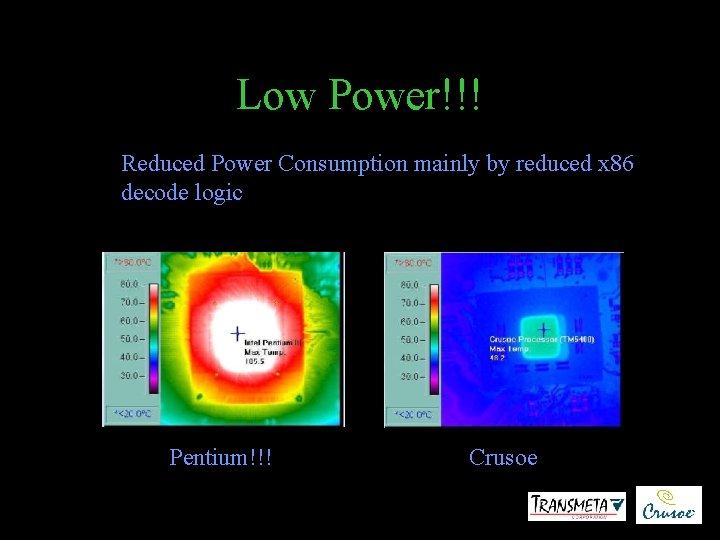

Low Power!!! Reduced Power Consumption mainly by reduced x 86 decode logic Pentium!!! Crusoe