Transition Delay Fault Testing of Microprocessors by Spectral

Transition Delay Fault Testing of Microprocessors by Spectral Method Nitin Yogi and Vishwani D. Agrawal Auburn University Department of ECE Auburn, AL 36849, USA March 6, 2007 39 th Southeastern Symposium on System Theory 1

Outline n Introduction q q n Problem and Approach q q n n n Defects and transition delay fault model Microprocessor testing Issues Register-transfer level modeling of transition delay faults Spectral analysis and test generation Design for Testability Experimental Results Conclusion March 6, 2007 39 th Southeastern Symposium on System Theory 2

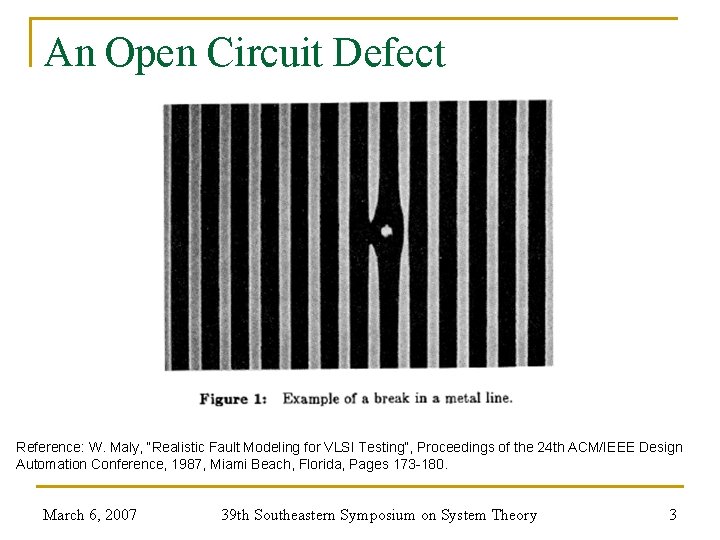

An Open Circuit Defect Reference: W. Maly, “Realistic Fault Modeling for VLSI Testing”, Proceedings of the 24 th ACM/IEEE Design Automation Conference, 1987, Miami Beach, Florida, Pages 173 -180. March 6, 2007 39 th Southeastern Symposium on System Theory 3

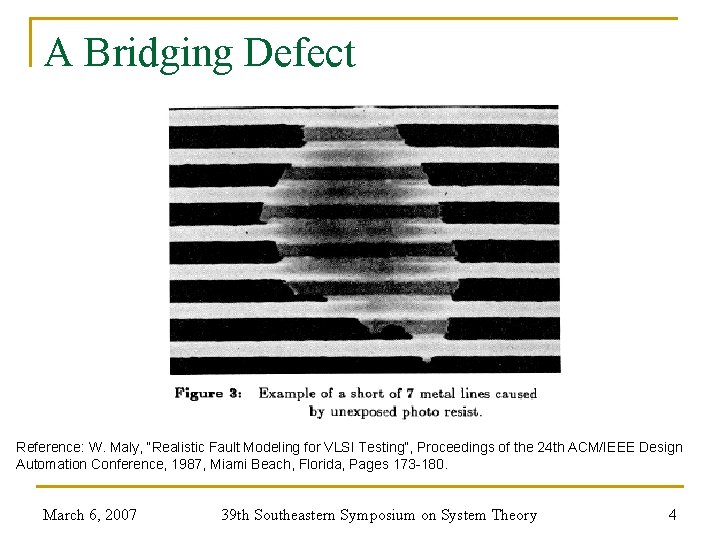

A Bridging Defect Reference: W. Maly, “Realistic Fault Modeling for VLSI Testing”, Proceedings of the 24 th ACM/IEEE Design Automation Conference, 1987, Miami Beach, Florida, Pages 173 -180. March 6, 2007 39 th Southeastern Symposium on System Theory 4

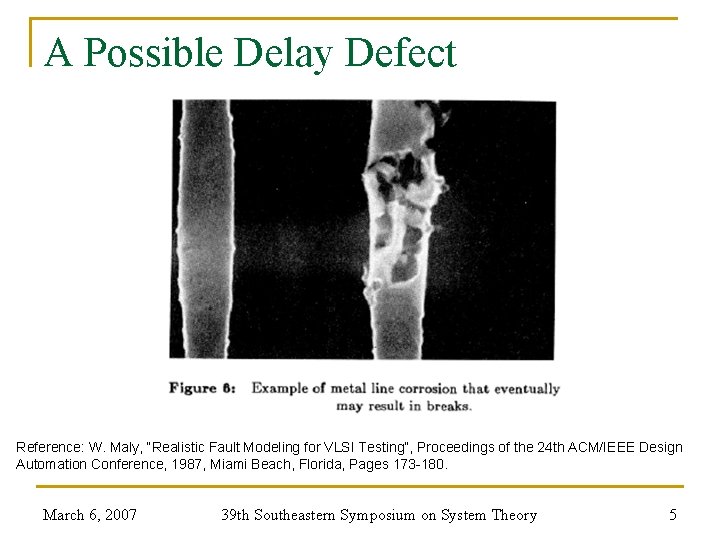

A Possible Delay Defect Reference: W. Maly, “Realistic Fault Modeling for VLSI Testing”, Proceedings of the 24 th ACM/IEEE Design Automation Conference, 1987, Miami Beach, Florida, Pages 173 -180. March 6, 2007 39 th Southeastern Symposium on System Theory 5

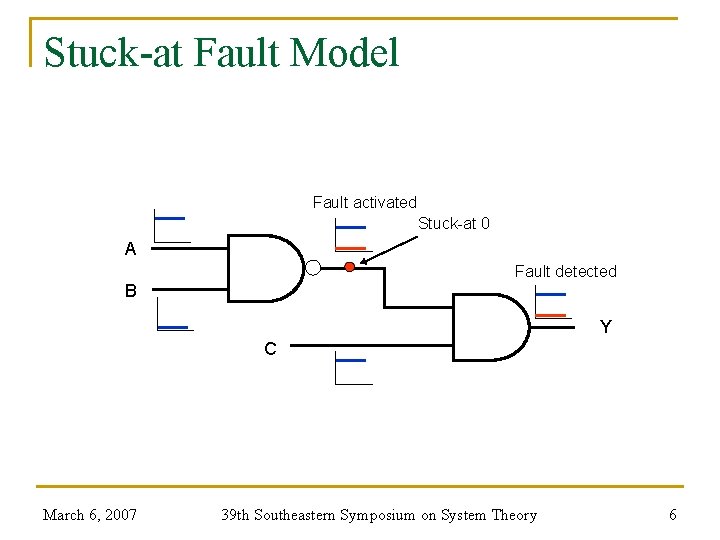

Stuck-at Fault Model Fault activated Stuck-at 0 A Fault detected B Y C March 6, 2007 39 th Southeastern Symposium on System Theory 6

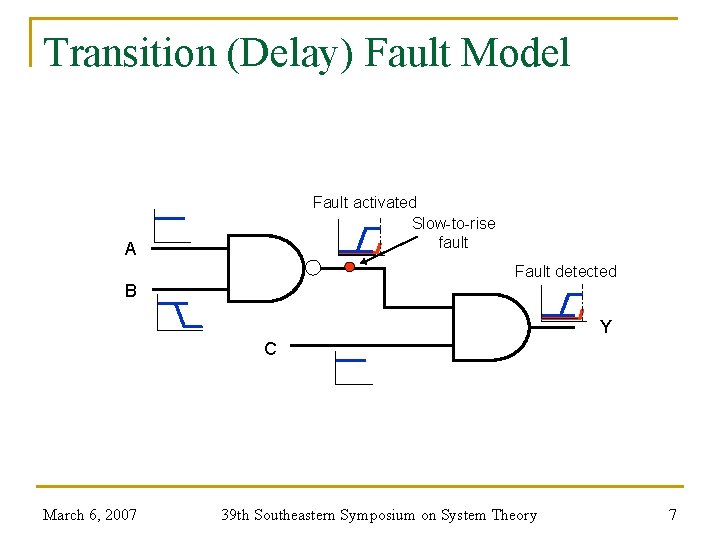

Transition (Delay) Fault Model Fault activated Slow-to-rise fault A Fault detected B Y C March 6, 2007 39 th Southeastern Symposium on System Theory 7

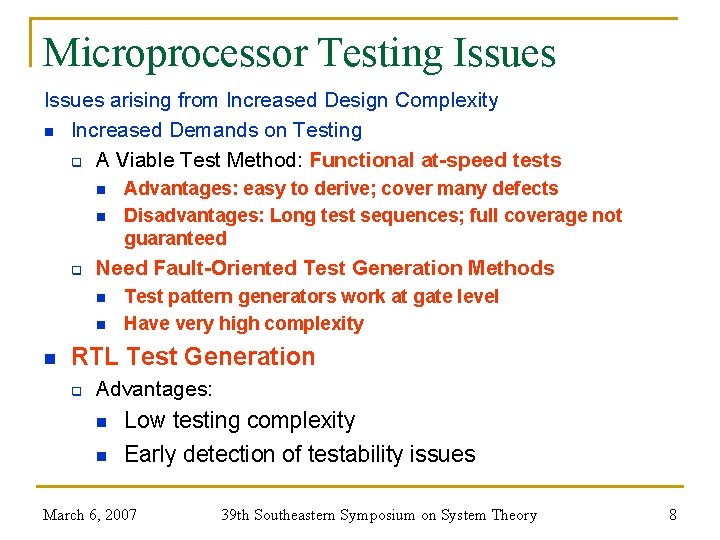

Microprocessor Testing Issues arising from Increased Design Complexity n Increased Demands on Testing q A Viable Test Method: Functional at-speed tests n n q Need Fault-Oriented Test Generation Methods n n n Advantages: easy to derive; cover many defects Disadvantages: Long test sequences; full coverage not guaranteed Test pattern generators work at gate level Have very high complexity RTL Test Generation q Advantages: n n Low testing complexity Early detection of testability issues March 6, 2007 39 th Southeastern Symposium on System Theory 8

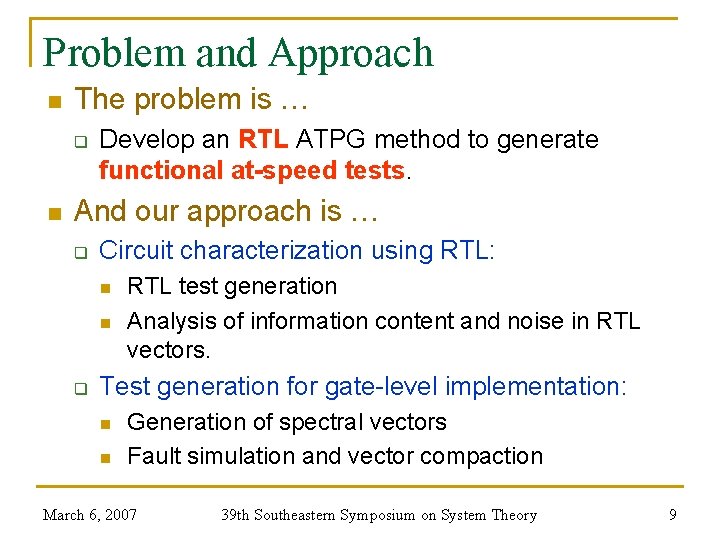

Problem and Approach n The problem is … q n Develop an RTL ATPG method to generate functional at-speed tests. And our approach is … q Circuit characterization using RTL: n n q RTL test generation Analysis of information content and noise in RTL vectors. Test generation for gate-level implementation: n n Generation of spectral vectors Fault simulation and vector compaction March 6, 2007 39 th Southeastern Symposium on System Theory 9

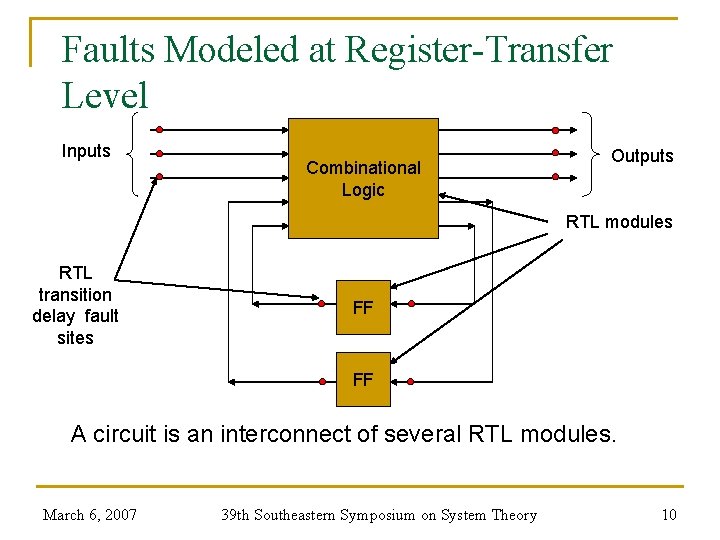

Faults Modeled at Register-Transfer Level Inputs Combinational Logic Outputs RTL modules RTL transition delay fault sites FF FF A circuit is an interconnect of several RTL modules. March 6, 2007 39 th Southeastern Symposium on System Theory 10

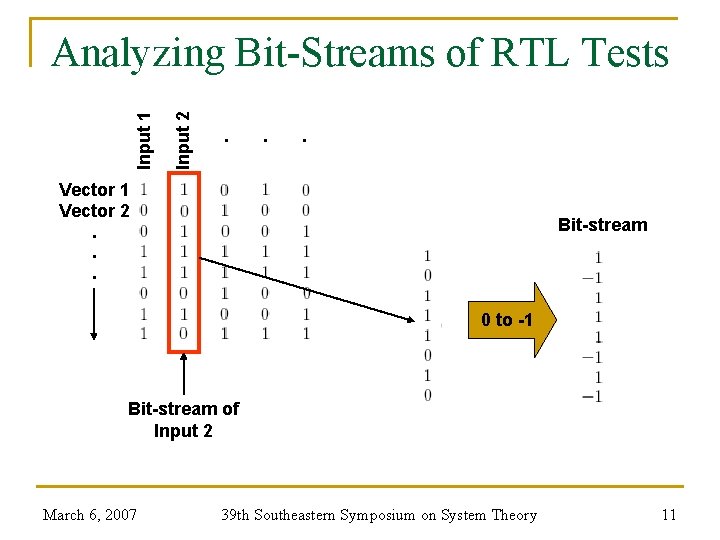

. . . Input 2 Input 1 Analyzing Bit-Streams of RTL Tests Vector 1 Vector 2. . . Bit-stream 0 to -1 Bit-stream of Input 2 March 6, 2007 39 th Southeastern Symposium on System Theory 11

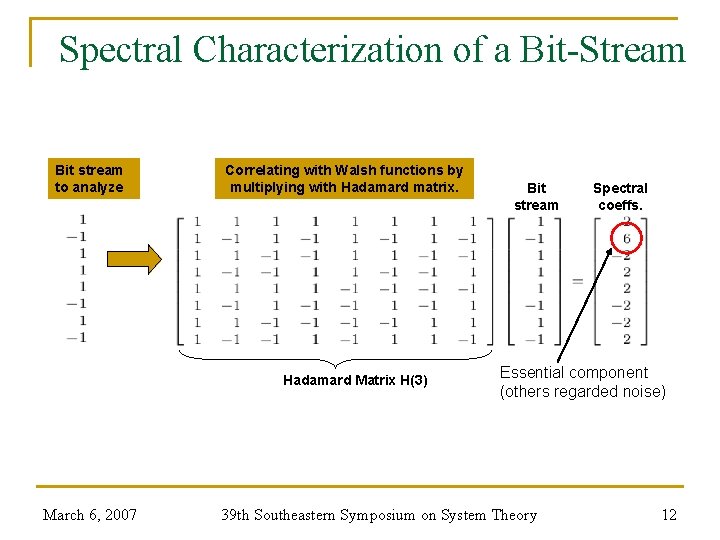

Spectral Characterization of a Bit-Stream Bit stream to analyze Correlating with Walsh functions by multiplying with Hadamard matrix. Hadamard Matrix H(3) March 6, 2007 Bit stream Spectral coeffs. Essential component (others regarded noise) 39 th Southeastern Symposium on System Theory 12

Generation of New Bit-Streams Perturbation Spectral components Generation of new bit-stream by multiplying with Hadamard matrix Essential component retained; noise components randomly perturbed Sign function New bit stream -1 to 0 Bits changed March 6, 2007 39 th Southeastern Symposium on System Theory 13

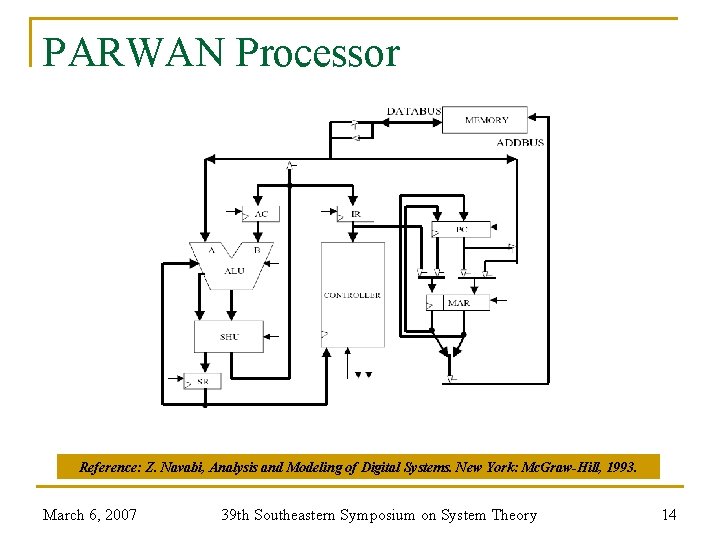

PARWAN Processor Reference: Z. Navabi, Analysis and Modeling of Digital Systems. New York: Mc. Graw-Hill, 1993. March 6, 2007 39 th Southeastern Symposium on System Theory 14

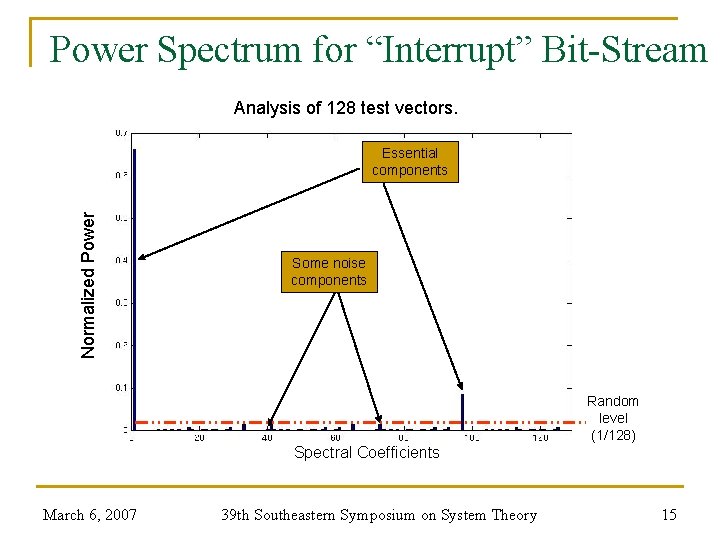

Power Spectrum for “Interrupt” Bit-Stream Analysis of 128 test vectors. Normalized Power Essential components Some noise components Random level (1/128) Spectral Coefficients March 6, 2007 39 th Southeastern Symposium on System Theory 15

![Power Spectrum for “Data. In[5]” Signal Normalized Power Analysis of 128 test vectors. Some Power Spectrum for “Data. In[5]” Signal Normalized Power Analysis of 128 test vectors. Some](http://slidetodoc.com/presentation_image_h2/17e399369f226b3266697eea23537580/image-16.jpg)

Power Spectrum for “Data. In[5]” Signal Normalized Power Analysis of 128 test vectors. Some essential components Some noise components Theoretical random noise level (1/128) Spectral Coefficients March 6, 2007 39 th Southeastern Symposium on System Theory 16

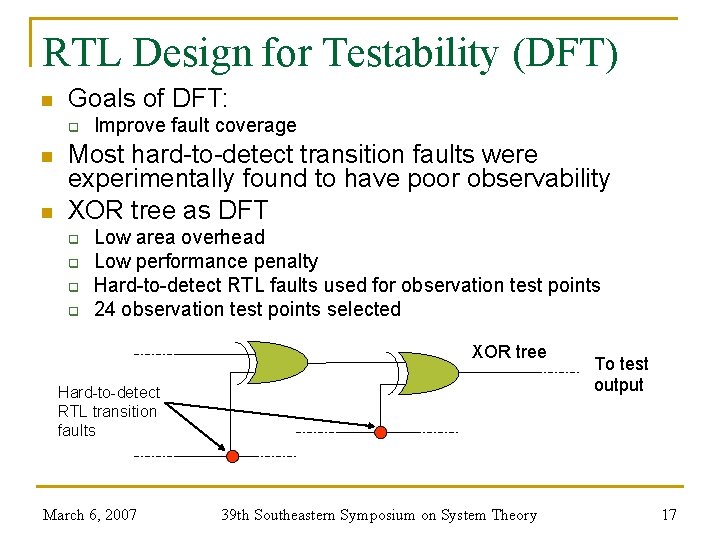

RTL Design for Testability (DFT) n Goals of DFT: q n n Improve fault coverage Most hard-to-detect transition faults were experimentally found to have poor observability XOR tree as DFT q q Low area overhead Low performance penalty Hard-to-detect RTL faults used for observation test points 24 observation test points selected XOR tree Hard-to-detect RTL transition faults March 6, 2007 39 th Southeastern Symposium on System Theory To test output 17

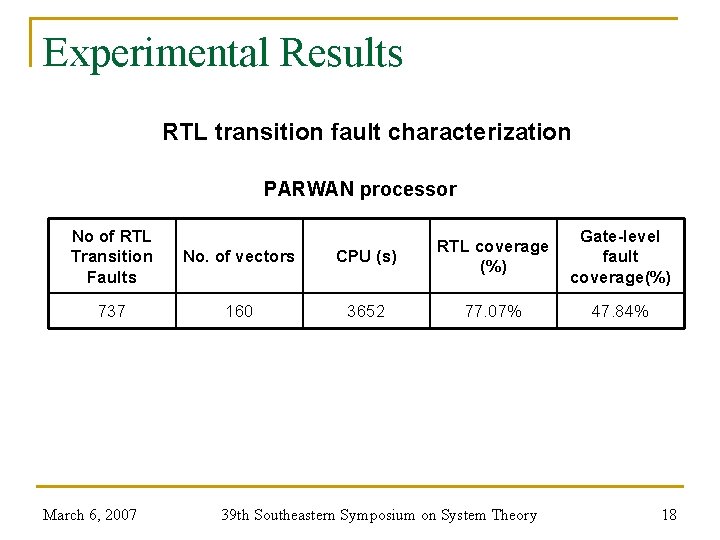

Experimental Results RTL transition fault characterization PARWAN processor No of RTL Transition Faults No. of vectors 737 160 March 6, 2007 CPU (s) RTL coverage (%) Gate-level fault coverage(%) 3652 77. 07% 47. 84% 39 th Southeastern Symposium on System Theory 18

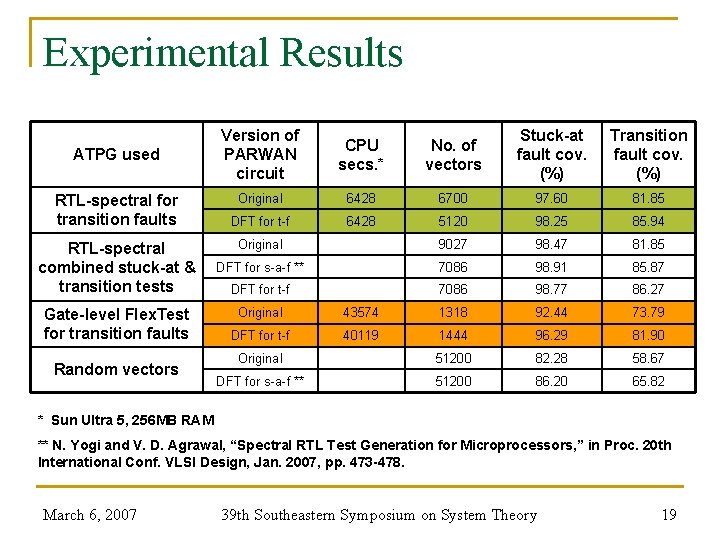

Experimental Results ATPG used RTL-spectral for transition faults RTL-spectral combined stuck-at & transition tests Gate-level Flex. Test for transition faults Random vectors Version of PARWAN circuit CPU secs. * No. of vectors Stuck-at fault cov. (%) Transition fault cov. (%) Original 6428 6700 97. 60 81. 85 DFT for t-f 6428 5120 98. 25 85. 94 Original 9027 98. 47 81. 85 DFT for s-a-f ** 7086 98. 91 85. 87 DFT for t-f 7086 98. 77 86. 27 Original 43574 1318 92. 44 73. 79 DFT for t-f 40119 1444 96. 29 81. 90 Original 51200 82. 28 58. 67 DFT for s-a-f ** 51200 86. 20 65. 82 * Sun Ultra 5, 256 MB RAM ** N. Yogi and V. D. Agrawal, “Spectral RTL Test Generation for Microprocessors, ” in Proc. 20 th International Conf. VLSI Design, Jan. 2007, pp. 473 -478. March 6, 2007 39 th Southeastern Symposium on System Theory 19

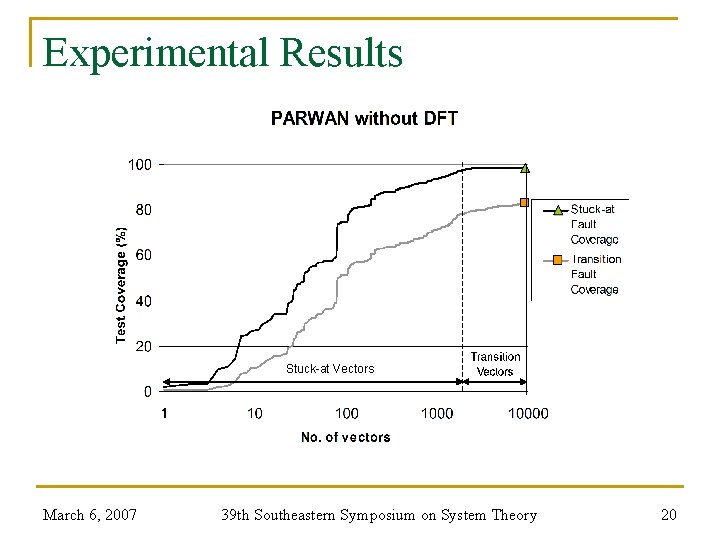

Experimental Results Stuck-at Vectors March 6, 2007 39 th Southeastern Symposium on System Theory 20

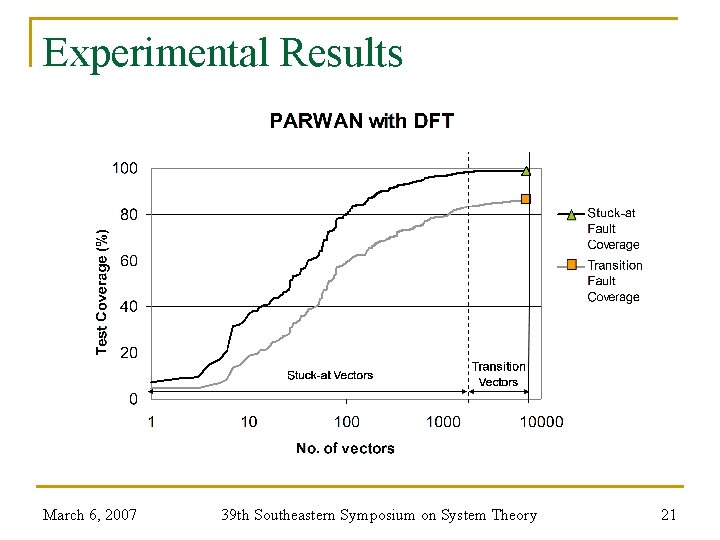

Experimental Results March 6, 2007 39 th Southeastern Symposium on System Theory 21

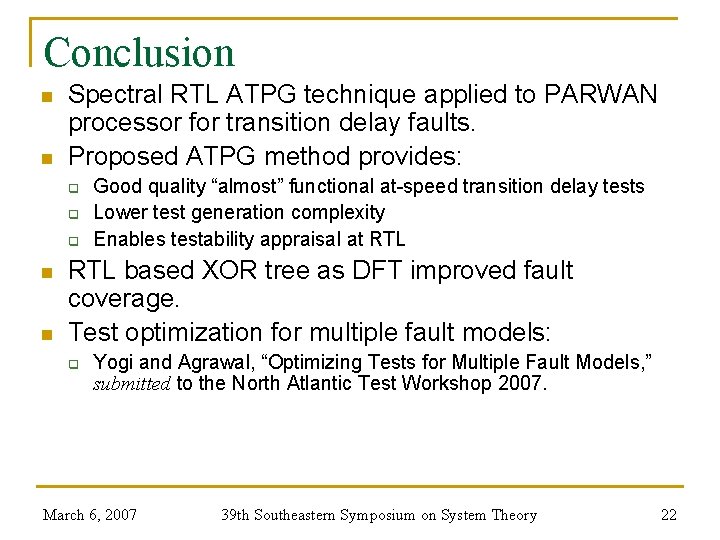

Conclusion n n Spectral RTL ATPG technique applied to PARWAN processor for transition delay faults. Proposed ATPG method provides: q q q n n Good quality “almost” functional at-speed transition delay tests Lower test generation complexity Enables testability appraisal at RTL based XOR tree as DFT improved fault coverage. Test optimization for multiple fault models: q Yogi and Agrawal, “Optimizing Tests for Multiple Fault Models, ” submitted to the North Atlantic Test Workshop 2007. March 6, 2007 39 th Southeastern Symposium on System Theory 22

Thank You ! Questions ? March 6, 2007 39 th Southeastern Symposium on System Theory 23

- Slides: 23