TransistorTransistor Logic and Bi CMOS Dr T Y

Transistor-Transistor Logic and Bi. CMOS Dr. T. Y. Chang NTHU EE 2007. 12. 11_13 Laboratory of Reliable Computing 8 -1

Introduction n Diode-Transistor Logic n Basic TTL NAND gate n Schottky TTL n Bi. CMOS Text Book: D. A. Neamen, Electronic Circuits Analysis And Design, 2 nd ed. Chapters 17. Laboratory of Reliable Computing 2

Parameters Laboratory of Reliable Computing 3

Diode-Transistor Logic-1=5 V Logic-0=0. 1 V Laboratory of Reliable Computing 4

Example 17. 8 @p 1137 n Find Is and Vs in DTL as shown in Fig. 17. 20 with =25. Laboratory of Reliable Computing 5

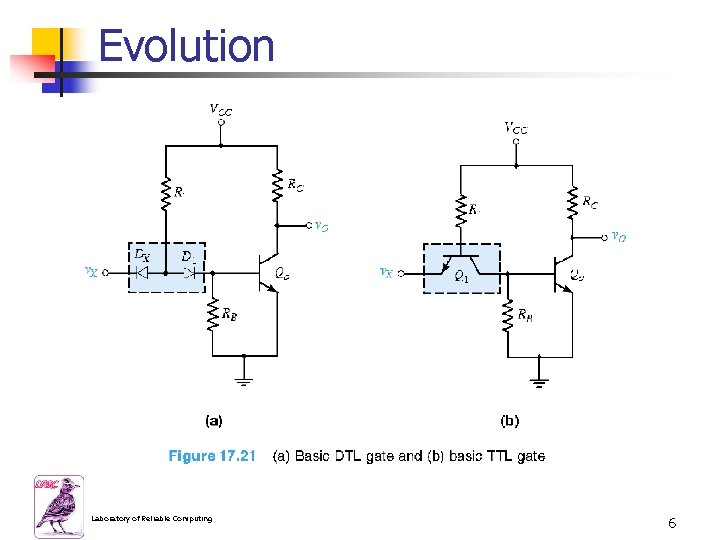

Evolution Laboratory of Reliable Computing 6

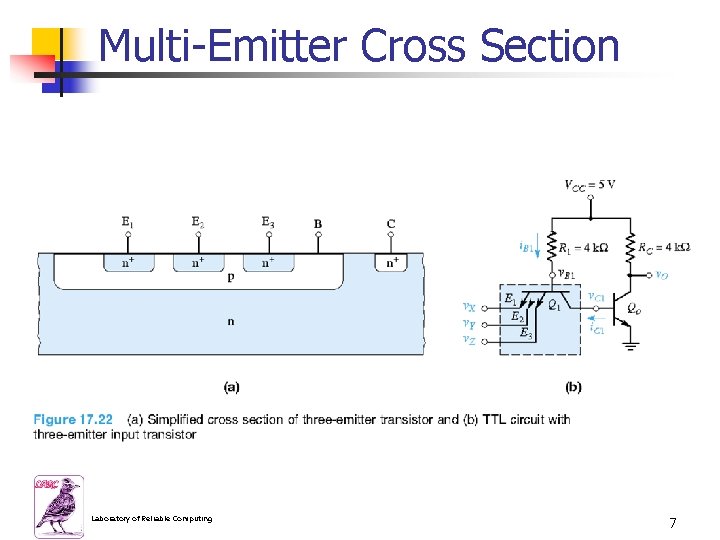

Multi-Emitter Cross Section Laboratory of Reliable Computing 7

TTL Inputs Laboratory of Reliable Computing 8

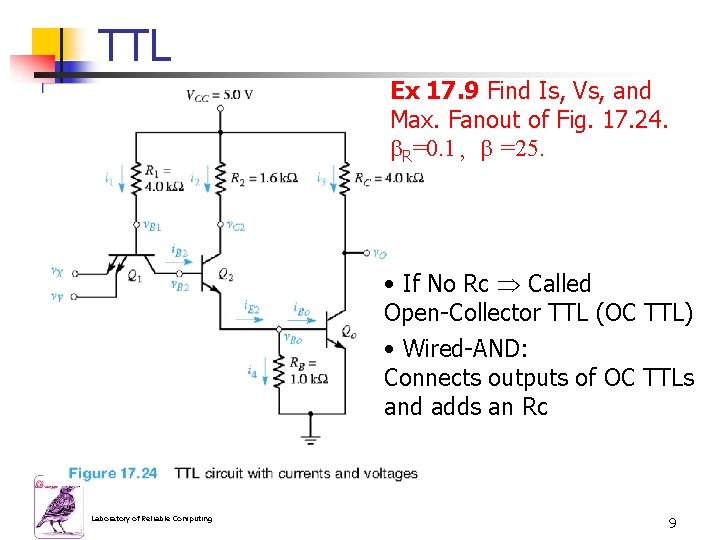

TTL Ex 17. 9 Find Is, Vs, and Max. Fanout of Fig. 17. 24. R=0. 1, =25. • If No Rc Called Open-Collector TTL (OC TTL) • Wired-AND: Connects outputs of OC TTLs and adds an Rc Laboratory of Reliable Computing 9

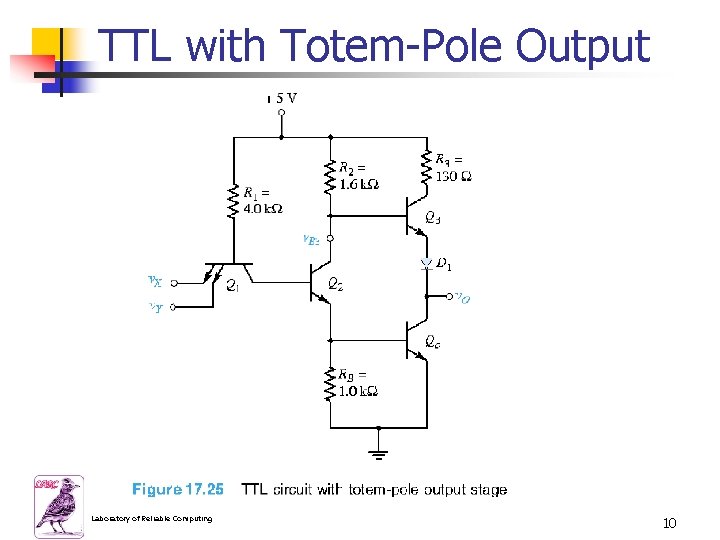

TTL with Totem-Pole Output Laboratory of Reliable Computing 10

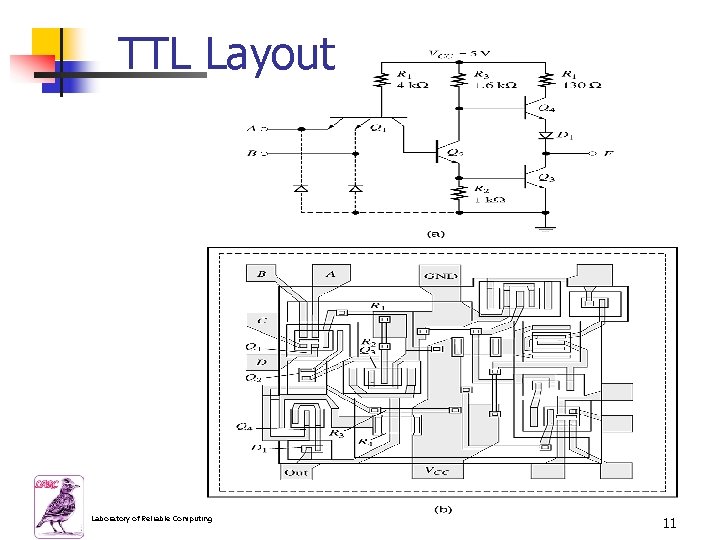

TTL Layout Laboratory of Reliable Computing 11

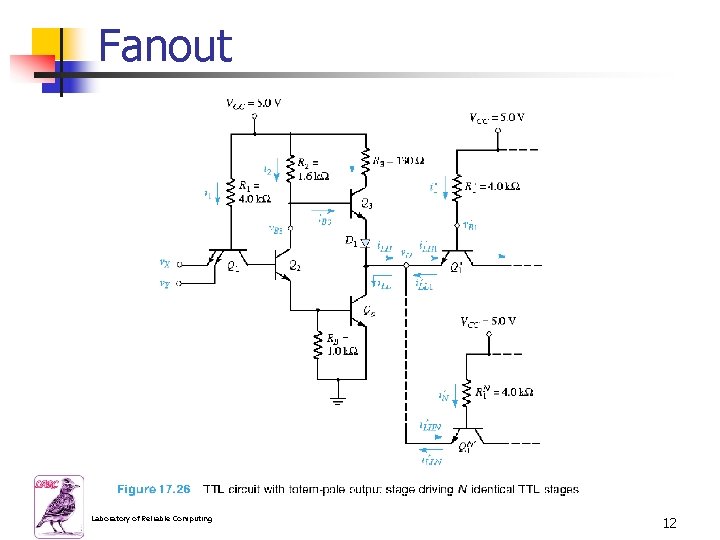

Fanout Laboratory of Reliable Computing 12

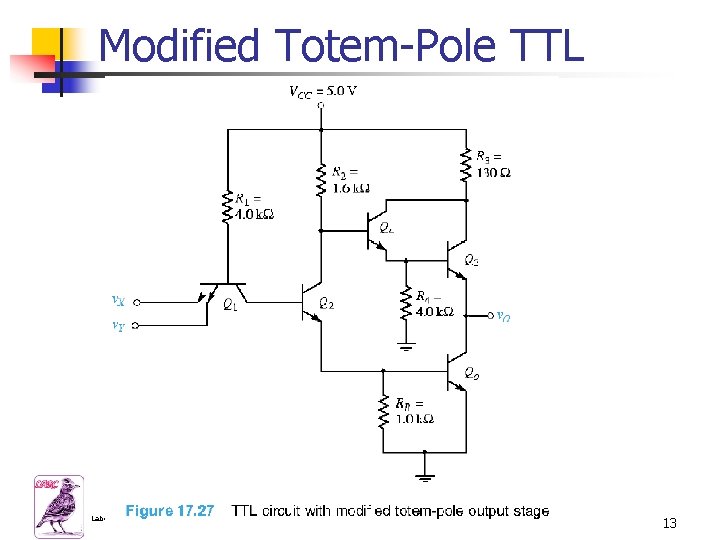

Modified Totem-Pole TTL Laboratory of Reliable Computing 13

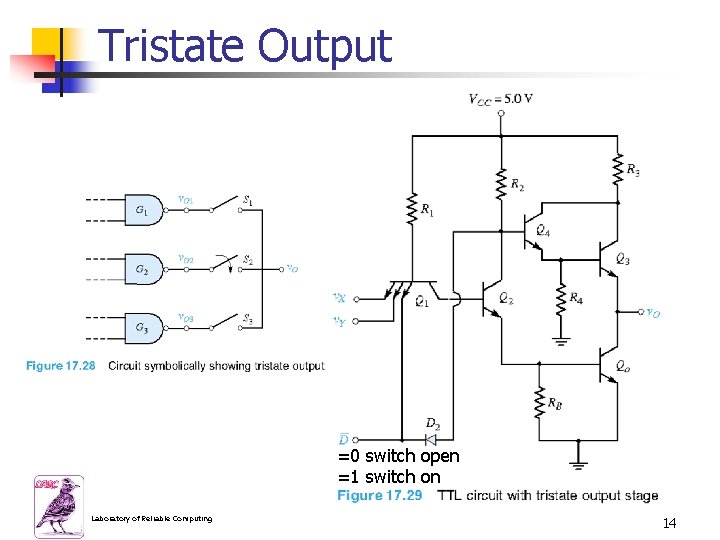

Tristate Output =0 switch open =1 switch on Laboratory of Reliable Computing 14

Schottky BJT Laboratory of Reliable Computing 15

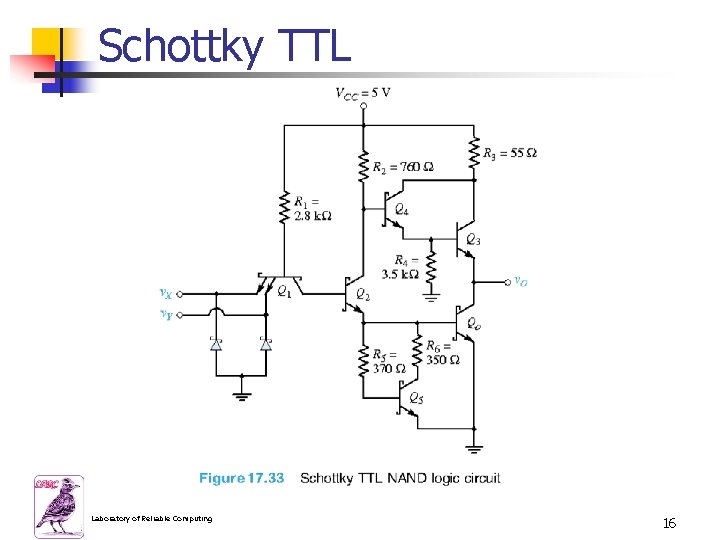

Schottky TTL Laboratory of Reliable Computing 16

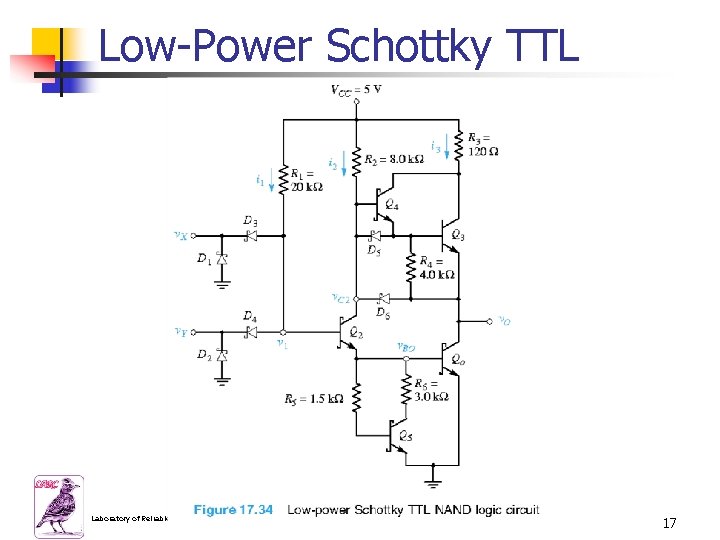

Low-Power Schottky TTL Laboratory of Reliable Computing 17

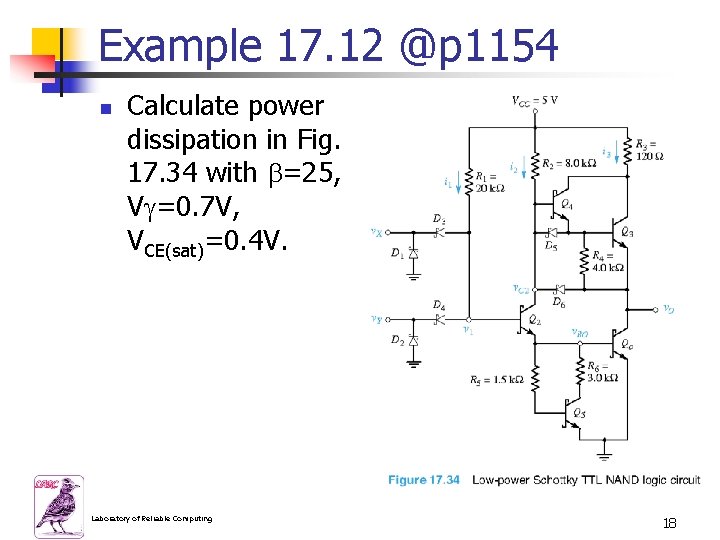

Example 17. 12 @p 1154 n Calculate power dissipation in Fig. 17. 34 with =25, V =0. 7 V, VCE(sat)=0. 4 V. Laboratory of Reliable Computing 18

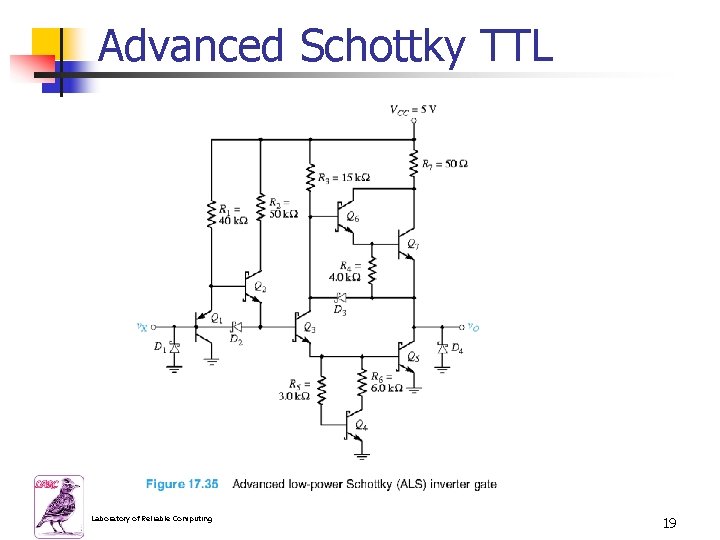

Advanced Schottky TTL Laboratory of Reliable Computing 19

Bi. CMOS n n n BJT n n n Low Power Slower Faster High Power Core: CMOS, Interface: BJT Laboratory of Reliable Computing 20

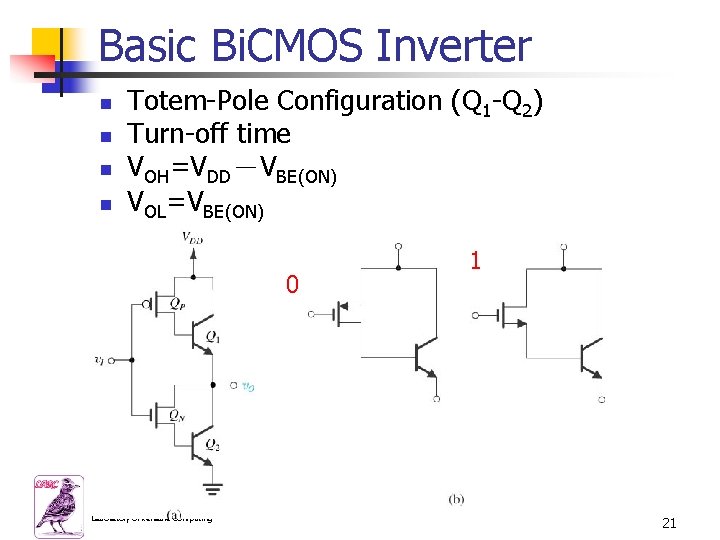

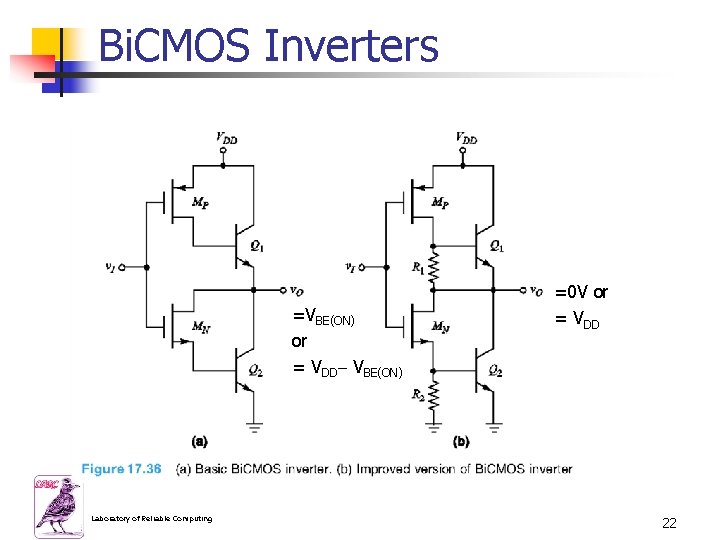

Basic Bi. CMOS Inverter n n Totem-Pole Configuration (Q 1 -Q 2) Turn-off time VOH=VDD-VBE(ON) VOL=VBE(ON) 0 Laboratory of Reliable Computing 1 21

Bi. CMOS Inverters =VBE(ON) or = VDD VBE(ON) Laboratory of Reliable Computing =0 V or = VDD 22

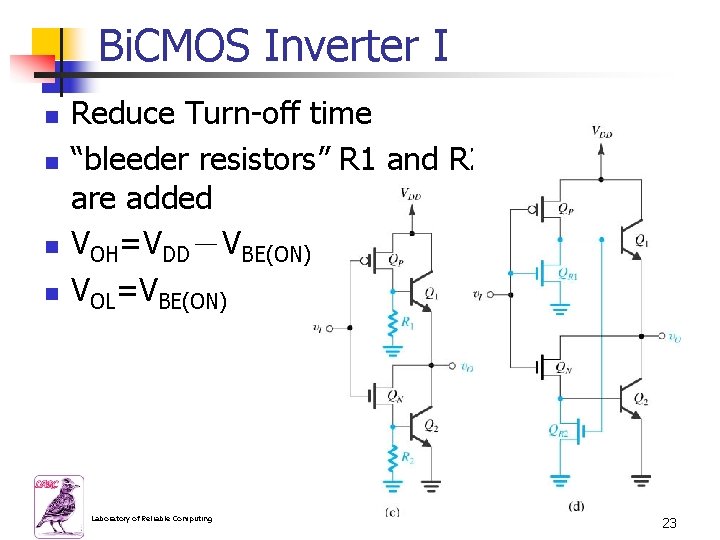

Bi. CMOS Inverter I n n Reduce Turn-off time “bleeder resistors” R 1 and R 2 are added VOH=VDD-VBE(ON) VOL=VBE(ON) Laboratory of Reliable Computing 23

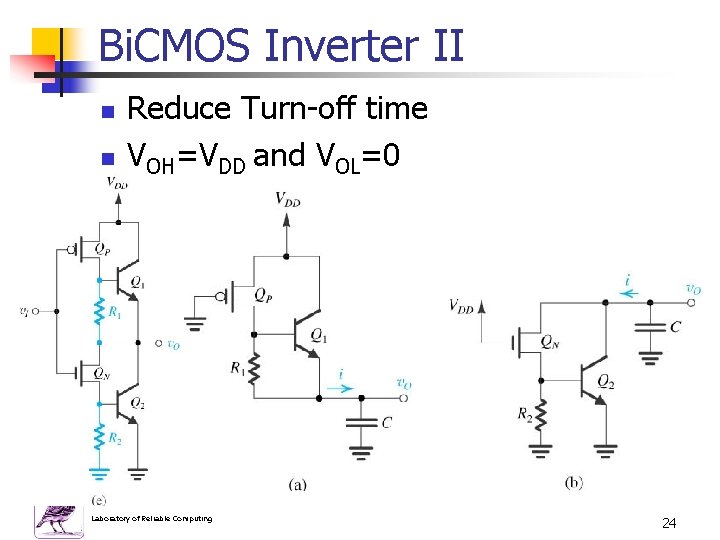

Bi. CMOS Inverter II n n Reduce Turn-off time VOH=VDD and VOL=0 Laboratory of Reliable Computing 24

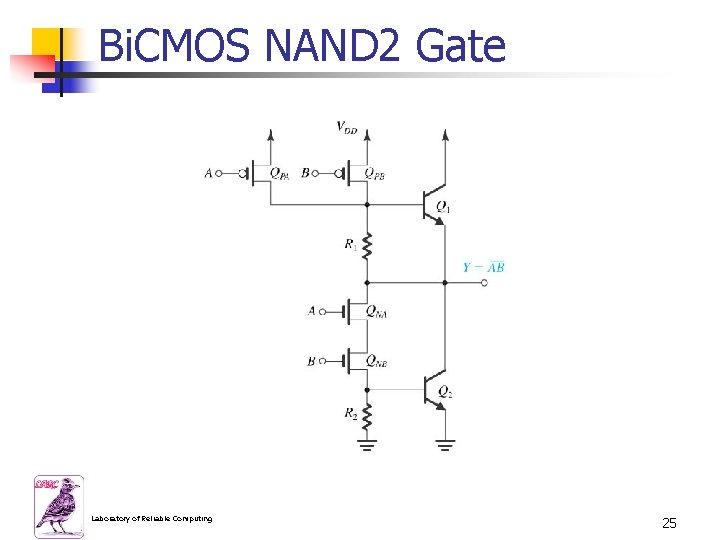

Bi. CMOS NAND 2 Gate Laboratory of Reliable Computing 25

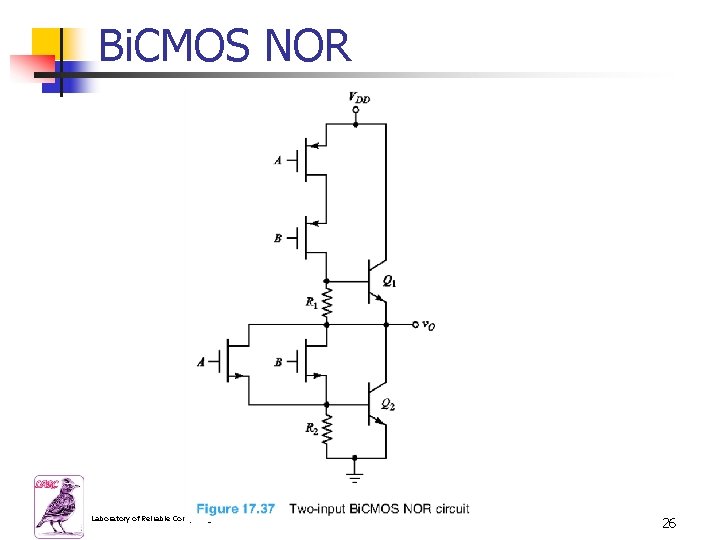

Bi. CMOS NOR Laboratory of Reliable Computing 26

Problem (Not HW) n n Implement E=AB+CD in two-level TTL gates. Implement a Bi. CMOS NAND gate. Laboratory of Reliable Computing 27

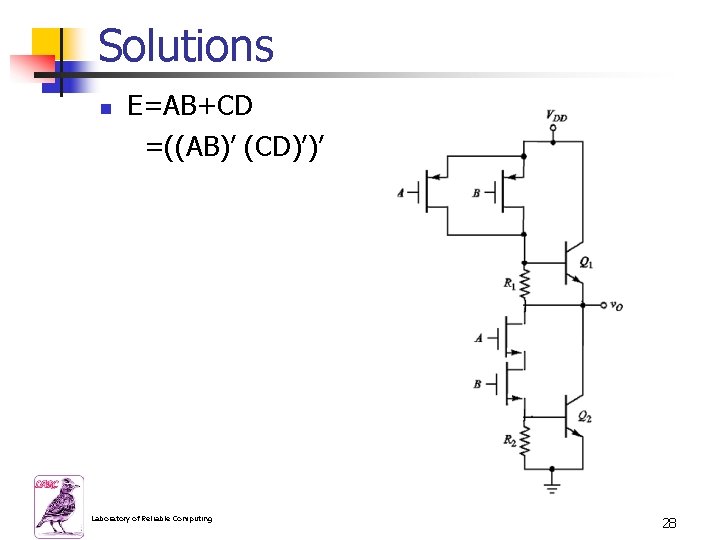

Solutions n E=AB+CD =((AB)’ (CD)’)’ Laboratory of Reliable Computing 28

- Slides: 28