TRANSISTOR AMPLIFIER CONFIGURATION BJT CommonEmitter Amplifier By Syahrul

TRANSISTOR AMPLIFIER CONFIGURATION -BJT Common-Emitter Amplifier. By: Syahrul Ashikin Azmi School of Electrical System Engineering 1

Objectives n n To understand familiar with dc analysis of bipolar transistor circuits. To study common-emitter amplifier in term of ac analysis and familiar with general characteristic of this circuit. 2

Introduction n 3 basic single-transistor amplifier configuration that can be formed are: n n Common-emitter (C-E configuration) Common collector / emitter follower (C-C configuration) Common base (C-B configuration) Each configuration has its own advantages in form of: n n n Input impedance Output impedance Current / voltage amplification 3

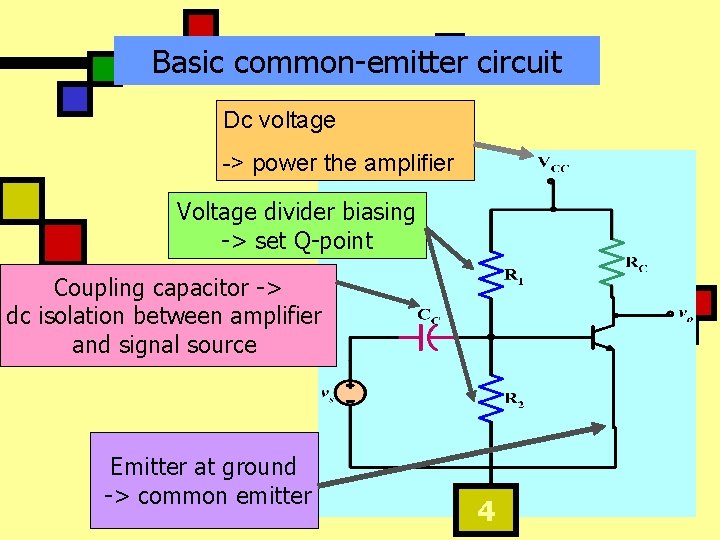

Basic common-emitter circuit Dc voltage -> power the amplifier Voltage divider biasing -> set Q-point Coupling capacitor -> dc isolation between amplifier and signal source Emitter at ground -> common emitter 4

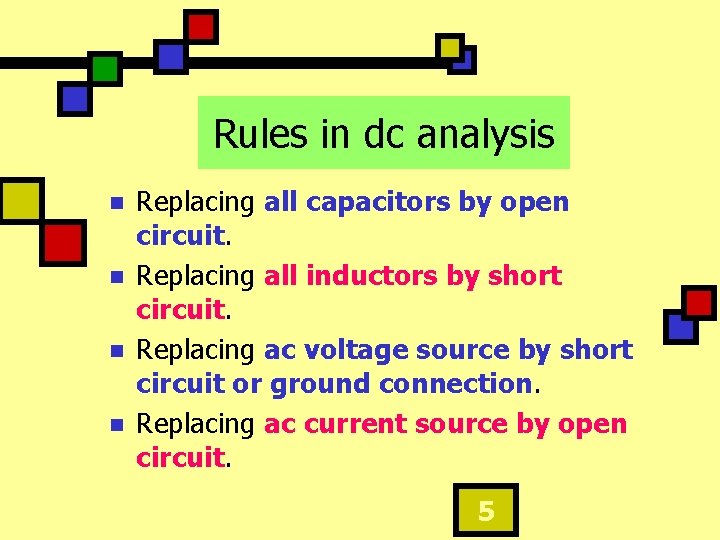

Rules in dc analysis n n Replacing all capacitors by open circuit. Replacing all inductors by short circuit. Replacing ac voltage source by short circuit or ground connection. Replacing ac current source by open circuit. 5

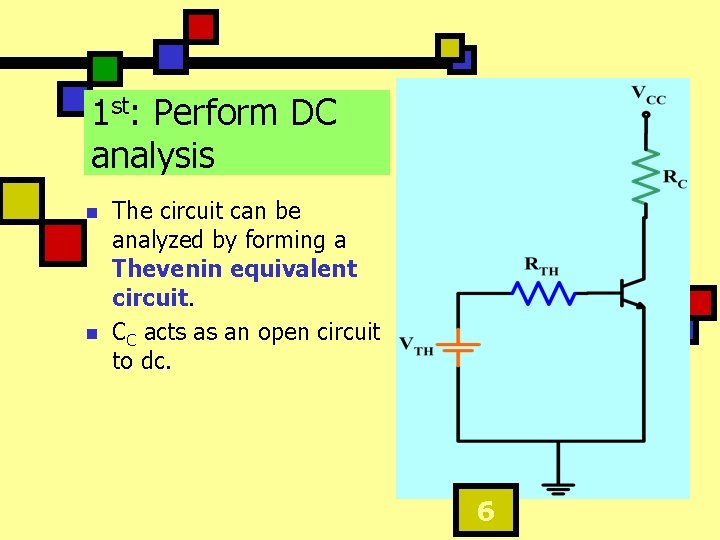

1 st: Perform DC analysis n n The circuit can be analyzed by forming a Thevenin equivalent circuit. CC acts as an open circuit to dc. 6

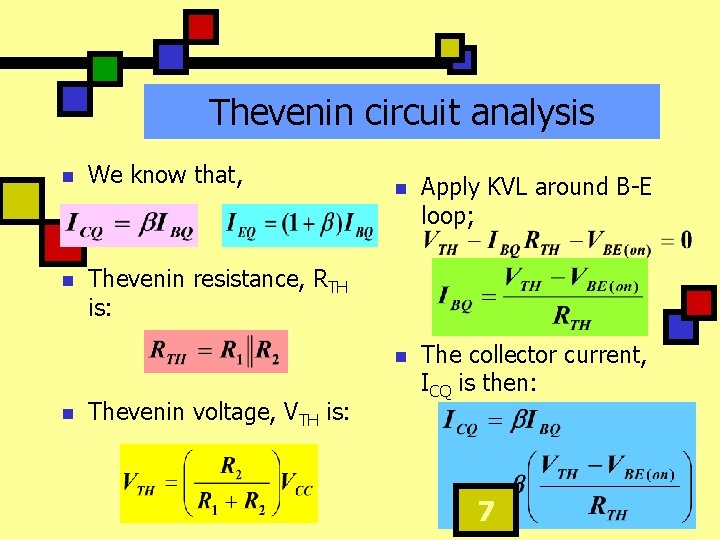

Thevenin circuit analysis n We know that, n Thevenin resistance, RTH is: n Thevenin voltage, VTH is: n Apply KVL around B-E loop; n The collector current, ICQ is then: 7

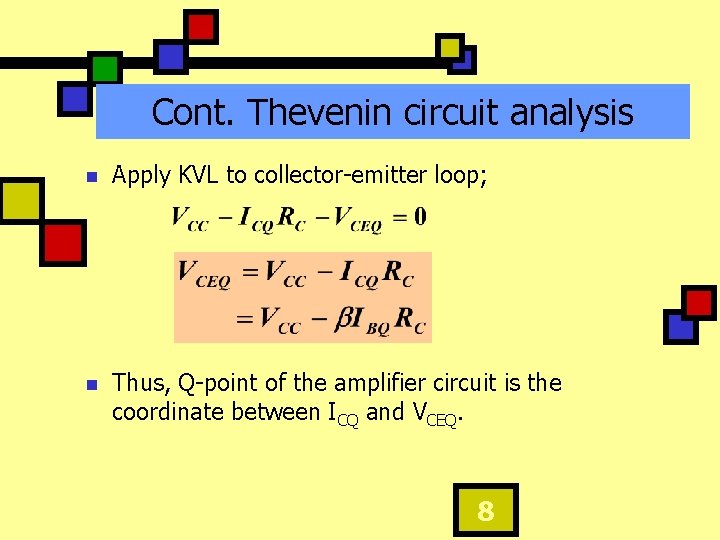

Cont. Thevenin circuit analysis n Apply KVL to collector-emitter loop; n Thus, Q-point of the amplifier circuit is the coordinate between ICQ and VCEQ. 8

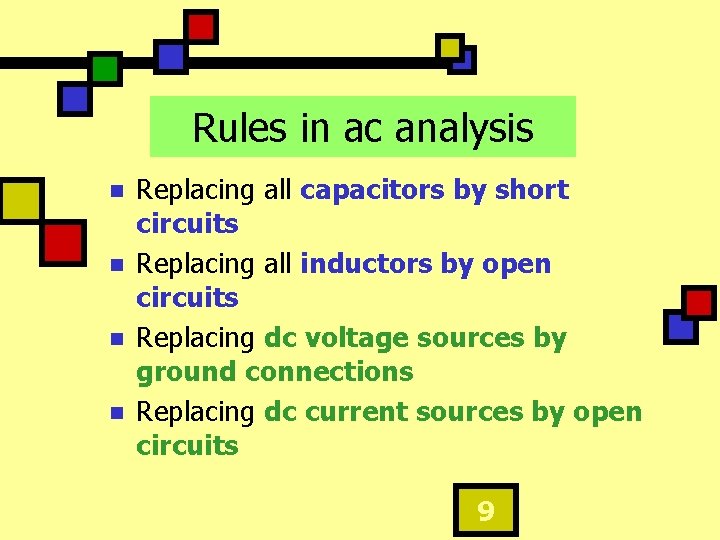

Rules in ac analysis n n Replacing all capacitors by short circuits Replacing all inductors by open circuits Replacing dc voltage sources by ground connections Replacing dc current sources by open circuits 9

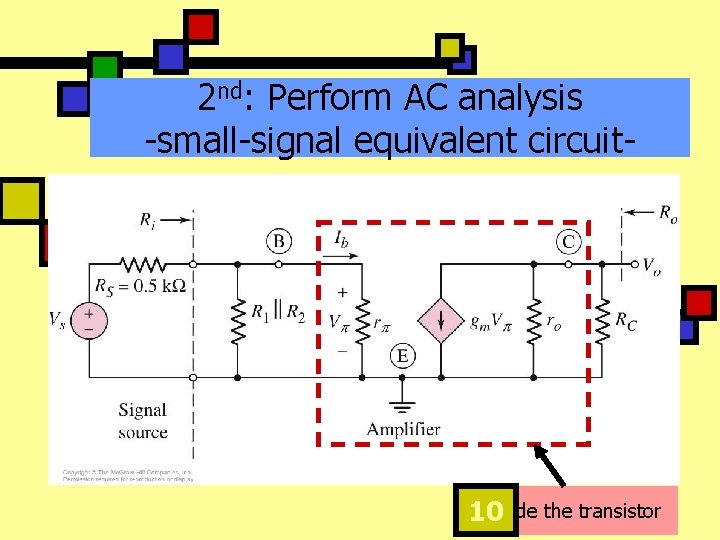

2 nd: Perform AC analysis -small-signal equivalent circuit- Inside the transistor 10

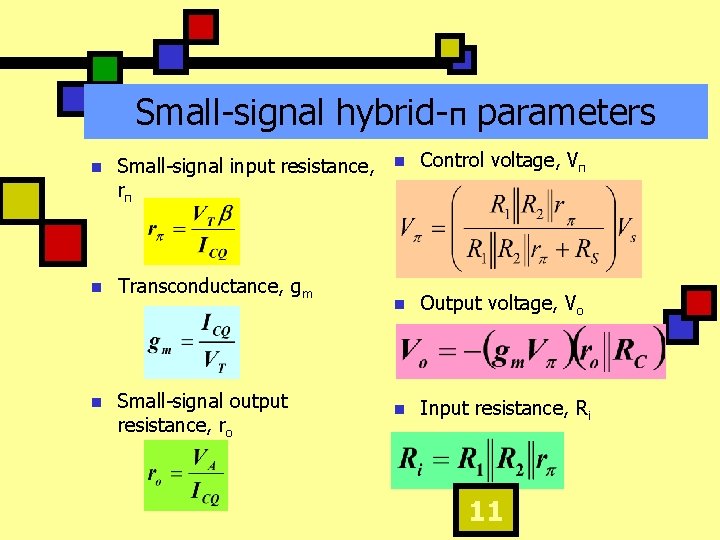

Small-signal hybrid-π parameters n Small-signal input resistance, rπ n Transconductance, gm n Small-signal output resistance, ro n Control voltage, Vπ n Output voltage, Vo n Input resistance, Ri 11

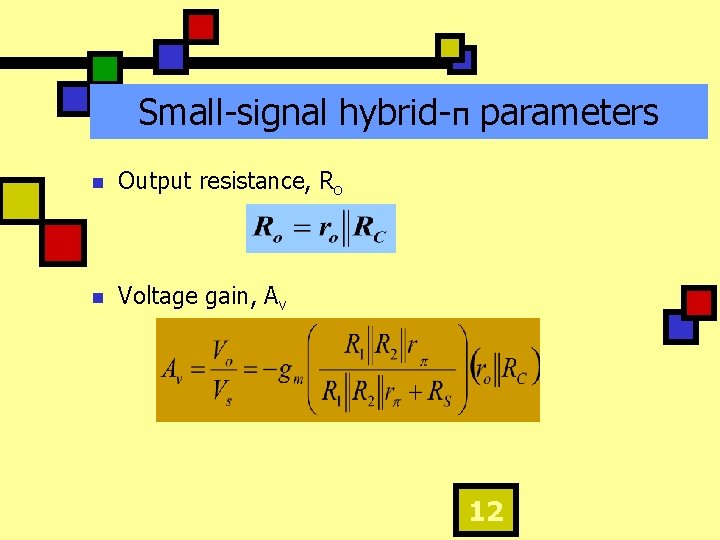

Small-signal hybrid-π parameters n Output resistance, Ro n Voltage gain, Av 12

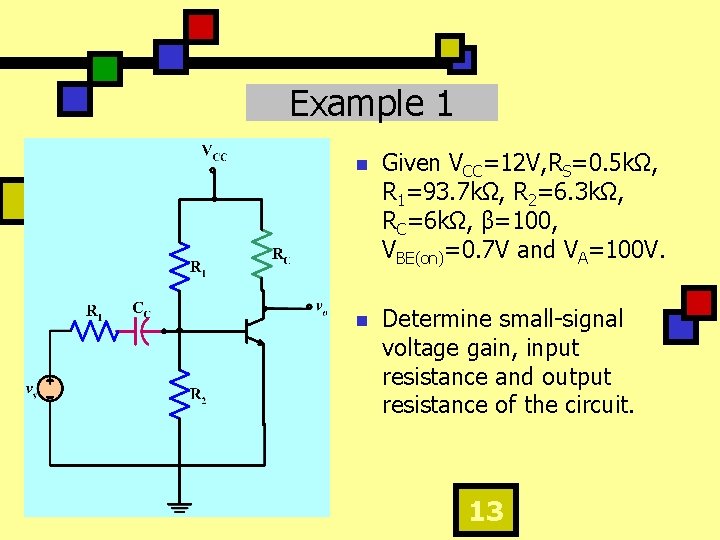

Example 1 n Given VCC=12 V, RS=0. 5 kΩ, R 1=93. 7 kΩ, R 2=6. 3 kΩ, RC=6 kΩ, β=100, VBE(on)=0. 7 V and VA=100 V. n Determine small-signal voltage gain, input resistance and output resistance of the circuit. 13

Solution Example 1 n n 1 st step: DC solution Find Q-point values. ICQ = 0. 95 m. A VCEQ=6. 31 V. 14

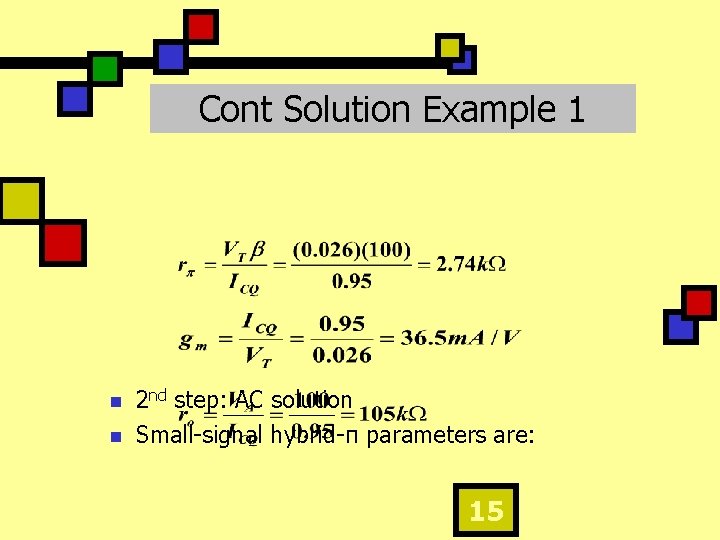

Cont Solution Example 1 n n 2 nd step: AC solution Small-signal hybrid-π parameters are: 15

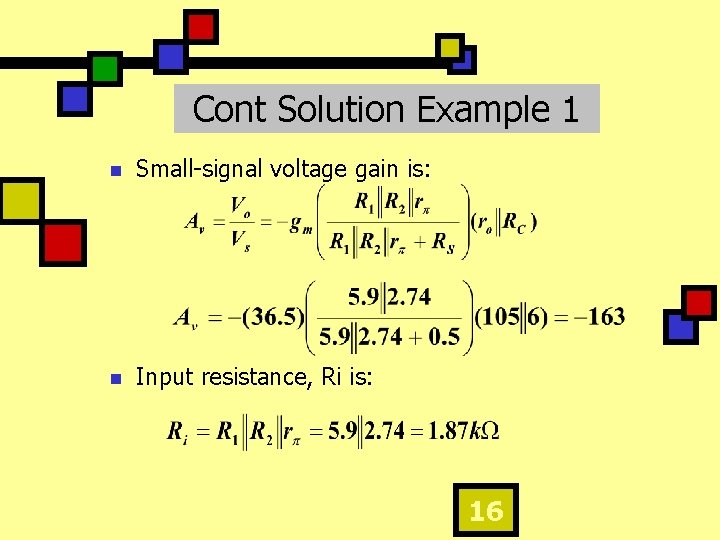

Cont Solution Example 1 n Small-signal voltage gain is: n Input resistance, Ri is: 16

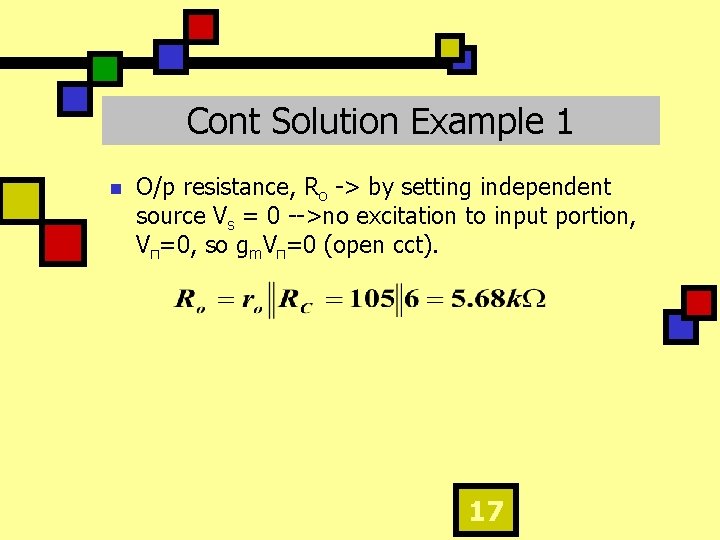

Cont Solution Example 1 n O/p resistance, Ro -> by setting independent source Vs = 0 -->no excitation to input portion, Vπ=0, so gm. Vπ=0 (open cct). 17

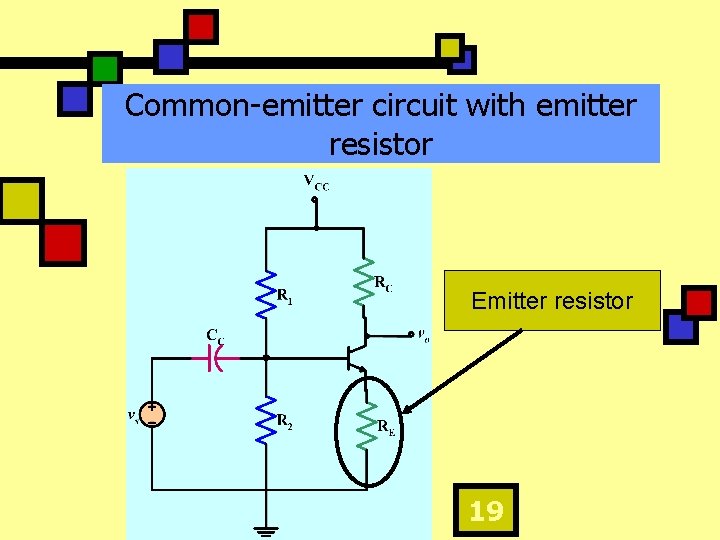

Common-emitter circuit with emitter resistor n n n Why we need to add emitter resistor, RE in the circuit design? Without RE, when β increases or decreases -> ICQ and VCEQ also vary, thus Q-point will be shifted and makes the circuit unstable. By adding RE, there will be not much shift in Qpoint is stabilized even with variation of β. Moreover, the voltage gain is less dependent on transistor current gain in ac analysis. 18

Common-emitter circuit with emitter resistor Emitter resistor 19

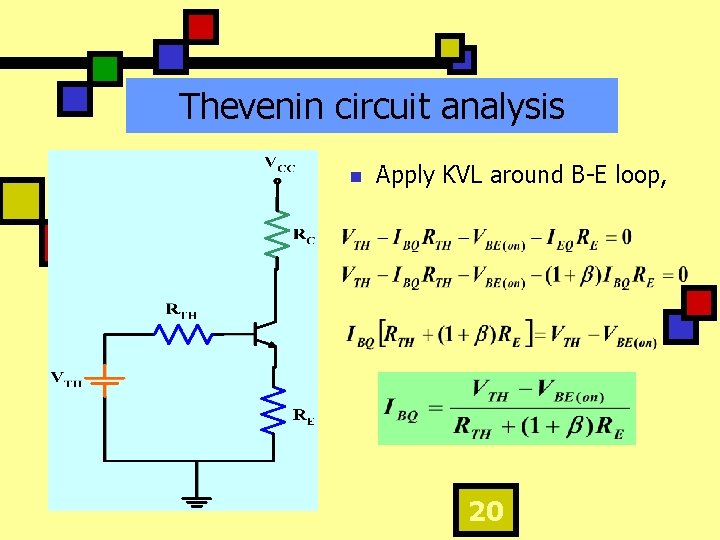

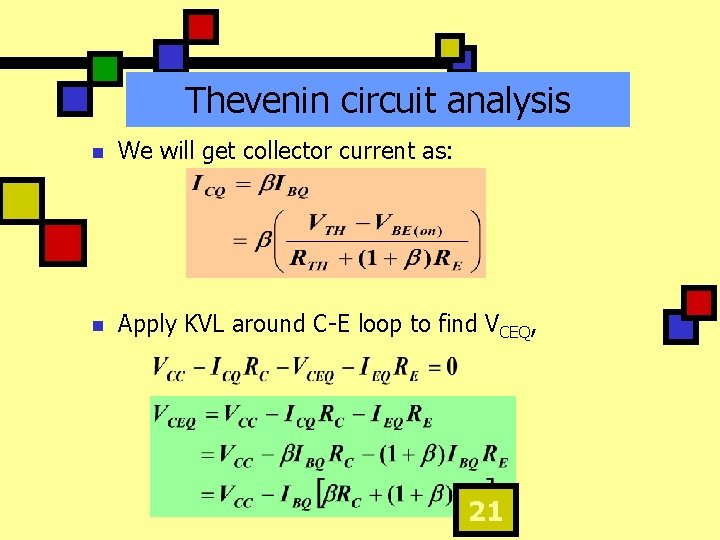

Thevenin circuit analysis n Apply KVL around B-E loop, 20

Thevenin circuit analysis n We will get collector current as: n Apply KVL around C-E loop to find VCEQ, 21

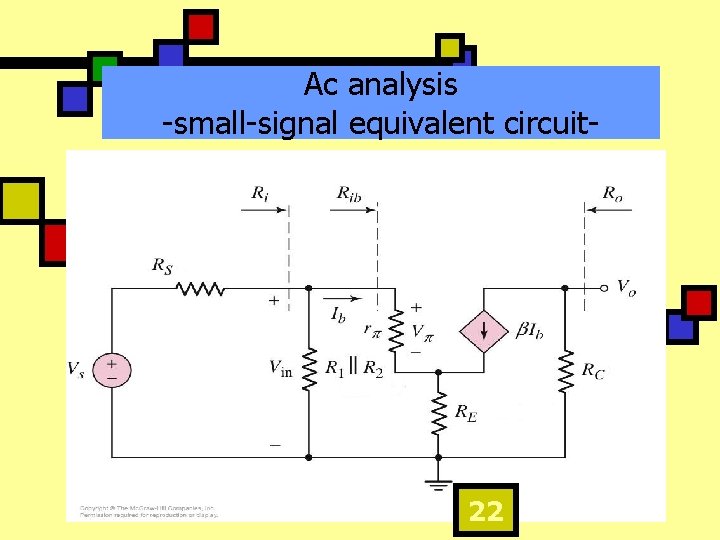

Ac analysis -small-signal equivalent circuit- 22

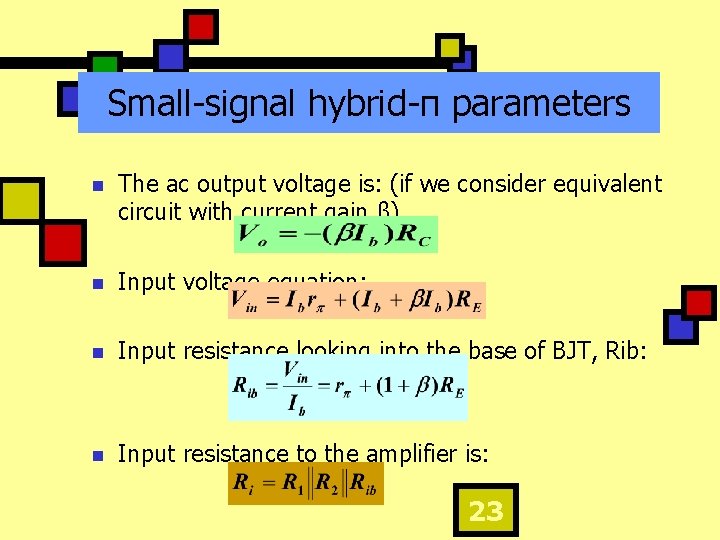

Small-signal hybrid-π parameters n The ac output voltage is: (if we consider equivalent circuit with current gain β) n Input voltage equation: n Input resistance looking into the base of BJT, Rib: n Input resistance to the amplifier is: 23

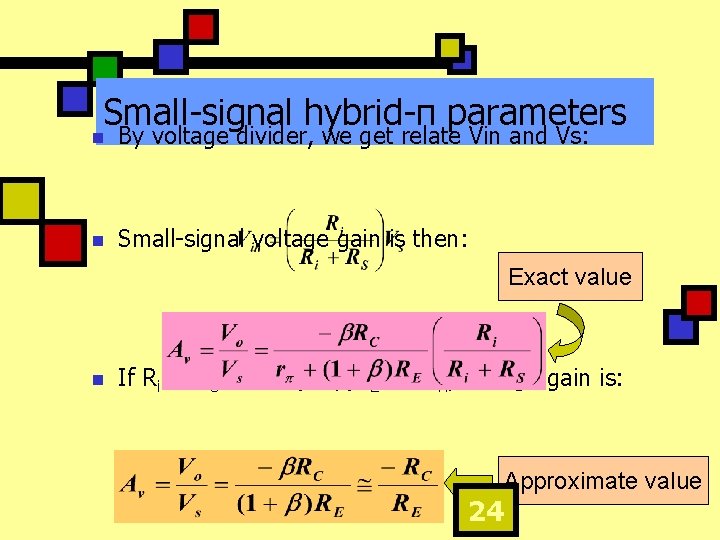

Small-signal hybrid-π parameters n By voltage divider, we get relate Vin and Vs: n Small-signal voltage gain is then: Exact value n If Ri>>RS and if (1+β)RE >> rπ, voltage gain is: Approximate value 24

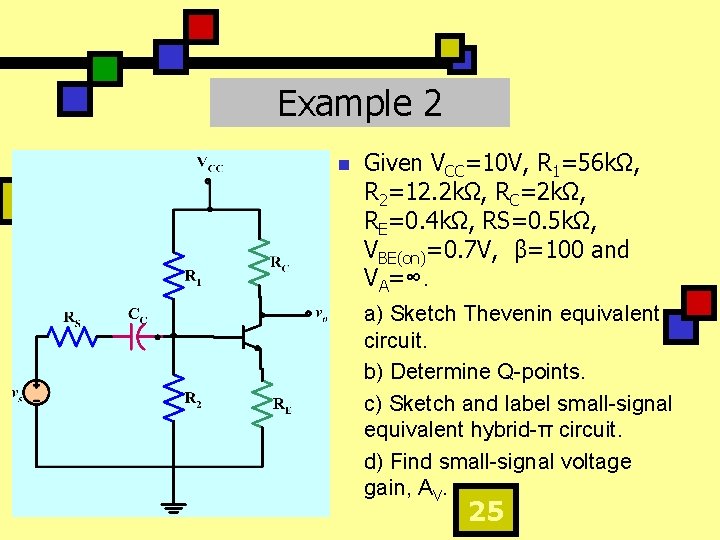

Example 2 n Given VCC=10 V, R 1=56 kΩ, R 2=12. 2 kΩ, RC=2 kΩ, RE=0. 4 kΩ, RS=0. 5 kΩ, VBE(on)=0. 7 V, β=100 and VA=∞. a) Sketch Thevenin equivalent circuit. b) Determine Q-points. c) Sketch and label small-signal equivalent hybrid-π circuit. d) Find small-signal voltage gain, AV. 25

Common-emitter circuit with positive and negative voltage biasing n Biasing with dual supplies in desirable in some applications because: n n Eliminate coupling capacitor Allow dc input voltages as input signals. 26

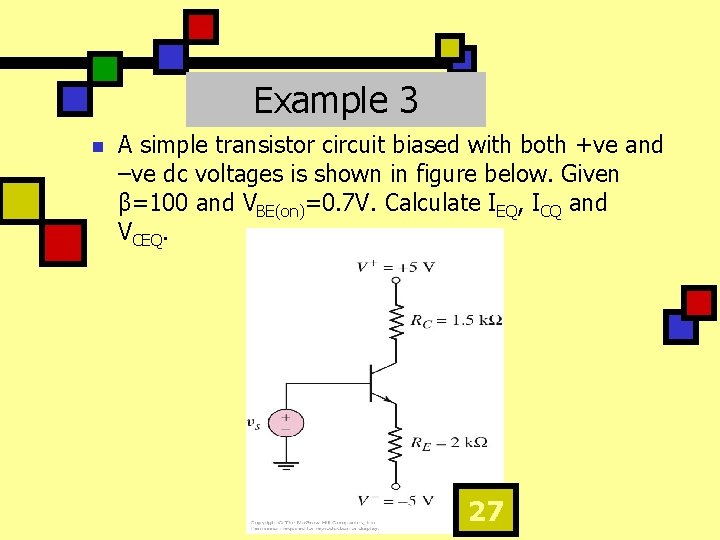

Example 3 n A simple transistor circuit biased with both +ve and –ve dc voltages is shown in figure below. Given β=100 and VBE(on)=0. 7 V. Calculate IEQ, ICQ and VCEQ. 27

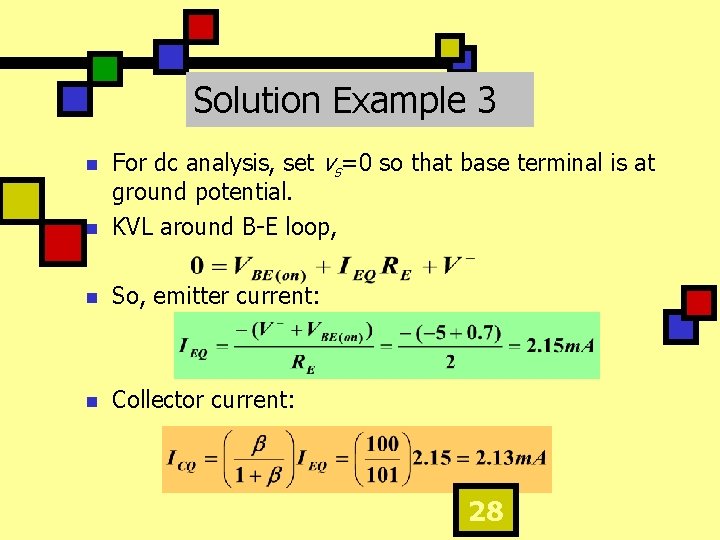

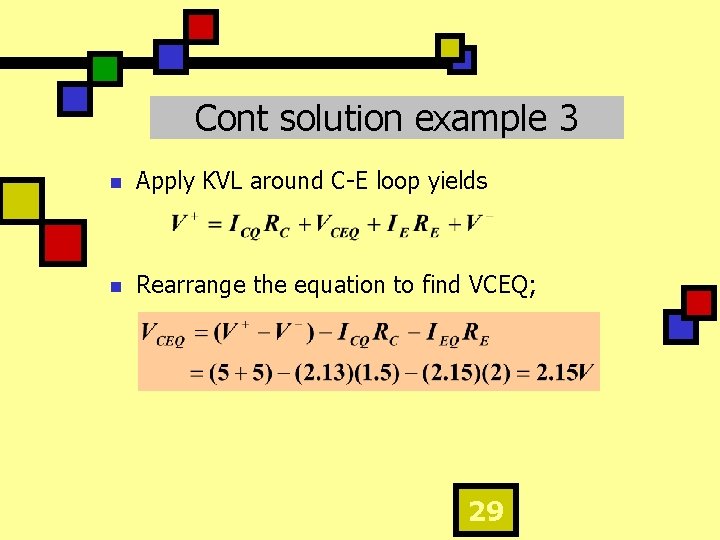

Solution Example 3 n For dc analysis, set vs=0 so that base terminal is at ground potential. KVL around B-E loop, n So, emitter current: n Collector current: n 28

Cont solution example 3 n Apply KVL around C-E loop yields n Rearrange the equation to find VCEQ; 29

Example 4 n Let β=120, R 1=175 kΩ, R 2=250 kΩ, RC=10 kΩ, RE=20 kΩ and VBE(on)=0. 7 V. n For the given circuit, i) Find RTH, VTH and Q -points. ii) Sketch dc load line 30

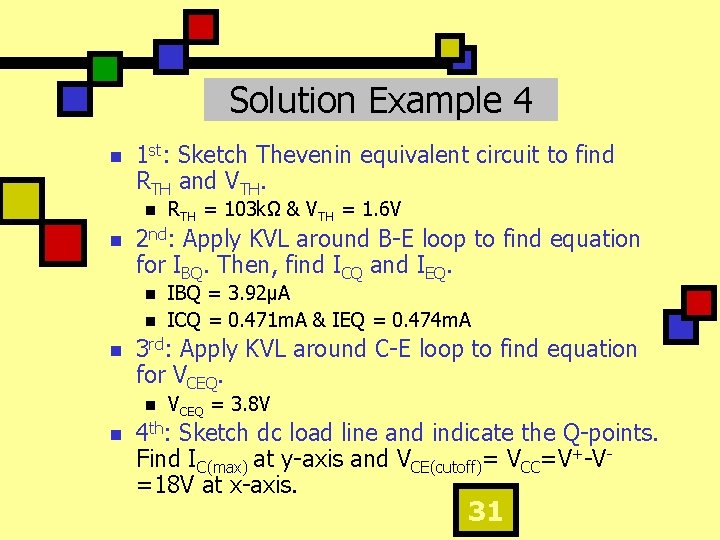

Solution Example 4 n 1 st: Sketch Thevenin equivalent circuit to find RTH and VTH. n n 2 nd: Apply KVL around B-E loop to find equation for IBQ. Then, find ICQ and IEQ. n n n IBQ = 3. 92μA ICQ = 0. 471 m. A & IEQ = 0. 474 m. A 3 rd: Apply KVL around C-E loop to find equation for VCEQ. n n RTH = 103 kΩ & VTH = 1. 6 V VCEQ = 3. 8 V 4 th: Sketch dc load line and indicate the Q-points. Find IC(max) at y-axis and VCE(cutoff)= VCC=V+-V=18 V at x-axis. 31

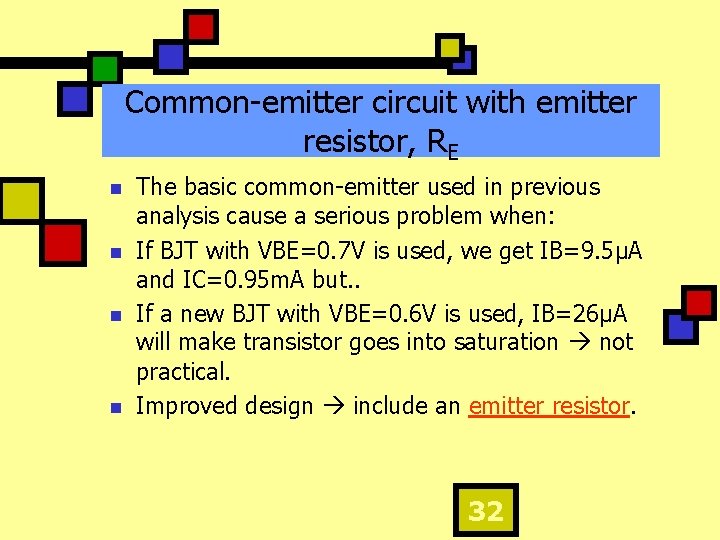

Common-emitter circuit with emitter resistor, RE n n The basic common-emitter used in previous analysis cause a serious problem when: If BJT with VBE=0. 7 V is used, we get IB=9. 5μA and IC=0. 95 m. A but. . If a new BJT with VBE=0. 6 V is used, IB=26μA will make transistor goes into saturation not practical. Improved design include an emitter resistor. 32

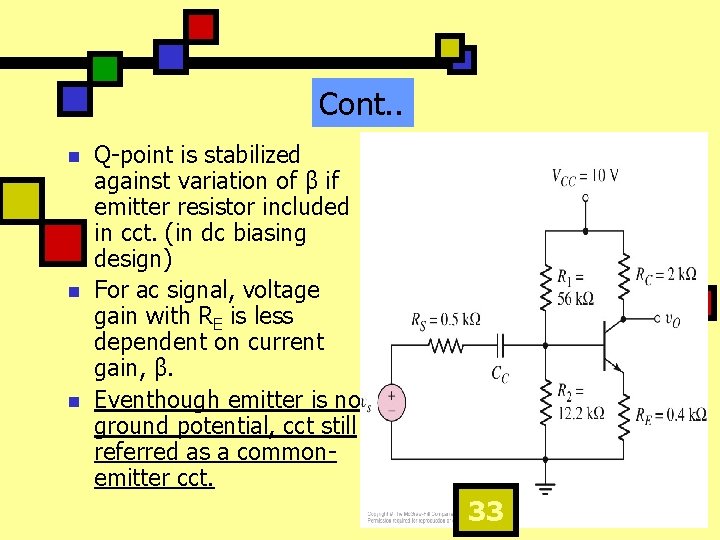

Cont. . n n n Q-point is stabilized against variation of β if emitter resistor included in cct. (in dc biasing design) For ac signal, voltage gain with RE is less dependent on current gain, β. Eventhough emitter is not ground potential, cct still referred as a commonemitter cct. 33

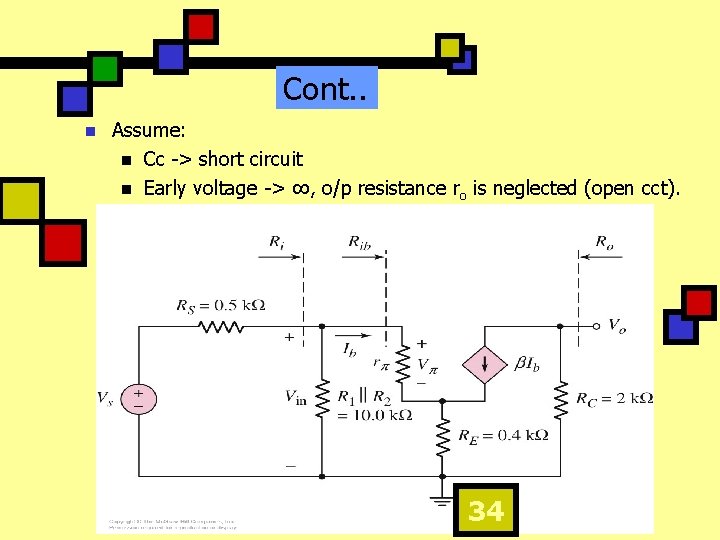

Cont. . n Assume: n Cc -> short circuit n Early voltage -> ∞, o/p resistance ro is neglected (open cct). 34

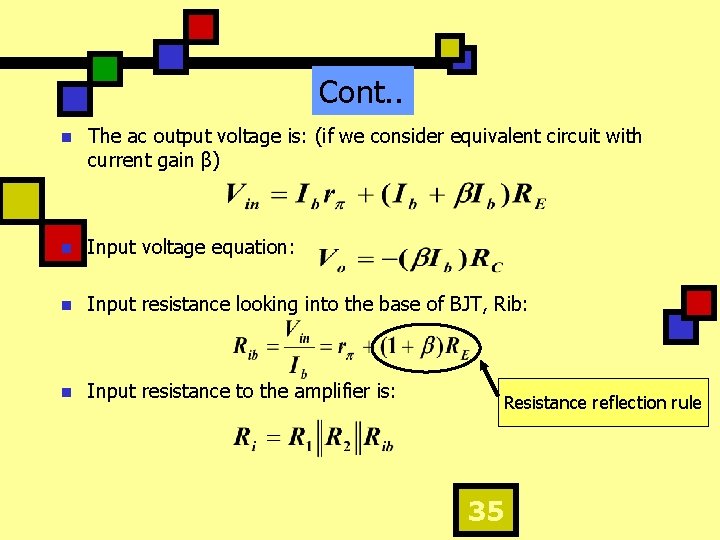

Cont. . n The ac output voltage is: (if we consider equivalent circuit with current gain β) n Input voltage equation: n Input resistance looking into the base of BJT, Rib: n Input resistance to the amplifier is: Resistance reflection rule 35

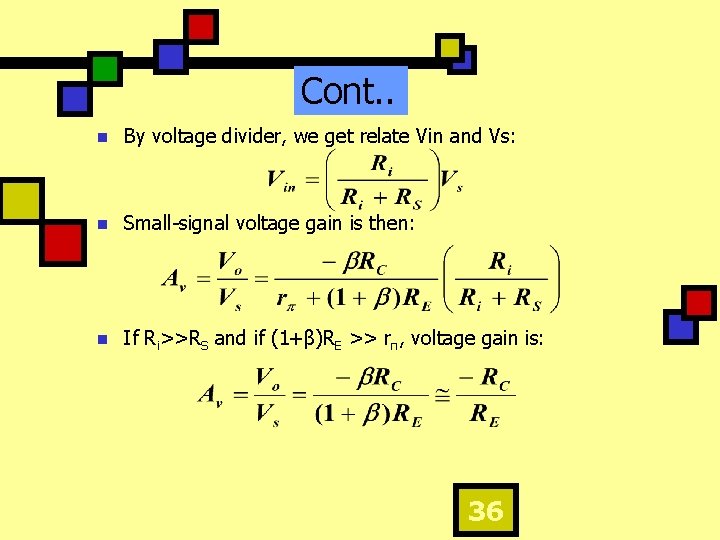

Cont. . n By voltage divider, we get relate Vin and Vs: n Small-signal voltage gain is then: n If Ri>>RS and if (1+β)RE >> rπ, voltage gain is: 36

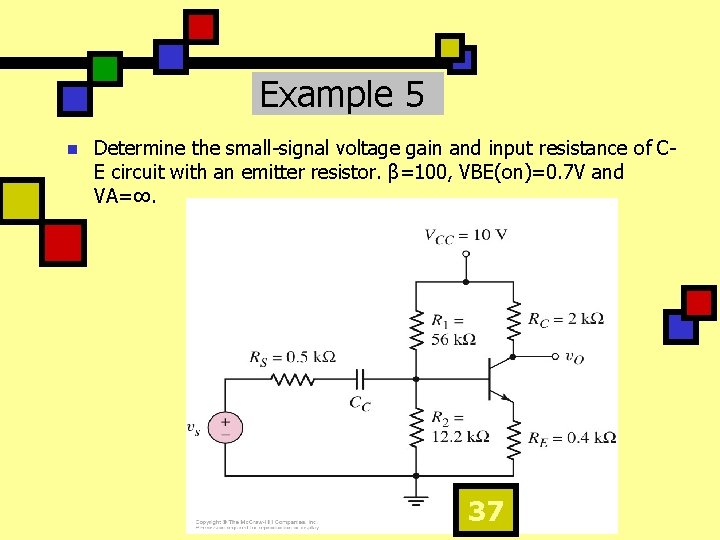

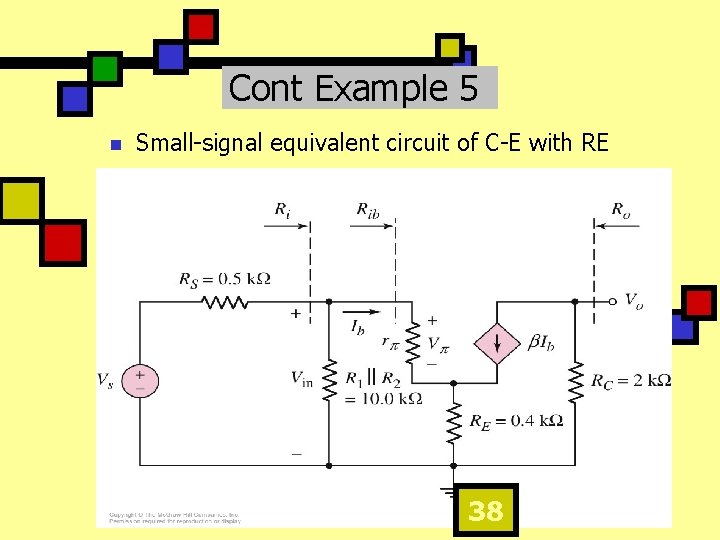

Example 5 n Determine the small-signal voltage gain and input resistance of CE circuit with an emitter resistor. β=100, VBE(on)=0. 7 V and VA=∞. 37

Cont Example 5 n Small-signal equivalent circuit of C-E with RE 38

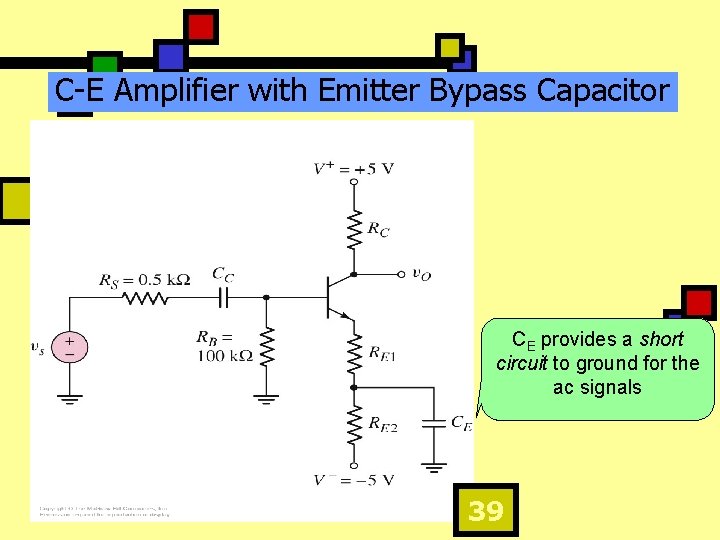

C-E Amplifier with Emitter Bypass Capacitor CE provides a short circuit to ground for the ac signals 39

Cont. . n n n By include RE, it provide stability of Q-point. If RE is too high +++> small-signal voltage gain will be reduced severely. (see Av equation) Thus, RE is split to RE 1 & RE 2 and the second resistor is bypassed with “emitter bypass capacitor”. CE provides a short circuit to ground for ac signal. So, only RE 1 is a part of ac equivalent circuit. For dc stability: RE=RE 1+RE 2 For ac gain stability: RE=RE 1 since CE will short RE 2 to ground. 40

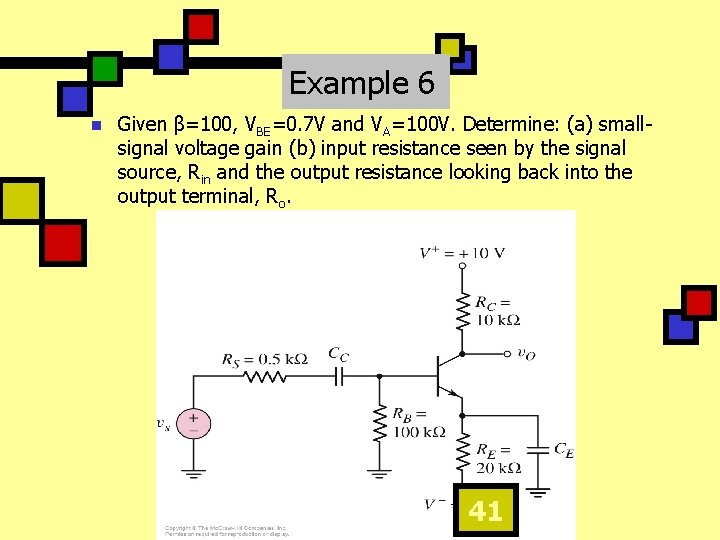

Example 6 n Given β=100, VBE=0. 7 V and VA=100 V. Determine: (a) smallsignal voltage gain (b) input resistance seen by the signal source, Rin and the output resistance looking back into the output terminal, Ro. 41

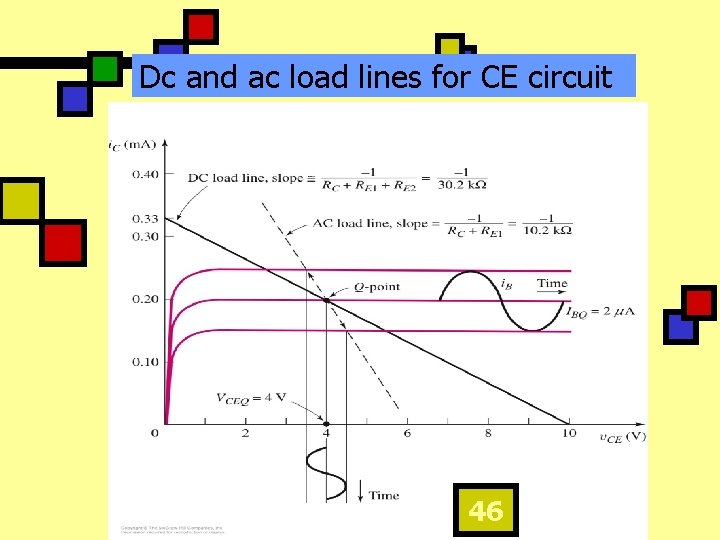

AC Load Line Analysis n n Dc load line -> a way of visualizing r/ship between Q -point and transistor characteristic. When capacitor included in cct, a new effective load line ac load line exist. Ac load line -> visualizing r/ship between smallsignal response and transistor characteristic. Ac operating region is on ac load line. 42

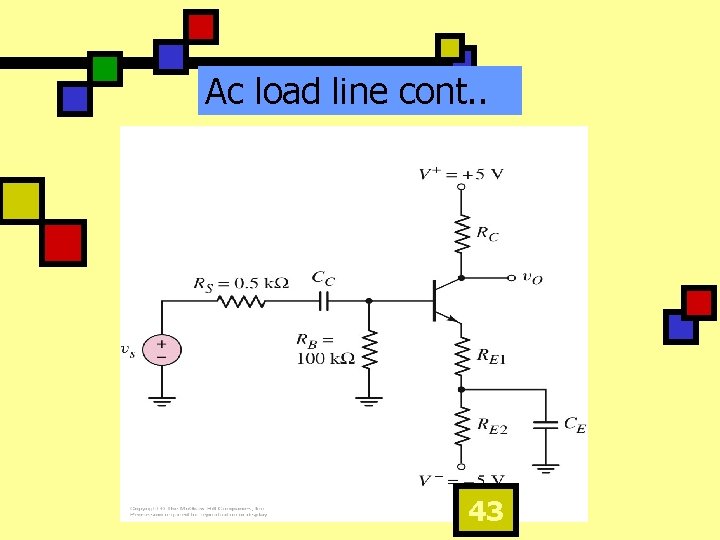

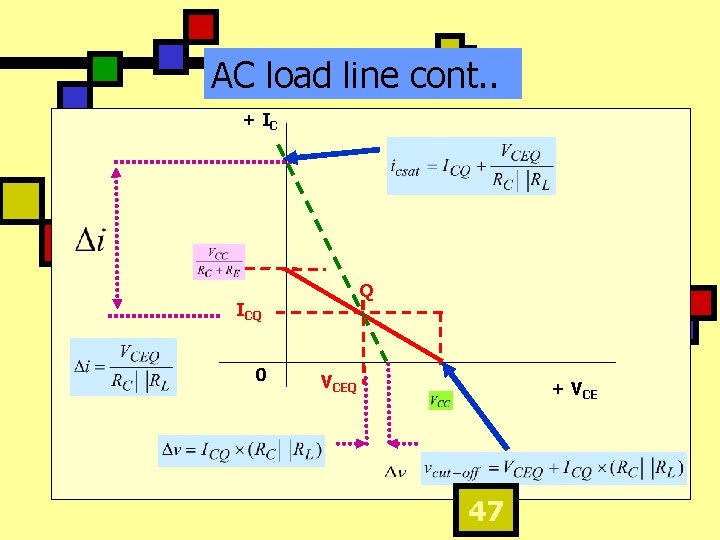

Ac load line cont. . 43

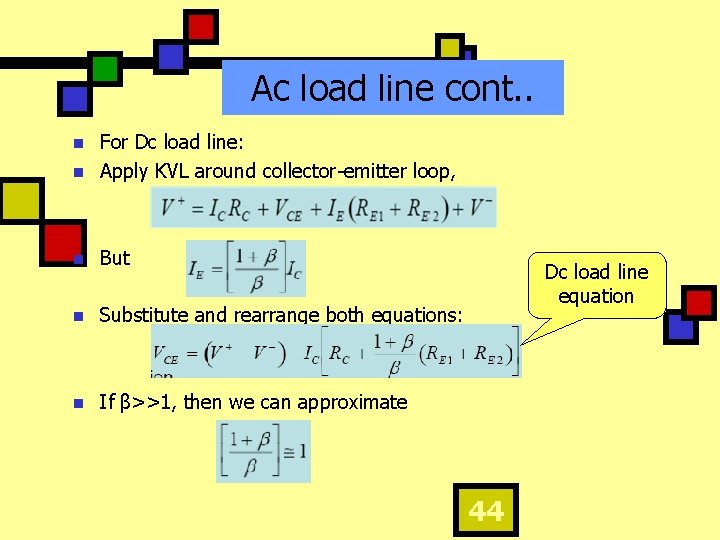

Ac load line cont. . n For Dc load line: Apply KVL around collector-emitter loop, n But n Substitute and rearrange both equations: n If β>>1, then we can approximate n Dc load line equation 44

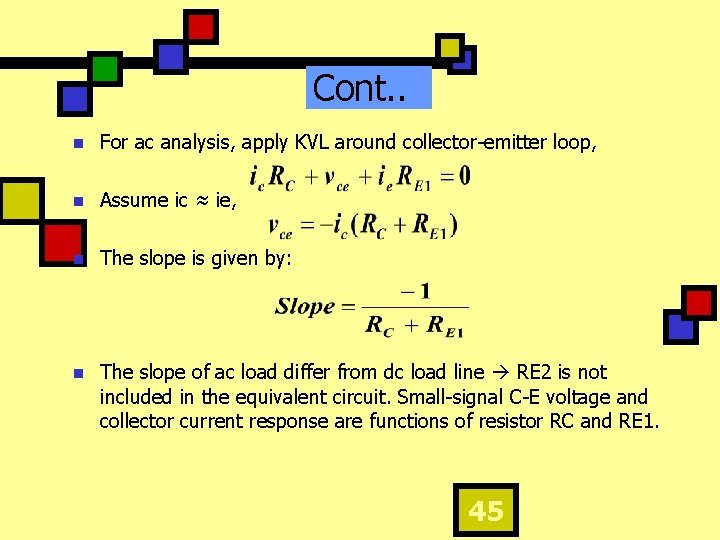

Cont. . n For ac analysis, apply KVL around collector-emitter loop, n Assume ic ≈ ie, n The slope is given by: n The slope of ac load differ from dc load line RE 2 is not included in the equivalent circuit. Small-signal C-E voltage and collector current response are functions of resistor RC and RE 1. 45

Dc and ac load lines for CE circuit 46

AC load line cont. . + IC Q ICQ 0 VCEQ + VCE 47

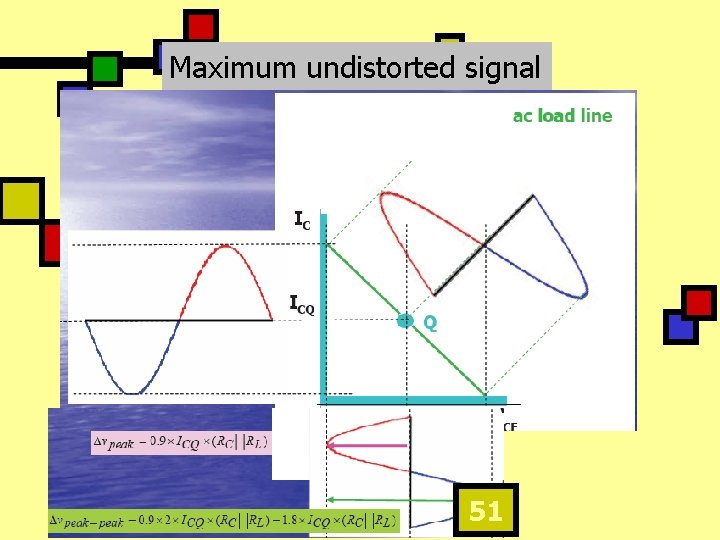

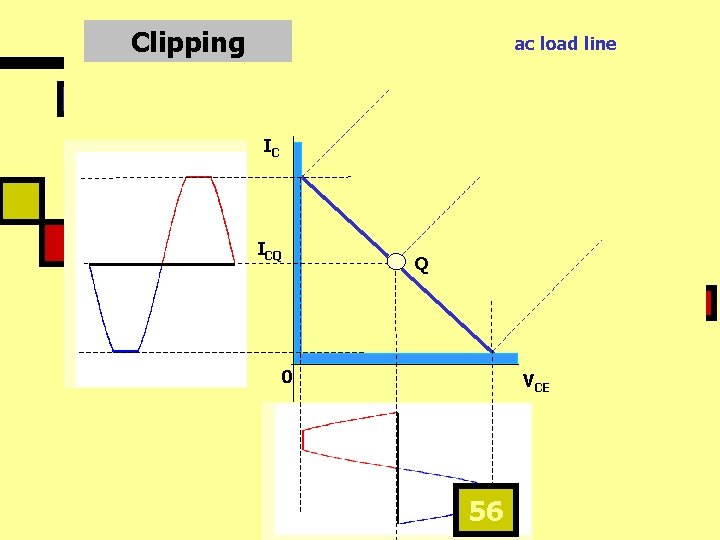

Maximum symmetrical swing n n n When symmetrical sinusoidal signal applied to i/p of amplifier, symmetrical sinusoidal signal generated at o/p. Use ac load line to determine the maximum output symmetrical swing. If output exceed limit, a portion of o/p signal will be clipped and signal distortion occur. 48

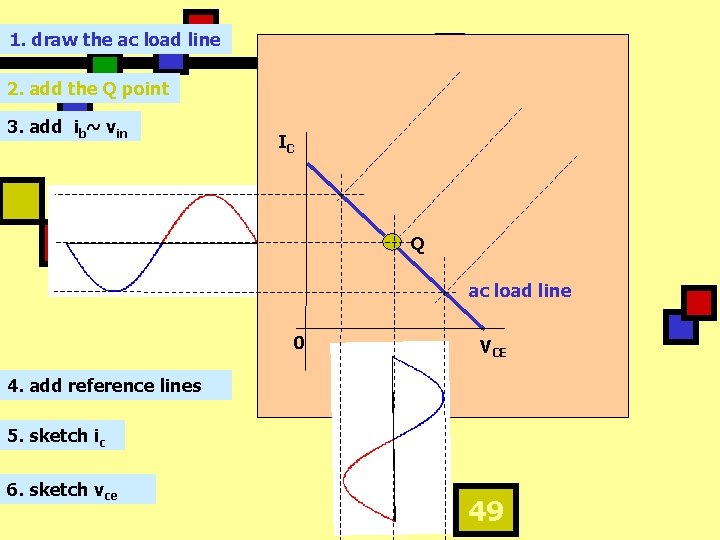

1. draw the ac load line 2. add the Q point 3. add ib~ vin IC Q ac load line 0 VCE 4. add reference lines 5. sketch ic 6. sketch vce 49

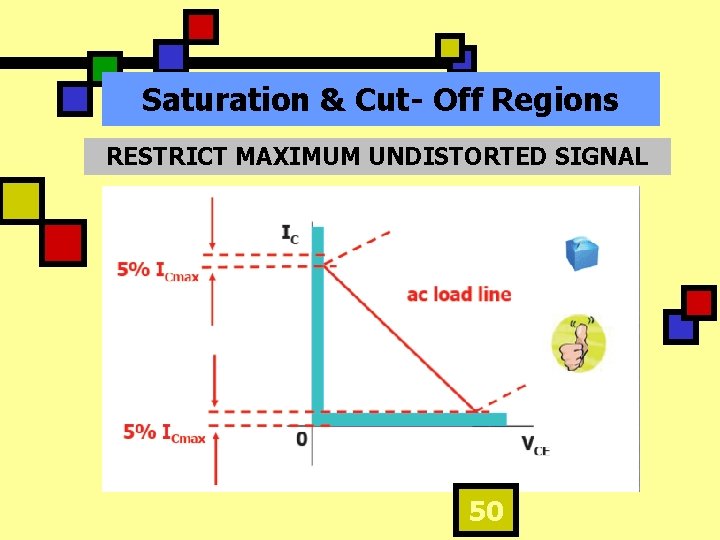

Saturation & Cut- Off Regions RESTRICT MAXIMUM UNDISTORTED SIGNAL 50

Maximum undistorted signal 51

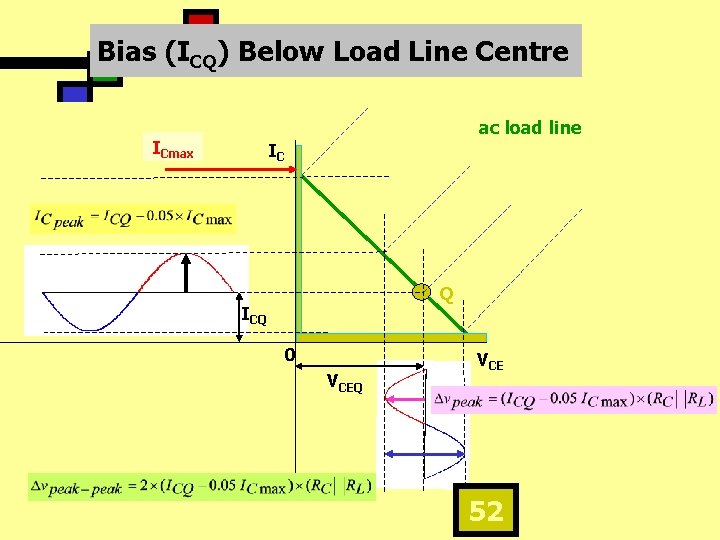

Bias (ICQ) Below Load Line Centre ac load line ICmax IC Q ICQ 0 VCEQ VCE 52

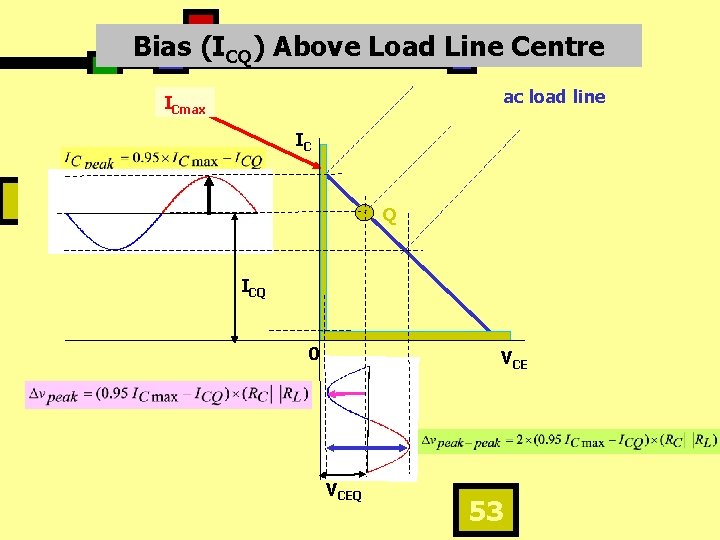

Bias (ICQ) Above Load Line Centre ac load line ICmax IC Q ICQ 0 VCEQ 53

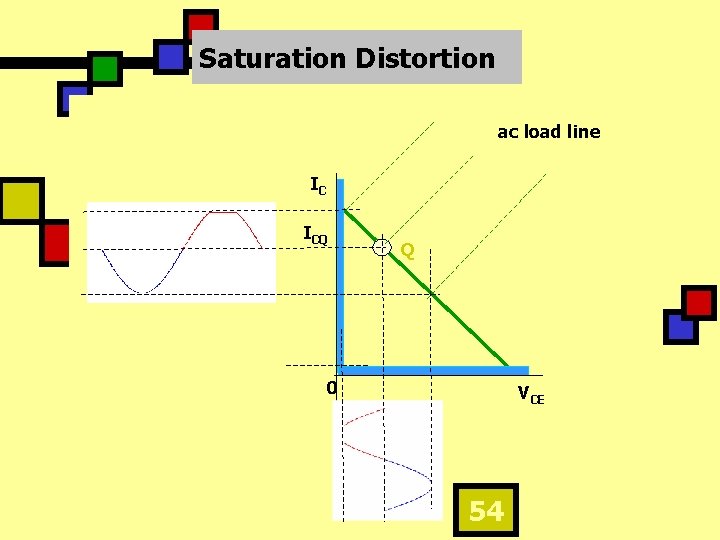

Saturation Distortion ac load line IC ICQ Q 0 VCE 54

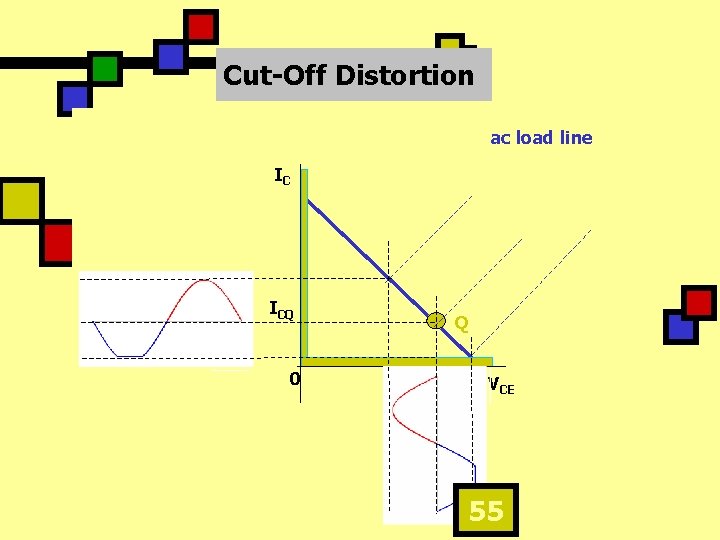

Cut-Off Distortion ac load line IC ICQ 0 Q VCE 55

Clipping ac load line IC ICQ Q 0 VCE 56

- Slides: 56