Transactionlevel riending An Open StandardsBased Library for Connecting

Transaction-level riending An Open, Standards-Based Library for Connecting TLM Models in System. C and System. Verilog UVM Connect blah Ankur Jain, Verification Technologist 1 © 2013 Mentor Graphics Corp. www. mentor. com

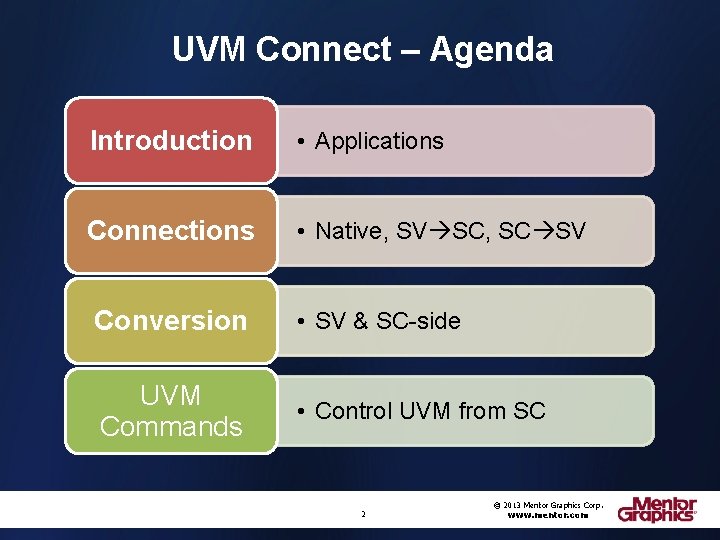

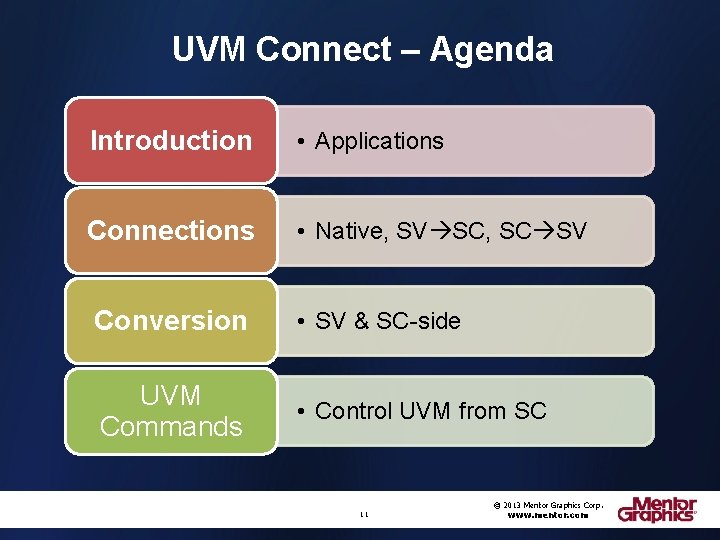

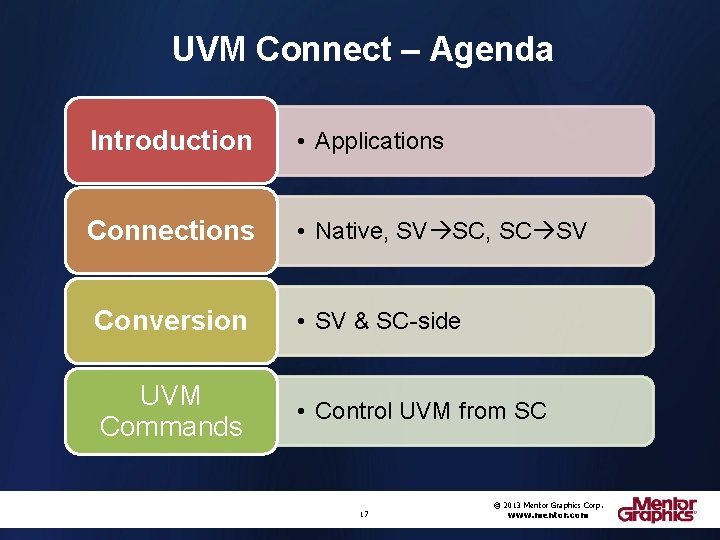

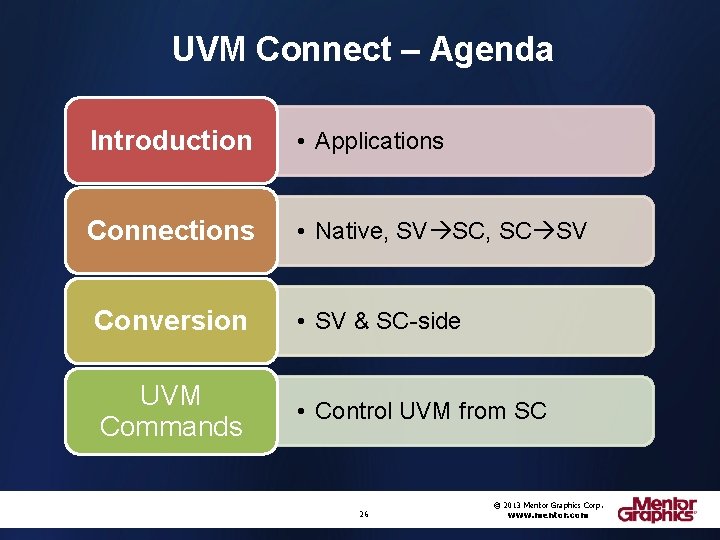

UVM Connect – Agenda Introduction • Applications Connections • Native, SV SC, SC SV Conversion • SV & SC-side UVM Commands • Control UVM from SC 2 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Agenda Introduction • Applications 3 © 2013 Mentor Graphics Corp. www. mentor. com

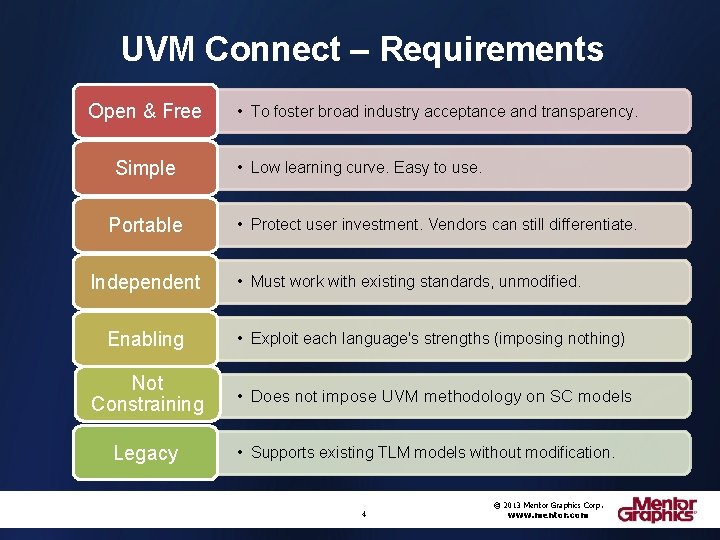

UVM Connect – Requirements Open & Free Simple Portable Independent • To foster broad industry acceptance and transparency. • Low learning curve. Easy to use. • Protect user investment. Vendors can still differentiate. • Must work with existing standards, unmodified. Enabling • Exploit each language's strengths (imposing nothing) Not Constraining • Does not impose UVM methodology on SC models Legacy • Supports existing TLM models without modification. 4 © 2013 Mentor Graphics Corp. www. mentor. com

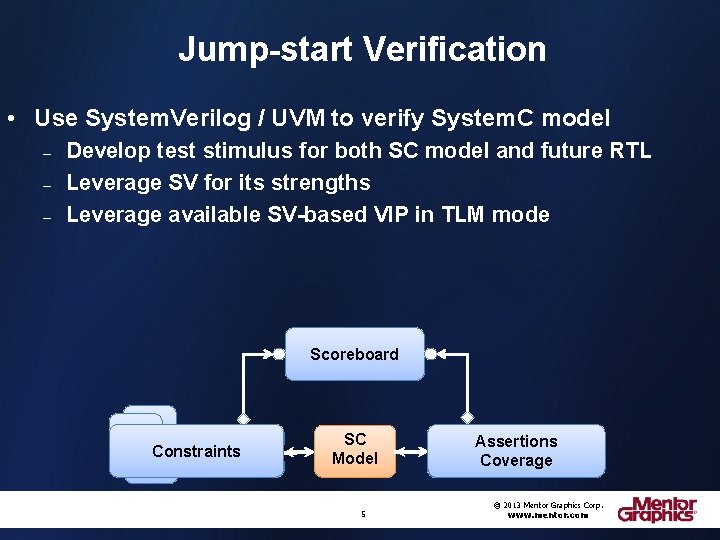

Jump-start Verification • Use System. Verilog / UVM to verify System. C model – – – Develop test stimulus for both SC model and future RTL Leverage SV for its strengths Leverage available SV-based VIP in TLM mode Scoreboard Seqs Constraints Agent Seqs SC Model 5 Assertions Agent Seqs Coverage © 2013 Mentor Graphics Corp. www. mentor. com

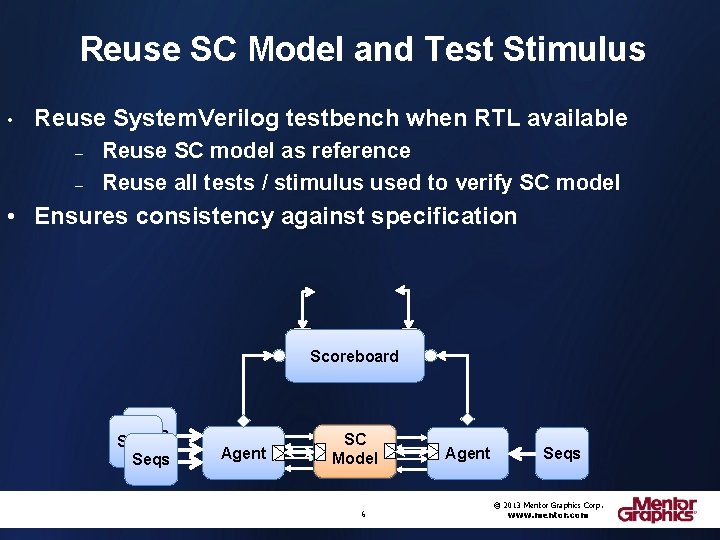

Reuse SC Model and Test Stimulus • Reuse System. Verilog testbench when RTL available – – Reuse SC model as reference Reuse all tests / stimulus used to verify SC model • Ensures consistency against specification Scoreboard Seqs Agent SC RTL Model 6 Agent Seqs © 2013 Mentor Graphics Corp. www. mentor. com

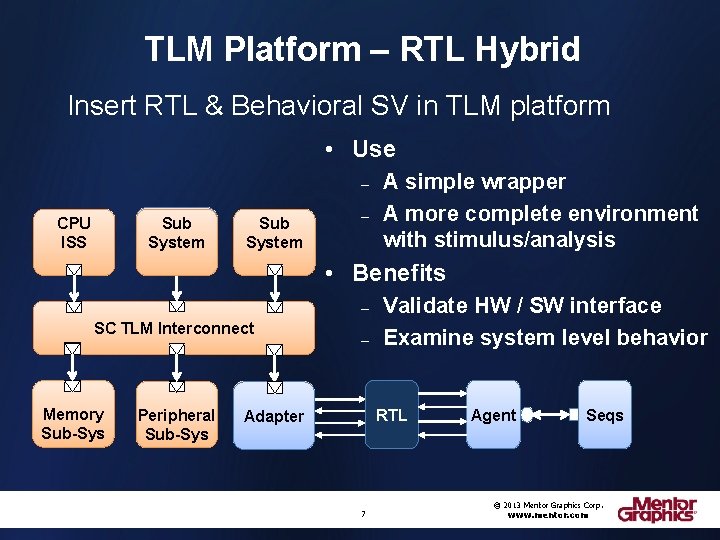

TLM Platform – RTL Hybrid Insert RTL & Behavioral SV in TLM platform • Use – Sub System CPU ISS Sub System – A simple wrapper A more complete environment with stimulus/analysis • Benefits – SC TLM Interconnect Memory Sub-Sys Peripheral Sub-Sys – Validate HW / SW interface Examine system level behavior RTL Sub Adapter System 7 Agent Seqs © 2013 Mentor Graphics Corp. www. mentor. com

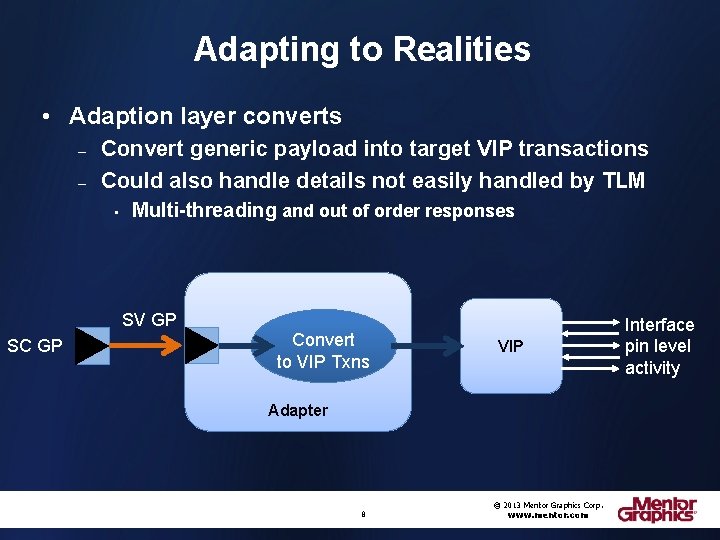

Adapting to Realities • Adaption layer converts – – Convert generic payload into target VIP transactions Could also handle details not easily handled by TLM • Multi-threading and out of order responses SV GP SC GP Convert to VIP Txns VIP Adapter 8 © 2013 Mentor Graphics Corp. www. mentor. com Interface pin level activity

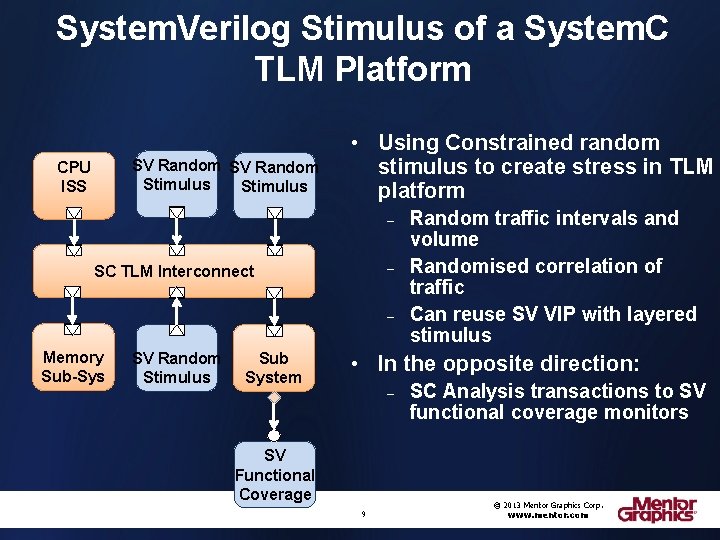

System. Verilog Stimulus of a System. C TLM Platform SV Random Stimulus CPU ISS • Using Constrained random stimulus to create stress in TLM platform – – SC TLM Interconnect – Memory Sub-Sys SV Random Stimulus Sub System Random traffic intervals and volume Randomised correlation of traffic Can reuse SV VIP with layered stimulus • In the opposite direction: – SV Functional Coverage 9 SC Analysis transactions to SV functional coverage monitors © 2013 Mentor Graphics Corp. www. mentor. com

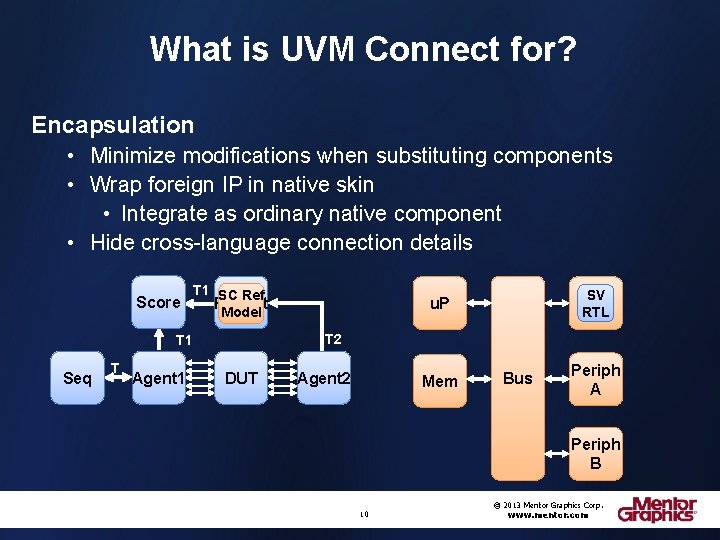

What is UVM Connect for? Encapsulation • Minimize modifications when substituting components • Wrap foreign IP in native skin • Integrate as ordinary native component • Hide cross-language connection details T 1 SC Ref Score Predict Model T 2 T 1 Seq T Agent 1 DMA SV RTL Ctrl u. P DUT Agent 2 Mem Bus Periph A Periph B 10 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Agenda Introduction • Applications Connections • Native, SV SC, SC SV Conversion • SV & SC-side UVM Commands • Control UVM from SC 11 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Agenda Connections • Native, SV SC, SC SV 12 © 2013 Mentor Graphics Corp. www. mentor. com

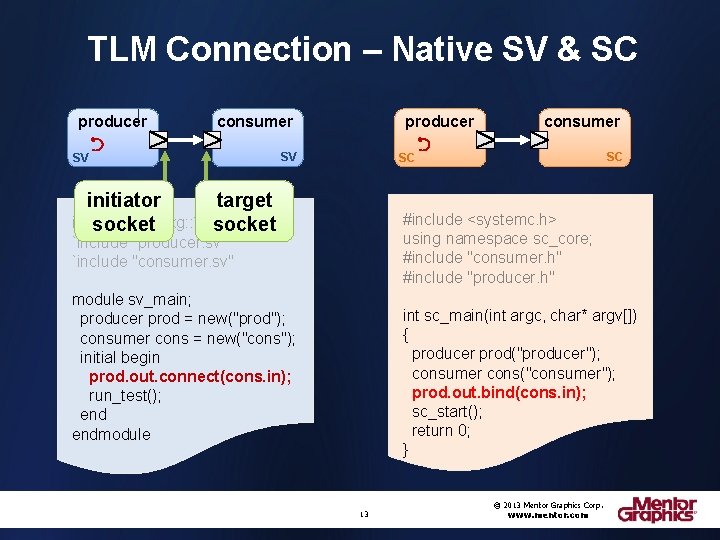

TLM Connection – Native SV & SC producer consumer SV producer SV consumer SC SC initiator target import uvm_pkg: : *; socket #include <systemc. h> using namespace sc_core; #include "consumer. h" #include "producer. h" `include "producer. sv" `include "consumer. sv" module sv_main; producer prod = new("prod"); consumer cons = new("cons"); initial begin prod. out. connect(cons. in); run_test(); endmodule int sc_main(int argc, char* argv[]) { producer prod("producer"); consumer cons("consumer"); prod. out. bind(cons. in); sc_start(); return 0; } 13 © 2013 Mentor Graphics Corp. www. mentor. com

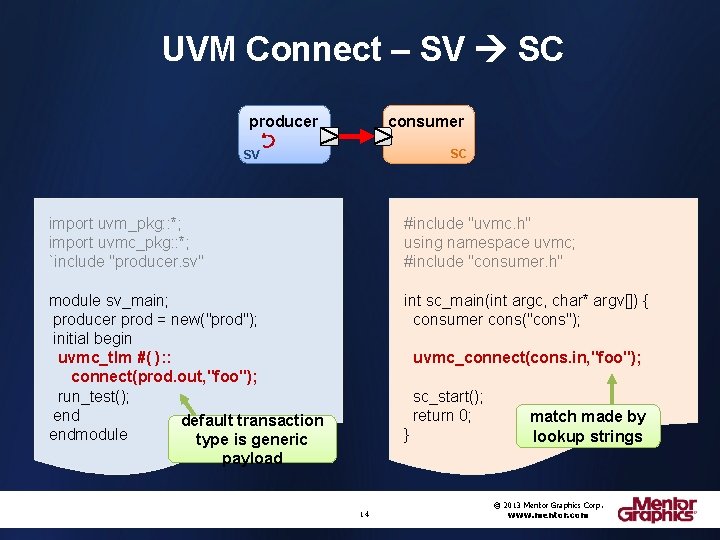

UVM Connect – SV SC producer consumer SC SV import uvm_pkg: : *; import uvmc_pkg: : *; `include "producer. sv" #include "uvmc. h" using namespace uvmc; #include "consumer. h" module sv_main; producer prod = new("prod"); initial begin uvmc_tlm #( ): : connect(prod. out, "foo"); run_test(); end default transaction endmodule type is generic int sc_main(int argc, char* argv[]) { consumer cons("cons"); uvmc_connect(cons. in, "foo"); sc_start(); return 0; } match made by lookup strings payload 14 © 2013 Mentor Graphics Corp. www. mentor. com

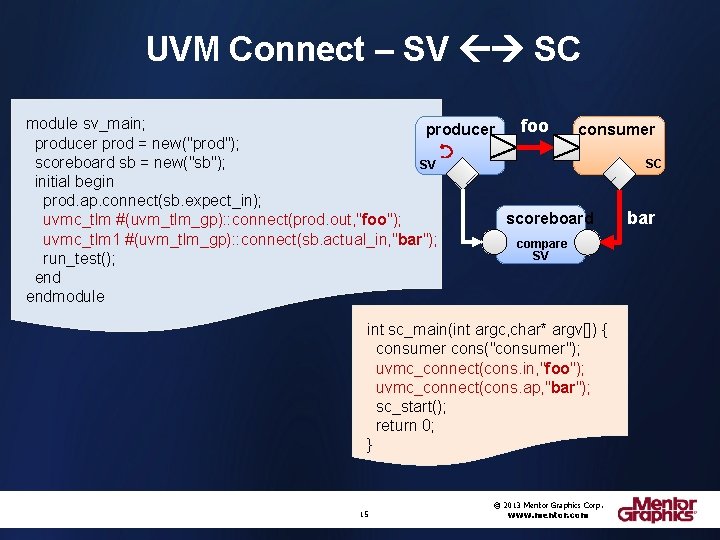

UVM Connect – SV SC module sv_main; foo producer consumer producer prod = new("prod"); scoreboard sb = new("sb"); SC SV initial begin prod. ap. connect(sb. expect_in); bar scoreboard uvmc_tlm #(uvm_tlm_gp): : connect(prod. out, "foo"); uvmc_tlm 1 #(uvm_tlm_gp): : connect(sb. actual_in, "bar"); compare SV run_test(); endmodule int sc_main(int argc, char* argv[]) { consumer cons("consumer"); uvmc_connect(cons. in, "foo"); uvmc_connect(cons. ap, "bar"); sc_start(); return 0; } 15 © 2013 Mentor Graphics Corp. www. mentor. com

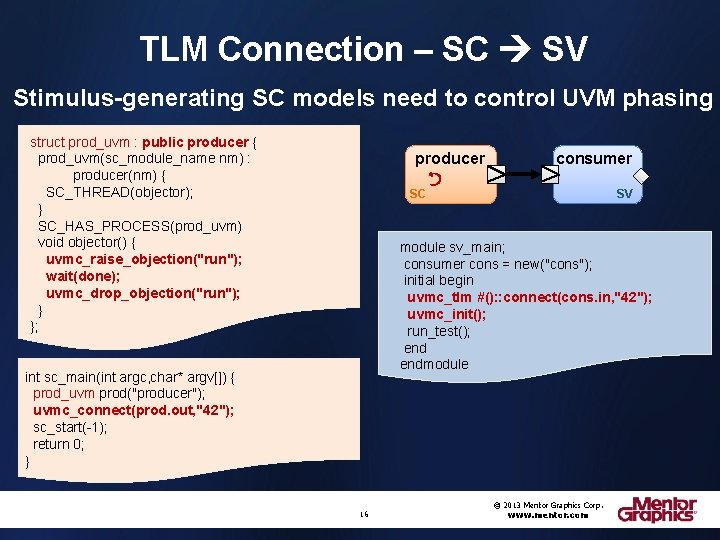

TLM Connection – SC SV Stimulus-generating SC models need to control UVM phasing struct prod_uvm : public producer { prod_uvm(sc_module_name nm) : producer(nm) { SC_THREAD(objector); } SC_HAS_PROCESS(prod_uvm) void objector() { uvmc_raise_objection("run"); wait(done); uvmc_drop_objection("run"); } }; producer consumer SV SC module sv_main; consumer cons = new("cons"); initial begin uvmc_tlm #(): : connect(cons. in, "42"); uvmc_init(); run_test(); endmodule int sc_main(int argc, char* argv[]) { prod_uvm prod("producer"); uvmc_connect(prod. out, "42"); sc_start(-1); return 0; } 16 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Agenda Introduction • Applications Connections • Native, SV SC, SC SV Conversion • SV & SC-side UVM Commands • Control UVM from SC 17 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Agenda Conversion • SV & SC-side 18 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Behind the Scenes producer consumer 19 © 2013 Mentor Graphics Corp. www. mentor. com

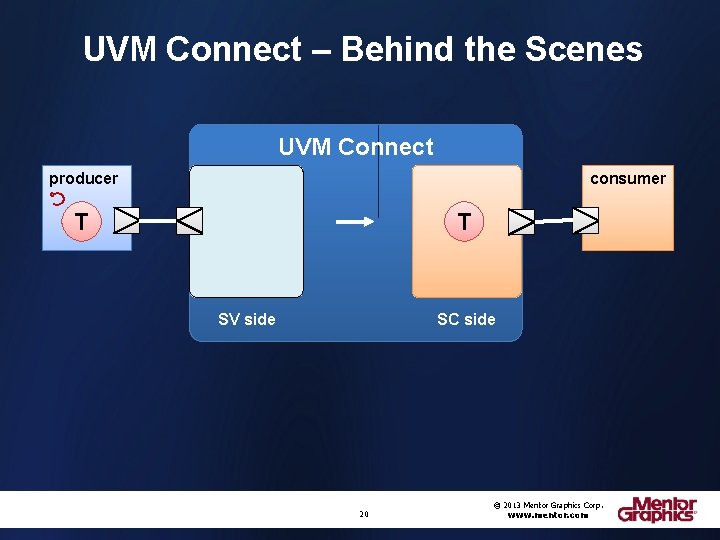

UVM Connect – Behind the Scenes UVM Connect producer consumer T T SV side SC side 20 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Behind the Scenes producer consumer 21 © 2013 Mentor Graphics Corp. www. mentor. com

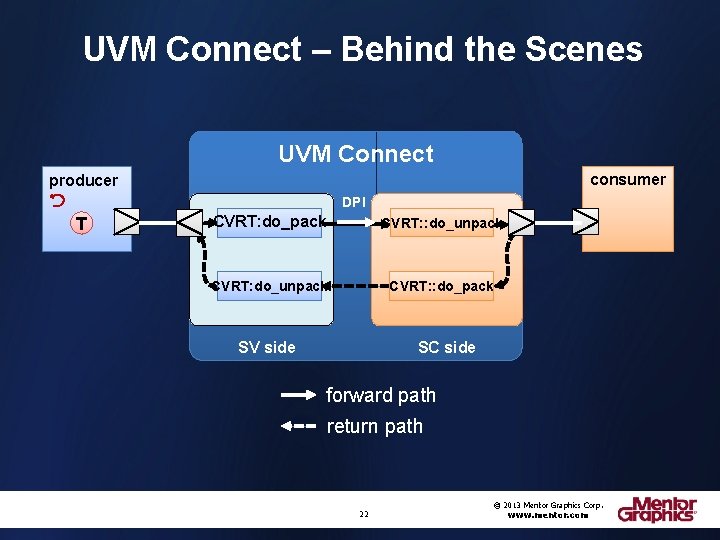

UVM Connect – Behind the Scenes UVM Connect consumer producer DPI T CVRT: do_pack CVRT: : do_unpack T CVRT: do_unpack CVRT: : do_pack SV side SC side forward path return path 22 © 2013 Mentor Graphics Corp. www. mentor. com

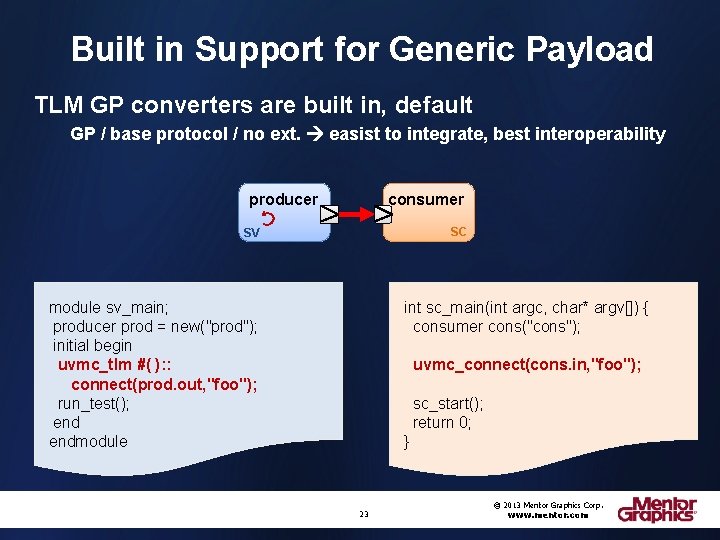

Built in Support for Generic Payload TLM GP converters are built in, default GP / base protocol / no ext. easist to integrate, best interoperability producer consumer SC SV module sv_main; producer prod = new("prod"); initial begin uvmc_tlm #( ): : connect(prod. out, "foo"); run_test(); endmodule int sc_main(int argc, char* argv[]) { consumer cons("cons"); uvmc_connect(cons. in, "foo"); sc_start(); return 0; } 23 © 2013 Mentor Graphics Corp. www. mentor. com

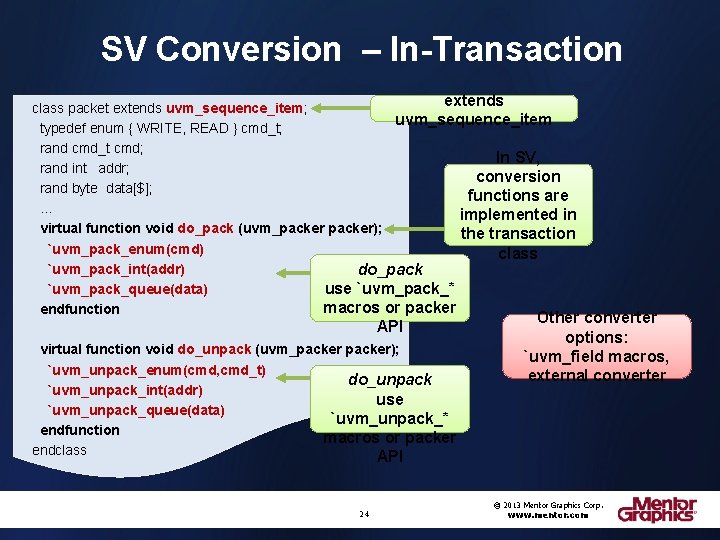

SV Conversion – In-Transaction extends class packet extends uvm_sequence_item; uvm_sequence_item typedef enum { WRITE, READ } cmd_t; rand cmd_t cmd; In SV, rand int addr; conversion rand byte data[$]; functions are … implemented in virtual function void do_pack (uvm_packer); the transaction `uvm_pack_enum(cmd) class `uvm_pack_int(addr) do_pack `uvm_pack_queue(data) use `uvm_pack_* macros or packer endfunction API virtual function void do_unpack (uvm_packer); `uvm_unpack_enum(cmd, cmd_t) do_unpack `uvm_unpack_int(addr) use `uvm_unpack_queue(data) `uvm_unpack_* endfunction macros or packer endclass API 24 Other converter options: `uvm_field macros, external converter © 2013 Mentor Graphics Corp. www. mentor. com

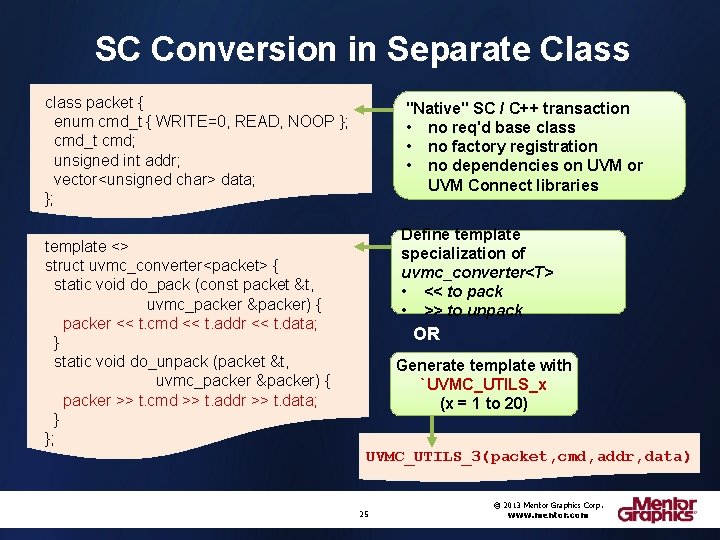

SC Conversion in Separate Class class packet { enum cmd_t { WRITE=0, READ, NOOP }; cmd_t cmd; unsigned int addr; vector<unsigned char> data; }; "Native" SC / C++ transaction • no req'd base class • no factory registration • no dependencies on UVM or UVM Connect libraries Define template specialization of uvmc_converter<T> • << to pack • >> to unpack template <> struct uvmc_converter<packet> { static void do_pack (const packet &t, uvmc_packer &packer) { packer << t. cmd << t. addr << t. data; } static void do_unpack (packet &t, uvmc_packer &packer) { packer >> t. cmd >> t. addr >> t. data; } }; OR Generate template with `UVMC_UTILS_x (x = 1 to 20) UVMC_UTILS_3(packet, cmd, addr, data) 25 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Agenda Introduction • Applications Connections • Native, SV SC, SC SV Conversion • SV & SC-side UVM Commands • Control UVM from SC 26 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect – Agenda UVM Commands • Control UVM from SC 27 © 2013 Mentor Graphics Corp. www. mentor. com

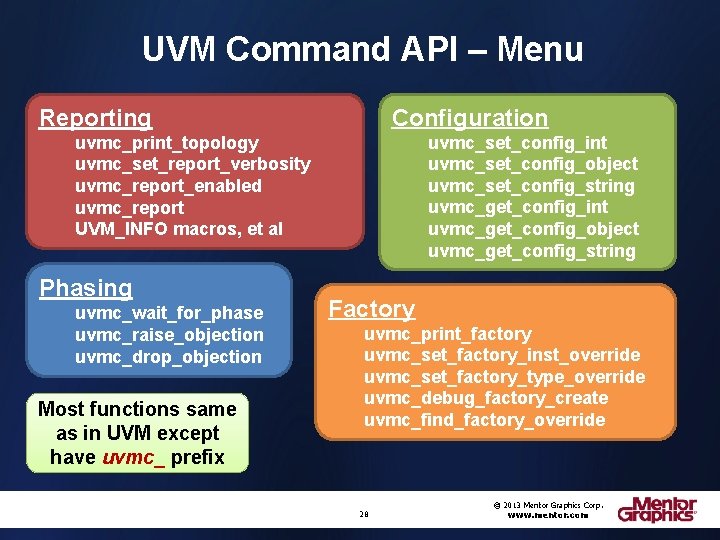

UVM Command API – Menu Configuration Reporting uvmc_set_config_int uvmc_set_config_object uvmc_set_config_string uvmc_get_config_int uvmc_get_config_object uvmc_get_config_string uvmc_print_topology uvmc_set_report_verbosity uvmc_report_enabled uvmc_report UVM_INFO macros, et al Phasing uvmc_wait_for_phase uvmc_raise_objection uvmc_drop_objection Most functions same as in UVM except have uvmc_ prefix Factory uvmc_print_factory uvmc_set_factory_inst_override uvmc_set_factory_type_override uvmc_debug_factory_create uvmc_find_factory_override 28 © 2013 Mentor Graphics Corp. www. mentor. com

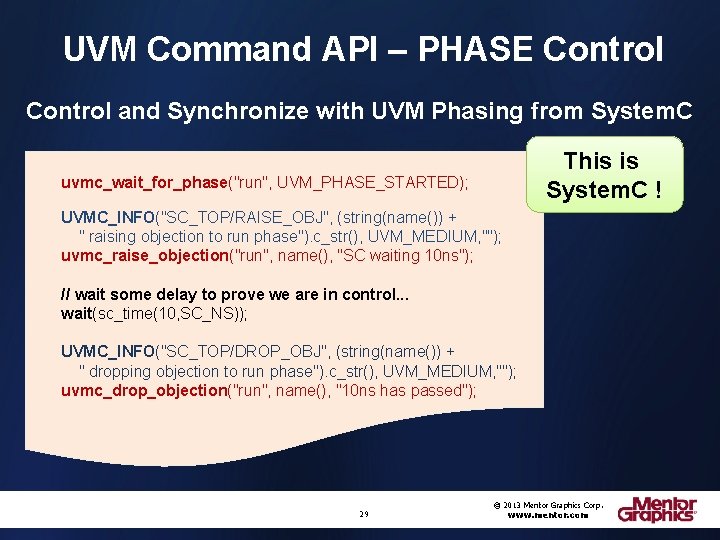

UVM Command API – PHASE Control and Synchronize with UVM Phasing from System. C This is System. C ! uvmc_wait_for_phase("run", UVM_PHASE_STARTED); UVMC_INFO("SC_TOP/RAISE_OBJ", (string(name()) + " raising objection to run phase"). c_str(), UVM_MEDIUM, ""); uvmc_raise_objection("run", name(), "SC waiting 10 ns"); // wait some delay to prove we are in control. . . wait(sc_time(10, SC_NS)); UVMC_INFO("SC_TOP/DROP_OBJ", (string(name()) + " dropping objection to run phase"). c_str(), UVM_MEDIUM, ""); uvmc_drop_objection("run", name(), "10 ns has passed"); 29 © 2013 Mentor Graphics Corp. www. mentor. com

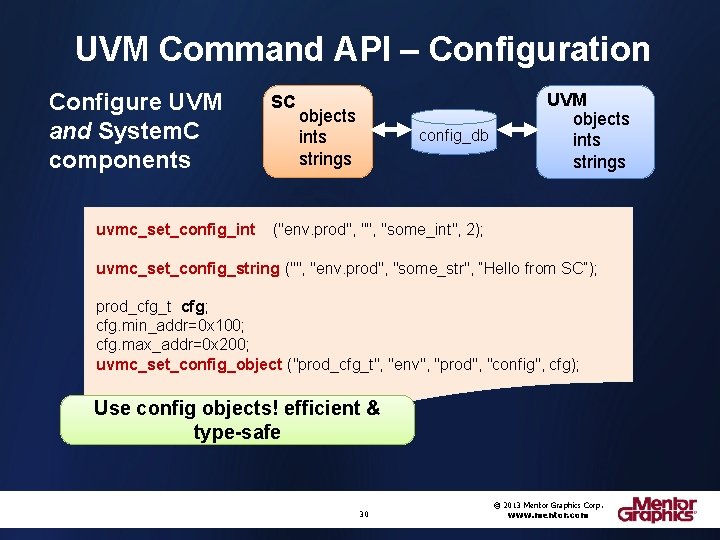

UVM Command API – Configuration Configure UVM and System. C components uvmc_set_config_int SC objects ints strings config_db UVM objects ints strings ("env. prod", "some_int", 2); uvmc_set_config_string ("", "env. prod", "some_str", “Hello from SC”); prod_cfg_t cfg; cfg. min_addr=0 x 100; cfg. max_addr=0 x 200; uvmc_set_config_object ("prod_cfg_t", "env", "prod", "config", cfg); Use config objects! efficient & type-safe 30 © 2013 Mentor Graphics Corp. www. mentor. com

Download UVM Connect verificationacademy. com/courses/uvm-connect Download Kit Video modules Forum HTML docs Many examples 31 © 2013 Mentor Graphics Corp. www. mentor. com

UVM Connect 32 © 2013 Mentor Graphics Corp. www. mentor. com

- Slides: 32