Transaction Level Modeling Definitions and Approximations Trevor Meyerowitz

![References [CCATB] S. Pasricha, N. Dutt, and M. Ben-Romdhane, “Extending the Transaction Level Modeling References [CCATB] S. Pasricha, N. Dutt, and M. Ben-Romdhane, “Extending the Transaction Level Modeling](https://slidetodoc.com/presentation_image_h2/a7cf5a347d1a32f784690b3b88c6f22c/image-18.jpg)

- Slides: 18

Transaction Level Modeling Definitions and Approximations Trevor Meyerowitz EE 290 A Presentation May 12, 2005

Outline Motivation n Recent Definitions n ¨ System. C Definitions ¨ Spec. C Definitions ¨ Other Defintions n Classifying Models of Microprocessor Microarchitectures

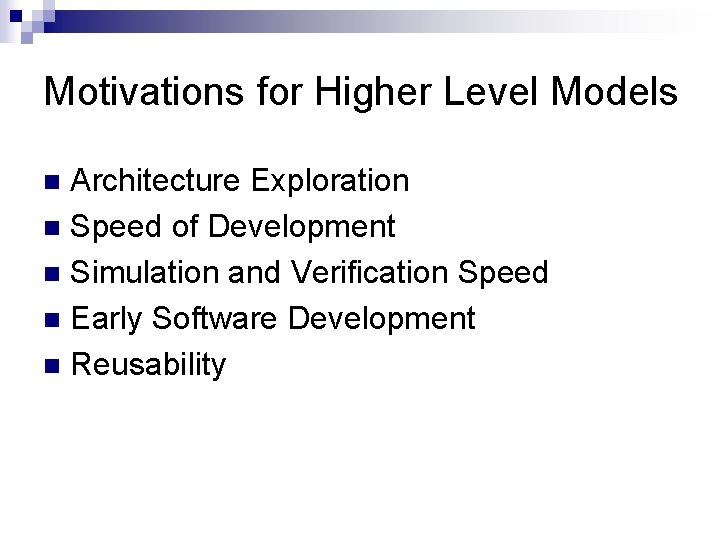

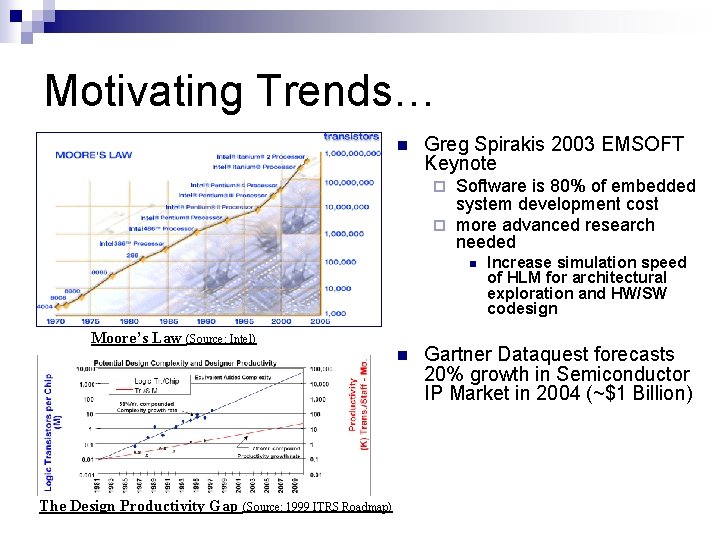

Motivating Trends… n Greg Spirakis 2003 EMSOFT Keynote Software is 80% of embedded system development cost ¨ more advanced research needed ¨ n Moore’s Law (Source: Intel) n The Design Productivity Gap (Source: 1999 ITRS Roadmap) Increase simulation speed of HLM for architectural exploration and HW/SW codesign Gartner Dataquest forecasts 20% growth in Semiconductor IP Market in 2004 (~$1 Billion)

Motivations for Higher Level Models Architecture Exploration n Speed of Development n Simulation and Verification Speed n Early Software Development n Reusability n

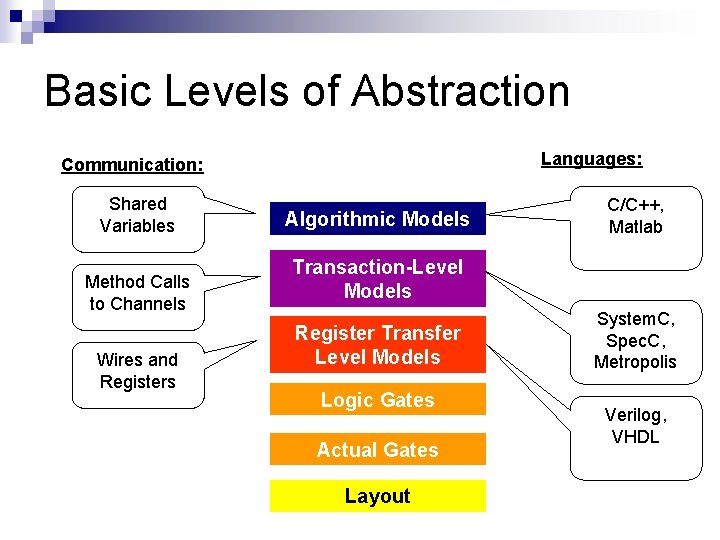

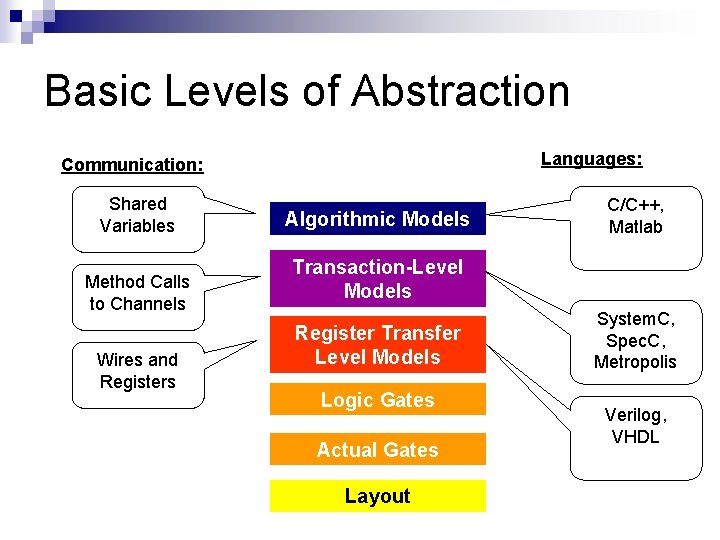

Basic Levels of Abstraction Languages: Communication: Shared Variables Method Calls to Channels Wires and Registers Algorithmic Models C/C++, Matlab Transaction-Level Models Register Transfer Level Models Logic Gates Actual Gates Layout System. C, Spec. C, Metropolis Verilog, VHDL

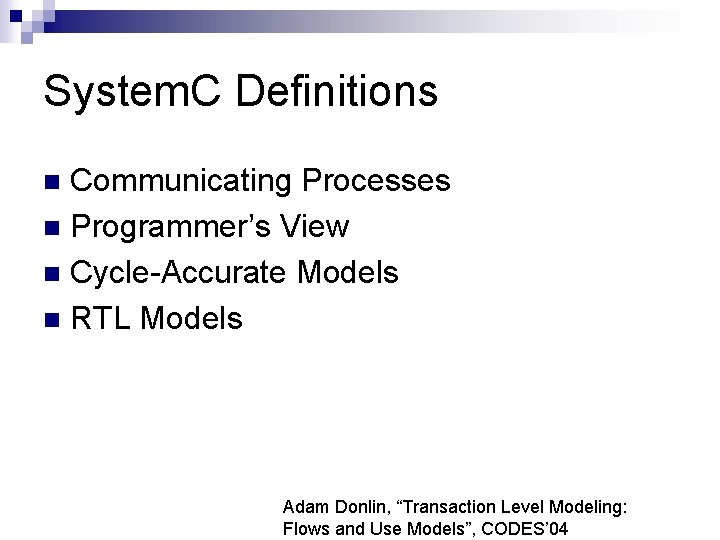

System. C Definitions Communicating Processes n Programmer’s View n Cycle-Accurate Models n RTL Models n Adam Donlin, “Transaction Level Modeling: Flows and Use Models”, CODES’ 04

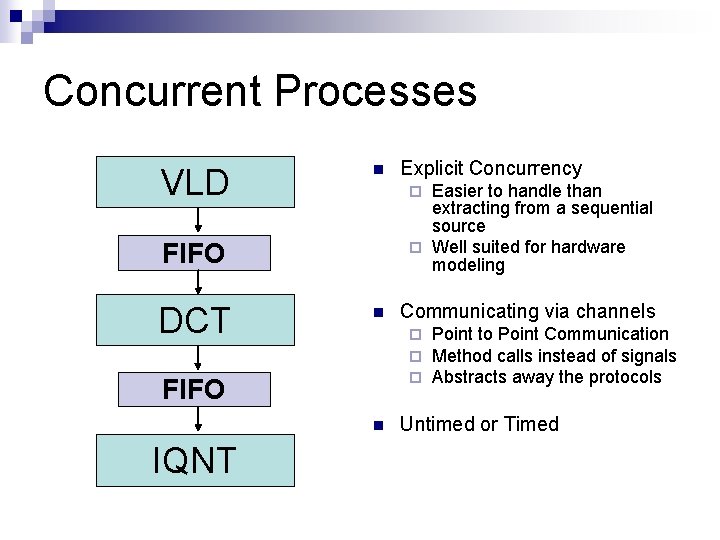

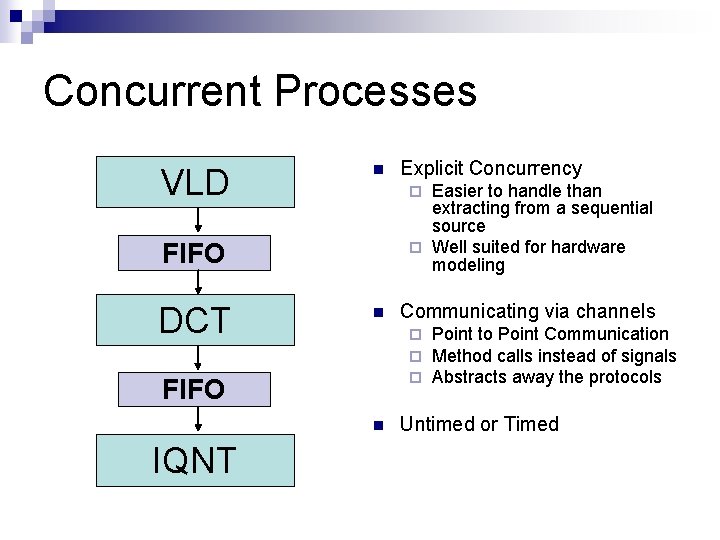

Concurrent Processes VLD n Easier to handle than extracting from a sequential source ¨ Well suited for hardware modeling ¨ FIFO DCT n Communicating via channels ¨ ¨ ¨ FIFO n IQNT Explicit Concurrency Point to Point Communication Method calls instead of signals Abstracts away the protocols Untimed or Timed

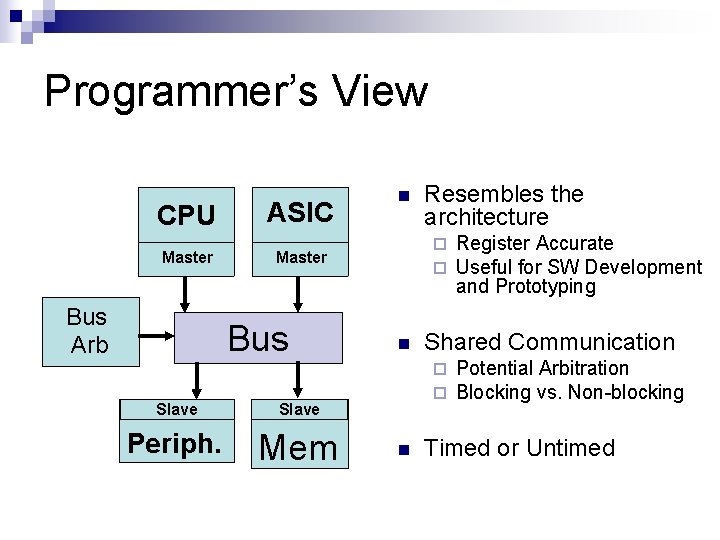

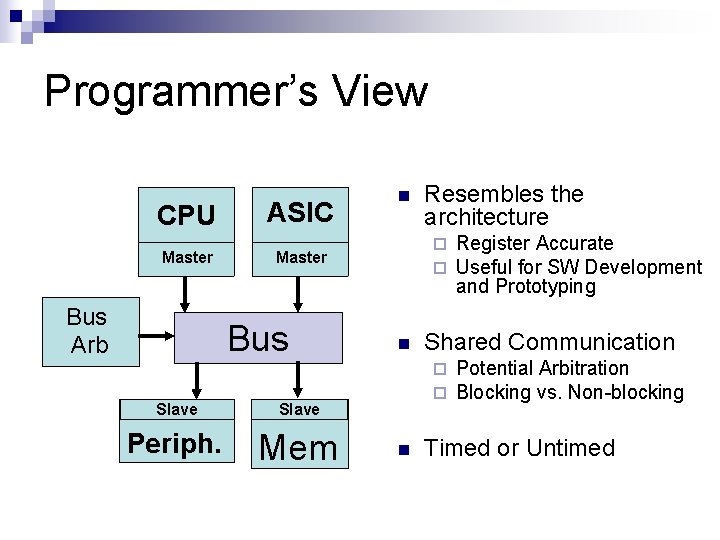

Programmer’s View CPU ASIC Master Bus Arb Bus Slave Periph. Mem n Resembles the architecture ¨ ¨ n Shared Communication ¨ ¨ n Register Accurate Useful for SW Development and Prototyping Potential Arbitration Blocking vs. Non-blocking Timed or Untimed

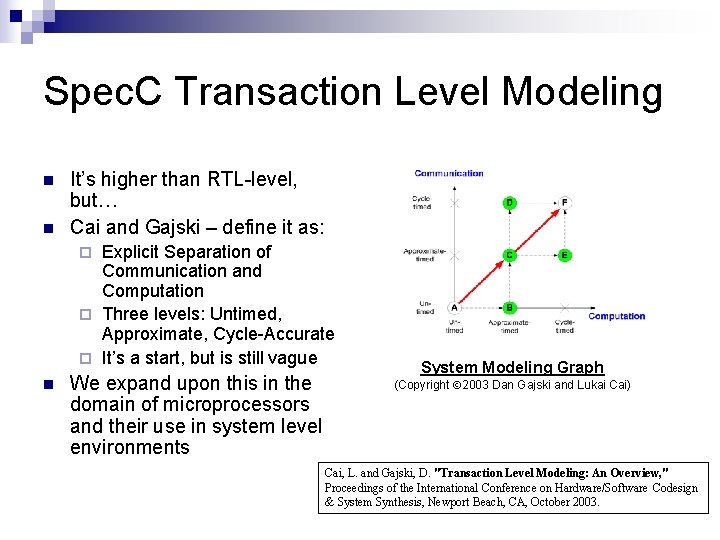

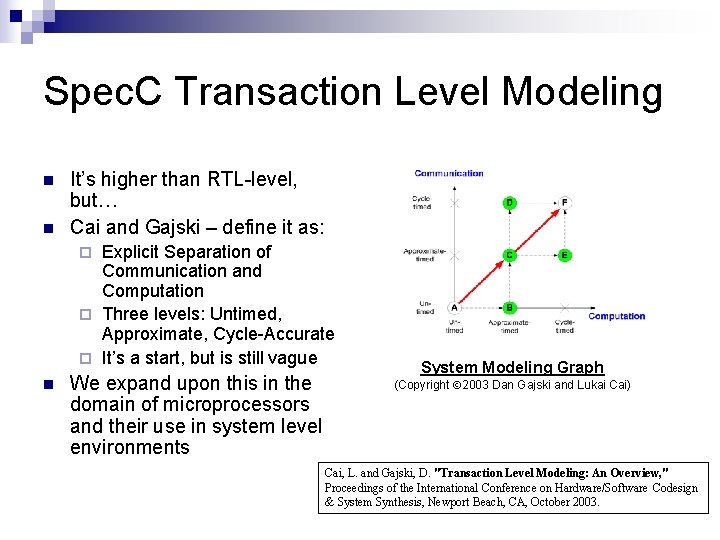

Spec. C Transaction Level Modeling n n It’s higher than RTL-level, but… Cai and Gajski – define it as: Explicit Separation of Communication and Computation ¨ Three levels: Untimed, Approximate, Cycle-Accurate ¨ It’s a start, but is still vague ¨ n We expand upon this in the domain of microprocessors and their use in system level environments System Modeling Graph (Copyright Ó 2003 Dan Gajski and Lukai Cai) Cai, L. and Gajski, D. "Transaction Level Modeling: An Overview, " Proceedings of the International Conference on Hardware/Software Codesign & System Synthesis, Newport Beach, CA, October 2003.

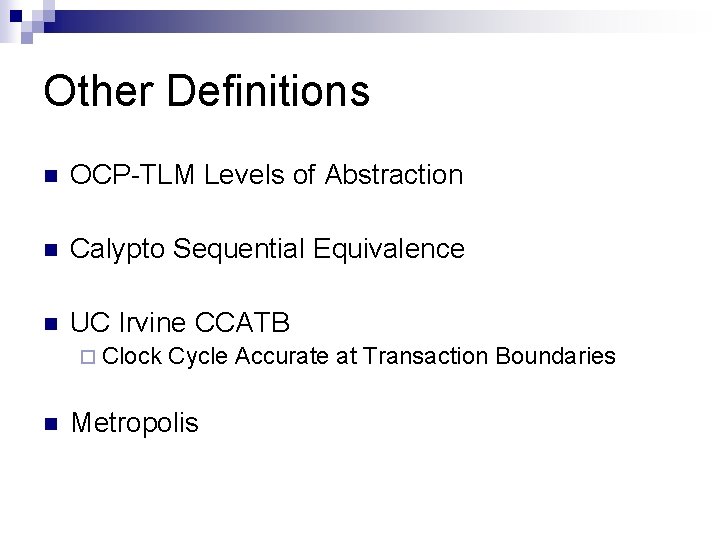

Other Definitions n OCP-TLM Levels of Abstraction n Calypto Sequential Equivalence n UC Irvine CCATB ¨ Clock n Cycle Accurate at Transaction Boundaries Metropolis

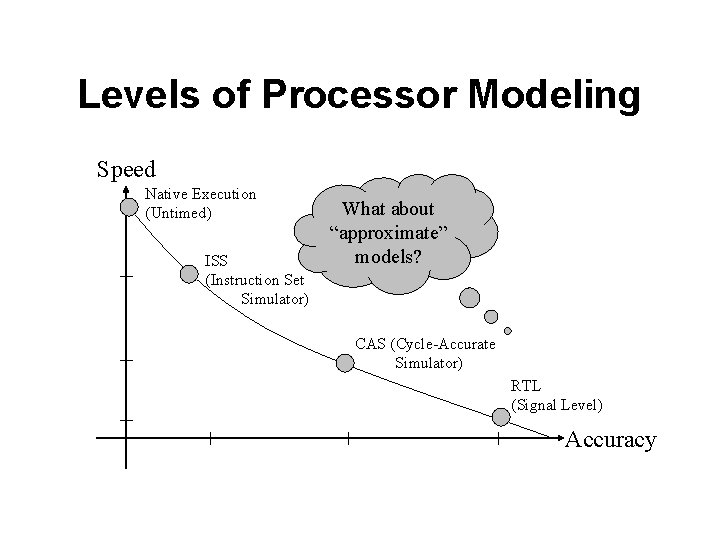

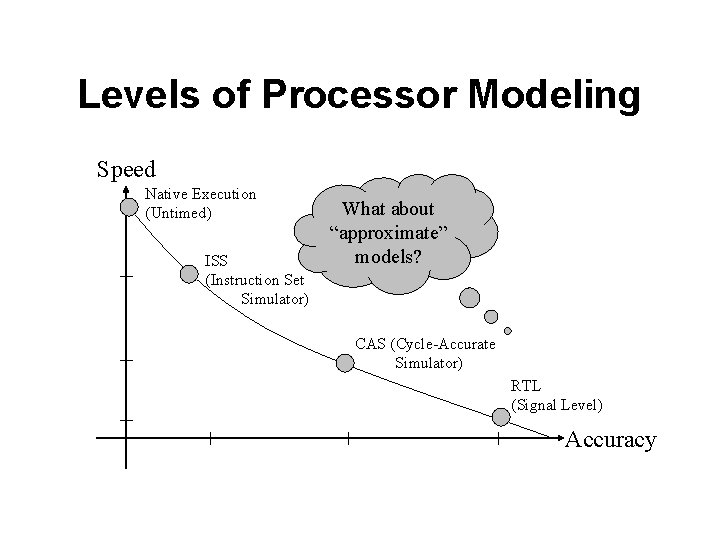

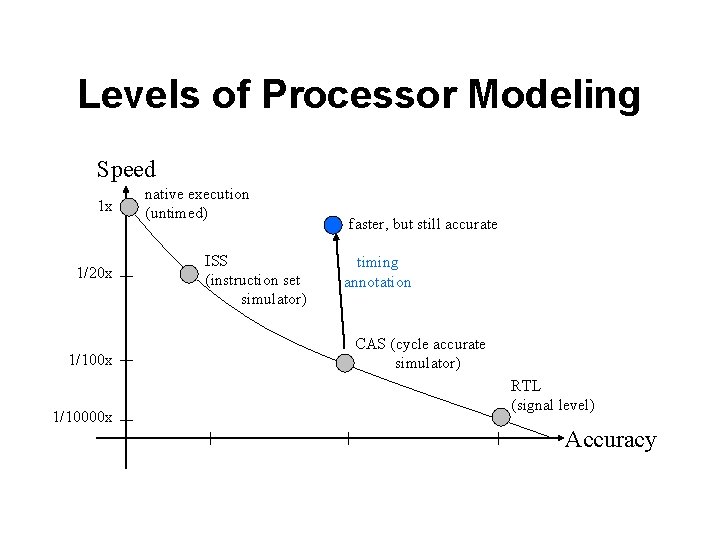

Levels of Processor Modeling Speed Native Execution (Untimed) ISS (Instruction Set Simulator) What about “approximate” models? CAS (Cycle-Accurate Simulator) RTL (Signal Level) Accuracy

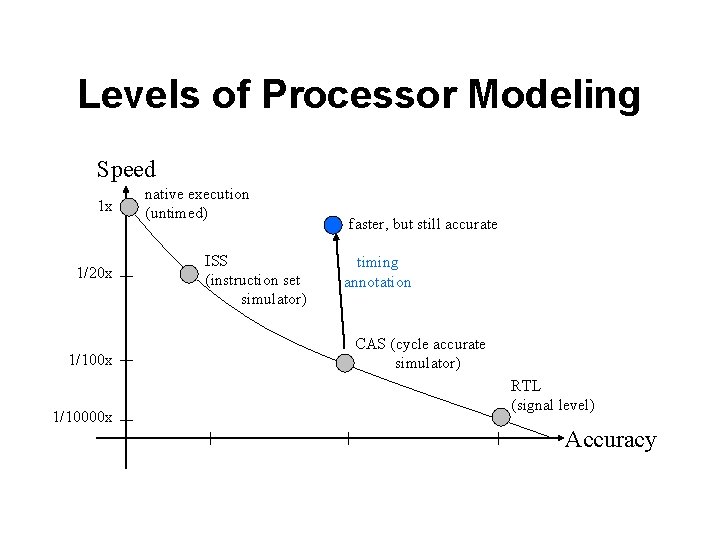

Levels of Processor Modeling Speed 1 x 1/20 x 1/10000 x native execution (untimed) ISS (instruction set simulator) faster, but still accurate timing annotation CAS (cycle accurate simulator) RTL (signal level) Accuracy

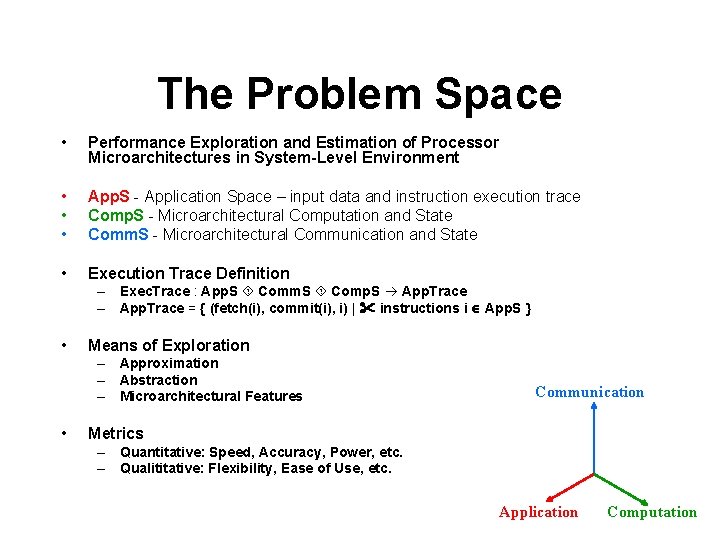

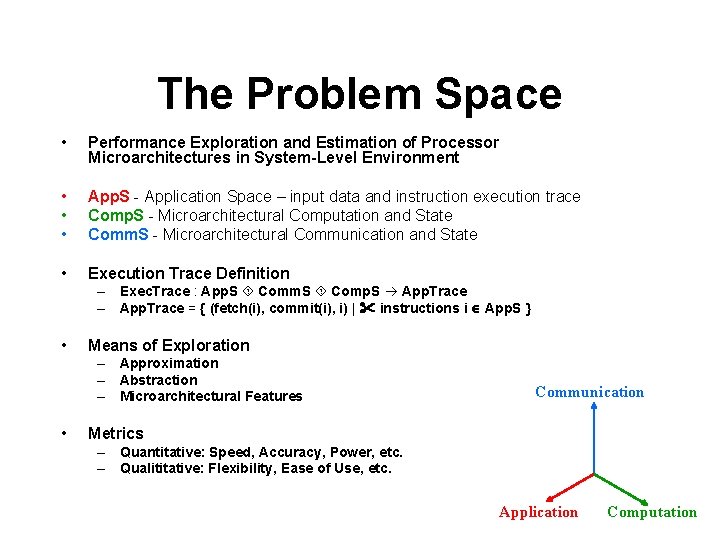

The Problem Space • Performance Exploration and Estimation of Processor Microarchitectures in System-Level Environment • • • App. S - Application Space – input data and instruction execution trace Comp. S - Microarchitectural Computation and State Comm. S - Microarchitectural Communication and State • Execution Trace Definition – Exec. Trace : App. S Comm. S Comp. S App. Trace – App. Trace = { (fetch(i), commit(i), i) | instructions i App. S } • Means of Exploration – Approximation – Abstraction – Microarchitectural Features • Communication Metrics – Quantitative: Speed, Accuracy, Power, etc. – Qualititative: Flexibility, Ease of Use, etc. Application Computation

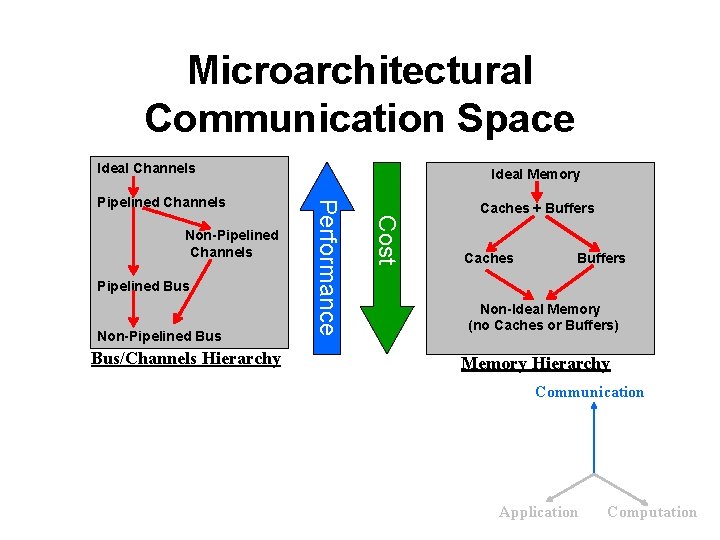

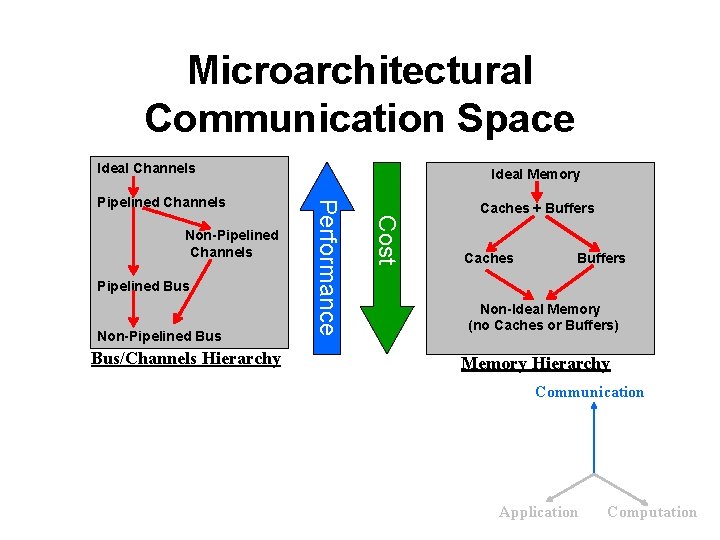

Microarchitectural Communication Space Ideal Channels Pipelined Bus Non-Pipelined Bus/Channels Hierarchy Cost Non-Pipelined Channels Performance Pipelined Channels Ideal Memory Caches + Buffers Caches Buffers Non-Ideal Memory (no Caches or Buffers) Memory Hierarchy Communication Application Computation

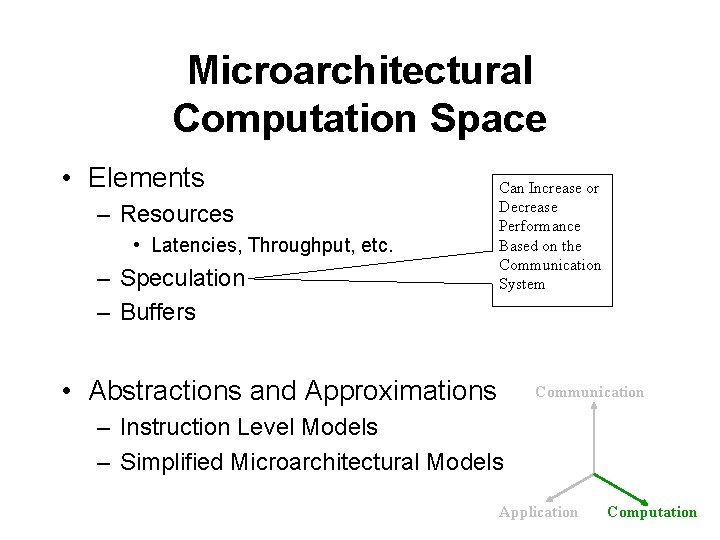

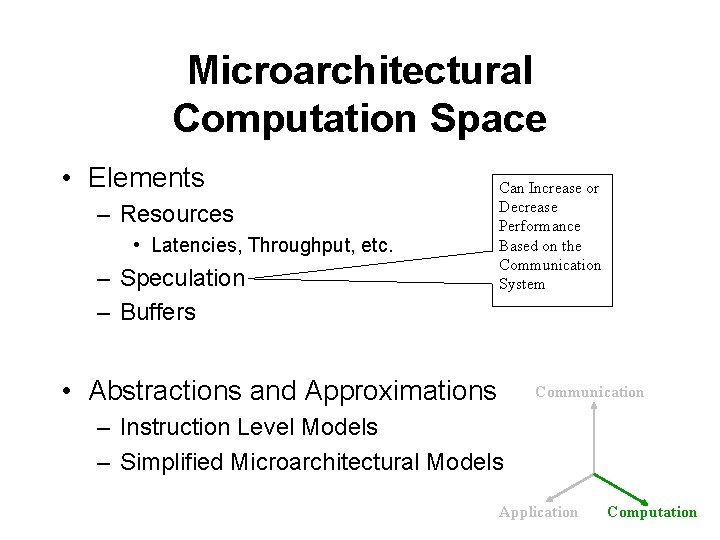

Microarchitectural Computation Space • Elements – Resources • Latencies, Throughput, etc. – Speculation – Buffers Can Increase or Decrease Performance Based on the Communication System • Abstractions and Approximations Communication – Instruction Level Models – Simplified Microarchitectural Models Application Computation

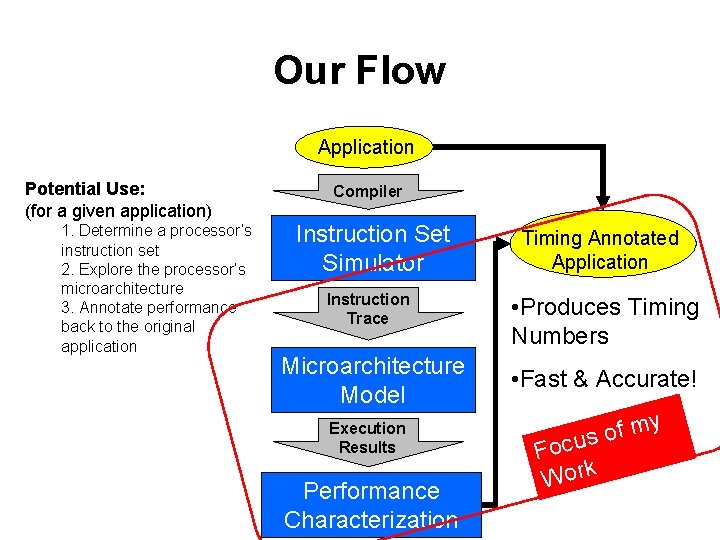

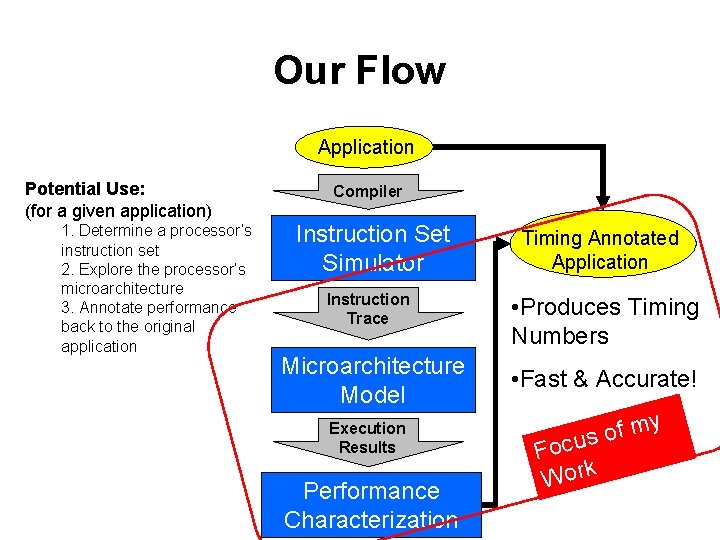

Our Flow Application Potential Use: (for a given application) 1. Determine a processor’s instruction set 2. Explore the processor’s microarchitecture 3. Annotate performance back to the original application Compiler Instruction Set Simulator Instruction Trace Microarchitecture Model Execution Results Performance Characterization Timing Annotated Application • Produces Timing Numbers • Fast & Accurate! y m f o s Focu Work

Final Words n Transaction-Level Modeling is an important idea in that it’s higher than RTL, but the term means different things to different people (still…) n Many Open Questions Remain ¨ How can the different levels of abstraction be related to one another? ¨ IP interchange standards and methodologies ¨ Can we go from algorithms to rtl and still get good results?

![References CCATB S Pasricha N Dutt and M BenRomdhane Extending the Transaction Level Modeling References [CCATB] S. Pasricha, N. Dutt, and M. Ben-Romdhane, “Extending the Transaction Level Modeling](https://slidetodoc.com/presentation_image_h2/a7cf5a347d1a32f784690b3b88c6f22c/image-18.jpg)

References [CCATB] S. Pasricha, N. Dutt, and M. Ben-Romdhane, “Extending the Transaction Level Modeling Approach for Fast Communication Architecture Exploration. ”, DAC, June 2004. [OCP] Open Core Protocol Web Site: www. ocpip. org [SPECC] Cai, L. and Gajski, D. "Transaction Level Modeling: An Overview, “, ISSS-CODES’ 03. [SYSTEMC] Grotker, T. , Liao, S. , Martin, G. , Swan, S. “System Design with System. C”, Kluwer Academic, 2002. [SYSC-TLM] Donlin, A. “Transaction Level Modeling: Flows and Use Models”, ISSS-CODES’ 04