TPC Large Prototype Vers les 7 modules Micromegas

- Slides: 17

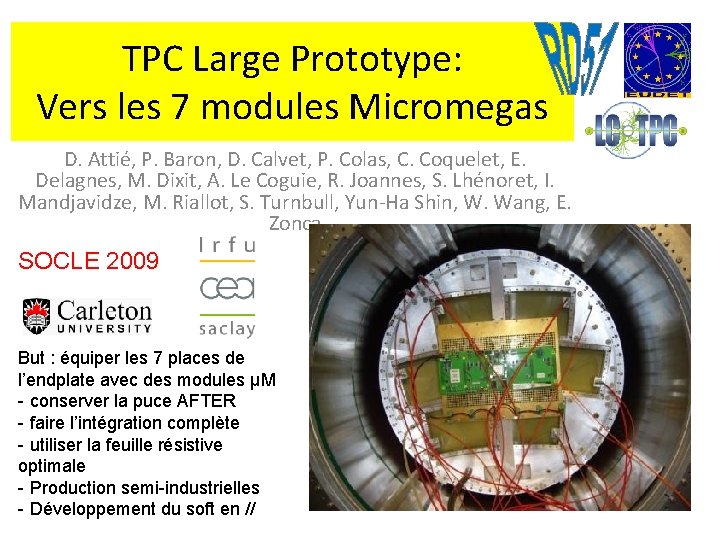

TPC Large Prototype: Vers les 7 modules Micromegas D. Attié, P. Baron, D. Calvet, P. Colas, C. Coquelet, E. Delagnes, M. Dixit, A. Le Coguie, R. Joannes, S. Lhénoret, I. Mandjavidze, M. Riallot, S. Turnbull, Yun-Ha Shin, W. Wang, E. Zonca SOCLE 2009 But : équiper les 7 places de l’endplate avec des modules µM - conserver la puce AFTER - faire l’intégration complète - utiliser la feuille résistive optimale - Production semi-industrielles - Développement du soft en //

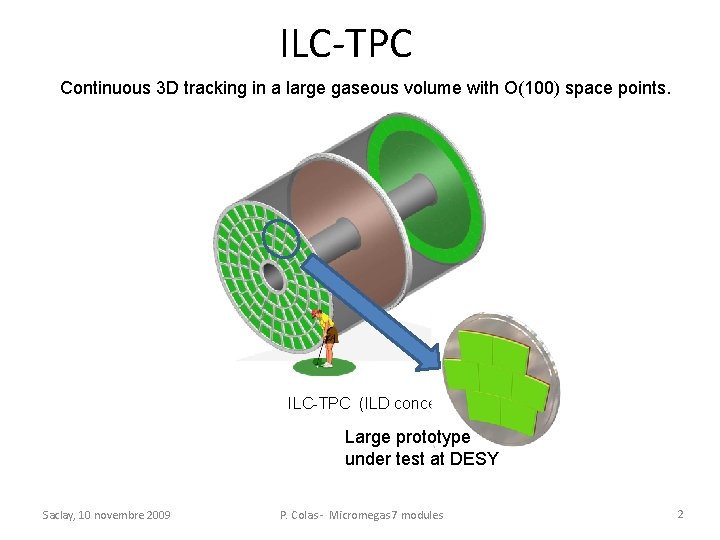

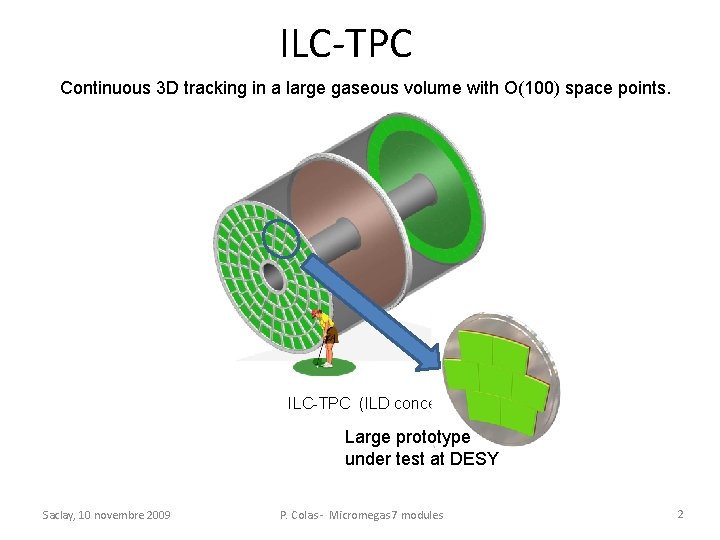

ILC-TPC Continuous 3 D tracking in a large gaseous volume with O(100) space points. ILC-TPC (ILD concept) Large prototype under test at DESY Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 2

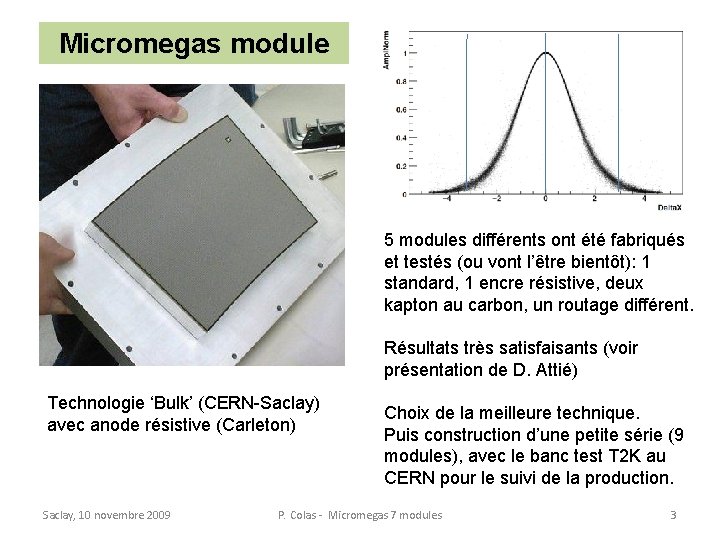

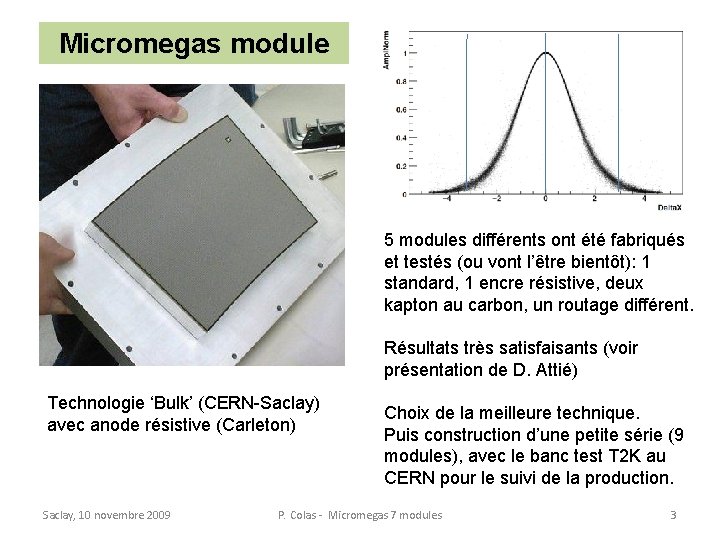

Micromegas module 5 modules différents ont été fabriqués et testés (ou vont l’être bientôt): 1 standard, 1 encre résistive, deux kapton au carbon, un routage différent. Résultats très satisfaisants (voir présentation de D. Attié) Technologie ‘Bulk’ (CERN-Saclay) avec anode résistive (Carleton) Saclay, 10 novembre 2009 Choix de la meilleure technique. Puis construction d’une petite série (9 modules), avec le banc test T 2 K au CERN pour le suivi de la production. P. Colas - Micromegas 7 modules 3

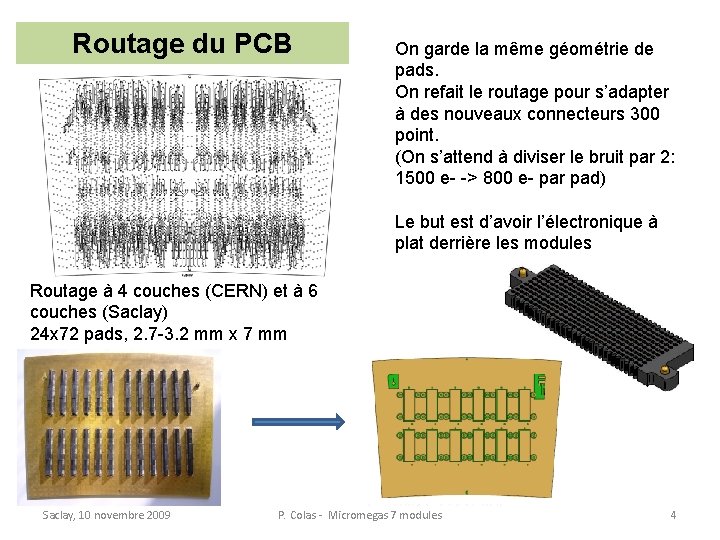

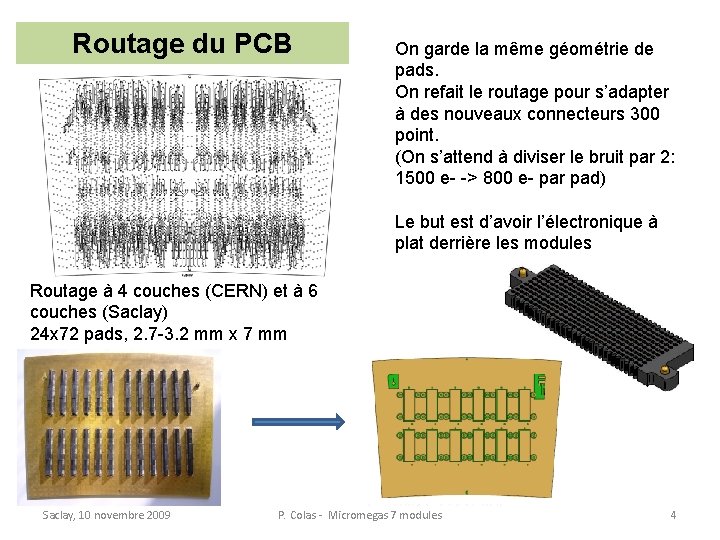

Routage du PCB On garde la même géométrie de pads. On refait le routage pour s’adapter à des nouveaux connecteurs 300 point. (On s’attend à diviser le bruit par 2: 1500 e- -> 800 e- par pad) Le but est d’avoir l’électronique à plat derrière les modules Routage à 4 couches (CERN) et à 6 couches (Saclay) 24 x 72 pads, 2. 7 -3. 2 mm x 7 mm Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 4

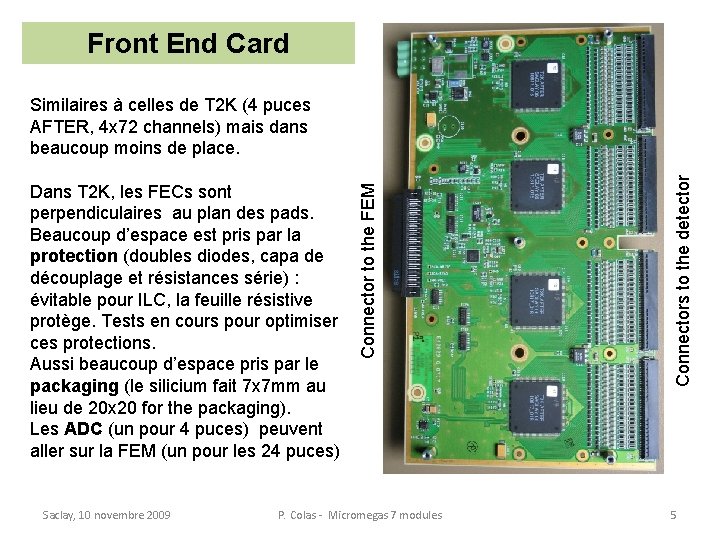

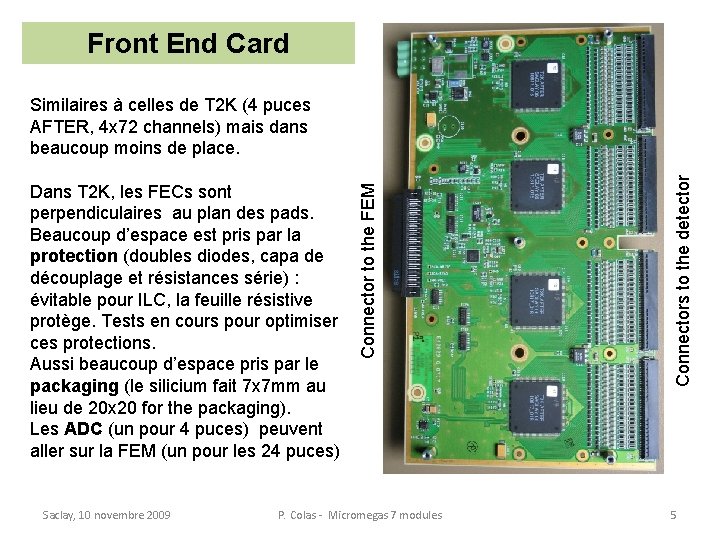

Front End Card Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules Connectors to the detector Dans T 2 K, les FECs sont perpendiculaires au plan des pads. Beaucoup d’espace est pris par la protection (doubles diodes, capa de découplage et résistances série) : évitable pour ILC, la feuille résistive protège. Tests en cours pour optimiser ces protections. Aussi beaucoup d’espace pris par le packaging (le silicium fait 7 x 7 mm au lieu de 20 x 20 for the packaging). Les ADC (un pour 4 puces) peuvent aller sur la FEM (un pour les 24 puces) Connector to the FEM Similaires à celles de T 2 K (4 puces AFTER, 4 x 72 channels) mais dans beaucoup moins de place. 5

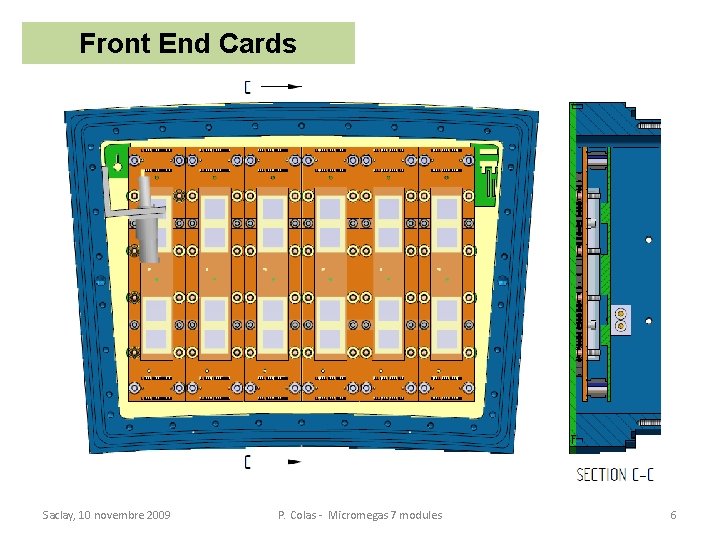

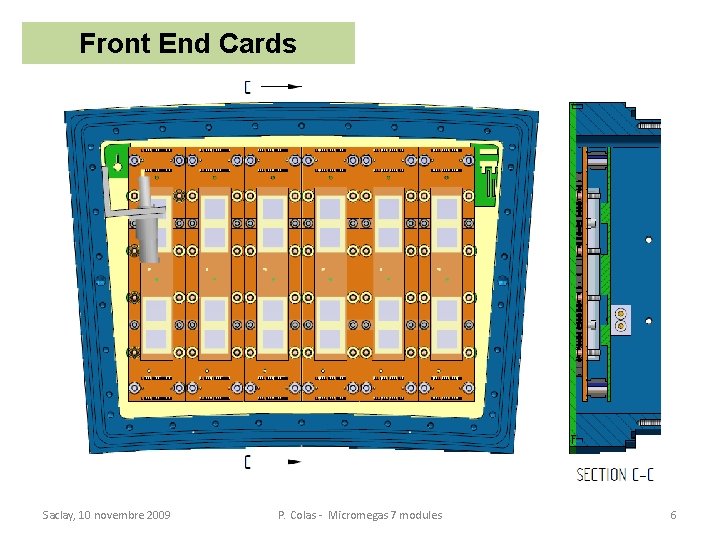

Front End Cards Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 6

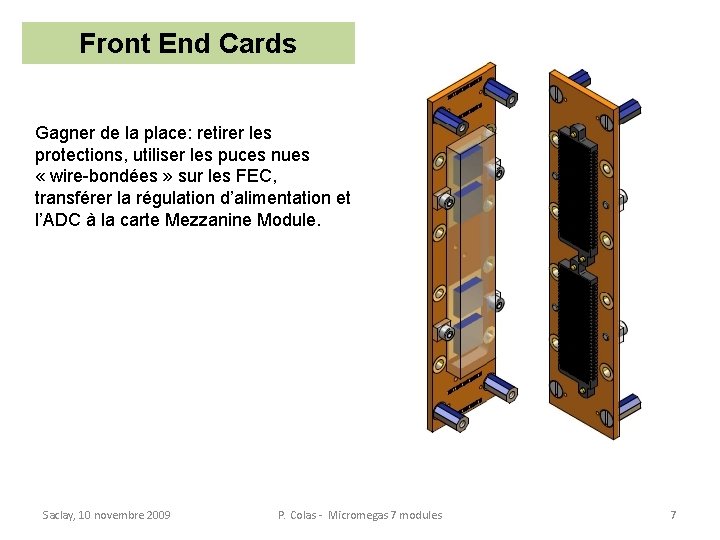

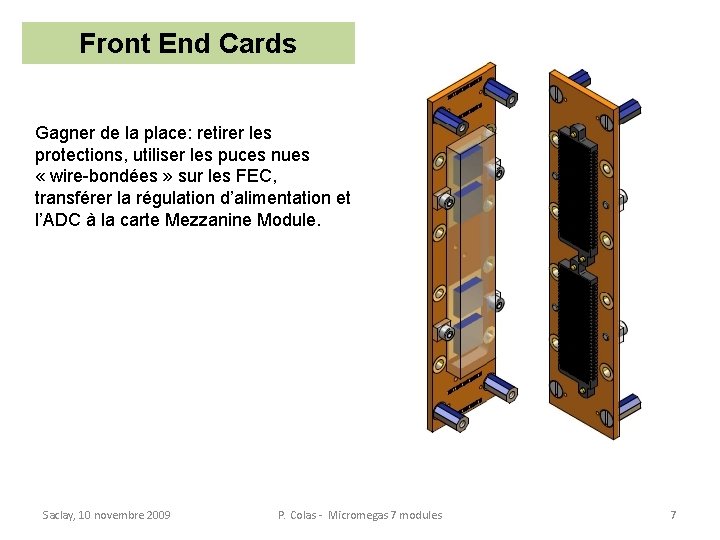

Front End Cards Gagner de la place: retirer les protections, utiliser les puces nues « wire-bondées » sur les FEC, transférer la régulation d’alimentation et l’ADC à la carte Mezzanine Module. Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 7

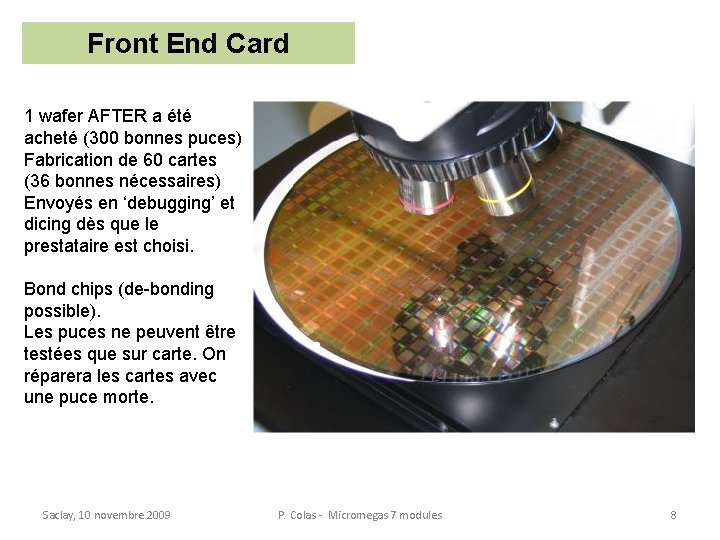

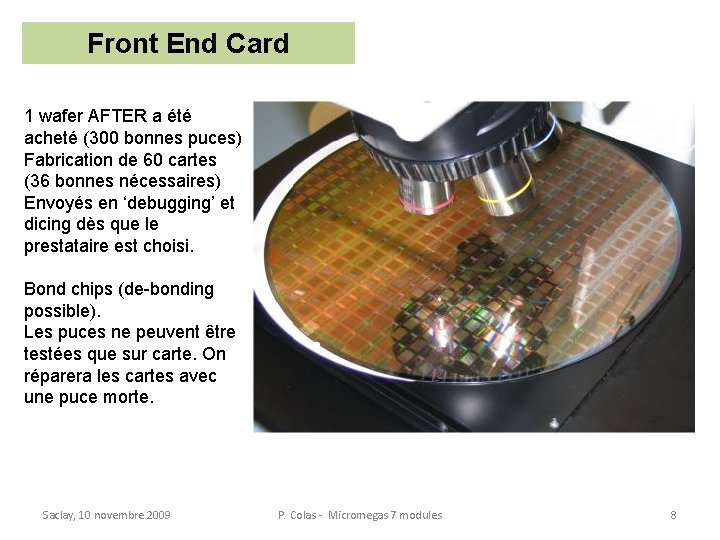

Front End Card 1 wafer AFTER a été acheté (300 bonnes puces) Fabrication de 60 cartes (36 bonnes nécessaires) Envoyés en ‘debugging’ et dicing dès que le prestataire est choisi. Bond chips (de-bonding possible). Les puces ne peuvent être testées que sur carte. On réparera les cartes avec une puce morte. Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 8

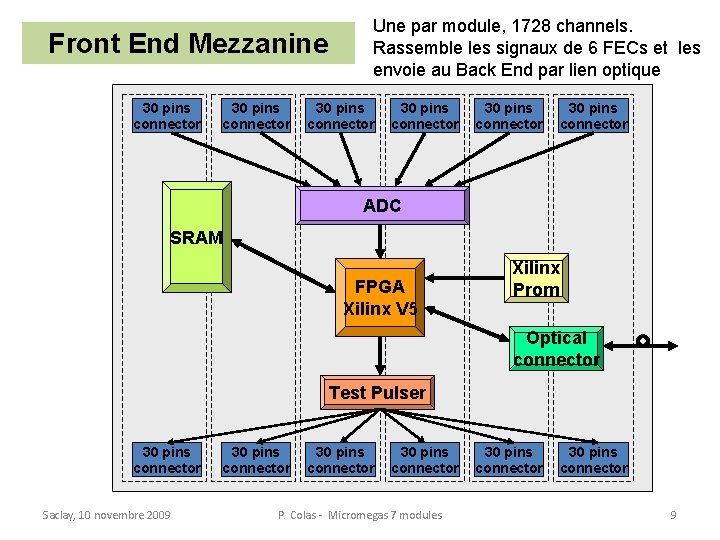

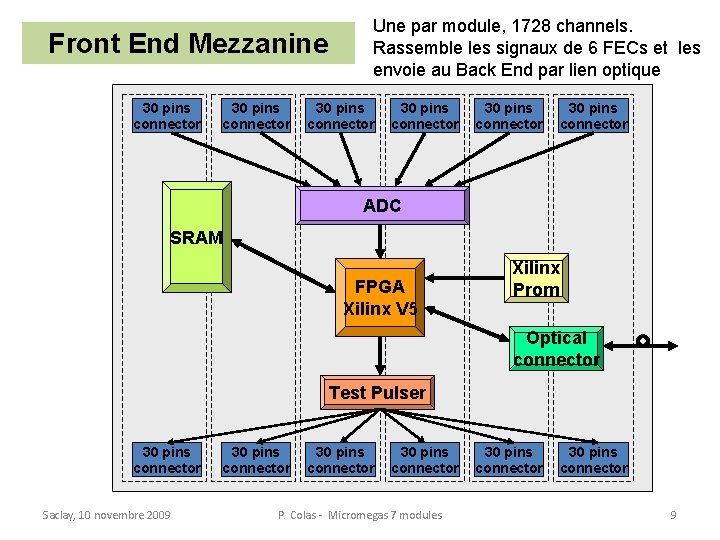

Front End Mezzanine 30 pins connector Une par module, 1728 channels. Rassemble les signaux de 6 FECs et les envoie au Back End par lien optique 30 pins connector ADC SRAM FPGA Xilinx V 5 Xilinx Prom Optical connector Test Pulser 30 pins connector Saclay, 10 novembre 2009 30 pins connector P. Colas - Micromegas 7 modules 30 pins connector 9

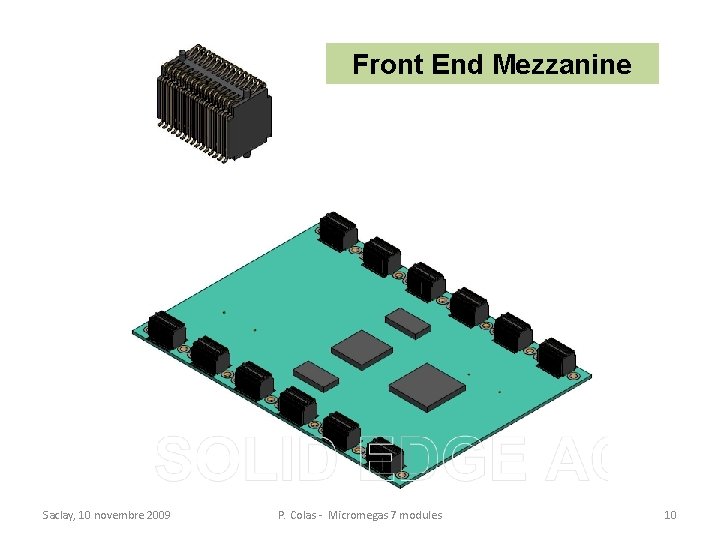

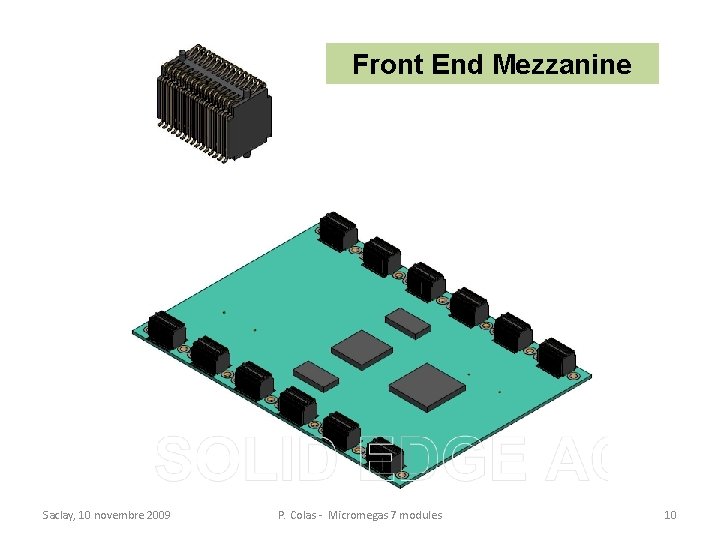

Front End Mezzanine Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 10

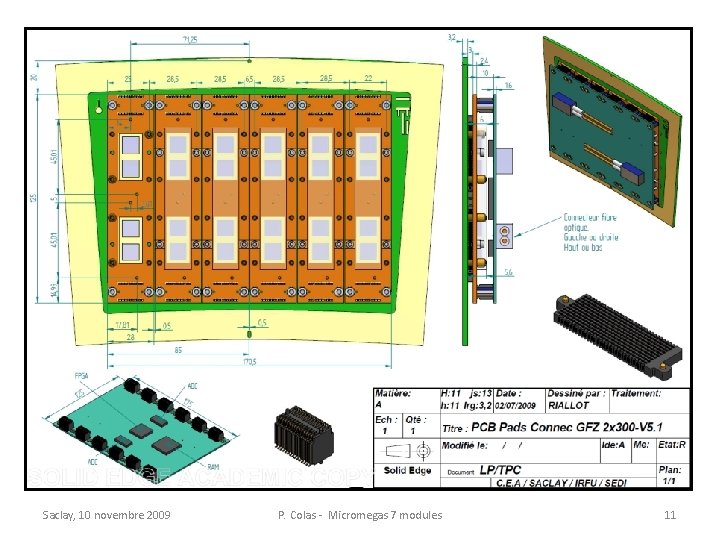

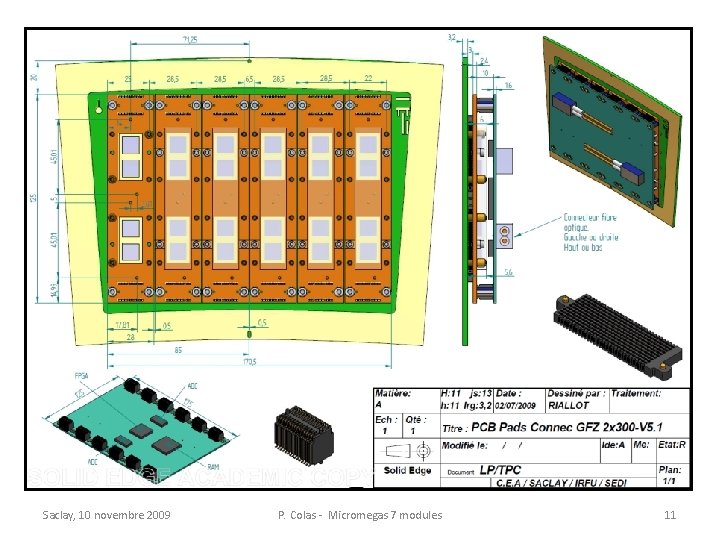

Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 11

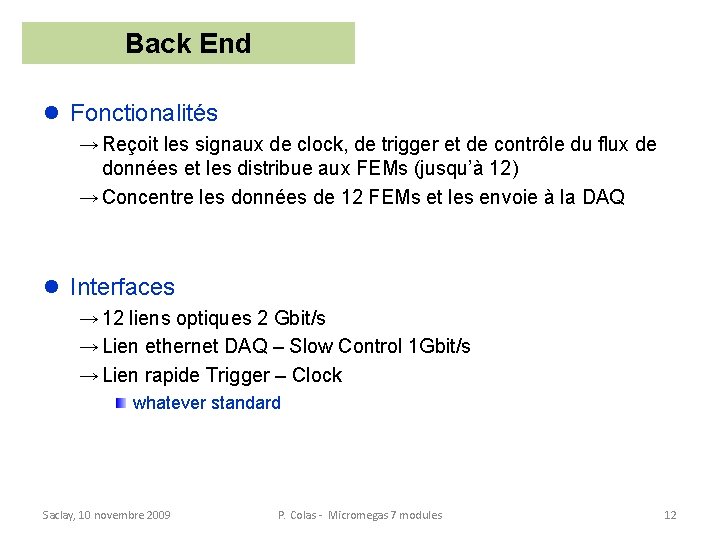

Back End l Fonctionalités → Reçoit les signaux de clock, de trigger et de contrôle du flux de données et les distribue aux FEMs (jusqu’à 12) → Concentre les données de 12 FEMs et les envoie à la DAQ l Interfaces → 12 liens optiques 2 Gbit/s → Lien ethernet DAQ – Slow Control 1 Gbit/s → Lien rapide Trigger – Clock whatever standard Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 12

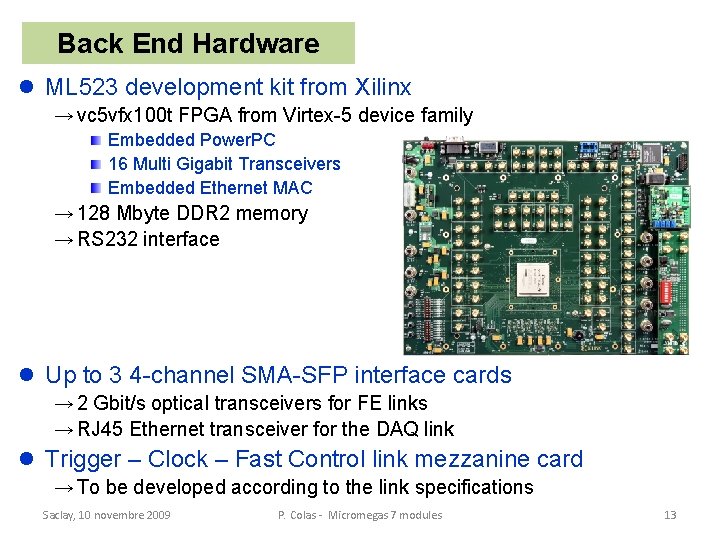

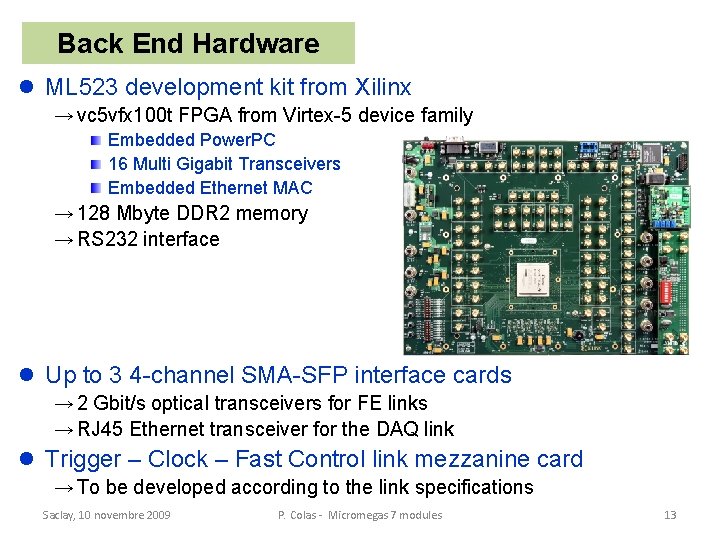

Back End Hardware l ML 523 development kit from Xilinx → vc 5 vfx 100 t FPGA from Virtex-5 device family Embedded Power. PC 16 Multi Gigabit Transceivers Embedded Ethernet MAC → 128 Mbyte DDR 2 memory → RS 232 interface l Up to 3 4 -channel SMA-SFP interface cards → 2 Gbit/s optical transceivers for FE links → RJ 45 Ethernet transceiver for the DAQ link l Trigger – Clock – Fast Control link mezzanine card → To be developed according to the link specifications Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 13

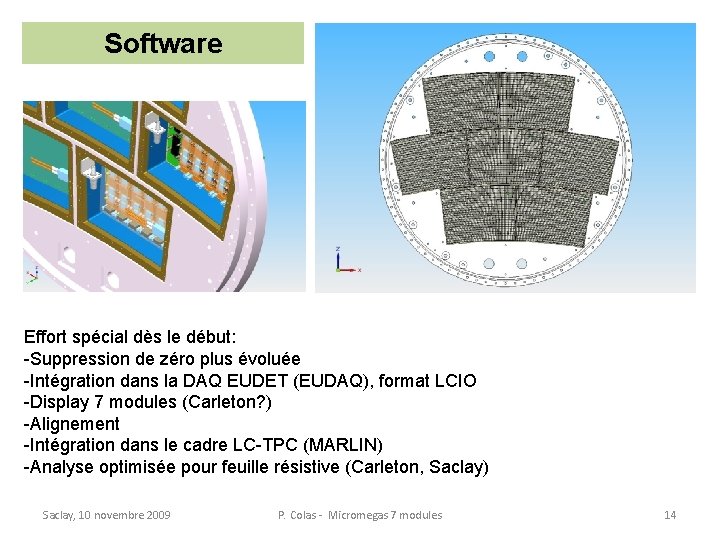

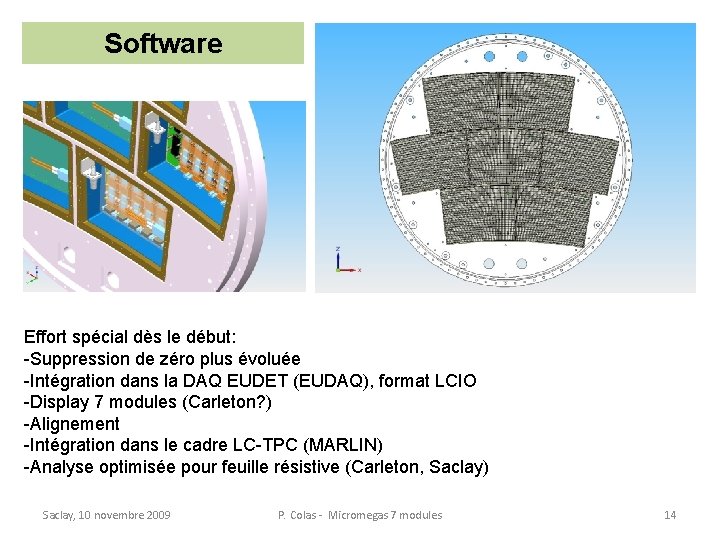

Software Effort spécial dès le début: -Suppression de zéro plus évoluée -Intégration dans la DAQ EUDET (EUDAQ), format LCIO -Display 7 modules (Carleton? ) -Alignement -Intégration dans le cadre LC-TPC (MARLIN) -Analyse optimisée pour feuille résistive (Carleton, Saclay) Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 14

Status and plans PCB routing : started, no show-stopper, 3 -4 weeks FEC routing : concept adopted, details being studied AFTER Wafer : purchased, choice of company to dice, “debug” and bond in progress. Mechanical model : to test new connectors, wire bonding, etc…mechanical model (PCB+FECs+FEM) in November FEM routing : concept adopted, work under progress, 3 months FEM prototype operational : March 2010 Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 15

Status and plans ML 523 development kit from Xilinx - Purchased Embedded Power. PC-based So. C design underway SFP RJ 45 Ethernet link operational 12 2 Gbit/s FE Transceivers up & under tests DDR 2 memory to be debugged 4 -channel SMA-SFP interface cards : Schematics done, placement and routing underway Trigger – Clock – Fast Control link mezzanine card Specifications – to be done Backend overall mechanical structure to be done (Enclosure, power supplies, cooling, connectors) Significant support from Canada Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 16

CONCLUSION Après le succès des runs à 1 module, un grand effort est en cours pour un système TPC intégré à 7 modules Micromegas. De nouveaux concepts : connecteurs plats haute densité, zero-force d’extraction, puces nues sur cartes, et améliorations à la lecture T 2 K: nouveaux ADC et FPGA, nouvelle suppression de zéros Ce sera aussi une production semi-industrielle et une preuve de faisabilité, aux spécifications de la LOI. Saclay, 10 novembre 2009 P. Colas - Micromegas 7 modules 17