Topics Wire delay n Buffer insertion n Crosstalk

Topics Wire delay. n Buffer insertion. n Crosstalk. n Inductive interconnect. n Switch logic. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Wire delay Wires have parasitic resistance, capacitance. n Parasitics start to dominate in deepsubmicron wires. n Distributed RC introduces time of flight along wire into gate-to-gate delay. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

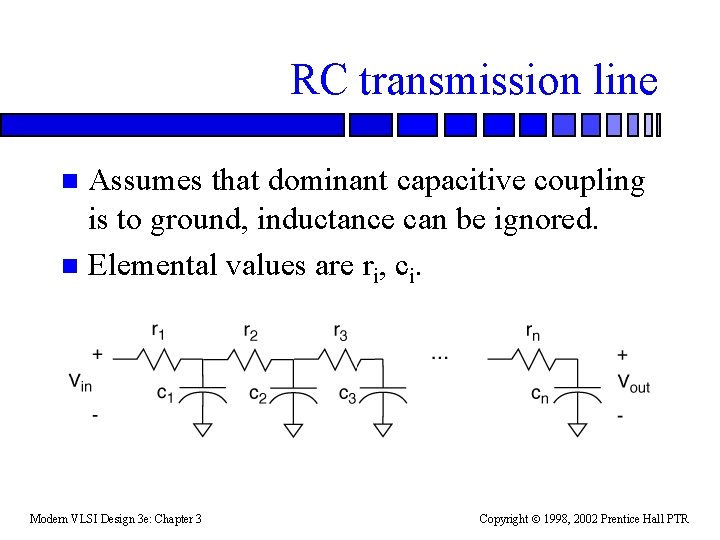

RC transmission line Assumes that dominant capacitive coupling is to ground, inductance can be ignored. n Elemental values are ri, ci. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Elmore delay n Elmore defined delay through linear network as the first moment of the network impulse response. Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

RC Elmore delay n Can be computed as sum of sections: E = r(n - i)c = 0. 5 rcn(n-1) Resistor ri must charge all downstream capacitors. n Delay grows as square of wire length. n Minimizing rc product minimizes growth of delay with increasing wire length. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

RC transmission lines More complex analysis. n Step response: n – V(t) @ 1 + K 1 exp{-s 1 t/RC}. Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Wire sizing Wire length is determined by layout architecture, but we can choose wire width to minimize delay. n Wire width can vary with distance from driver to adjust the resistance which drives downstream capacitance. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Optimal wiresizing Wire with minimum delay has an exponential taper. n Optimal tapering improves delay by about 8%. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

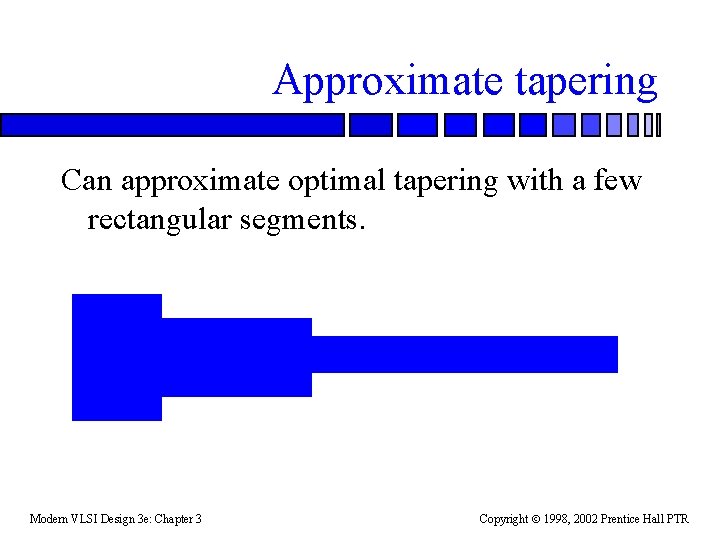

Approximate tapering Can approximate optimal tapering with a few rectangular segments. Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

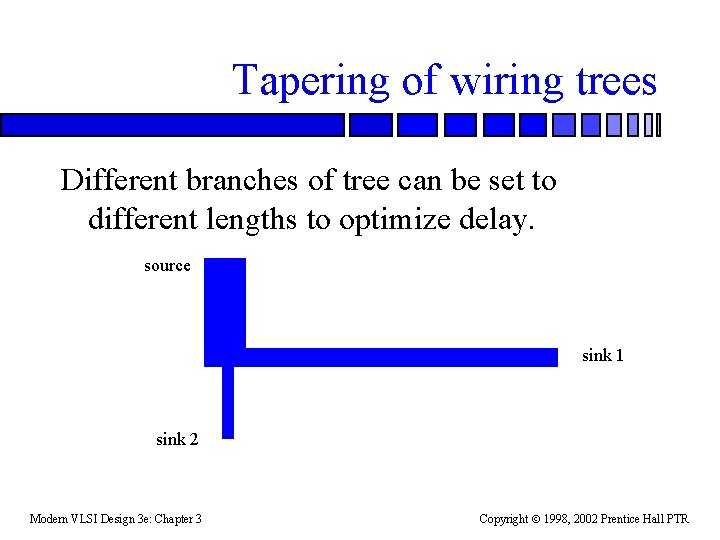

Tapering of wiring trees Different branches of tree can be set to different lengths to optimize delay. source sink 1 sink 2 Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

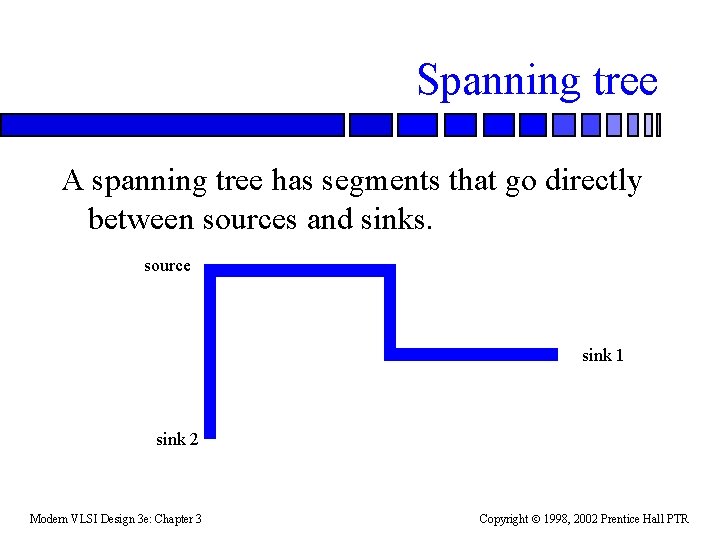

Spanning tree A spanning tree has segments that go directly between sources and sinks. source sink 1 sink 2 Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

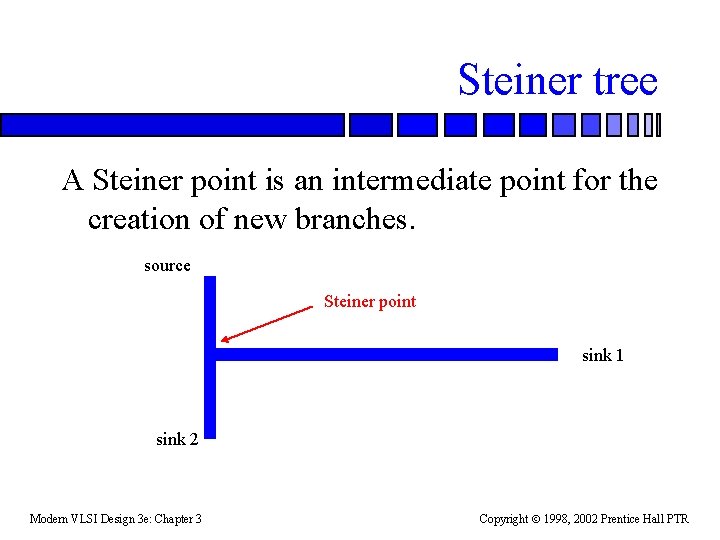

Steiner tree A Steiner point is an intermediate point for the creation of new branches. source Steiner point sink 1 sink 2 Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

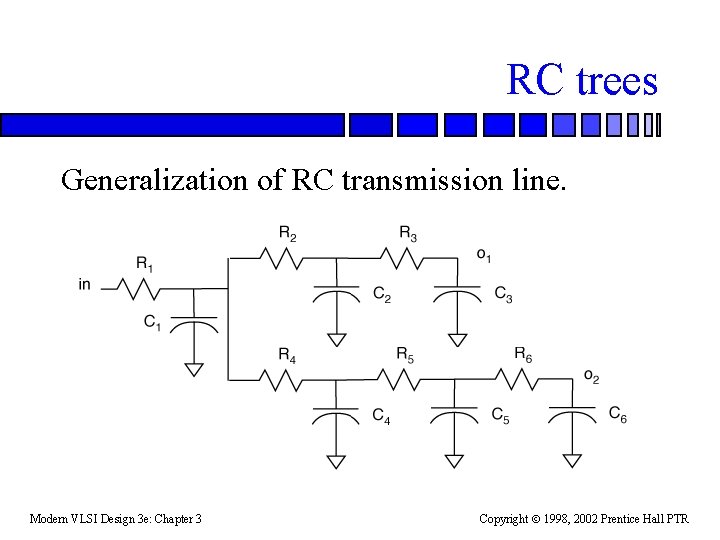

RC trees Generalization of RC transmission line. Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Buffer insertion in RC transmission lines Assume RC transmission line. n Assume R 0 is driver’s resistance, C 0 is driver’s input capacitance. n Want to divide line into k sections of length l. Each buffer is of size h. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

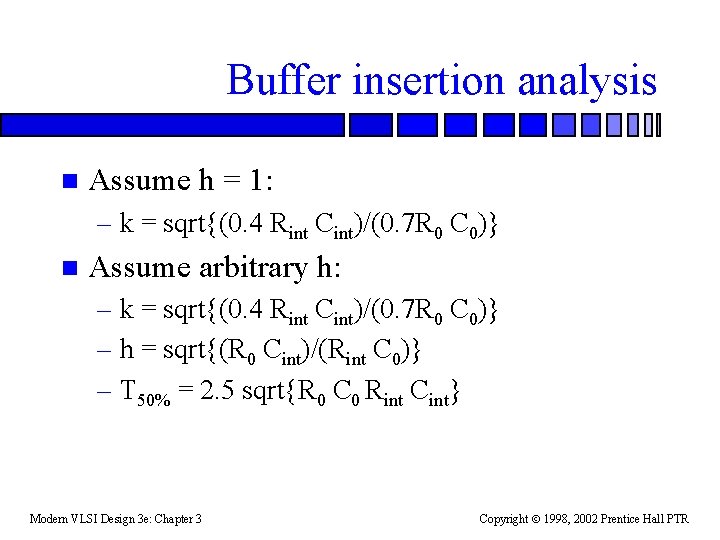

Buffer insertion analysis n Assume h = 1: – k = sqrt{(0. 4 Rint Cint)/(0. 7 R 0 C 0)} n Assume arbitrary h: – k = sqrt{(0. 4 Rint Cint)/(0. 7 R 0 C 0)} – h = sqrt{(R 0 Cint)/(Rint C 0)} – T 50% = 2. 5 sqrt{R 0 C 0 Rint Cint} Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Buffer insertion example n Minimum-size inverter drives metal 1 wire of 2000 l x 3 l. – R 0 = 3. 9 k. W, C 0 = 0. 68 f. F, Rint = 53. 3 k. W, Cint = 105. 1 f. F. n Then – k = 1. 099. – H = 106. 33. – T 50% = 9. 64 E-12 Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

RC crosstalk Crosstalk slows down signals---increases settling noise. n Two nets in analysis: n – aggressor net causes interference; – victim net is interfered with. Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

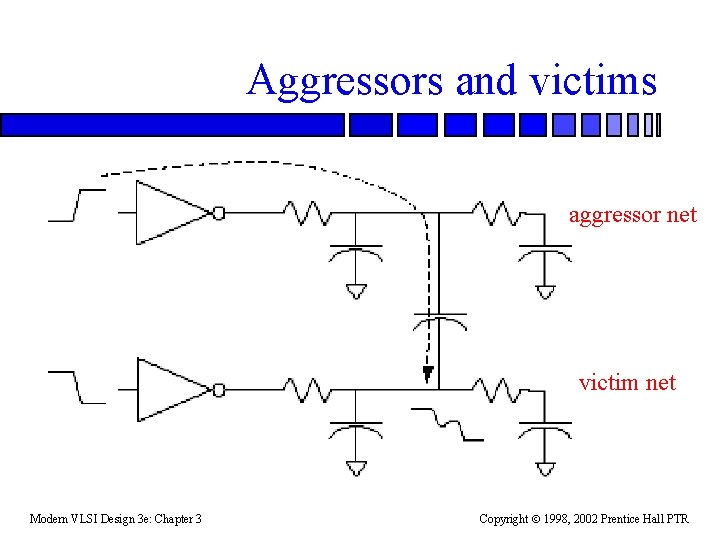

Aggressors and victims aggressor net victim net Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

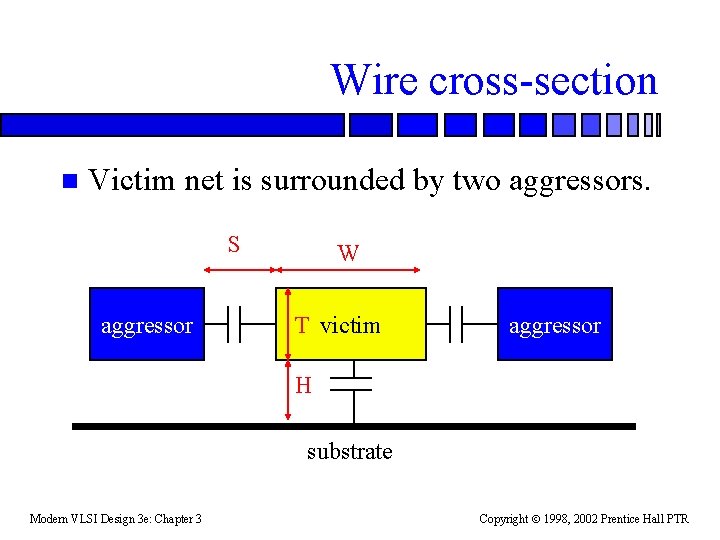

Wire cross-section n Victim net is surrounded by two aggressors. S aggressor W T victim aggressor H substrate Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

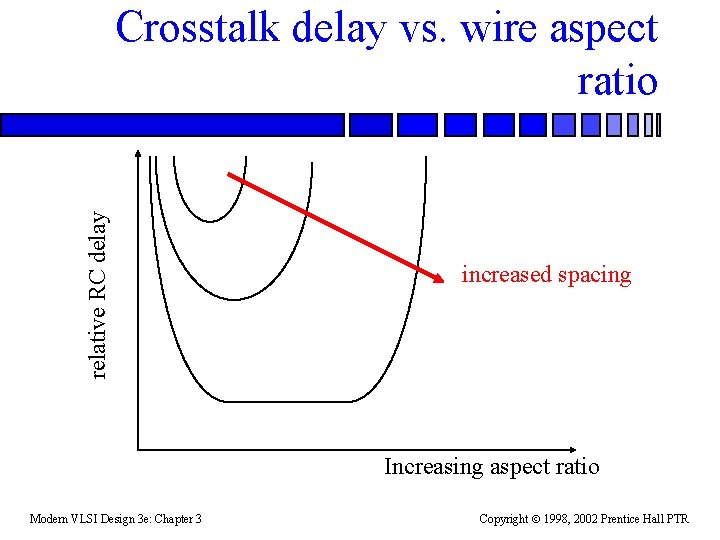

relative RC delay Crosstalk delay vs. wire aspect ratio increased spacing Increasing aspect ratio Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Crosstalk delay There is an optimum wire width for any given wire spacing---at bottom of U curve. n Optimium width increases as spacing between wires increases. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

RLC transmission lines Most results come from curve fitting. n Propagation delay is largely a factor of x. n 50% propagation delay can be calculated in terms of x. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Switch logic Can implement Boolean formulas as networks of switches. n Can build switches from MOS transistors— transmission gates. n Transmission gates do not amplify but have smaller layouts. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

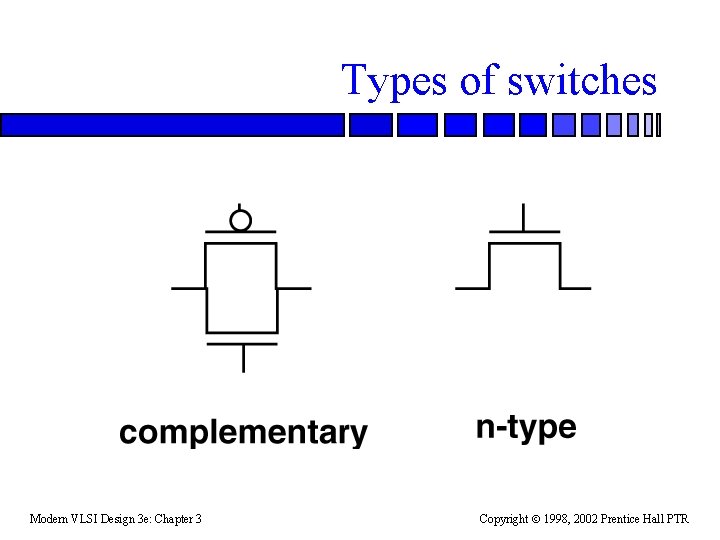

Types of switches Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

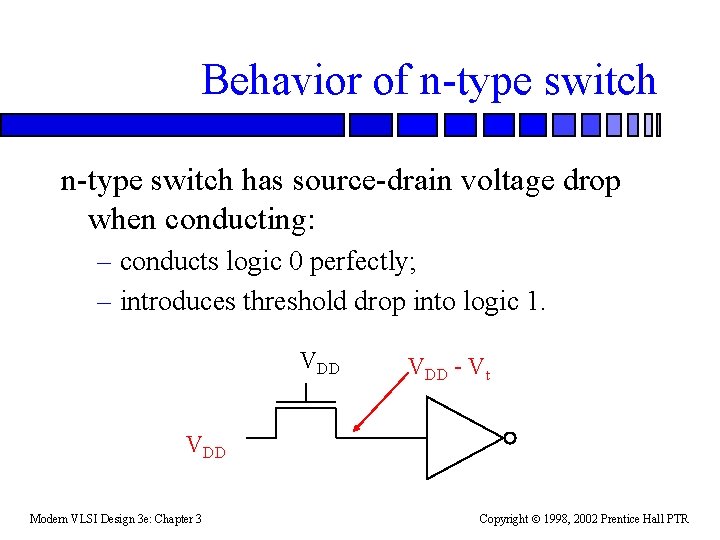

Behavior of n-type switch has source-drain voltage drop when conducting: – conducts logic 0 perfectly; – introduces threshold drop into logic 1. VDD - Vt VDD Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

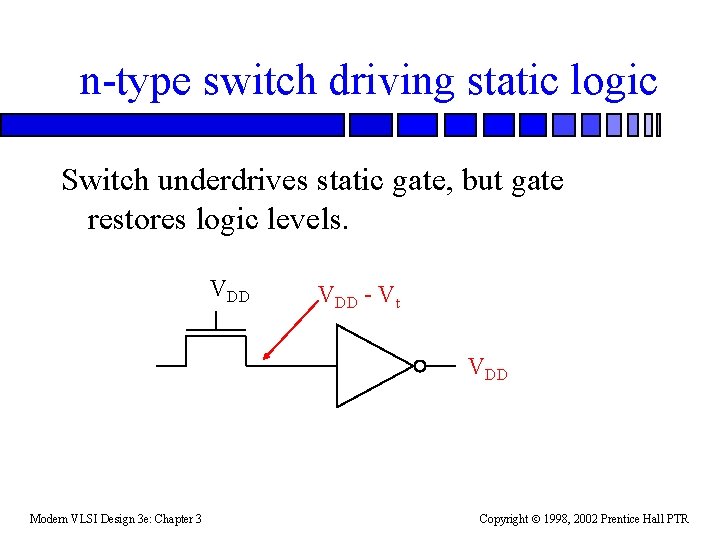

n-type switch driving static logic Switch underdrives static gate, but gate restores logic levels. VDD - Vt VDD Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

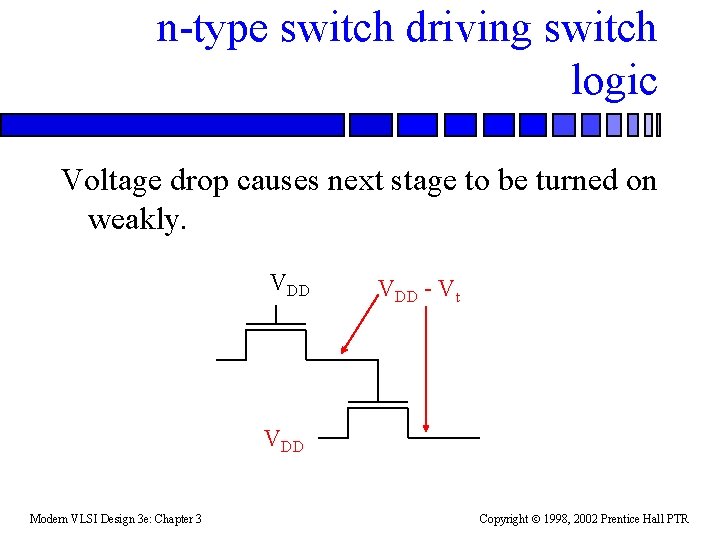

n-type switch driving switch logic Voltage drop causes next stage to be turned on weakly. VDD - Vt VDD Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

Behavior of complementary switch n Complementary switch products full-supply voltages for both logic 0 and logic 1: – n-type transistor conducts logic 0; – p-type transistor conducts logic 1. Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

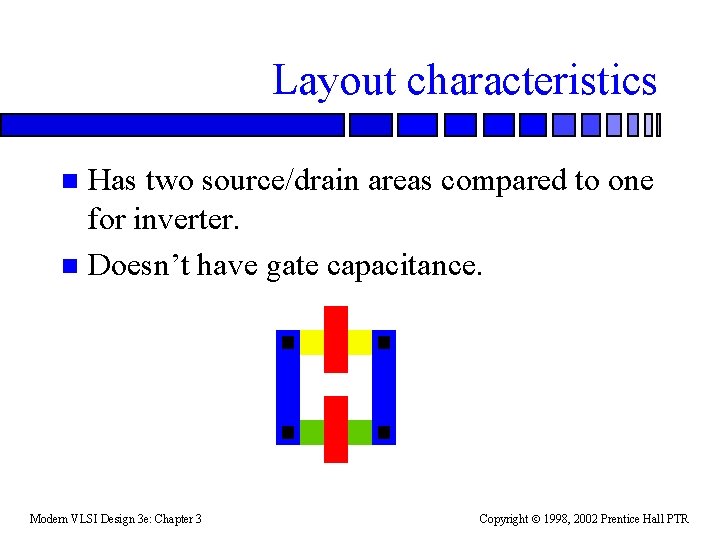

Layout characteristics Has two source/drain areas compared to one for inverter. n Doesn’t have gate capacitance. n Modern VLSI Design 3 e: Chapter 3 Copyright 1998, 2002 Prentice Hall PTR

- Slides: 29