Topics n Sequential machine implementation clocking n Sequential

- Slides: 31

Topics n Sequential machine implementation: – clocking. n Sequential machine design. Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

Clock period n For each phase, phase period must be longer than sum of: – combinational delay; – latch propagation delay. n Phase period depends on longest path. Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

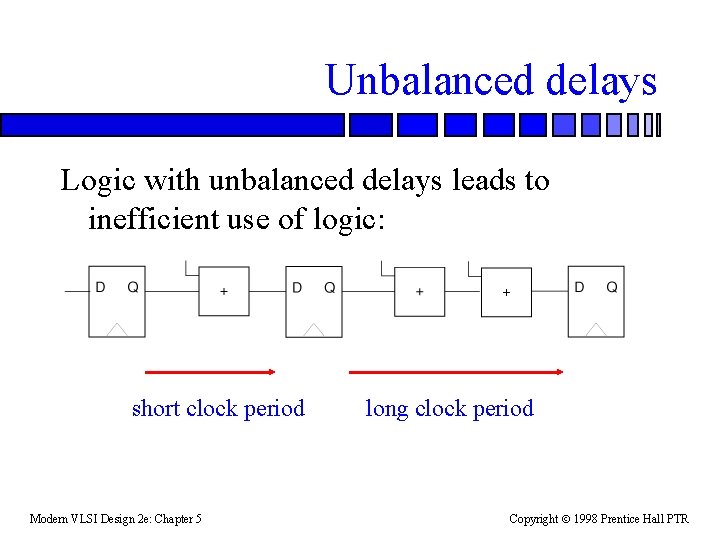

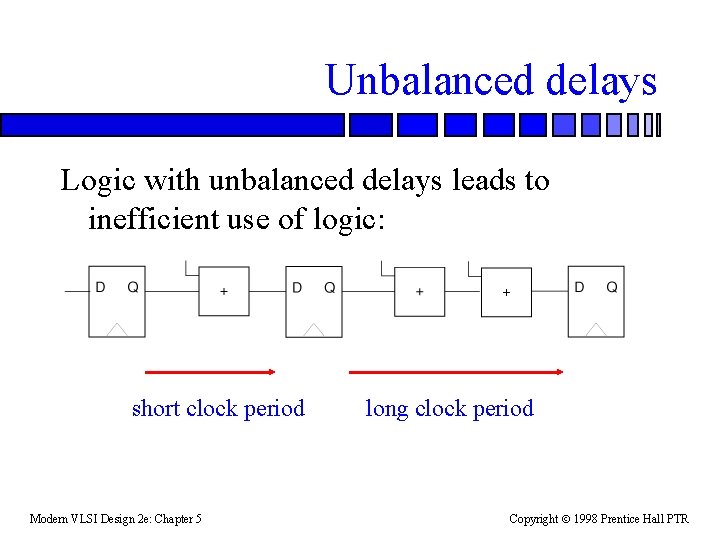

Unbalanced delays Logic with unbalanced delays leads to inefficient use of logic: short clock period Modern VLSI Design 2 e: Chapter 5 long clock period Copyright 1998 Prentice Hall PTR

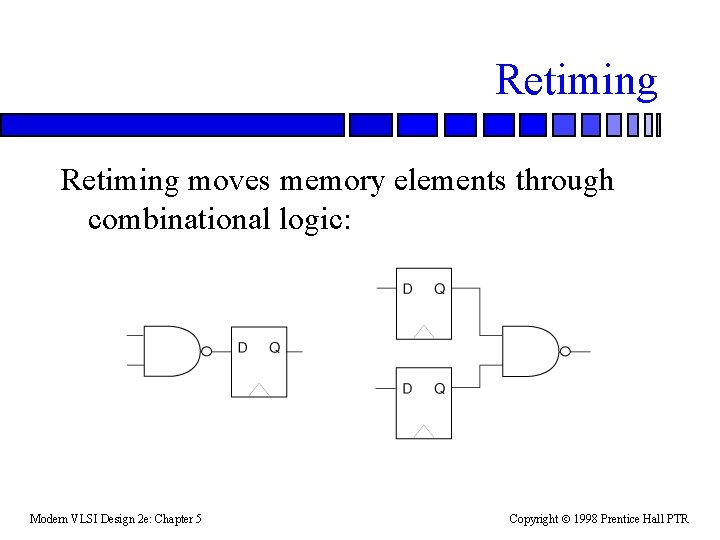

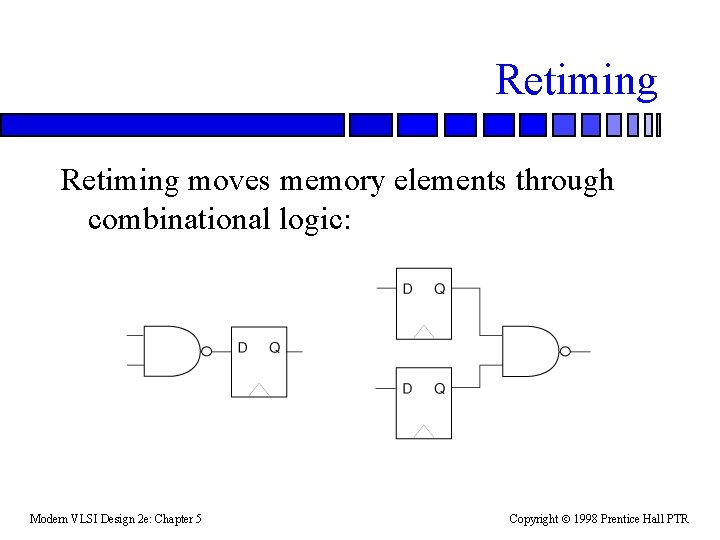

Retiming moves memory elements through combinational logic: Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

Retiming properties Retiming changes encoding of values in registers, but proper values can be reconstructed with combinational logic. n Retiming may increase number of registers required. n Retiming must preserve number of latches around a cycle - may not be possible with reconvergent fanout. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

Advanced performance analysis Latch-based systems always have some idle logic. n Can increase performance by blurring phase boundaries. Results in cycle time closer to average of phases. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

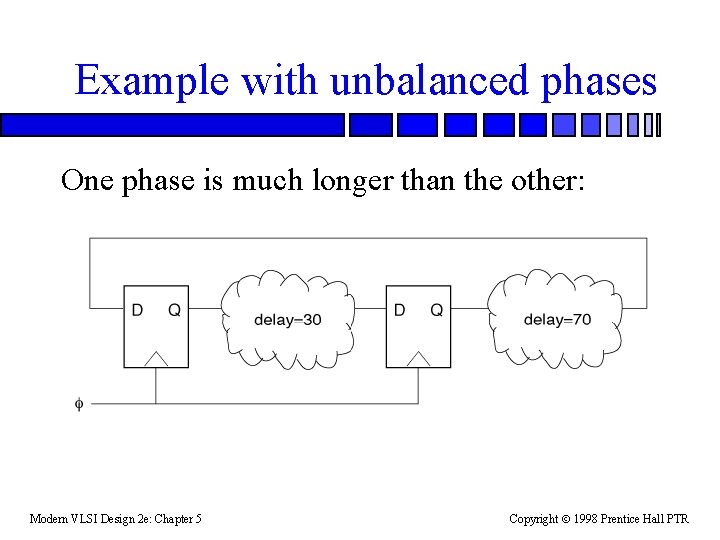

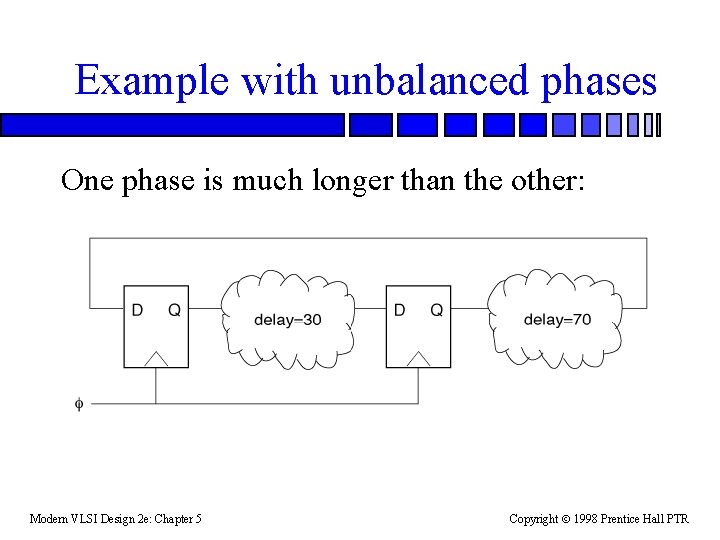

Example with unbalanced phases One phase is much longer than the other: Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

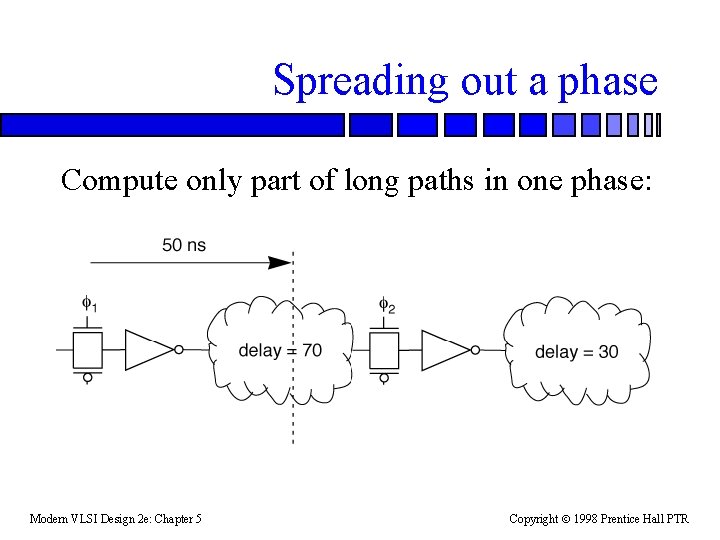

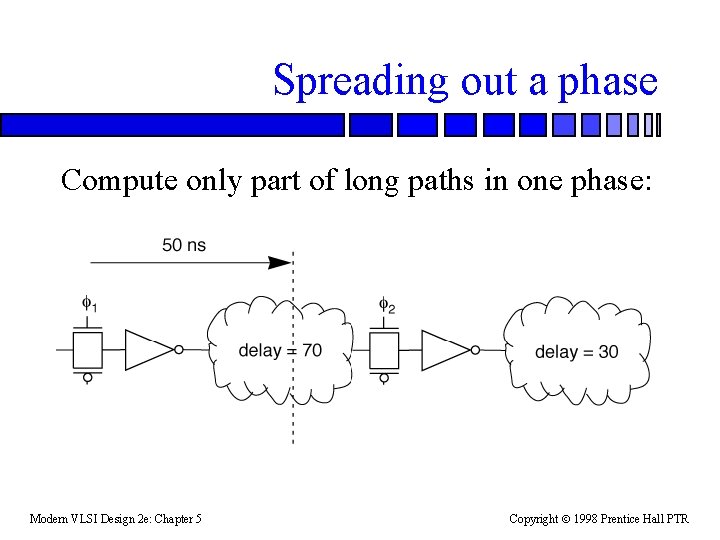

Spreading out a phase Compute only part of long paths in one phase: Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

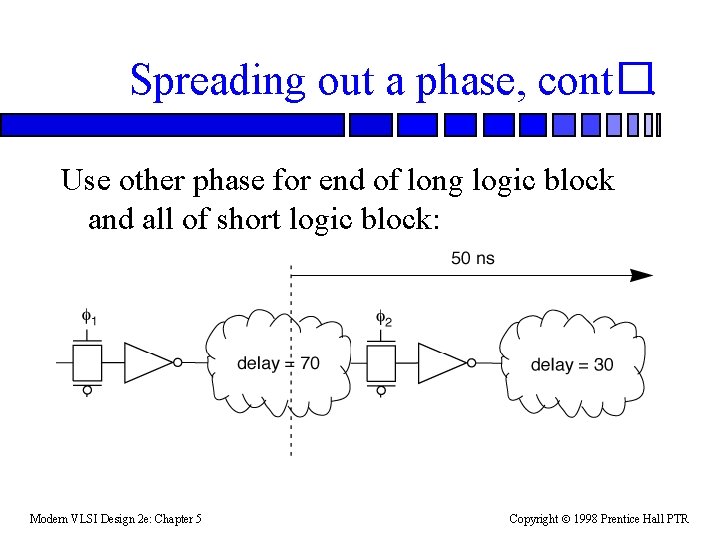

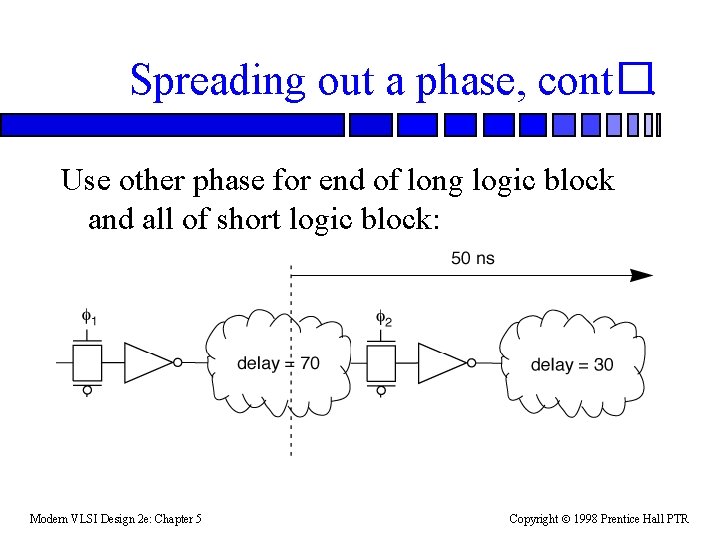

Spreading out a phase, cont�. Use other phase for end of long logic block and all of short logic block: Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

Problems Hard to debug - can’t stop the system. n Hard to initialize system state. n More sensitive to process variations. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

Sequential machine design n Two ways to specify sequential machine: – structure: interconnection of logic gates and memory elements. – function: Boolean description of next-state and output functions. n Best way depends on type of machine being described. Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

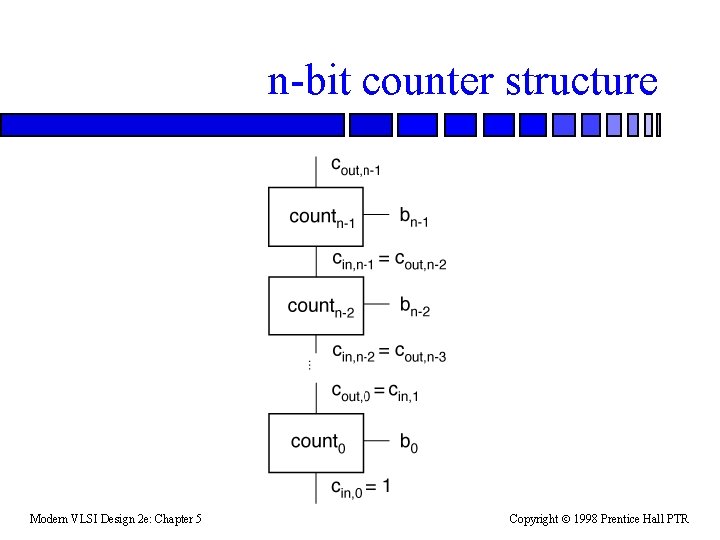

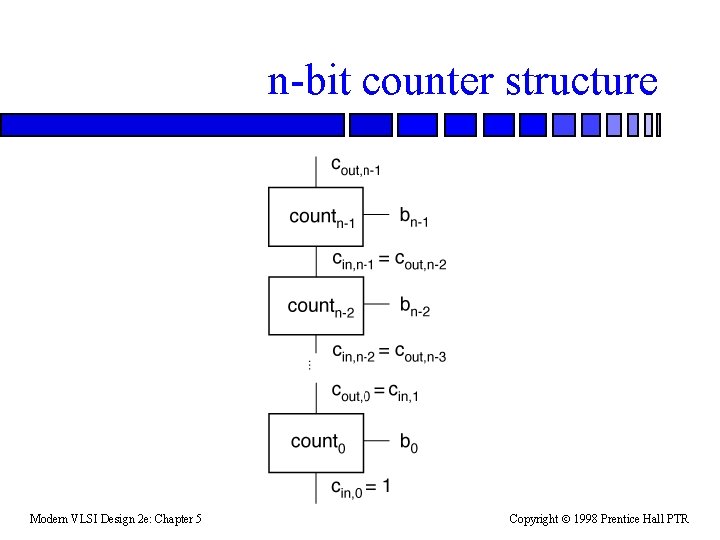

Counter Easy to specify as one-bit counter. n Harder to specify n-bit counter behavior. Can specify n-bit counter as structure made of 1 -bit counters. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

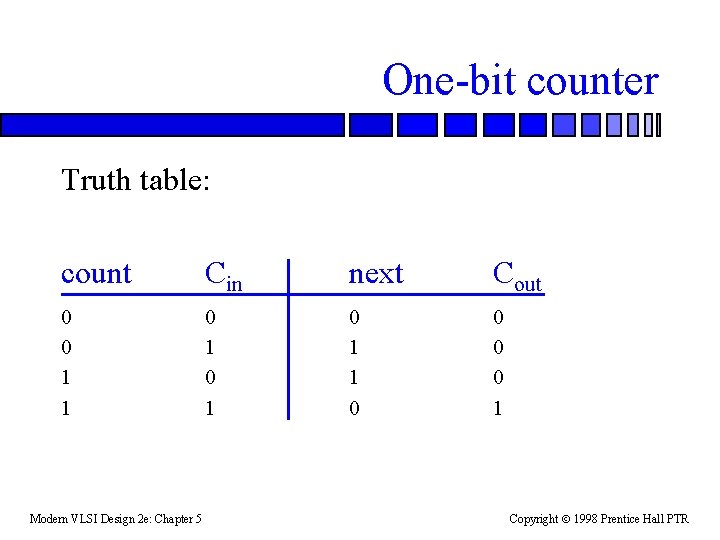

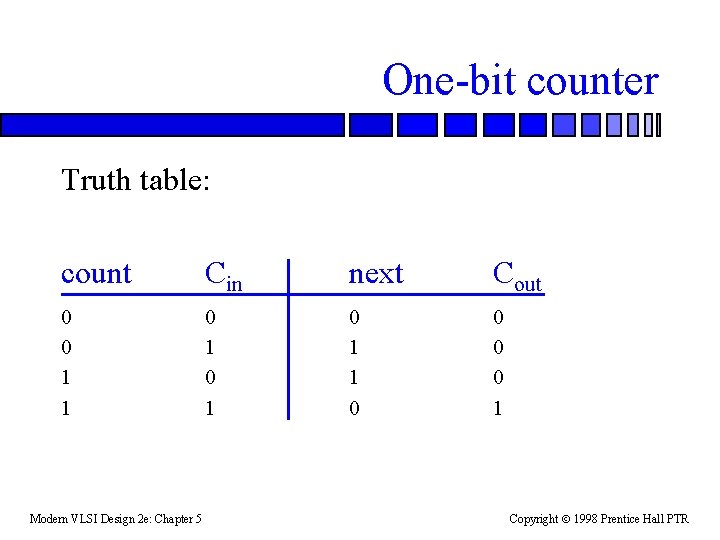

One-bit counter Truth table: count Cin next Cout 0 0 1 1 0 1 0 1 1 0 0 1 Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

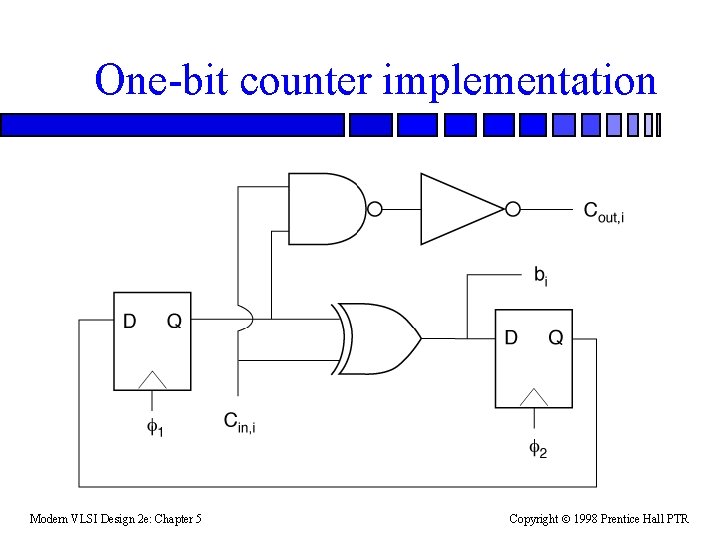

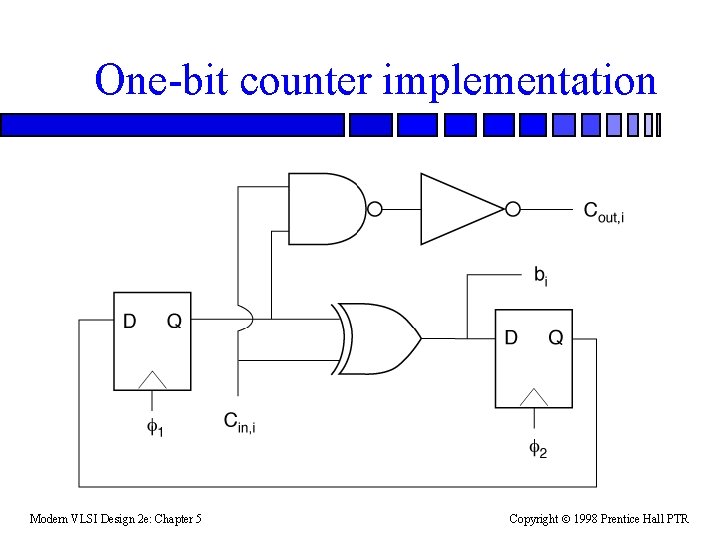

One-bit counter implementation Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

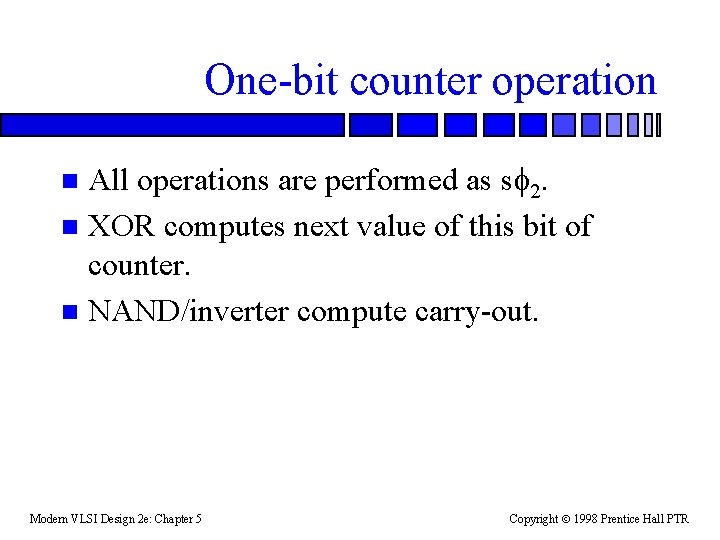

One-bit counter operation All operations are performed as s 2. n XOR computes next value of this bit of counter. n NAND/inverter compute carry-out. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

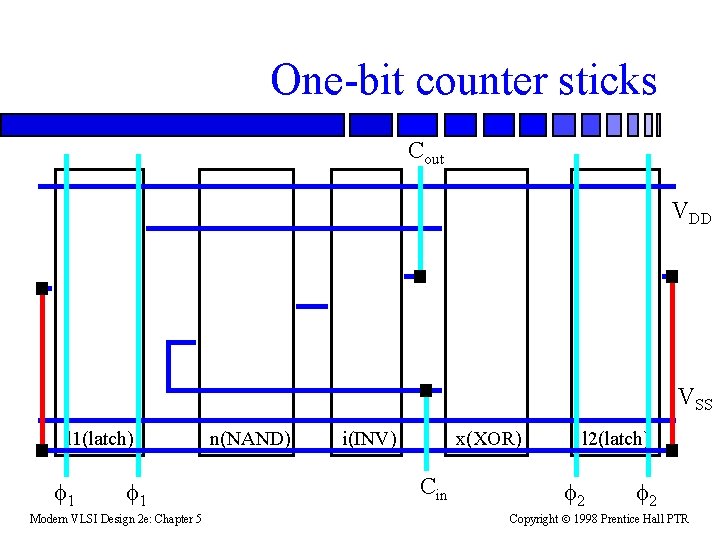

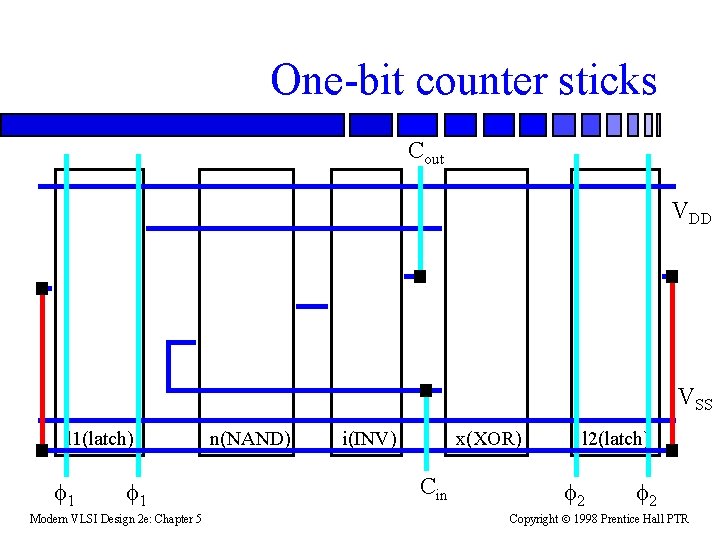

One-bit counter sticks Cout VDD VSS l 1(latch) 1 1 Modern VLSI Design 2 e: Chapter 5 n(NAND) i(INV) x(XOR) Cin l 2(latch) 2 2 Copyright 1998 Prentice Hall PTR

n-bit counter structure Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

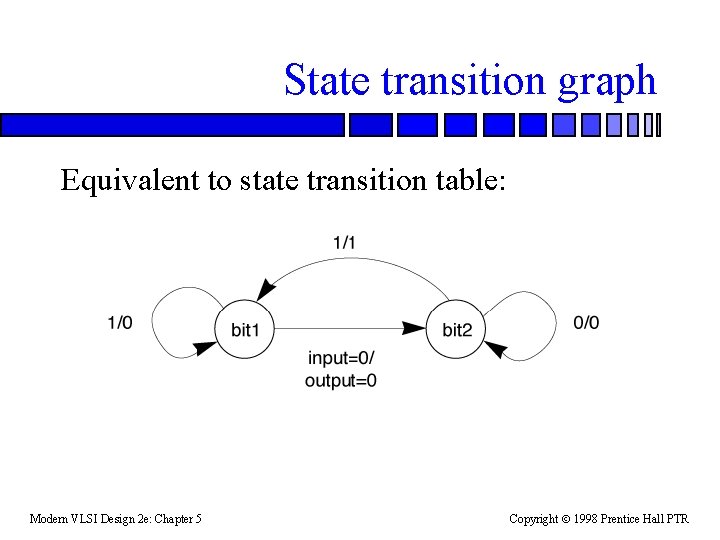

State transition graphs/tables Basic functional description of FSM. n Symbolic truth table for next-state, output functions: n – no structure of logic; – no encoding of states. n State transition graph and table are functionally equivalent. Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

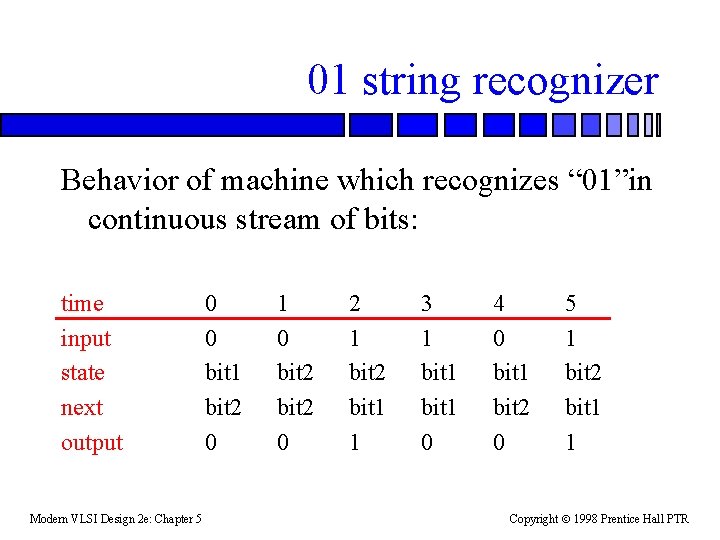

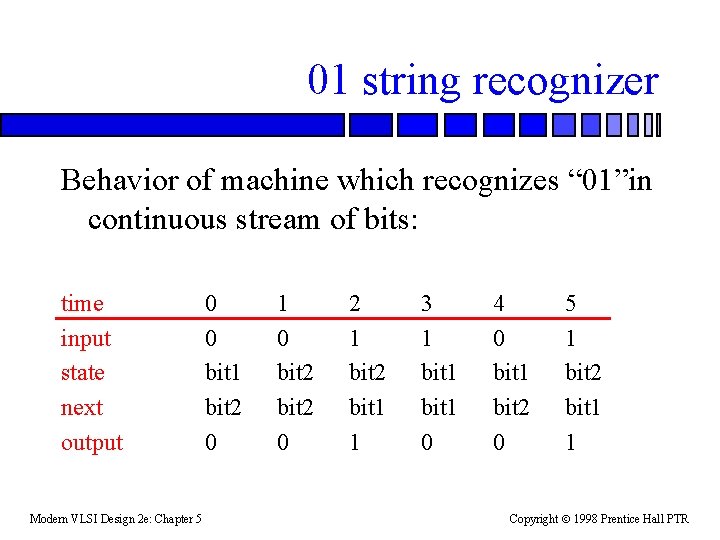

01 string recognizer Behavior of machine which recognizes “ 01”in continuous stream of bits: time input state next output Modern VLSI Design 2 e: Chapter 5 0 0 bit 1 bit 2 0 1 0 bit 2 0 2 1 bit 2 bit 1 1 3 1 bit 1 0 4 0 bit 1 bit 2 0 5 1 bit 2 bit 1 1 Copyright 1998 Prentice Hall PTR

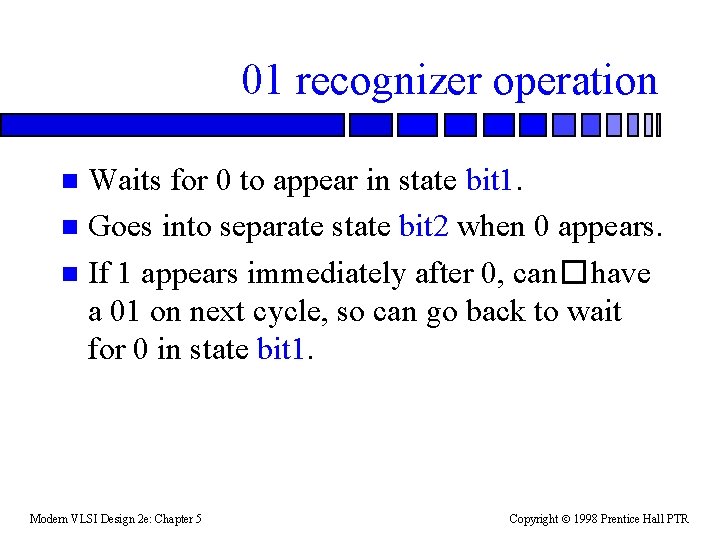

01 recognizer operation Waits for 0 to appear in state bit 1. n Goes into separate state bit 2 when 0 appears. n If 1 appears immediately after 0, can� have a 01 on next cycle, so can go back to wait for 0 in state bit 1. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

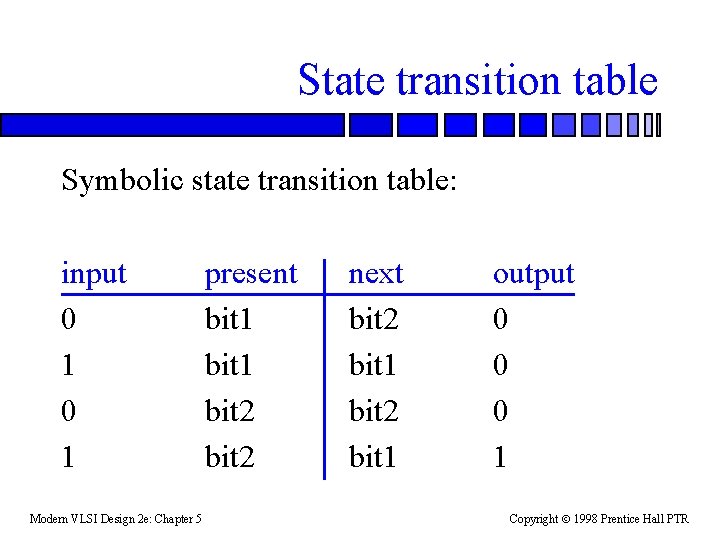

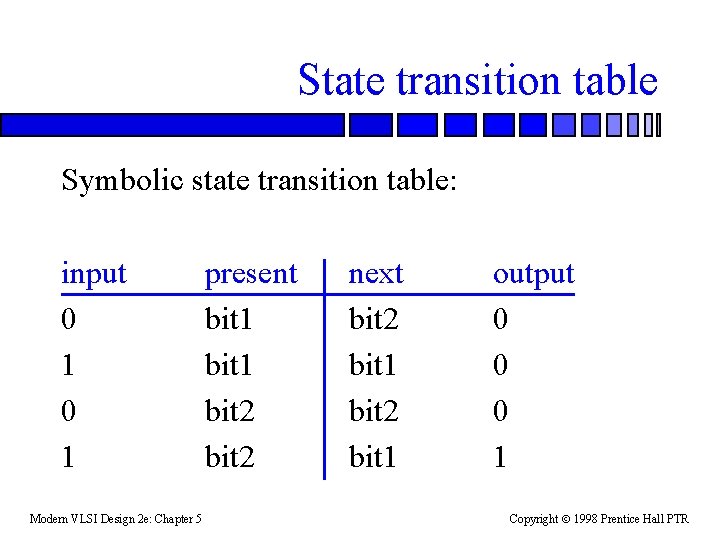

State transition table Symbolic state transition table: input 0 1 Modern VLSI Design 2 e: Chapter 5 present bit 1 bit 2 next bit 2 bit 1 output 0 0 0 1 Copyright 1998 Prentice Hall PTR

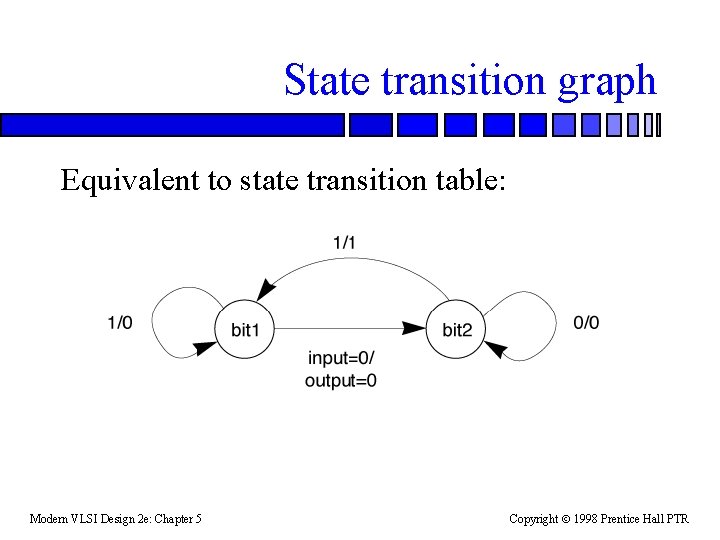

State transition graph Equivalent to state transition table: Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

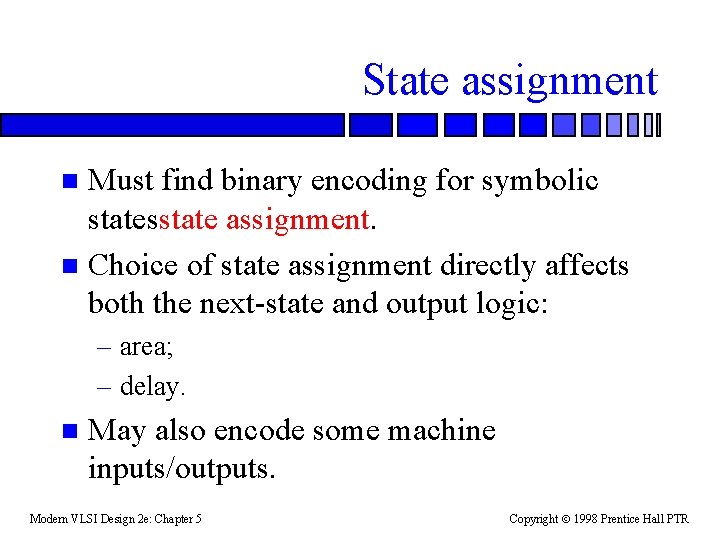

State assignment Must find binary encoding for symbolic statesstate assignment. n Choice of state assignment directly affects both the next-state and output logic: n – area; – delay. n May also encode some machine inputs/outputs. Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

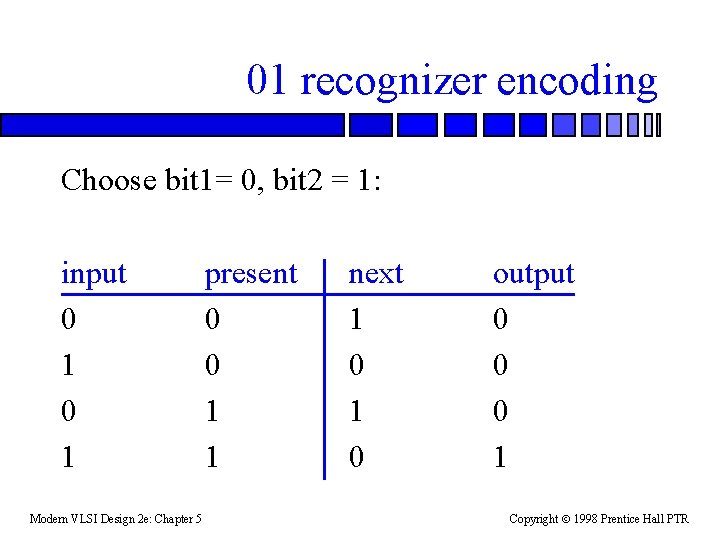

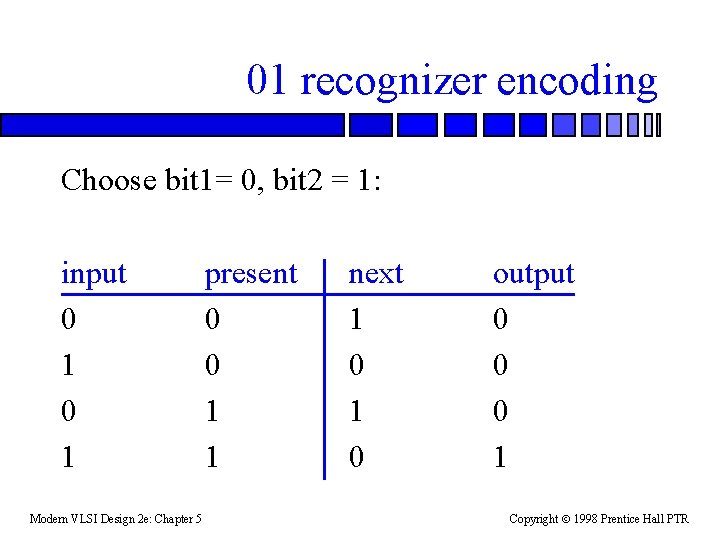

01 recognizer encoding Choose bit 1= 0, bit 2 = 1: input 0 1 Modern VLSI Design 2 e: Chapter 5 present 0 0 1 1 next 1 0 output 0 0 0 1 Copyright 1998 Prentice Hall PTR

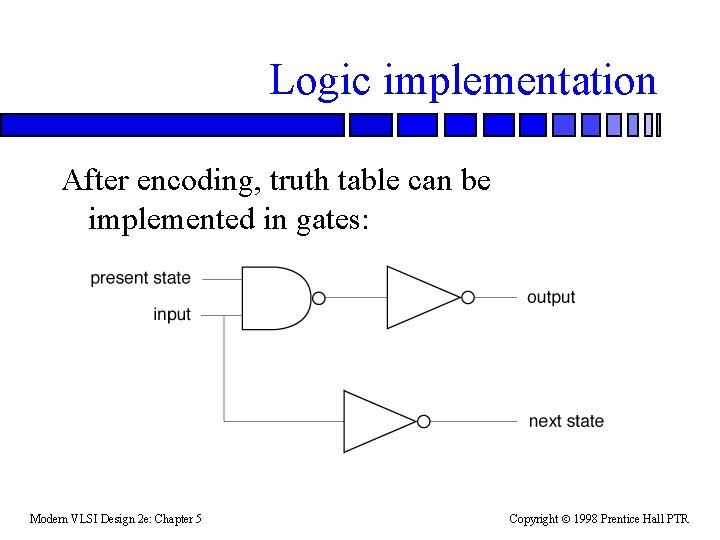

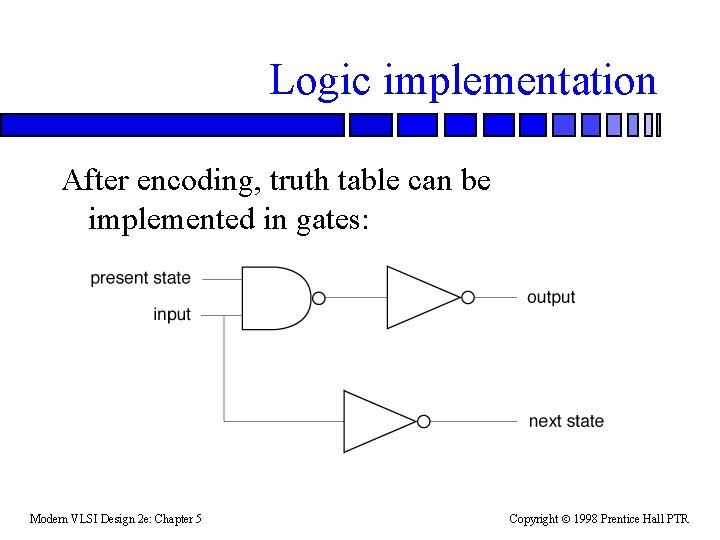

Logic implementation After encoding, truth table can be implemented in gates: Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

Traffic light controller n Intersection of two roads: – highway (busy); – farm (not busy). Want to give green light to highway as much as possible. n Want to give green to farm when needed. n Must always have at least one red light. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

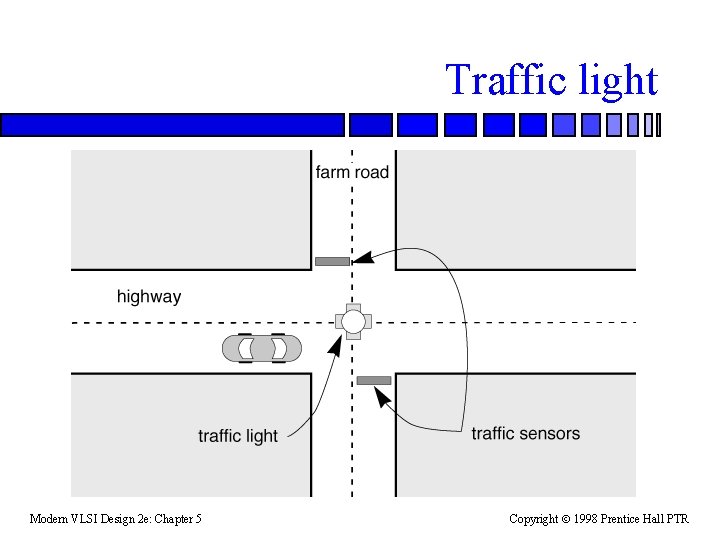

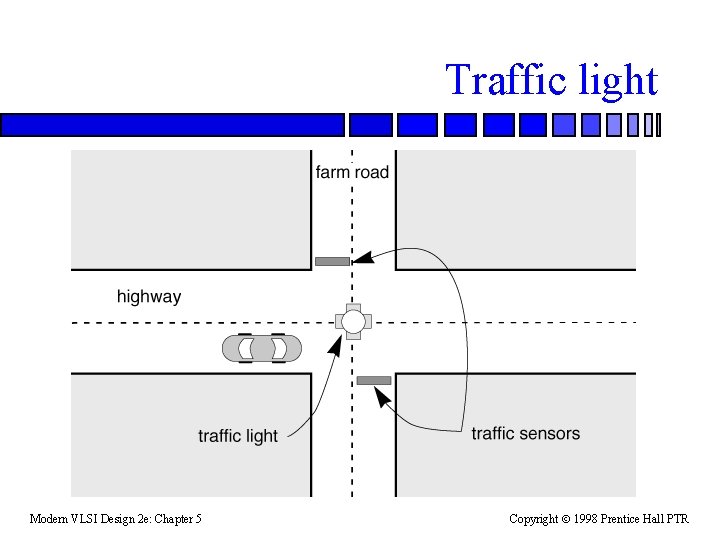

Traffic light Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

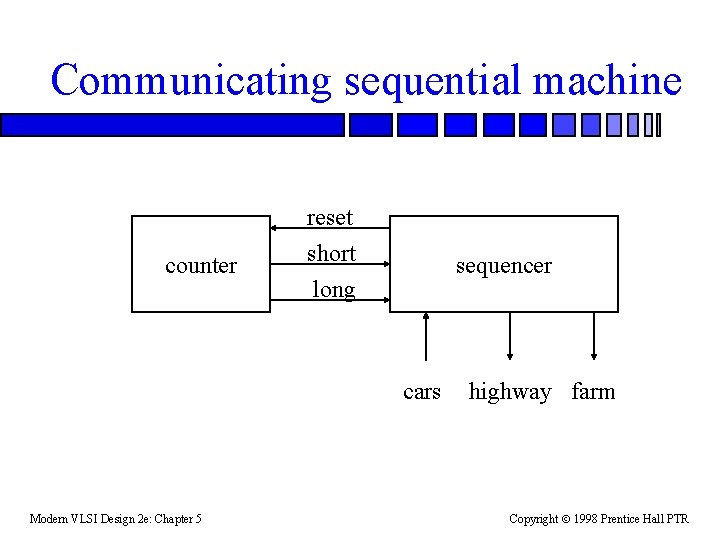

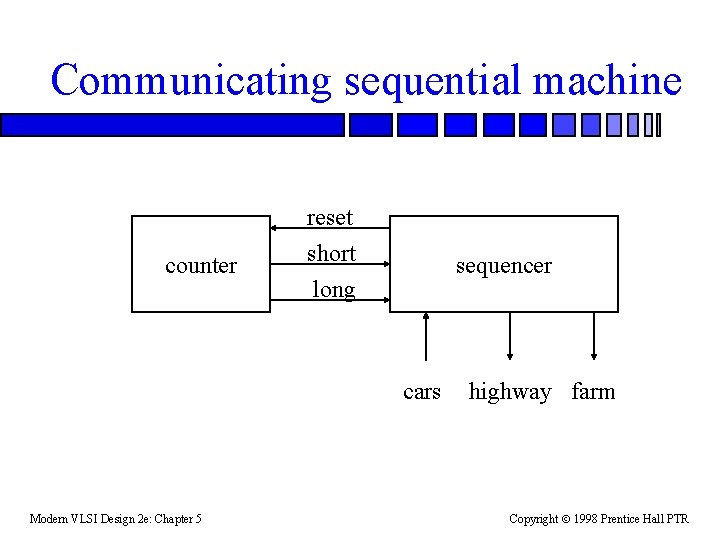

Communicating sequential machine counter reset short long sequencer cars Modern VLSI Design 2 e: Chapter 5 highway farm Copyright 1998 Prentice Hall PTR

System operation Sensor on farm road indicates when cars on farm road are waiting for green light. n Must obey required lengths for green, yellow lights. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

Traffic light machine n Build controller out of two machines: – sequencer which sets colors of lights, etc. – timer which is used to control durations of lights. Separate counter isolates logical design from clock period. n Separate counter greatly reduces number of states in sequencer. n Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR

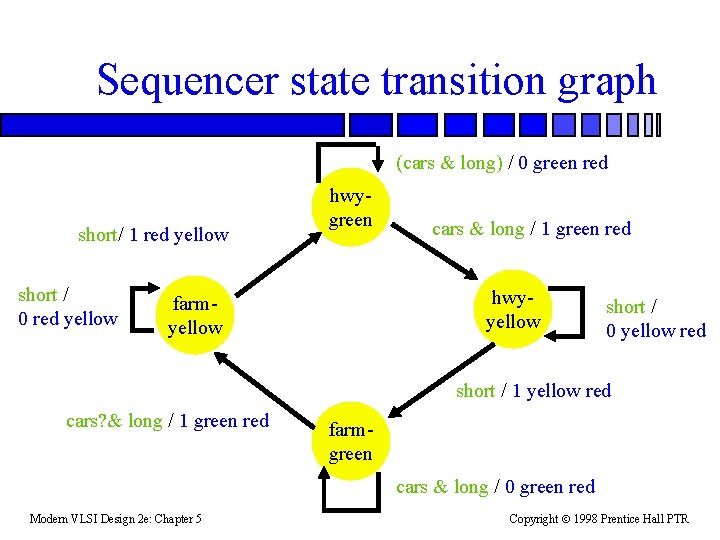

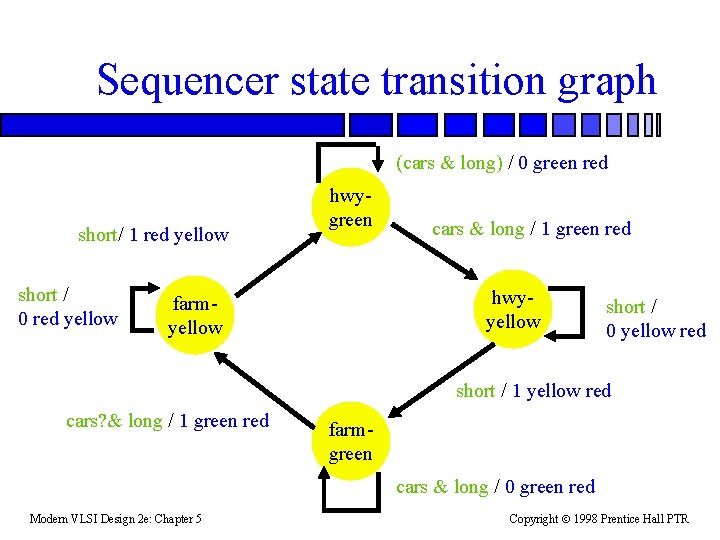

Sequencer state transition graph (cars & long) / 0 green red short/ 1 red yellow short / 0 red yellow hwygreen cars & long / 1 green red hwyyellow farmyellow short / 0 yellow red short / 1 yellow red cars? & long / 1 green red farmgreen cars & long / 0 green red Modern VLSI Design 2 e: Chapter 5 Copyright 1998 Prentice Hall PTR