Topics n HDL coding for synthesis Verilog VHDL

![Verilog structural descriptions n Build a structure by wiring together components: input [7: 0] Verilog structural descriptions n Build a structure by wiring together components: input [7: 0]](https://slidetodoc.com/presentation_image/bfb47e904506da5b2b277515adf7ac44/image-6.jpg)

![Fun with CAD tools n Array renaming between tools: – <0> – [0] – Fun with CAD tools n Array renaming between tools: – <0> – [0] –](https://slidetodoc.com/presentation_image/bfb47e904506da5b2b277515adf7ac44/image-22.jpg)

- Slides: 22

Topics n HDL coding for synthesis. – Verilog. – VHDL. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

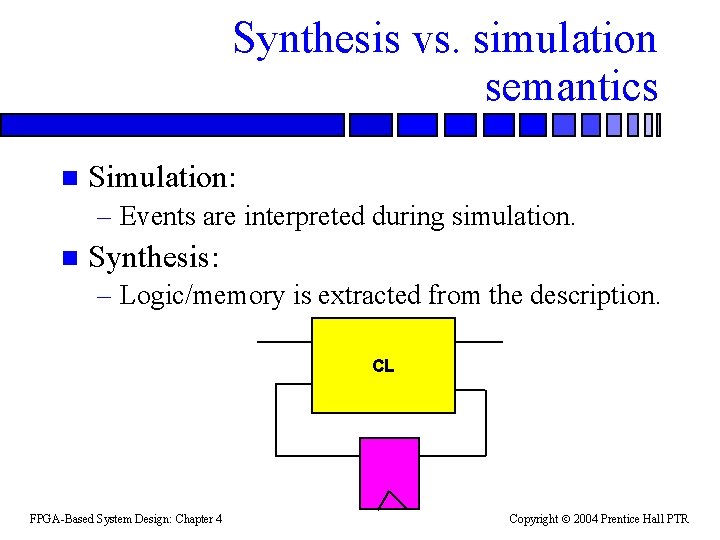

Synthesis vs. simulation semantics n Simulation: – Events are interpreted during simulation. n Synthesis: – Logic/memory is extracted from the description. CL FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

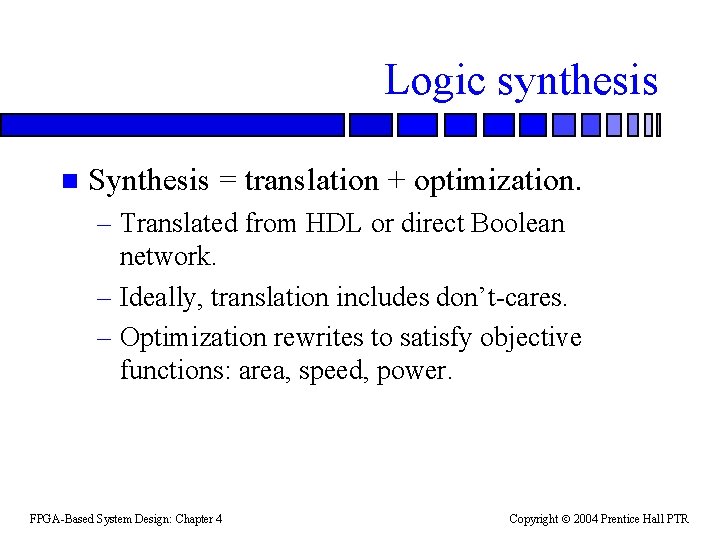

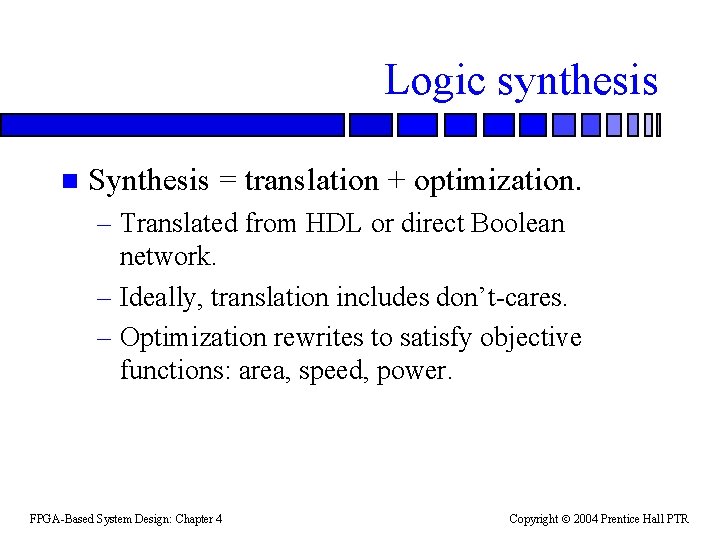

Logic synthesis n Synthesis = translation + optimization. – Translated from HDL or direct Boolean network. – Ideally, translation includes don’t-cares. – Optimization rewrites to satisfy objective functions: area, speed, power. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

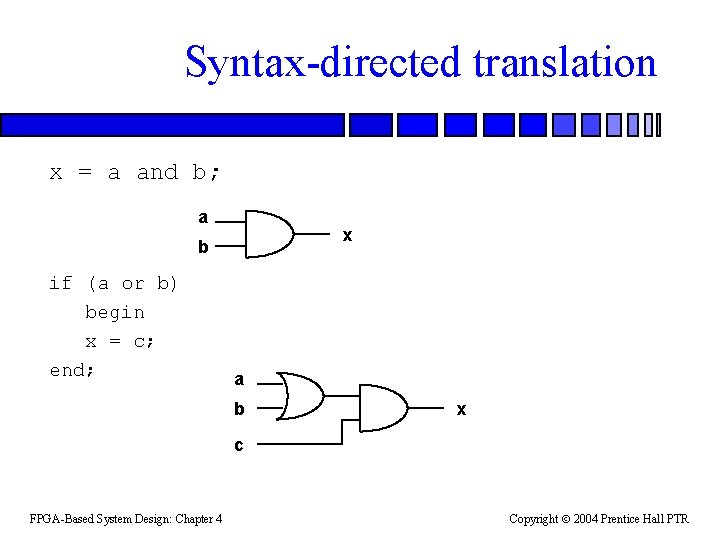

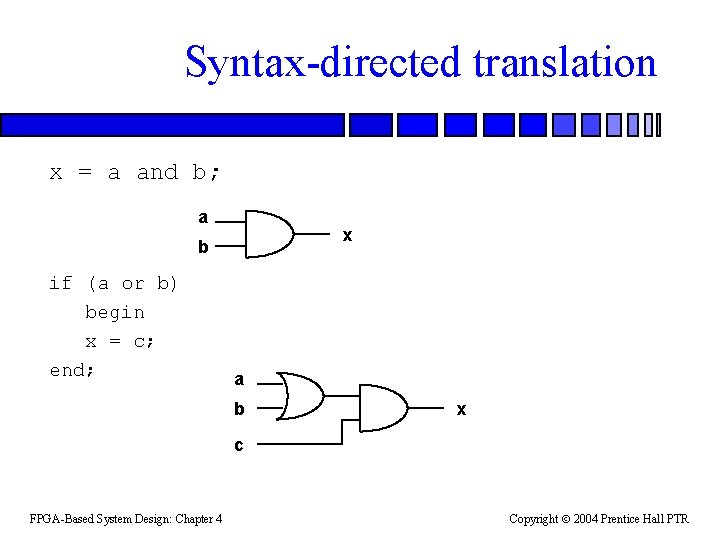

Syntax-directed translation x = a and b; a x b if (a or b) begin x = c; end; a b x c FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Verilog simulation and synthesis n Signal assignments must use the assign keyword: – assign sig 3 = sig 1 & sig 2; FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

![Verilog structural descriptions n Build a structure by wiring together components input 7 0 Verilog structural descriptions n Build a structure by wiring together components: input [7: 0]](https://slidetodoc.com/presentation_image/bfb47e904506da5b2b277515adf7ac44/image-6.jpg)

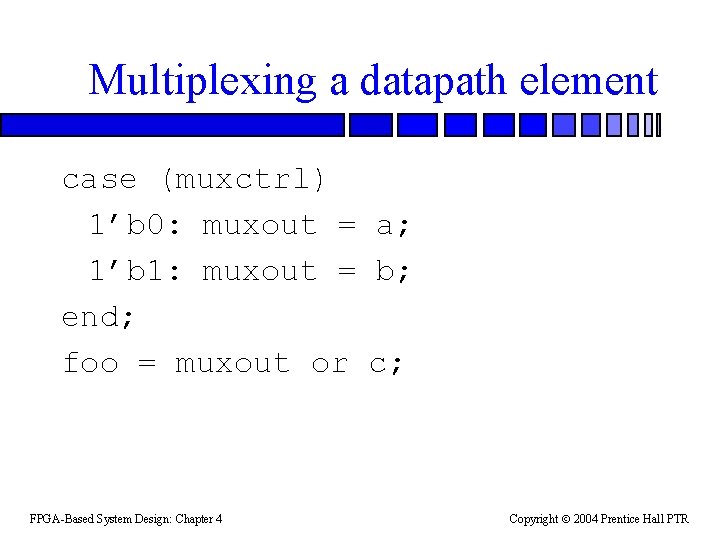

Verilog structural descriptions n Build a structure by wiring together components: input [7: 0] a, b; input carryin; output [7: 0] sum; output carryout; wire [7: 1] carry; fulladd a 0(a[0], b[0], carryin, sum[0], carry[1]); fulladd a 1(a[1], b[1], carry[1], sum[1], carry[2]); fulladd a 2(a[2], b[2], carry[2], sum[2], carry[3]); Type name FPGA-Based System Design: Chapter 4 Instance name Copyright 2004 Prentice Hall PTR

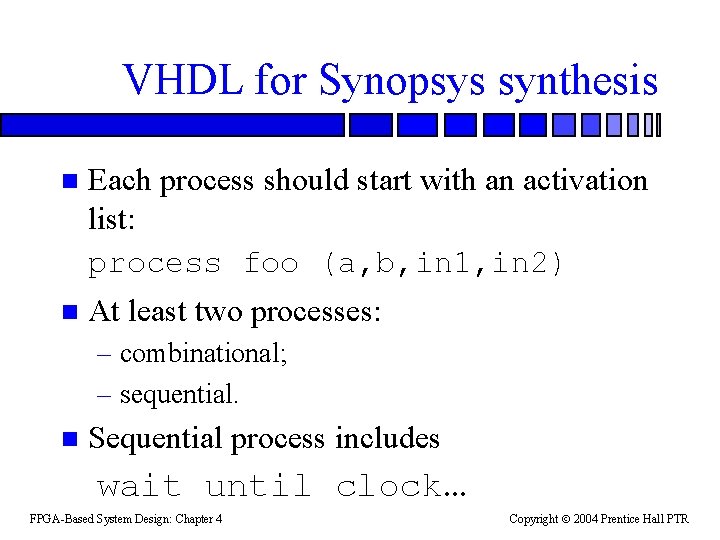

VHDL for Synopsys synthesis n Each process should start with an activation list: process foo (a, b, in 1, in 2) n At least two processes: – combinational; – sequential. n Sequential process includes wait until clock… FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Initializing variables All variables used must be initialized. Uninitialized variables cause latches to be introduced: BAD. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

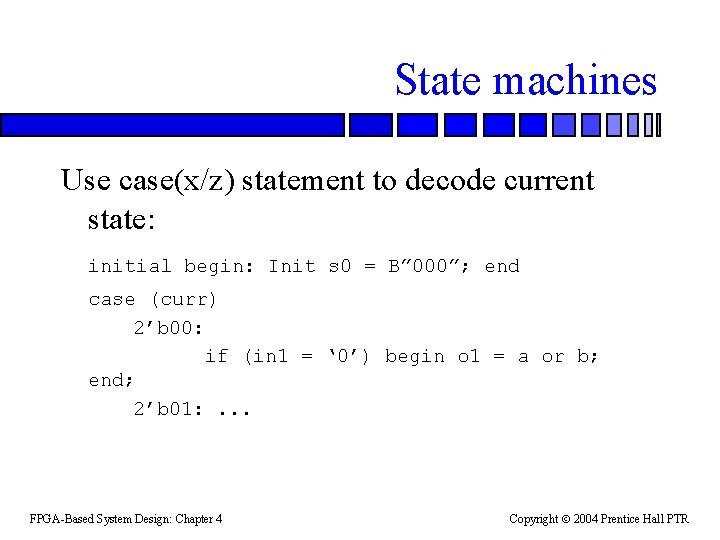

State machines Use case(x/z) statement to decode current state: initial begin: Init s 0 = B” 000”; end case (curr) 2’b 00: if (in 1 = ‘ 0’) begin o 1 = a or b; end; 2’b 01: . . . FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

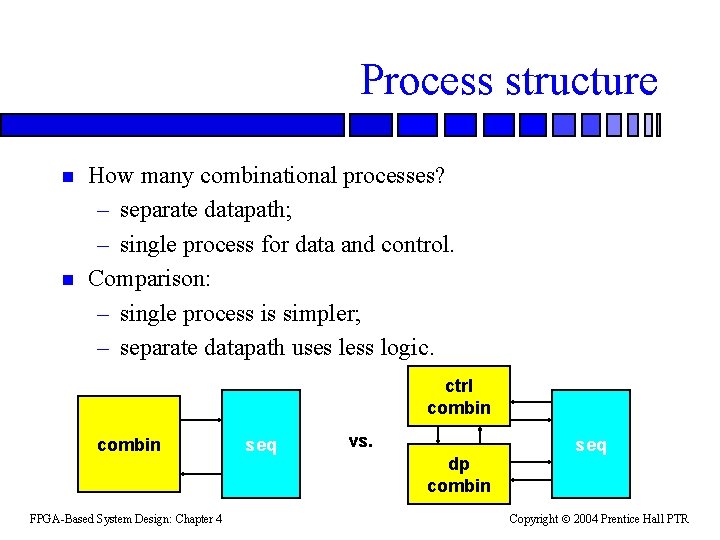

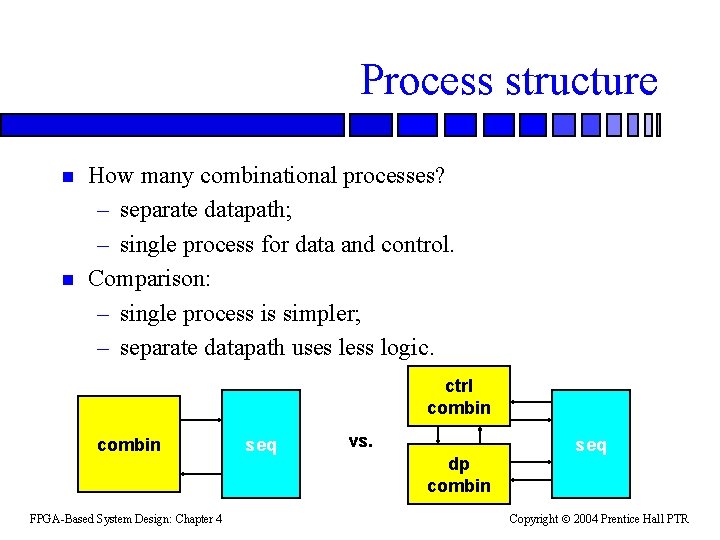

Process structure n n How many combinational processes? – separate datapath; – single process for data and control. Comparison: – single process is simpler; – separate datapath uses less logic. ctrl combin FPGA-Based System Design: Chapter 4 seq vs. dp combin seq Copyright 2004 Prentice Hall PTR

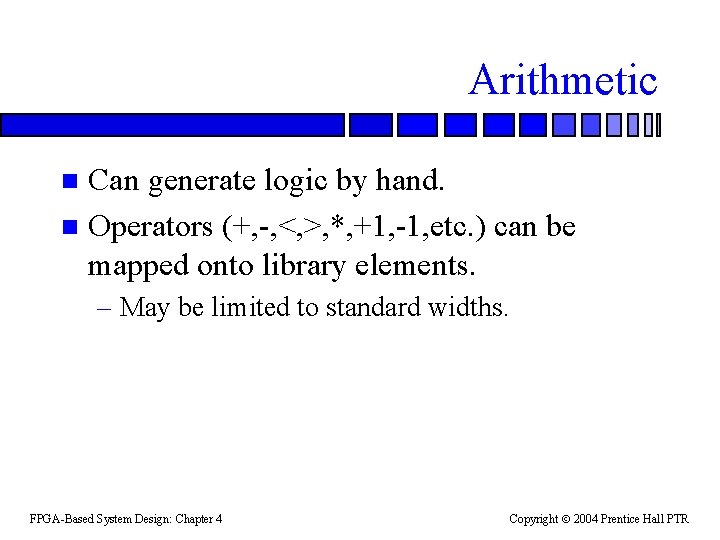

Multiplexing a datapath element case (muxctrl) 1’b 0: muxout = a; 1’b 1: muxout = b; end; foo = muxout or c; FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Arithmetic Can generate logic by hand. n Operators (+, -, <, >, *, +1, -1, etc. ) can be mapped onto library elements. n – May be limited to standard widths. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

General synthesis hints Check out all warnings carefully. n An early synthesis run keeps you from debugging a simulation that won’t synthesize. n FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

The synthesis process n Synthesis is driven by a script: compile -map_effort med report_fpga > TOP + “. fpga” n Script may be customized for the design. – Verilog file foo. v, script file foo. script. – Typically start with a standard script. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Timing constraints n Clock period. – Duty cycle, etc. n Group path timing. – Cells or ports that share the same timing behavior. n Input/output delay. – End-to-end delay. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Hierarchical design and logic optimization Boolean network model does not reach across component boundaries. n Tools generally won’t automatically flatten logic. n – Size may blow up. n You may direct the tool to flatten a group of components. – Heuristic flattening algorithms may be used. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Instantiating memory n Use a memory model: – primitive memories based on LUT; – larger memories synthesized from multiple logic elements. n Synthesis can’t handle a memory described behaviorally. – Can handle behavioral ROM. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

I/O configuraiton Synthesis can automatically determine the types of many I/O blocks, configure appropriately. n Some things that need to be specified: n – indirect three-state activity; – I/O pin location; – registered bidirectional I/O. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Timing model n Synthesis system reads a wire load model from a technology library. – Model depends on part, speed grade. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Attribute passing n FPGA Compiler allows attributes to be passed to EDIF: – BUFG X(. I(a), . O(b)); // synopsys attribute LOC BR FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

Results and reports n Save design as: – database; – EDIF. n Types of reports: – Default synthesis report. – Configuration report. » Describes LEs, IOBs, etc. – Timing report. FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR

![Fun with CAD tools n Array renaming between tools 0 0 Fun with CAD tools n Array renaming between tools: – <0> – [0] –](https://slidetodoc.com/presentation_image/bfb47e904506da5b2b277515adf7ac44/image-22.jpg)

Fun with CAD tools n Array renaming between tools: – <0> – [0] – _0_ FPGA-Based System Design: Chapter 4 Copyright 2004 Prentice Hall PTR