Topics Combinational network delay n Logic optimization n

Topics Combinational network delay. n Logic optimization. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Sources of delay n Gate delay: – drive; – load. n Wire: – lumped load; – transmission line. Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

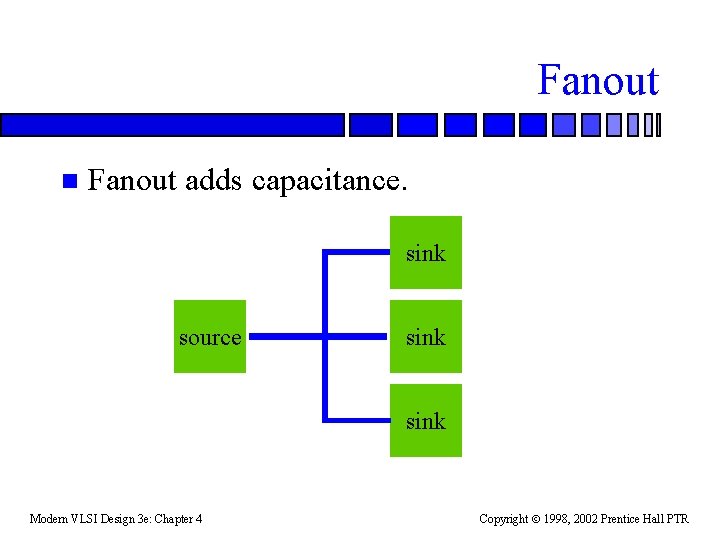

Fanout n Fanout adds capacitance. sink source sink Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

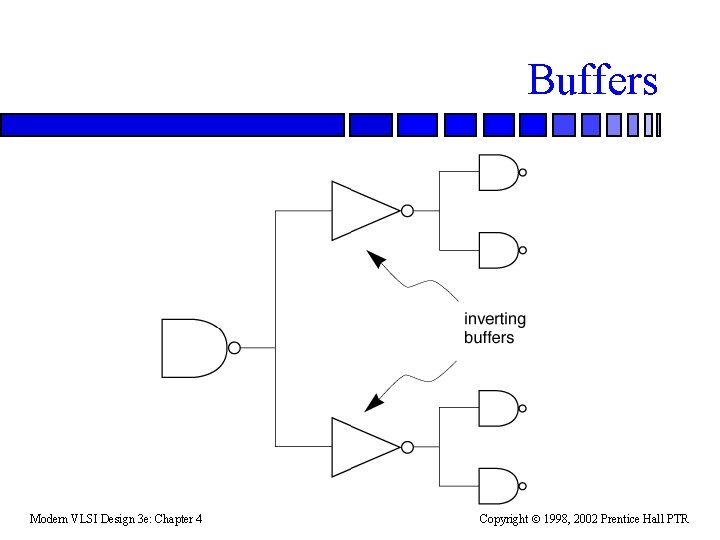

Ways to drive large fanout Increase sizes of driver transistors. Must take into account rules for driving large loads. n Add intermediate buffers. This may require/allow restructuring of the logic. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Buffers Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Wire capacitance Use layers with lower capacitance. n Redesign layout to reduce length of wires with excessive delay. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

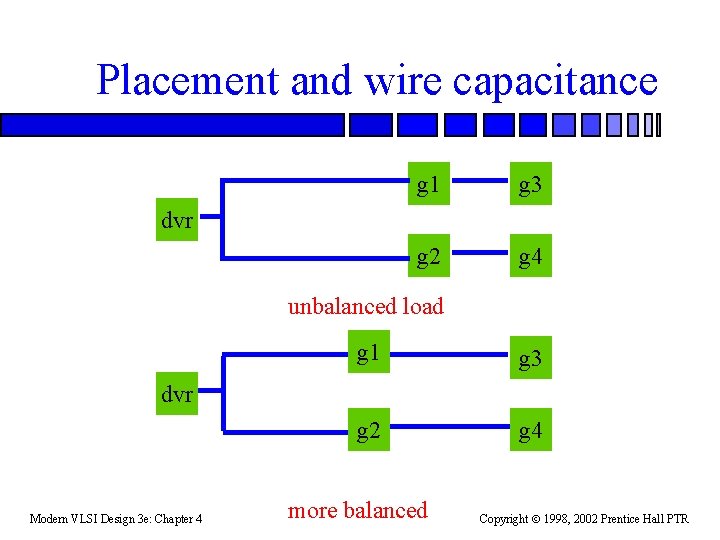

Placement and wire capacitance g 1 g 3 g 2 g 4 dvr unbalanced load g 1 g 3 g 2 g 4 dvr Modern VLSI Design 3 e: Chapter 4 more balanced Copyright 1998, 2002 Prentice Hall PTR

Path delay Combinational network delay is measured over paths through network. n Can trace a causality chain from inputs to worst-case output. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

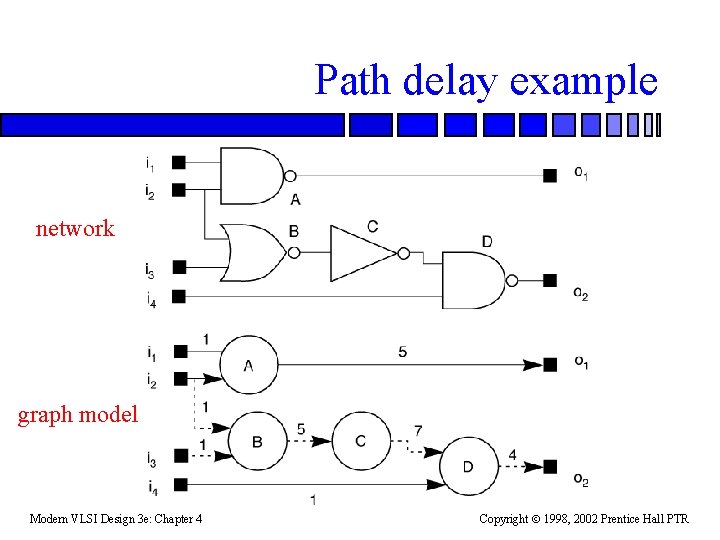

Path delay example network graph model Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Critical path = path which creates longest delay. n Can trace transitions which cause delays that are elements of the critical delay path. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Delay model Nodes represent gates. n Assign delays to edges—signal may have different delay to different sinks. n Lump gate and wire delay into a single value. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

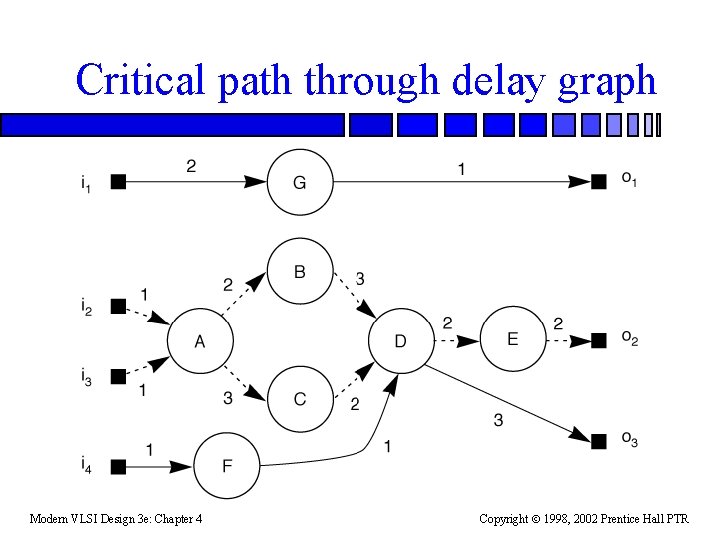

Critical path through delay graph Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Reducing critical path length To reduce circuit delay, must speed up the critical path—reducing delay off the path doesn’t help. n There may be more than one path of the same delay. Must speed up all equivalent paths to speed up circuit. n Must speed up cut-set through critical path. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

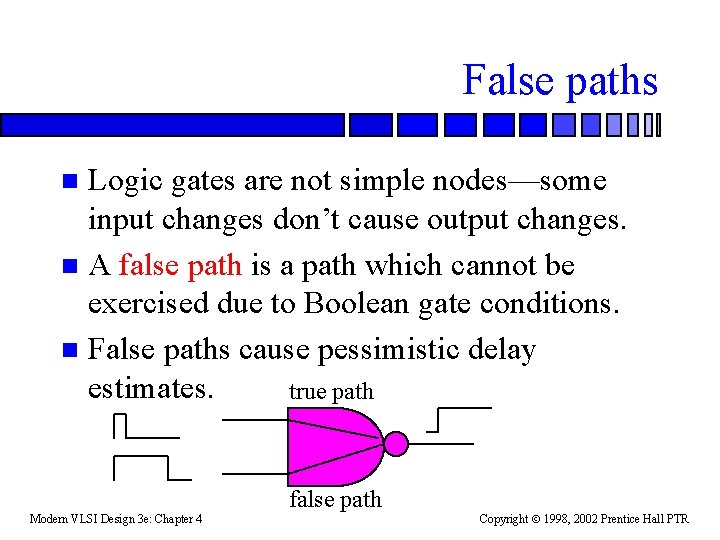

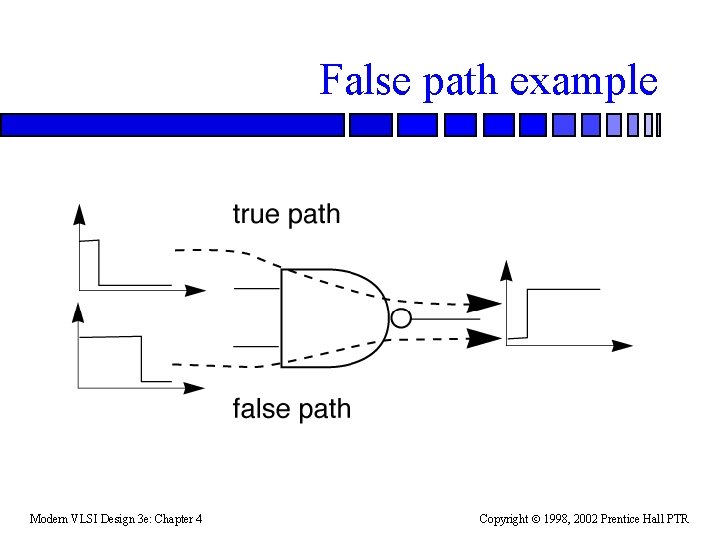

False paths Logic gates are not simple nodes—some input changes don’t cause output changes. n A false path is a path which cannot be exercised due to Boolean gate conditions. n False paths cause pessimistic delay estimates. true path n false path Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

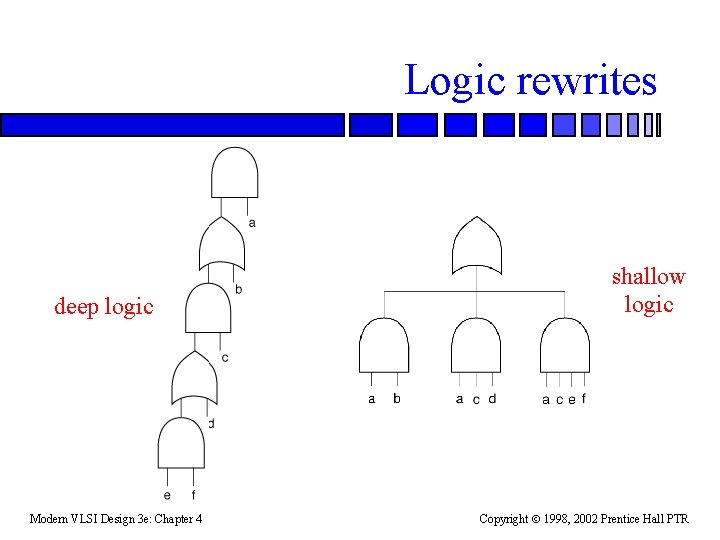

Logic rewrites deep logic Modern VLSI Design 3 e: Chapter 4 shallow logic Copyright 1998, 2002 Prentice Hall PTR

Logic transformations Can rewrite by using subexpressions. n Flattening logic increases gate fan-in. n Logic rewrites may affect gate placement. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

False path example Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Logic optimization Logic synthesis programs transform Boolean expressions into logic gate networks in a particular library. n Optimization goals: minimize area, meet delay constraint. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Technology-independent optimizations Works on Boolean expression equivalence. n Estimates size based on number of literals. n Uses factorization, re-substitution, minimization, etc. to optimize logic. n Technology-independent phase uses simple delay models. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

Technology-dependent optimizations Maps Boolean expressions into a particular cell library. n Mapping may take into account area, delay. n May perform some optimizations in addition to simple mapping. n Allows more accurate delay models. n Modern VLSI Design 3 e: Chapter 4 Copyright 1998, 2002 Prentice Hall PTR

- Slides: 20