Topics Basics of sequential machines n Sequential machine

Topics Basics of sequential machines. n Sequential machine specification. n Sequential machine design processes. n FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Sequential machines Use registers to make primary output values depend on state + primary inputs. n Varieties: n – Mealy—outputs function of present state, inputs; – Moore—outputs depend only on state. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

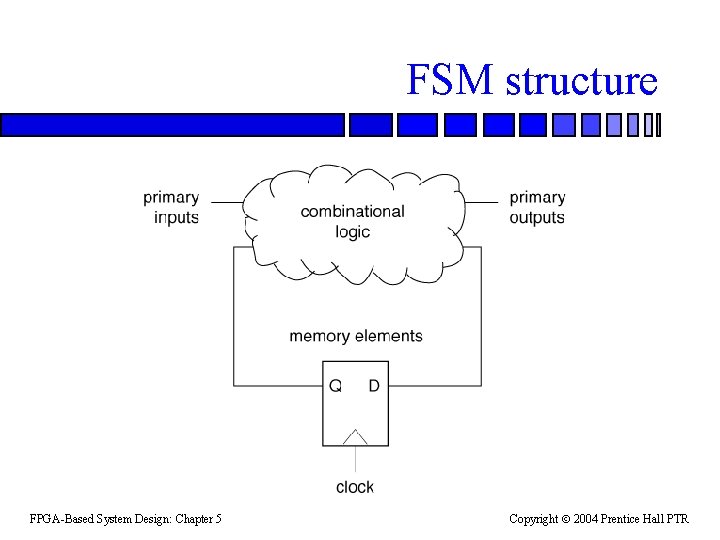

FSM structure FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Constraints on structure No combinational cycles. n All components must have bounded delay. n FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Synchronous design n Controlled by clock(s). – State changes at time determined by the clock. – Inputs to registers settle in time for state change. – Primary inputs settle in time for combinational delay through logic. n Machine state is determined solely by registers. – Don’t have to worry about timing constraints, events outside the registers. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Non-functional requirements and optimization n Performance: – Clock period is determined by combinational logic delay. n Area: – Combinational logic size usually dominates area. n Energy/power: – Often dominated by combinational logic. – May be improved by latching values. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Models of state machines n Register-transfer: – Combinational equations for inputs to registers. n State transition graph/table: – Next-state, output functions described piecewise. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

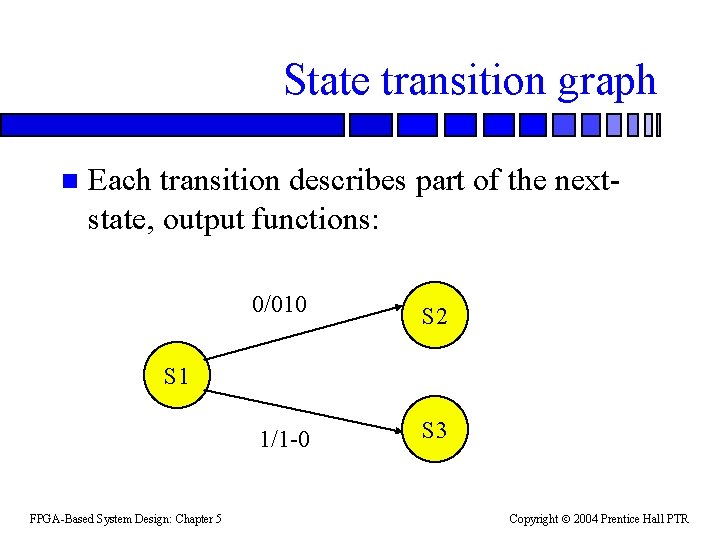

State transition graph n Each transition describes part of the nextstate, output functions: 0/010 S 2 1/1 -0 S 3 S 1 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

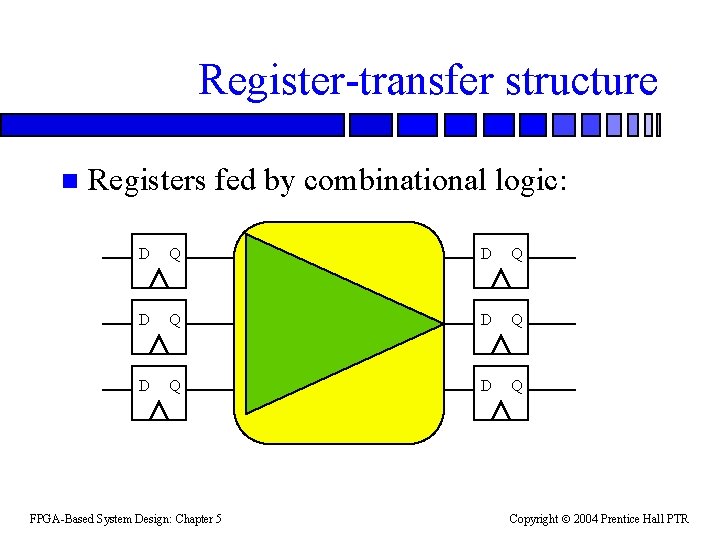

Register-transfer structure n Registers fed by combinational logic: D Q D Q FPGA-Based System Design: Chapter 5 Combinational logic D Q D Q Copyright 2004 Prentice Hall PTR

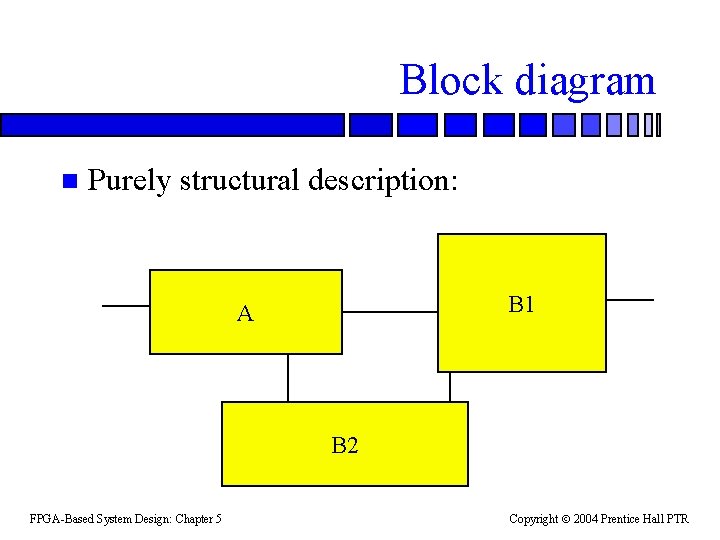

Block diagram n Purely structural description: B 1 A B 2 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Symbolic values n A sequential machine description may use symbolic, not binary values. – Symbolic values must be encoded during implementation. n Encoding may optimize implementation characteristics: – Area. – Performance. – Energy. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

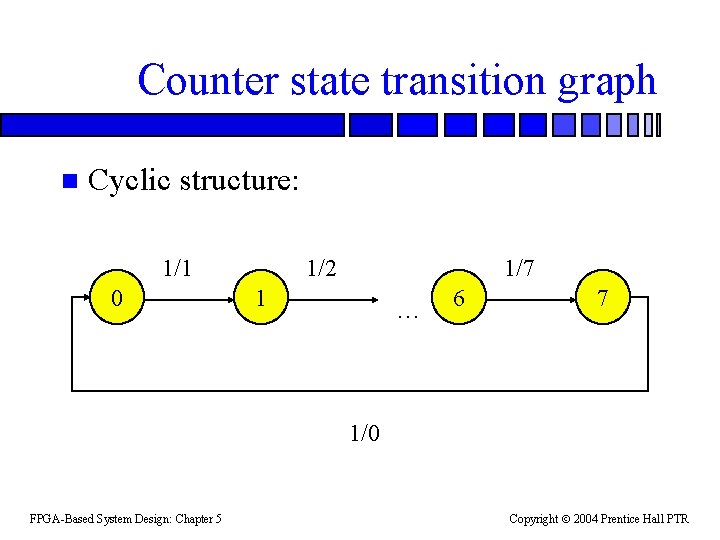

STG vs. register-transfer Each representation is easier for some types of machines. n Example: counter. n FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Counter state transition graph n Cyclic structure: 1/1 0 1/2 1/7 1 … 6 7 1/0 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Counter register-transfer function n Specify using addition: – Next_count = count + 1. n Regular structure of logic. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

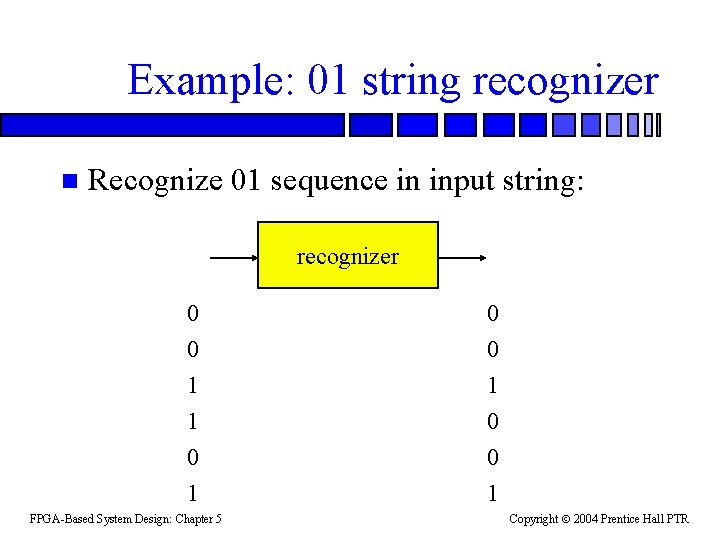

Example: 01 string recognizer n Recognize 01 sequence in input string: recognizer 0 0 1 1 0 1 FPGA-Based System Design: Chapter 5 0 0 1 Copyright 2004 Prentice Hall PTR

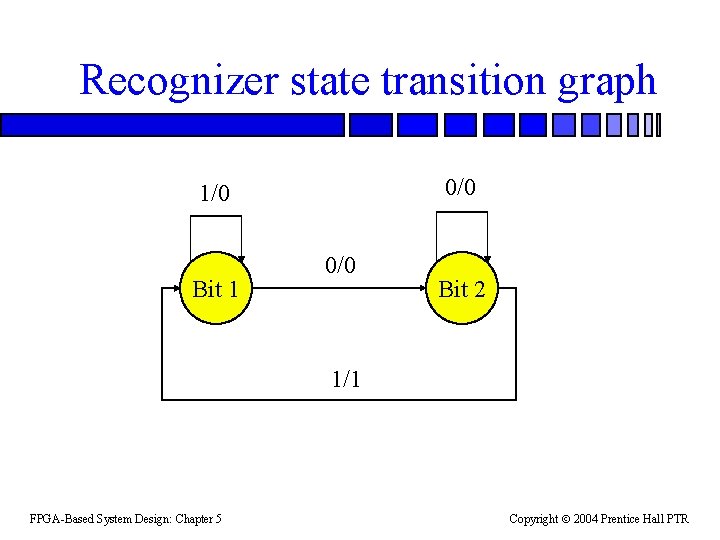

Recognizer state transition graph 0/0 1/0 Bit 1 0/0 Bit 2 1/1 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Mealy vs. Moore machine n Moore machine: – Output a function of state. n Mealy machine: – Output a function of primary inputs + state. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Sequential machine definition Machine computes next state N, primary outputs O from current state S, primary inputs I. n Next-state function: n – N = (I, S). n Output function (Mealy): – O = (I, S). FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

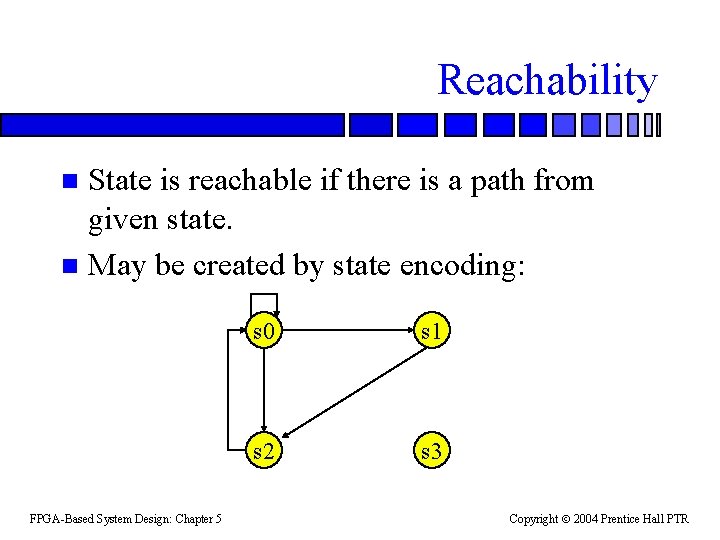

Reachability State is reachable if there is a path from given state. n May be created by state encoding: n FPGA-Based System Design: Chapter 5 s 0 s 1 s 2 s 3 Copyright 2004 Prentice Hall PTR

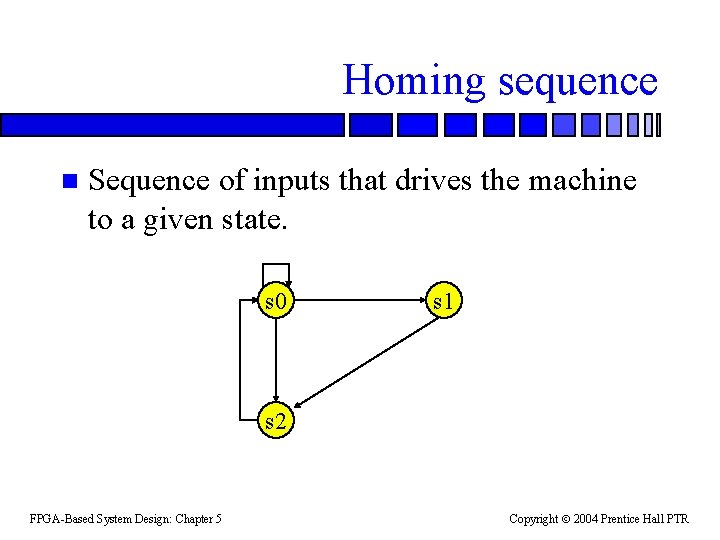

Homing sequence n Sequence of inputs that drives the machine to a given state. s 0 s 1 s 2 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

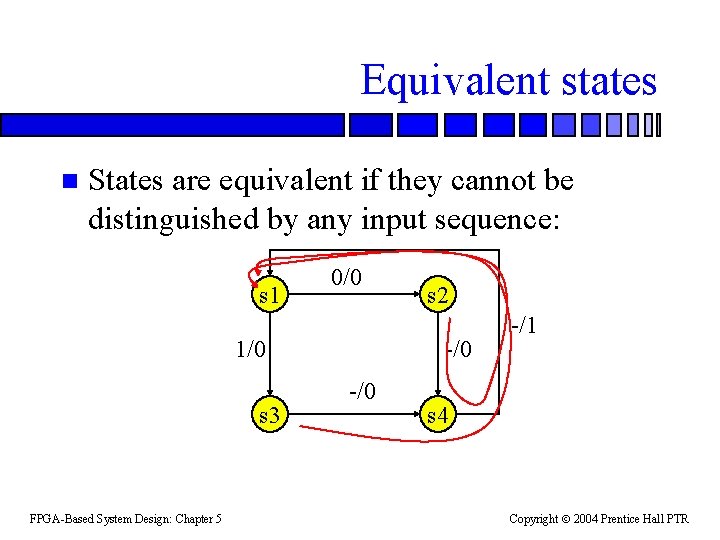

Equivalent states n States are equivalent if they cannot be distinguished by any input sequence: s 1 0/0 1/0 s 3 FPGA-Based System Design: Chapter 5 s 2 -/0 -/1 s 4 Copyright 2004 Prentice Hall PTR

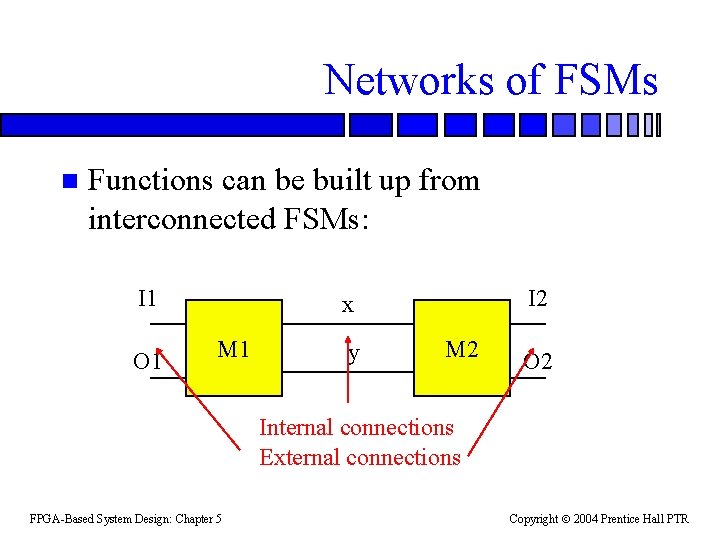

Networks of FSMs n Functions can be built up from interconnected FSMs: I 1 O 1 I 2 x M 1 y M 2 O 2 Internal connections External connections FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

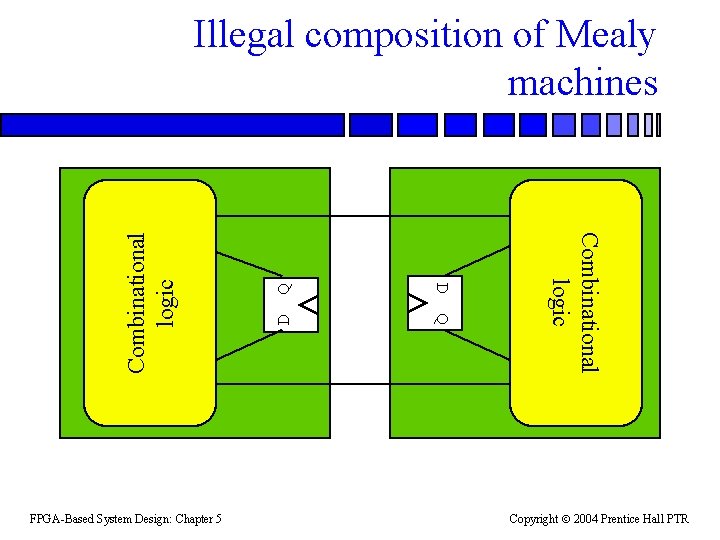

Q D Combinational logic Q FPGA-Based System Design: Chapter 5 D Combinational logic Illegal composition of Mealy machines Copyright 2004 Prentice Hall PTR

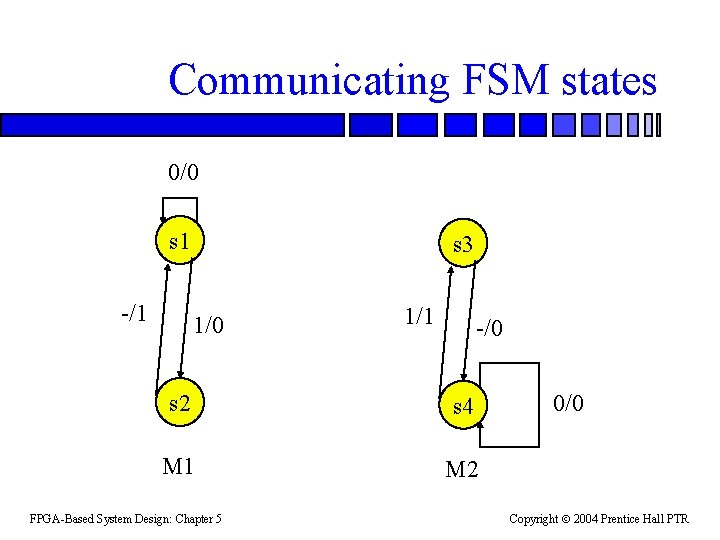

Communicating FSM states 0/0 s 1 -/1 s 3 1/0 1/1 -/0 s 2 s 4 M 1 M 2 FPGA-Based System Design: Chapter 5 0/0 Copyright 2004 Prentice Hall PTR

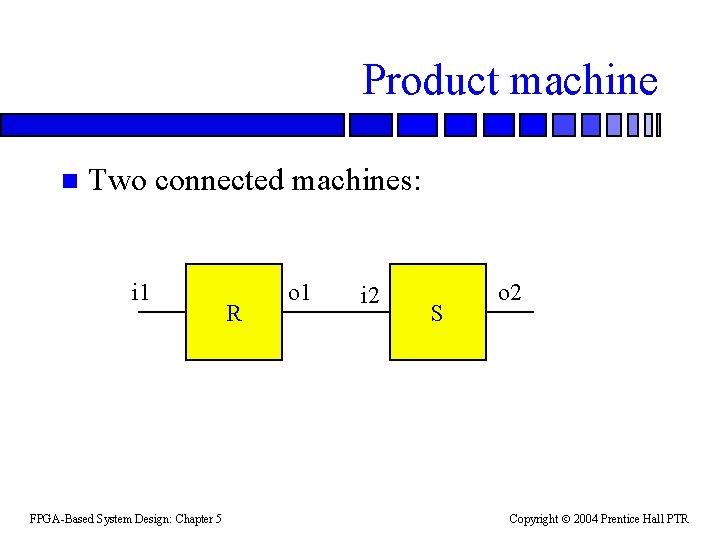

Product machine n Two connected machines: i 1 FPGA-Based System Design: Chapter 5 R o 1 i 2 S o 2 Copyright 2004 Prentice Hall PTR

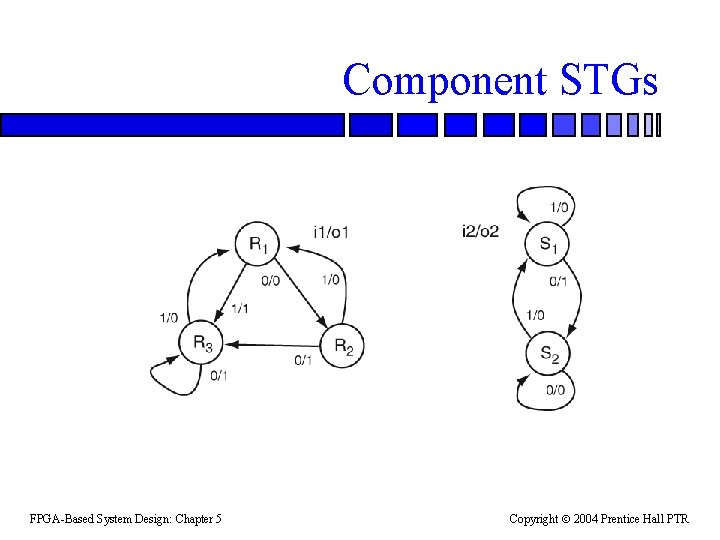

Component STGs FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

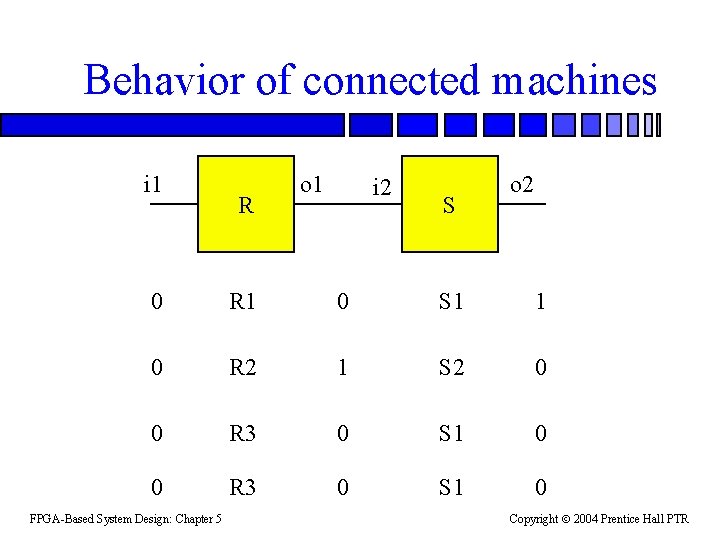

Behavior of connected machines i 1 R o 1 i 2 S o 2 0 R 1 0 S 1 1 0 R 2 1 S 2 0 0 R 3 0 S 1 0 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

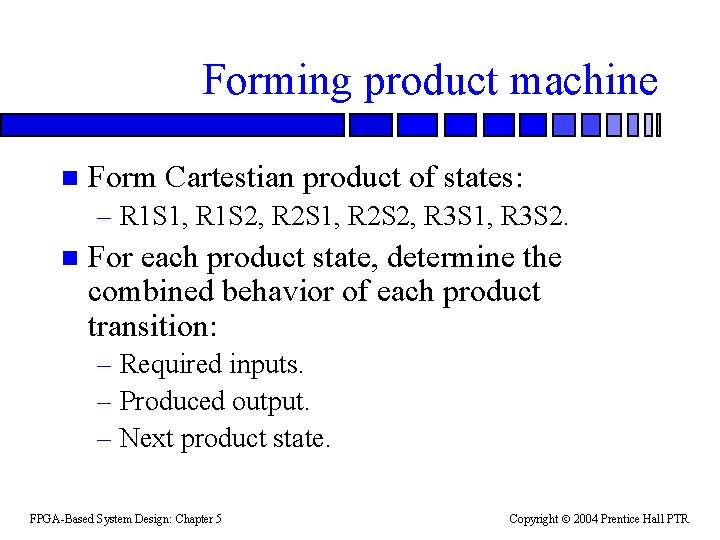

Forming product machine n Form Cartestian product of states: – R 1 S 1, R 1 S 2, R 2 S 1, R 2 S 2, R 3 S 1, R 3 S 2. n For each product state, determine the combined behavior of each product transition: – Required inputs. – Produced output. – Next product state. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

State assignment n Find a binary code for symbolic values in machine. – Optimize area, performance. – May be done on inputs, outputs as well. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Optimizing state assignments n Codes affect the next-state, output logic. – Compute conditions based on state. n Best code depends on the input, output logic and its interaction with state computations. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

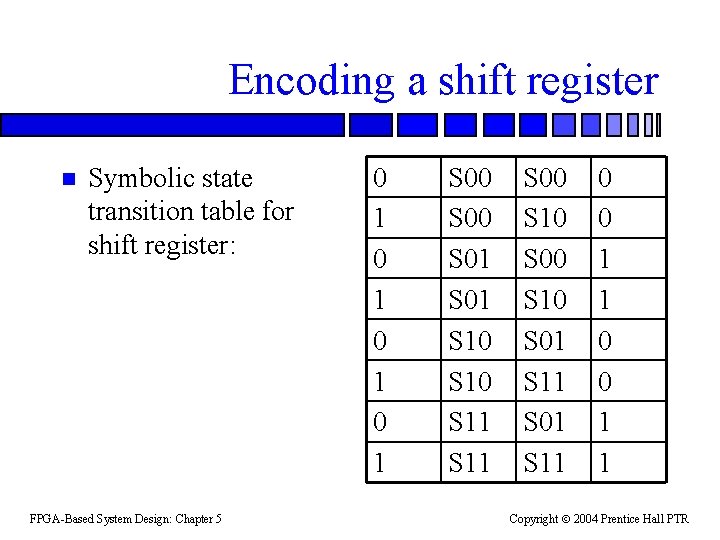

Encoding a shift register n Symbolic state transition table for shift register: FPGA-Based System Design: Chapter 5 0 1 0 1 S 00 S 01 S 10 S 11 S 00 S 10 S 01 S 11 0 0 1 1 Copyright 2004 Prentice Hall PTR

Bad encoding Let S 00 = 00, S 01 = 01, S 10 = 10, S 11 = 10. n Logic: n – Output = S 1 S 0’ + S 1’ S 0 – N 1 = I – N 0 = I S 1’ + I S 1 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Good encoding Let S 00 = 00, S 01 = 01, S 10 = 10, S 11 = 11. n Logic: n – Output = S 0 – N 1 = I – N 0 = S 1 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

One-hot code N-state machine has n-bit encoding. n Ith bit is 1 if machine is in state i. n Comparison: n – Easy to tell what state the machine is in. – Easy to get the machine into an illegal state (0000, 1111, etc. ). – Uses a lot of registers. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

Common factors in state coding n Consider this set of transitions: – 0, s 1 OR s 2 -> s 3, 1 n Want to choose a code that easily produces s 1 OR s 2. – S 1 = 00, S 2 = 01. FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

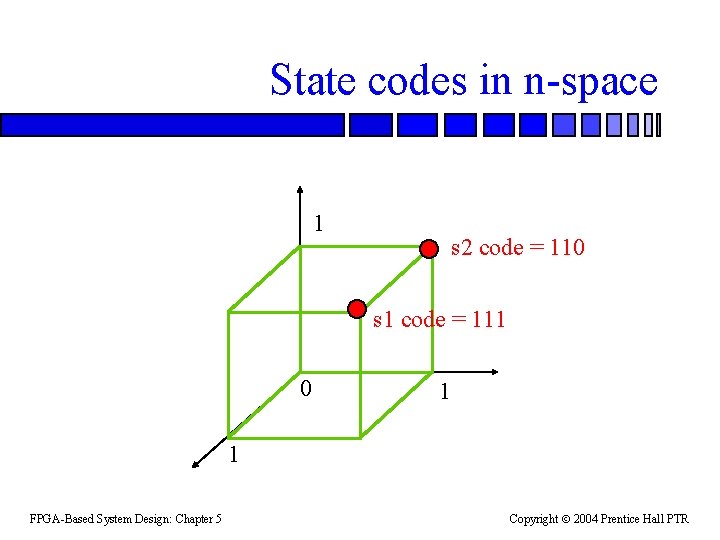

State codes in n-space 1 s 2 code = 110 s 1 code = 111 0 1 1 FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

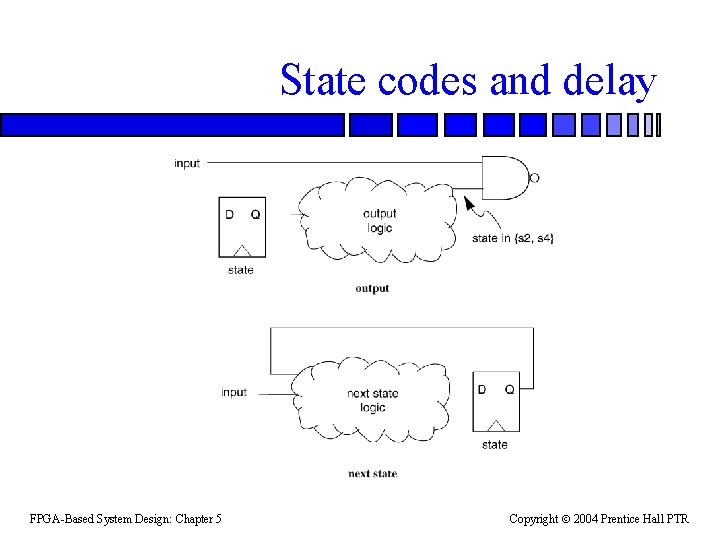

State codes and delay FPGA-Based System Design: Chapter 5 Copyright 2004 Prentice Hall PTR

- Slides: 37