Tomasulo With Reorder buffer Done FP Op Queue

Tomasulo With Reorder buffer: Done? FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer ROB 4 ROB 3 ROB 2 F 0 LD F 0, 10(R 2) Registers Dest ROB 1 To Memory from Memory Dest FP adders N Reservation Stations Dest 1 10+R 2 FP multipliers Oldest

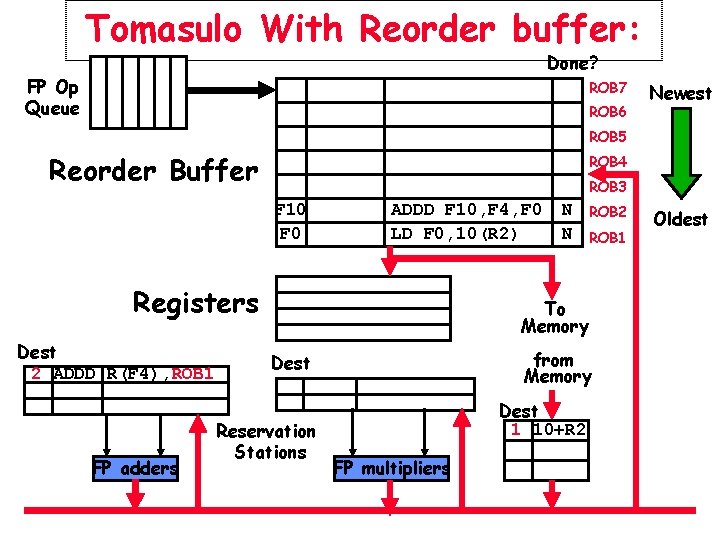

Tomasulo With Reorder buffer: Done? FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer ROB 4 ROB 3 F 10 F 0 ADDD F 10, F 4, F 0 LD F 0, 10(R 2) Registers Dest 2 ADDD R(F 4), ROB 1 FP adders N N ROB 2 ROB 1 To Memory from Memory Dest Reservation Stations Dest 1 10+R 2 FP multipliers Oldest

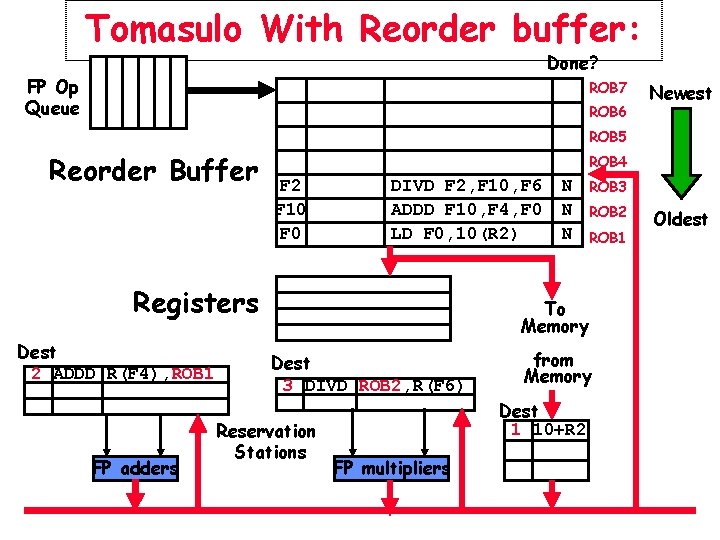

Tomasulo With Reorder buffer: Done? FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer ROB 4 F 2 F 10 F 0 DIVD F 2, F 10, F 6 ADDD F 10, F 4, F 0 LD F 0, 10(R 2) Registers Dest 2 ADDD R(F 4), ROB 1 FP adders N N N ROB 3 ROB 2 ROB 1 To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest 1 10+R 2 FP multipliers Oldest

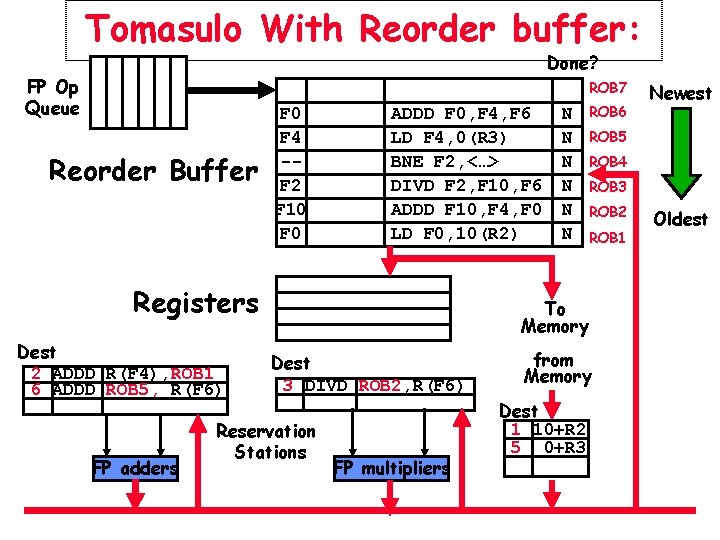

Tomasulo With Reorder buffer: Done? FP Op Queue ROB 7 Reorder Buffer F 0 F 4 -F 2 F 10 F 0 ADDD F 0, F 4, F 6 LD F 4, 0(R 3) BNE F 2, <…> DIVD F 2, F 10, F 6 ADDD F 10, F 4, F 0 LD F 0, 10(R 2) Registers Dest 2 ADDD R(F 4), ROB 1 6 ADDD ROB 5, R(F 6) FP adders N N N ROB 6 ROB 5 ROB 4 ROB 3 ROB 2 ROB 1 To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations FP multipliers from Memory Dest 1 10+R 2 5 0+R 3 Newest Oldest

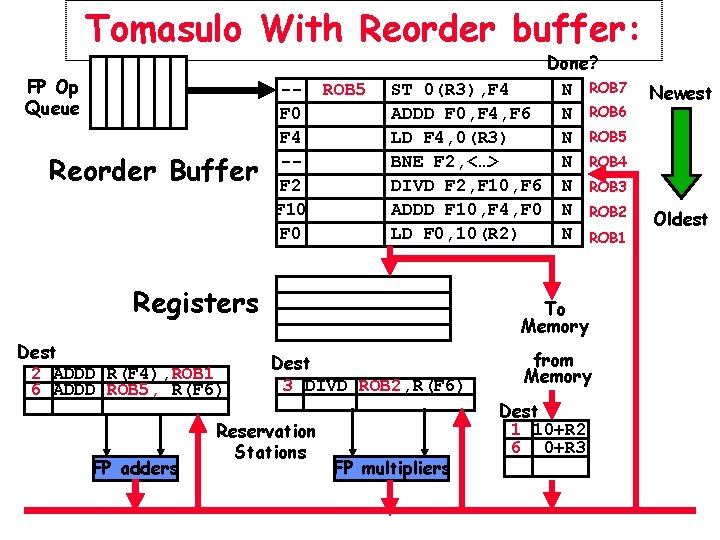

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer -- ROB 5 F 0 F 4 -F 2 F 10 F 0 Done? ST 0(R 3), F 4 N ROB 7 ADDD F 0, F 4, F 6 N ROB 6 LD F 4, 0(R 3) N ROB 5 BNE F 2, <…> N ROB 4 DIVD F 2, F 10, F 6 N ROB 3 ADDD F 10, F 4, F 0 N ROB 2 LD F 0, 10(R 2) N ROB 1 Registers Dest 2 ADDD R(F 4), ROB 1 6 ADDD ROB 5, R(F 6) FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations FP multipliers from Memory Dest 1 10+R 2 6 0+R 3 Newest Oldest

![Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer -- M[10] F 0 F Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer -- M[10] F 0 F](http://slidetodoc.com/presentation_image_h/0a225d364c3b7b6c6400a05236144ffd/image-6.jpg)

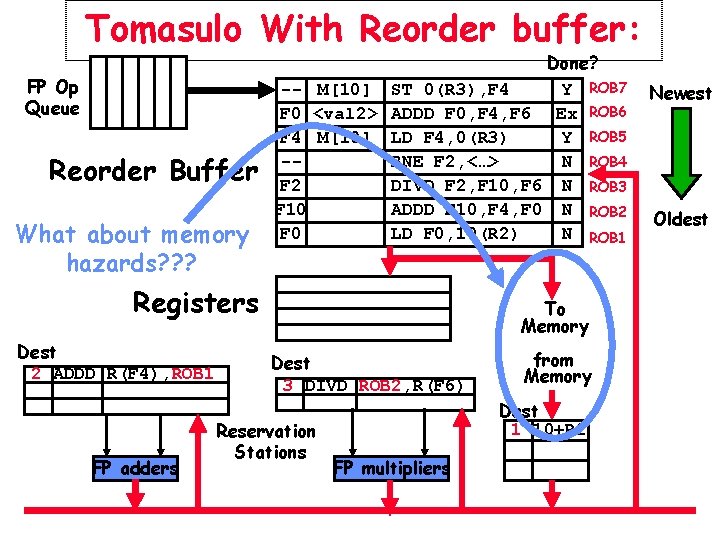

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer -- M[10] F 0 F 4 M[10] -F 2 F 10 F 0 Done? ST 0(R 3), F 4 Y ROB 7 ADDD F 0, F 4, F 6 N ROB 6 LD F 4, 0(R 3) Y ROB 5 BNE F 2, <…> N ROB 4 DIVD F 2, F 10, F 6 N ROB 3 ADDD F 10, F 4, F 0 N ROB 2 LD F 0, 10(R 2) N ROB 1 Registers Dest 2 ADDD R(F 4), ROB 1 6 ADDD M[10], R(F 6) FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest 1 10+R 2 FP multipliers Newest Oldest

![Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer Done? -- M[10] ST 0(R Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer Done? -- M[10] ST 0(R](http://slidetodoc.com/presentation_image_h/0a225d364c3b7b6c6400a05236144ffd/image-7.jpg)

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer Done? -- M[10] ST 0(R 3), F 4 Y ROB 7 F 0 <val 2> ADDD F 0, F 4, F 6 Ex ROB 6 F 4 M[10] LD F 4, 0(R 3) Y ROB 5 -BNE F 2, <…> N ROB 4 F 2 DIVD F 2, F 10, F 6 N ROB 3 F 10 ADDD F 10, F 4, F 0 N ROB 2 F 0 LD F 0, 10(R 2) N ROB 1 Registers Dest 2 ADDD R(F 4), ROB 1 FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest 1 10+R 2 FP multipliers Newest Oldest

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer What about memory hazards? ? ? Done? -- M[10] ST 0(R 3), F 4 Y ROB 7 F 0 <val 2> ADDD F 0, F 4, F 6 Ex ROB 6 F 4 M[10] LD F 4, 0(R 3) Y ROB 5 -BNE F 2, <…> N ROB 4 F 2 DIVD F 2, F 10, F 6 N ROB 3 F 10 ADDD F 10, F 4, F 0 N ROB 2 F 0 LD F 0, 10(R 2) N ROB 1 Registers Dest 2 ADDD R(F 4), ROB 1 FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest 1 10+R 2 FP multipliers Newest Oldest

Memory Disambiguation: Sorting out RAW Hazards in memory • Question: Given a load that follows a store in program order, are the two related? – (Alternatively: is there a RAW hazard between the store and the load)? Eg: st ld 0(R 2), R 5 R 6, 0(R 3) • Can we go ahead and start the load early? – Store address could be delayed for a long time by some calculation that leads to R 2 (divide? ). – We might want to issue/begin execution of both operations in same cycle. – Answer is that we are not allowed to start load until we know that address 0(R 2) 0(R 3)

Hardware Support for Memory Disambiguation • Need buffer to keep track of all outstanding stores to memory, in program order. – Keep track of address (when becomes available) and value (when becomes available) – FIFO ordering: will retire stores from this buffer in program order • When issuing a load, record current head of store queue (know which stores are ahead of you). • When have address for load, check store queue: – If any store prior to load is waiting for its address, stall load. – If load address matches earlier store address (associative lookup), then we have a memory-induced RAW hazard: » store value available return value » store value not available return ROB number of source – Otherwise, send out request to memory • Actual stores commit in order, so no worry about WAR/WAW hazards through memory.

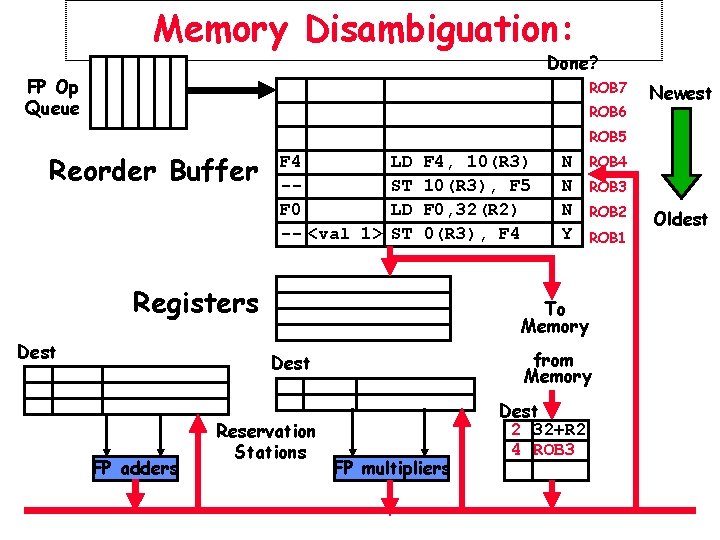

Memory Disambiguation: Done? FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer F 4 -F 0 -- <val 1> LD ST F 4, 10(R 3), F 5 F 0, 32(R 2) 0(R 3), F 4 Registers Dest ROB 4 ROB 3 ROB 2 ROB 1 To Memory from Memory Dest FP adders N N N Y Reservation Stations FP multipliers Dest 2 32+R 2 4 ROB 3 Oldest

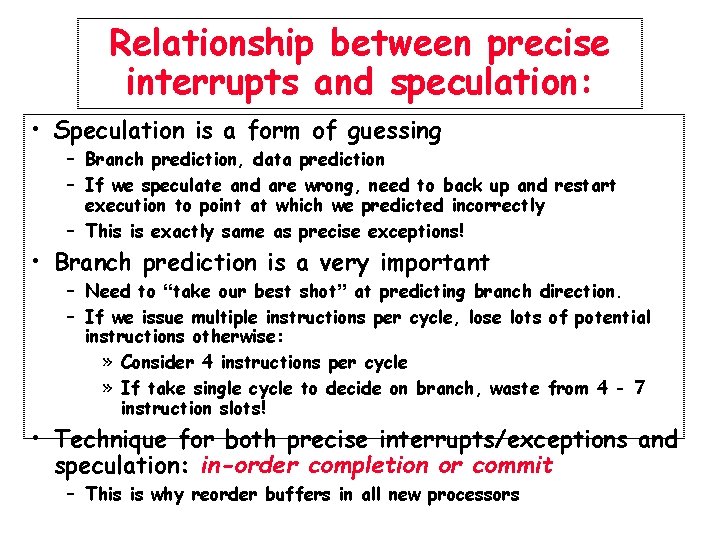

Relationship between precise interrupts and speculation: • Speculation is a form of guessing – Branch prediction, data prediction – If we speculate and are wrong, need to back up and restart execution to point at which we predicted incorrectly – This is exactly same as precise exceptions! • Branch prediction is a very important – Need to “take our best shot” at predicting branch direction. – If we issue multiple instructions per cycle, lose lots of potential instructions otherwise: » Consider 4 instructions per cycle » If take single cycle to decide on branch, waste from 4 - 7 instruction slots! • Technique for both precise interrupts/exceptions and speculation: in-order completion or commit – This is why reorder buffers in all new processors

- Slides: 12