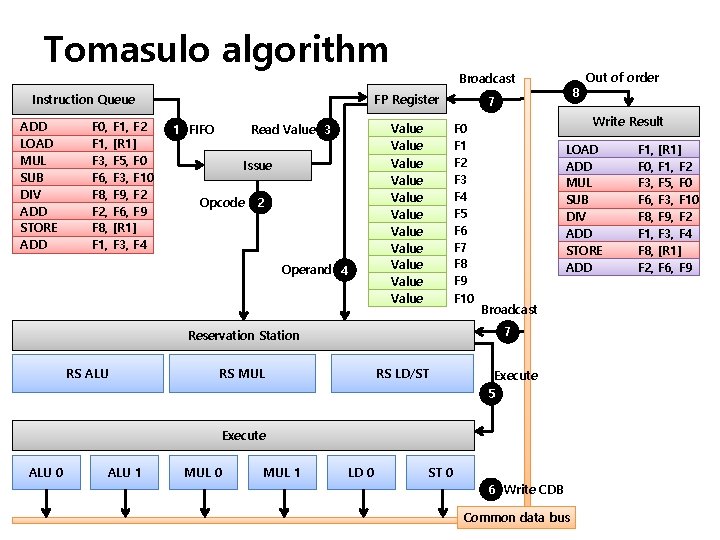

Tomasulo algorithm Tomasulo algorithm FP Register Instruction Queue

- Slides: 25

Tomasulo algorithm 윤진훈

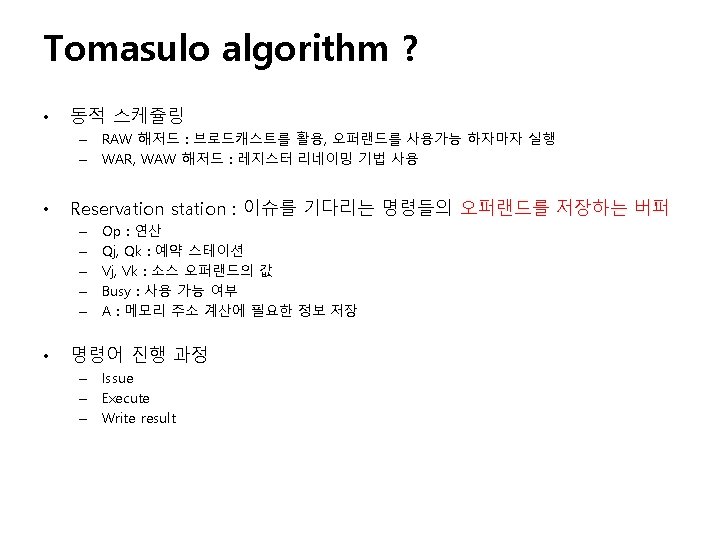

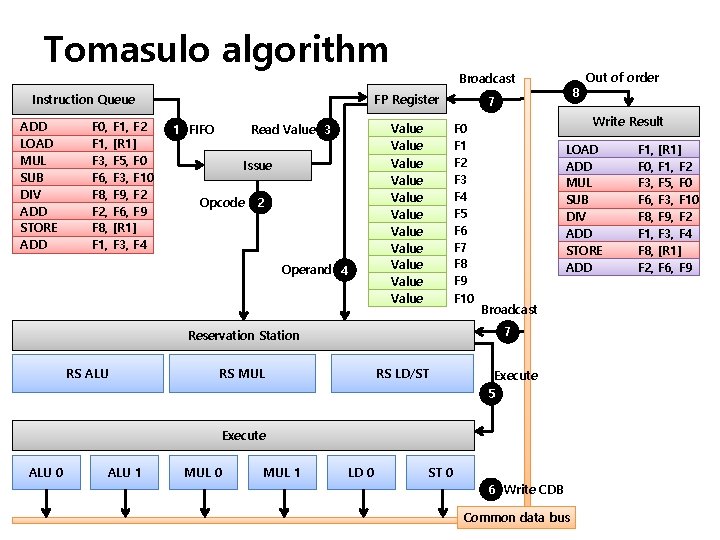

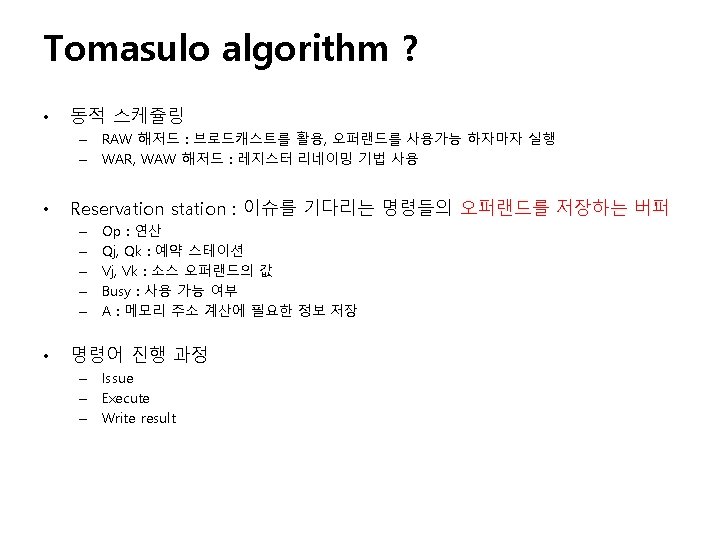

Tomasulo algorithm FP Register Instruction Queue ADD LOAD MUL SUB DIV ADD STORE ADD F 0, F 1, F 3, F 6, F 8, F 2, F 8, F 1, F 2 [R 1] F 5, F 0 F 3, F 10 F 9, F 2 F 6, F 9 [R 1] F 3, F 4 Broadcast 1 FIFO Read Value 3 Issue Opcode 2 Operand 4 Write Result F 0 F 1 F 2 F 3 F 4 F 5 F 6 F 7 F 8 F 9 Value Value Value F 10 LOAD ADD MUL SUB DIV ADD STORE ADD Broadcast 7 Reservation Station RS ALU 8 7 RS MUL RS LD/ST Execute 5 Execute ALU 0 ALU 1 MUL 0 MUL 1 LD 0 Out of order ST 0 6 Write CDB Common data bus F 1, F 0, F 3, F 6, F 8, F 1, F 8, F 2, [R 1] F 1, F 2 F 5, F 0 F 3, F 10 F 9, F 2 F 3, F 4 [R 1] F 6, F 9

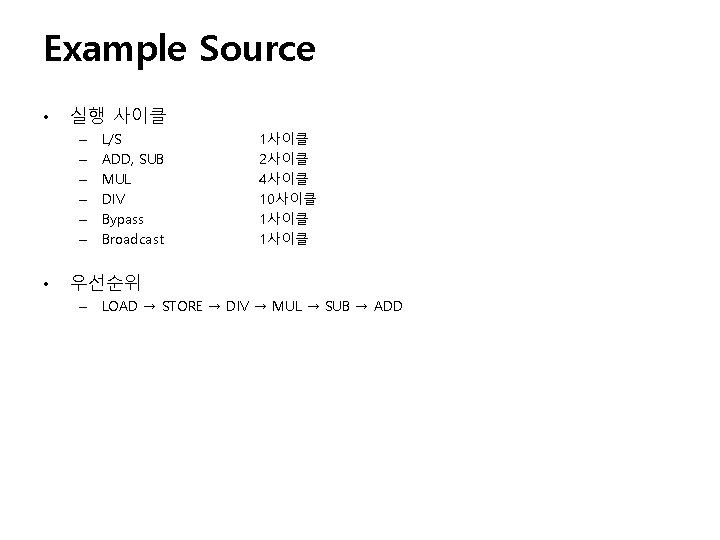

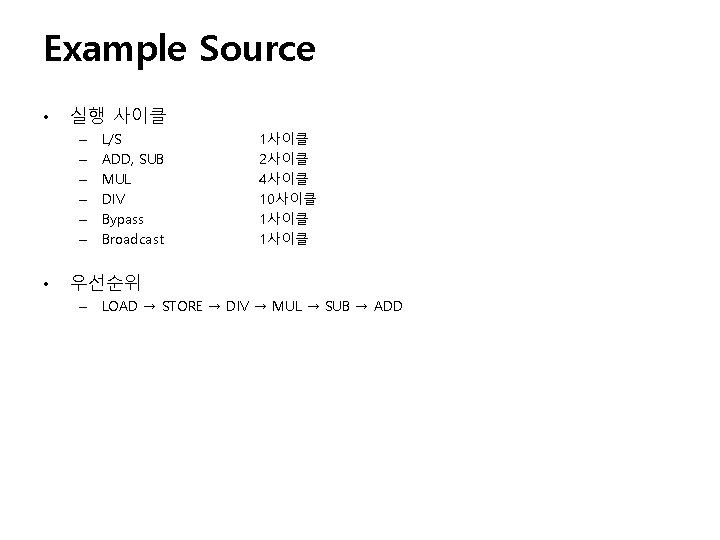

Example Source • 실행 사이클 – – – • L/S ADD, SUB MUL DIV Bypass Broadcast 1사이클 2사이클 4사이클 10사이클 1사이클 우선순위 – LOAD → STORE → DIV → MUL → SUB → ADD

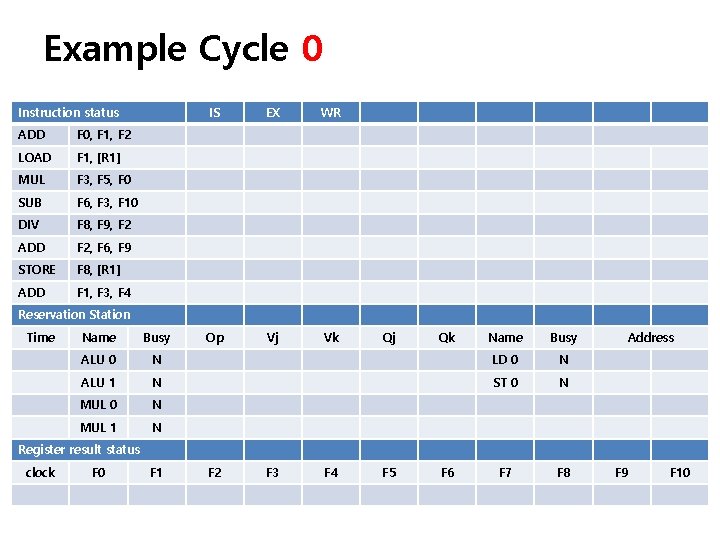

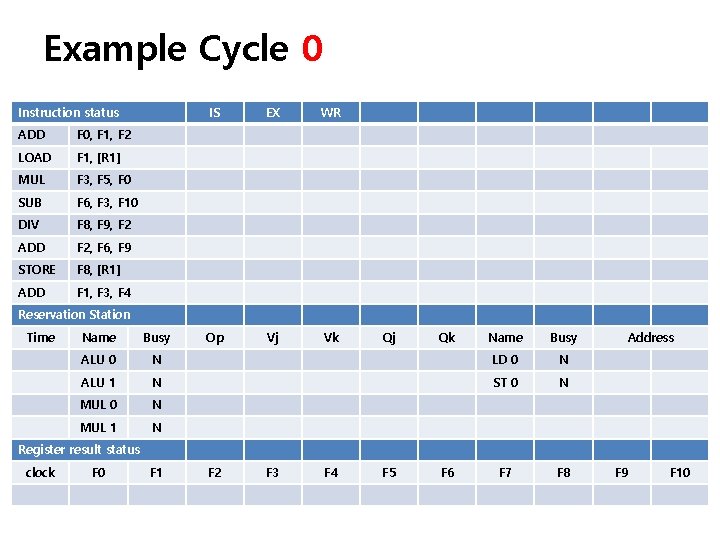

Example Cycle 0 Instruction status ADD F 0, F 1, F 2 LOAD F 1, [R 1] MUL F 3, F 5, F 0 SUB F 6, F 3, F 10 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 IS EX WR Op Vj Vk Reservation Station Time Name Busy ALU 0 Qj Qk Name Busy N LD 0 N ALU 1 N ST 0 N MUL 1 N F 7 F 8 Address Register result status clock F 0 F 1 F 2 F 3 F 4 F 5 F 6 F 9 F 10

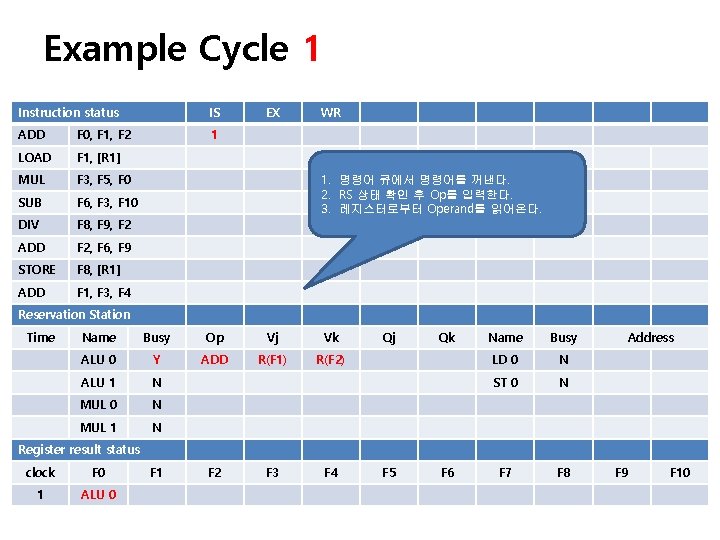

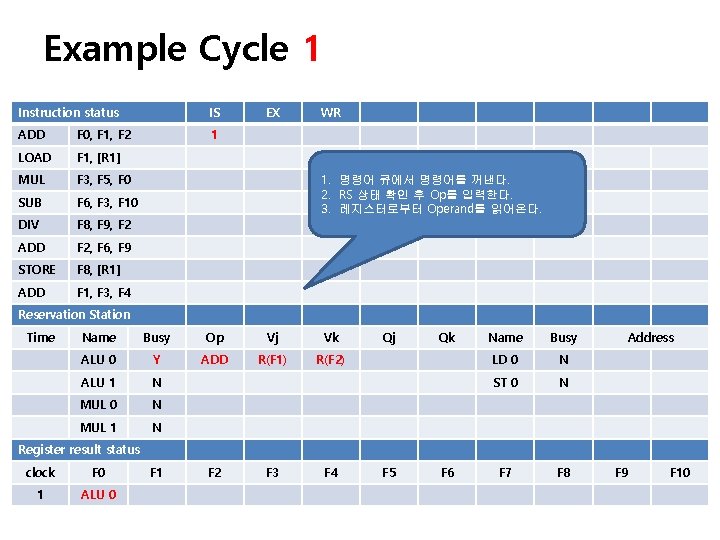

Example Cycle 1 Instruction status IS ADD F 0, F 1, F 2 1 LOAD F 1, [R 1] MUL F 3, F 5, F 0 SUB F 6, F 3, F 10 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 EX WR 1. 명령어 큐에서 명령어를 꺼낸다. 2. RS 상태 확인 후 Op를 입력한다. 3. 레지스터로부터 Operand를 읽어온다. Reservation Station Time Name Busy Op Vj Vk ALU 0 Y ADD R(F 1) R(F 2) ALU 1 N MUL 0 N MUL 1 N Qj Qk Name Busy LD 0 N ST 0 N F 7 F 8 Address Register result status clock F 0 1 ALU 0 F 1 F 2 F 3 F 4 F 5 F 6 F 9 F 10

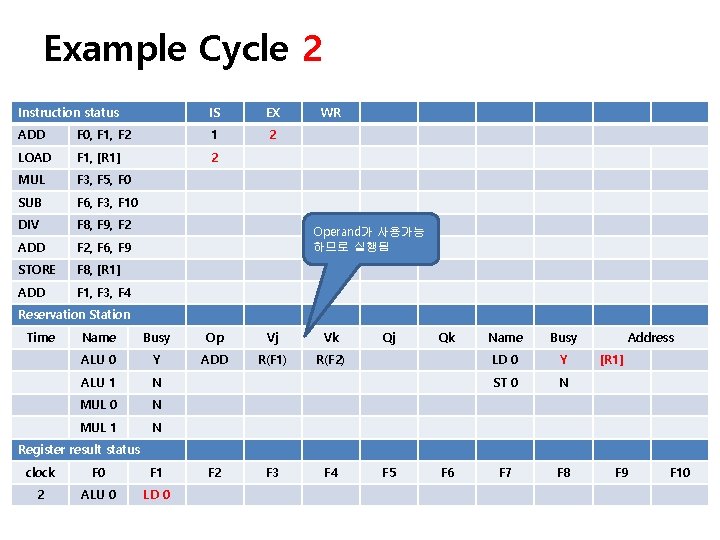

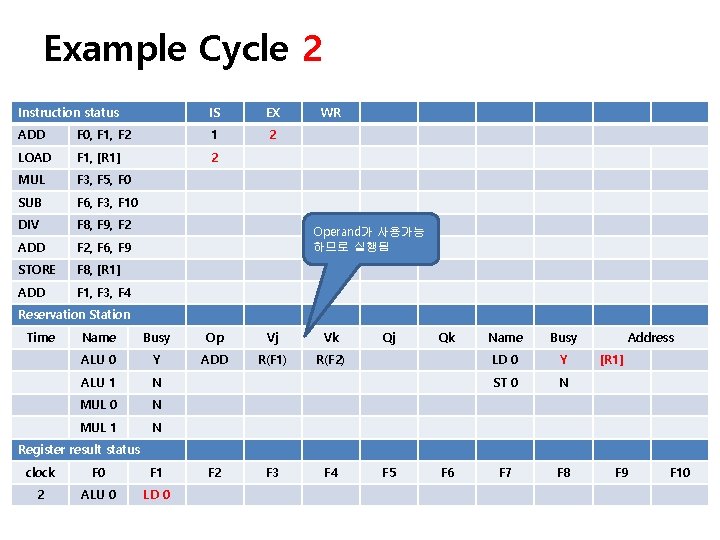

Example Cycle 2 Instruction status IS EX ADD F 0, F 1, F 2 1 2 LOAD F 1, [R 1] 2 MUL F 3, F 5, F 0 SUB F 6, F 3, F 10 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 WR Operand가 사용가능 하므로 실행됨 Reservation Station Time Name Busy Op Vj Vk ALU 0 Y ADD R(F 1) R(F 2) ALU 1 N MUL 0 N MUL 1 N Qj Qk Name Busy LD 0 Y ST 0 N F 7 F 8 Address [R 1] Register result status clock F 0 F 1 2 ALU 0 LD 0 F 2 F 3 F 4 F 5 F 6 F 9 F 10

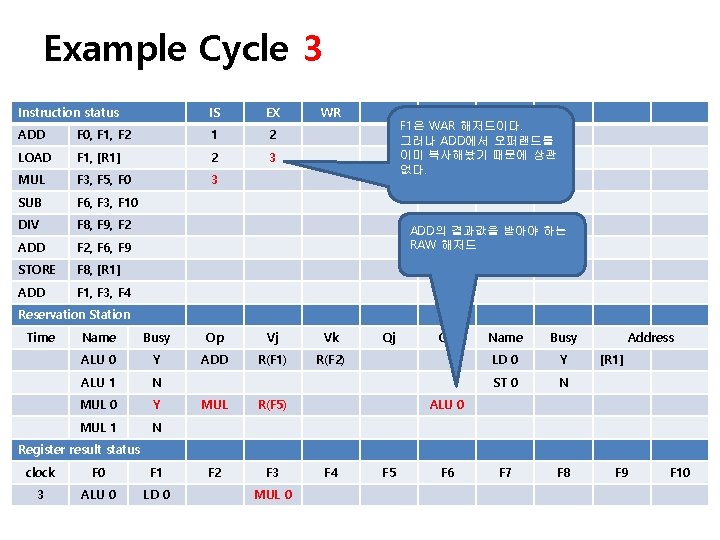

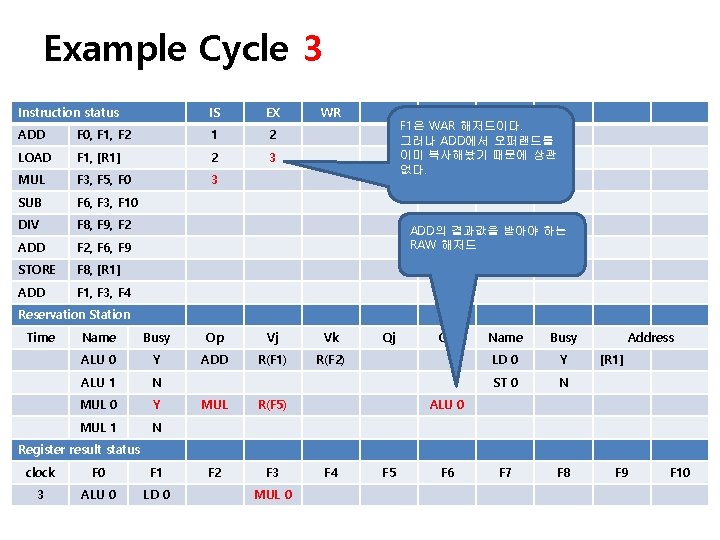

Example Cycle 3 Instruction status IS EX ADD F 0, F 1, F 2 1 2 LOAD F 1, [R 1] 2 3 MUL F 3, F 5, F 0 3 SUB F 6, F 3, F 10 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 WR F 1은 WAR 해저드이다. 그러나 ADD에서 오퍼랜드를 이미 복사해놨기 때문에 상관 없다. ADD의 결과값을 받아야 하는 RAW 해저드 Reservation Station Time Name Busy Op Vj Vk ALU 0 Y ADD R(F 1) R(F 2) ALU 1 N MUL 0 Y MUL 1 N MUL R(F 5) F 2 F 3 Qj Qk Name Busy LD 0 Y ST 0 N F 7 F 8 Address [R 1] ALU 0 Register result status clock F 0 F 1 3 ALU 0 LD 0 MUL 0 F 4 F 5 F 6 F 9 F 10

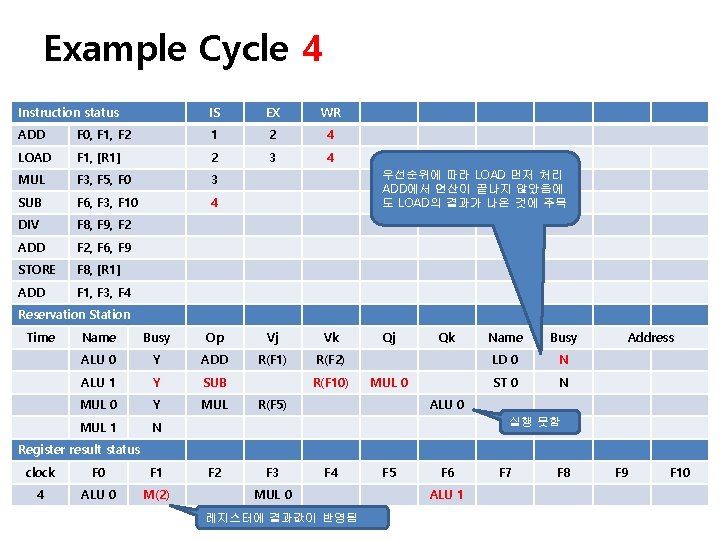

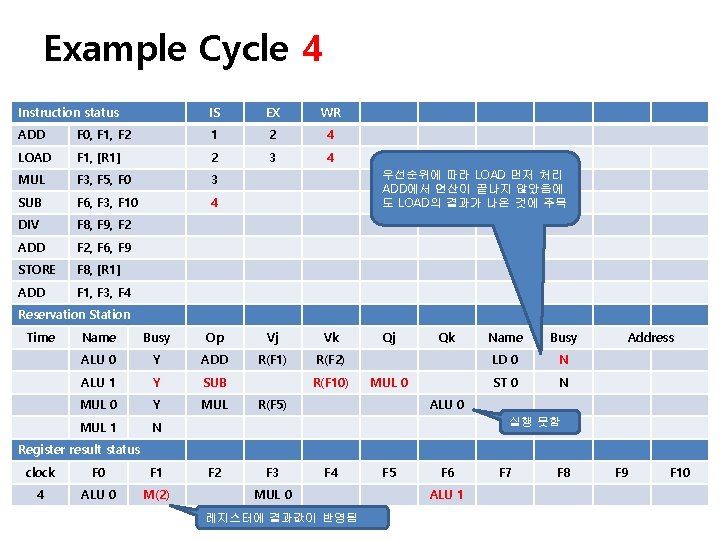

Example Cycle 4 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 4 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 우선순위에 따라 LOAD 먼저 처리 ADD에서 연산이 끝나지 않았음에 도 LOAD의 결과가 나온 것에 주목 Reservation Station Time Name Busy Op Vj Vk ALU 0 Y ADD R(F 1) R(F 2) ALU 1 Y SUB MUL 0 Y MUL 1 N R(F 10) Qj Qk MUL 0 R(F 5) Name Busy LD 0 N ST 0 N Address ALU 0 실행 못함 Register result status clock F 0 F 1 4 ALU 0 M(2) F 2 F 3 F 4 MUL 0 레지스터에 결과값이 반영됨 F 5 F 6 ALU 1 F 7 F 8 F 9 F 10

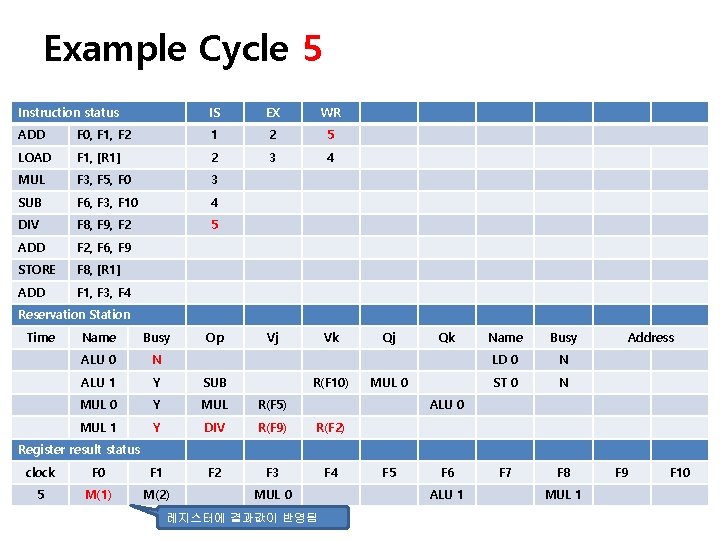

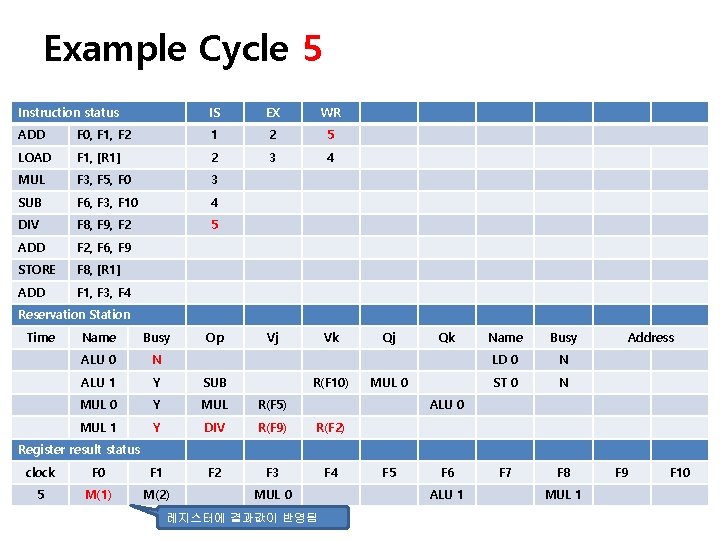

Example Cycle 5 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 Vj Vk Reservation Station Time Name Busy Op ALU 0 N ALU 1 Y SUB MUL 0 Y MUL R(F 5) MUL 1 Y DIV R(F 9) R(F 2) F 2 F 3 F 4 R(F 10) Qj Qk MUL 0 Name Busy LD 0 N ST 0 N F 7 F 8 Address ALU 0 Register result status clock F 0 F 1 5 M(1) M(2) MUL 0 레지스터에 결과값이 반영됨 F 5 F 6 ALU 1 MUL 1 F 9 F 10

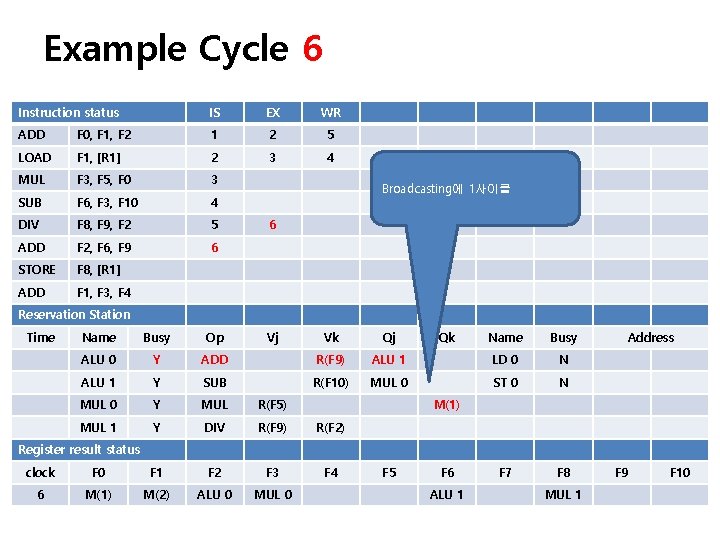

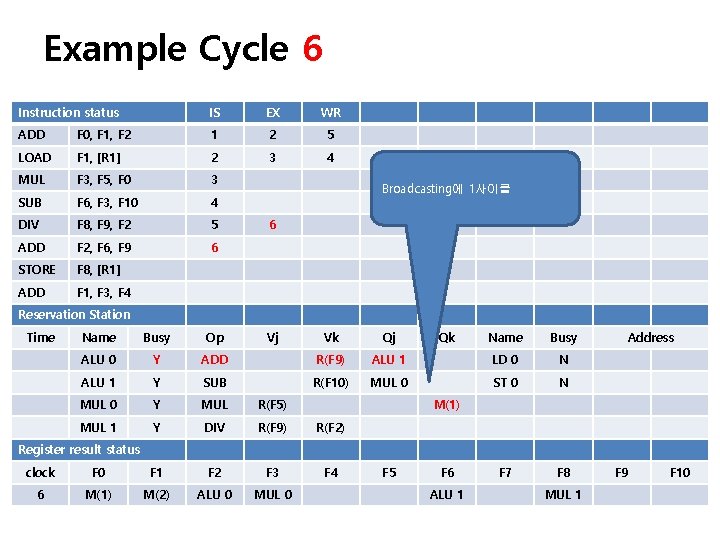

Example Cycle 6 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] ADD F 1, F 3, F 4 Broadcasting에 1사이클 6 Reservation Station Time Name Busy Op ALU 0 Y ALU 1 Vj Vk Qj ADD R(F 9) Y SUB R(F 10) MUL 0 Y MUL R(F 5) MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy ALU 1 LD 0 N MUL 0 ST 0 N F 7 F 8 Address M(1) Register result status clock F 0 F 1 F 2 F 3 6 M(1) M(2) ALU 0 MUL 0 F 5 F 6 ALU 1 MUL 1 F 9 F 10

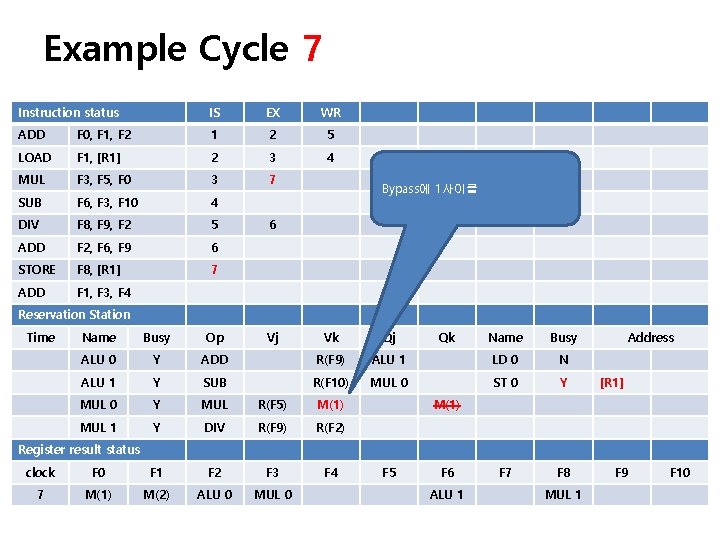

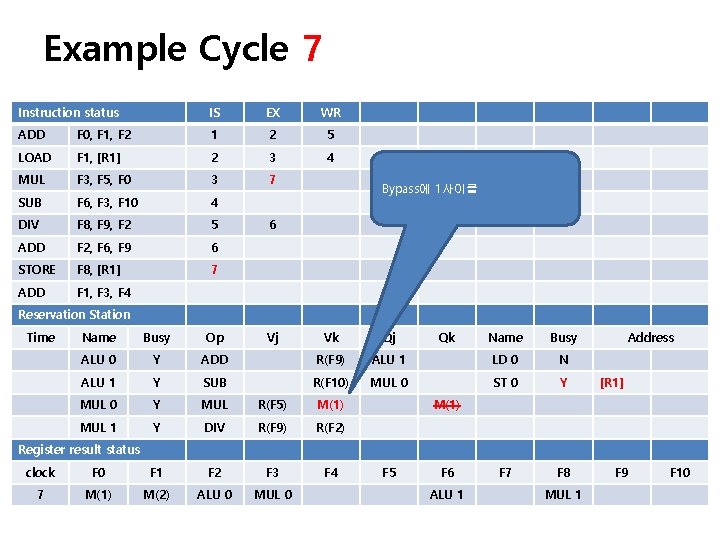

Example Cycle 7 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 Bypass에 1사이클 6 Reservation Station Time Name Busy Op ALU 0 Y ALU 1 Vj Vk Qj ADD R(F 9) Y SUB R(F 10) MUL 0 Y MUL R(F 5) M(1) MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy ALU 1 LD 0 N MUL 0 ST 0 Y F 7 F 8 Address [R 1] M(1) Register result status clock F 0 F 1 F 2 F 3 7 M(1) M(2) ALU 0 MUL 0 F 5 F 6 ALU 1 MUL 1 F 9 F 10

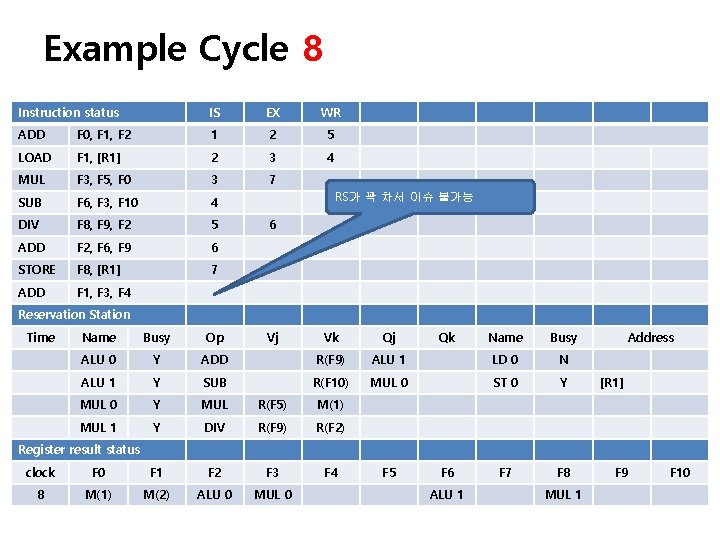

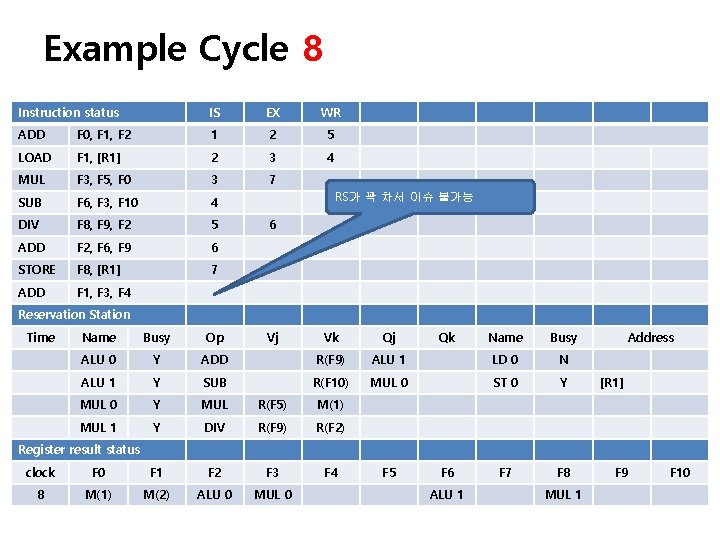

Example Cycle 8 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 RS가 꽉 차서 이슈 불가능 6 Reservation Station Time Name Busy Op ALU 0 Y ALU 1 Vj Vk Qj ADD R(F 9) Y SUB R(F 10) MUL 0 Y MUL R(F 5) M(1) MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy ALU 1 LD 0 N MUL 0 ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 8 M(1) M(2) ALU 0 MUL 0 F 5 F 6 ALU 1 MUL 1 F 9 F 10

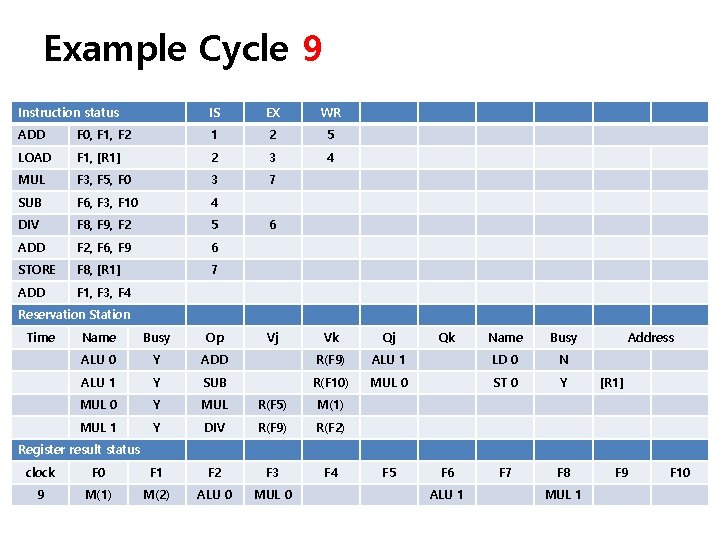

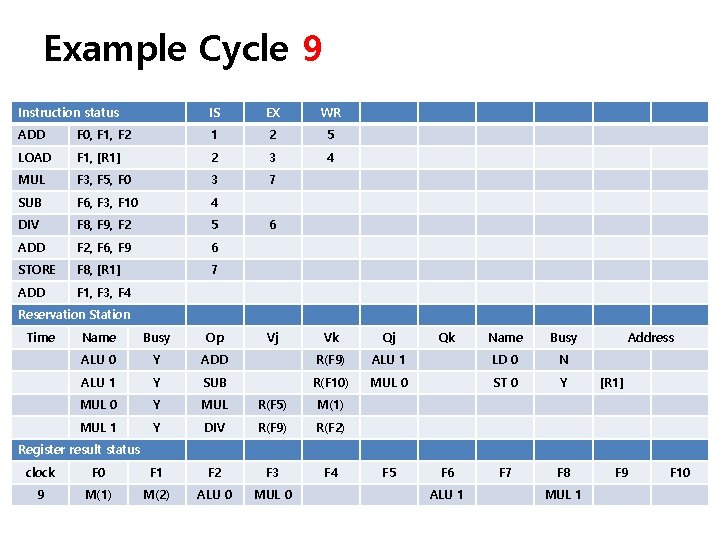

Example Cycle 9 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 6 Reservation Station Time Name Busy Op ALU 0 Y ALU 1 Vj Vk Qj ADD R(F 9) Y SUB R(F 10) MUL 0 Y MUL R(F 5) M(1) MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy ALU 1 LD 0 N MUL 0 ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 9 M(1) M(2) ALU 0 MUL 0 F 5 F 6 ALU 1 MUL 1 F 9 F 10

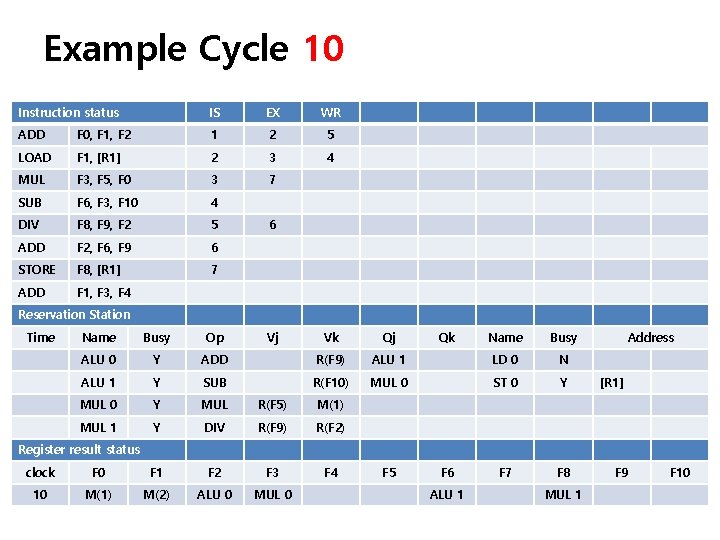

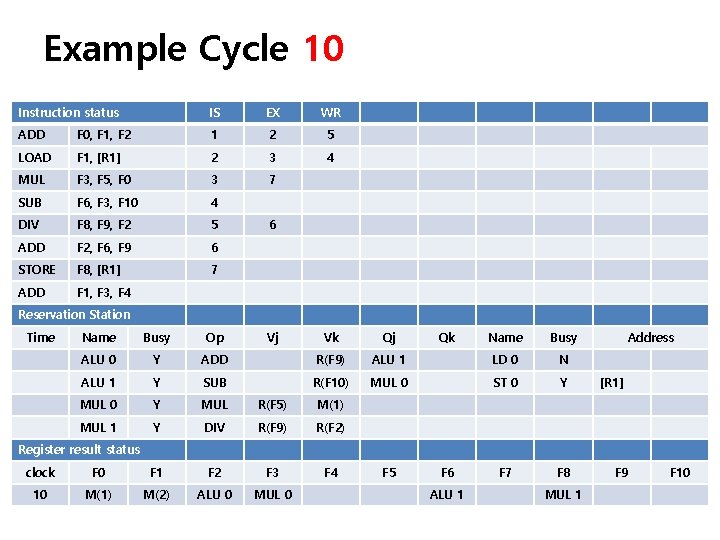

Example Cycle 10 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 6 Reservation Station Time Name Busy Op ALU 0 Y ALU 1 Vj Vk Qj ADD R(F 9) Y SUB R(F 10) MUL 0 Y MUL R(F 5) M(1) MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy ALU 1 LD 0 N MUL 0 ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 10 M(1) M(2) ALU 0 MUL 0 F 5 F 6 ALU 1 MUL 1 F 9 F 10

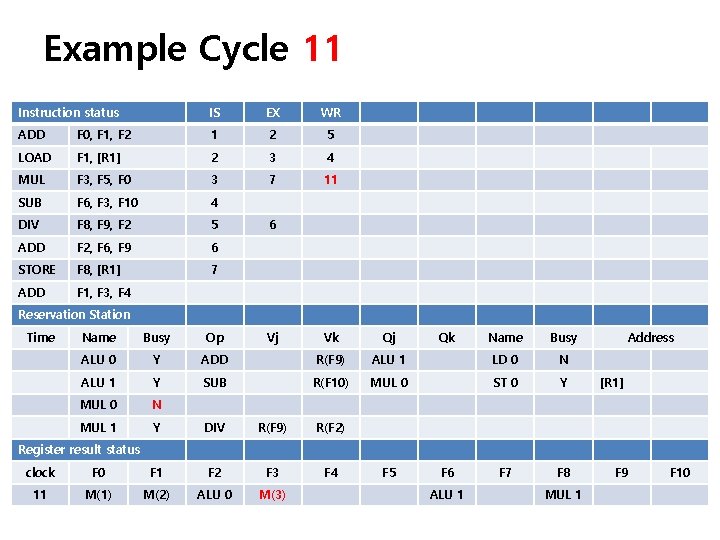

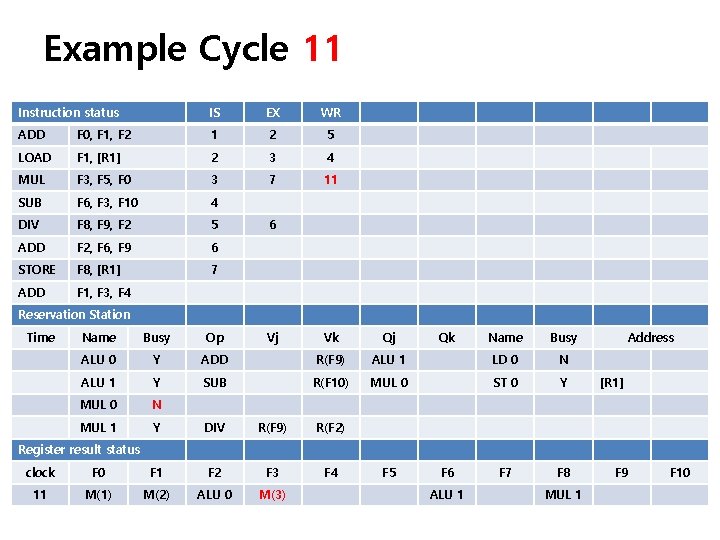

Example Cycle 11 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 6 Reservation Station Time Name Busy Op Vj Vk Qj ALU 0 Y ADD R(F 9) ALU 1 Y SUB R(F 10) MUL 0 N MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy ALU 1 LD 0 N MUL 0 ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 11 M(1) M(2) ALU 0 M(3) F 5 F 6 ALU 1 MUL 1 F 9 F 10

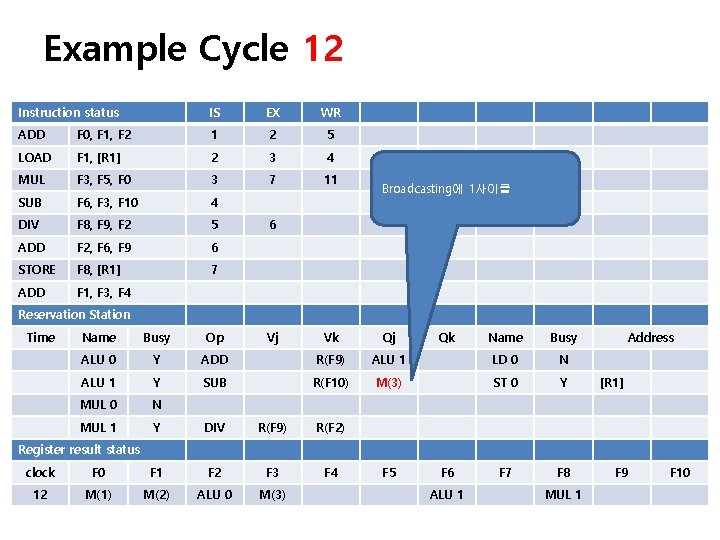

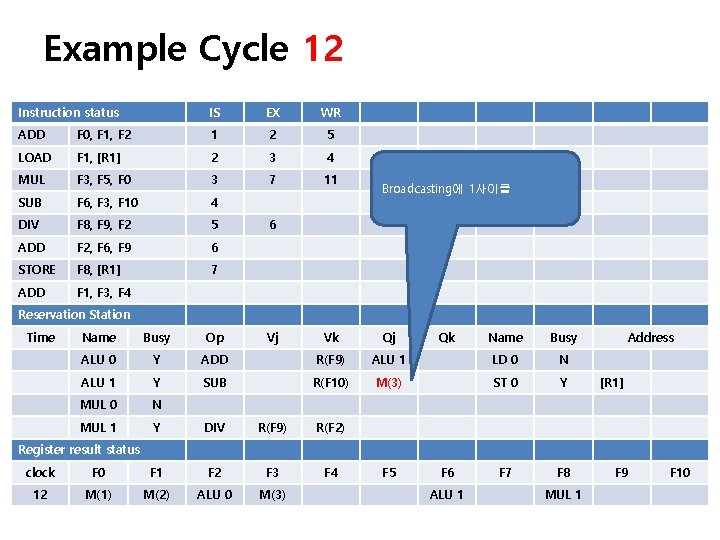

Example Cycle 12 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 Broadcasting에 1사이클 6 Reservation Station Time Name Busy Op Vj Vk Qj ALU 0 Y ADD R(F 9) ALU 1 Y SUB R(F 10) MUL 0 N MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy ALU 1 LD 0 N M(3) ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 12 M(1) M(2) ALU 0 M(3) F 5 F 6 ALU 1 MUL 1 F 9 F 10

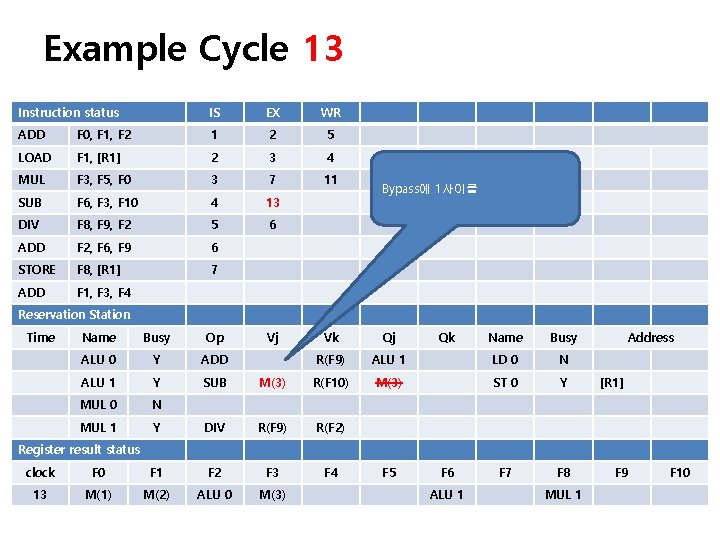

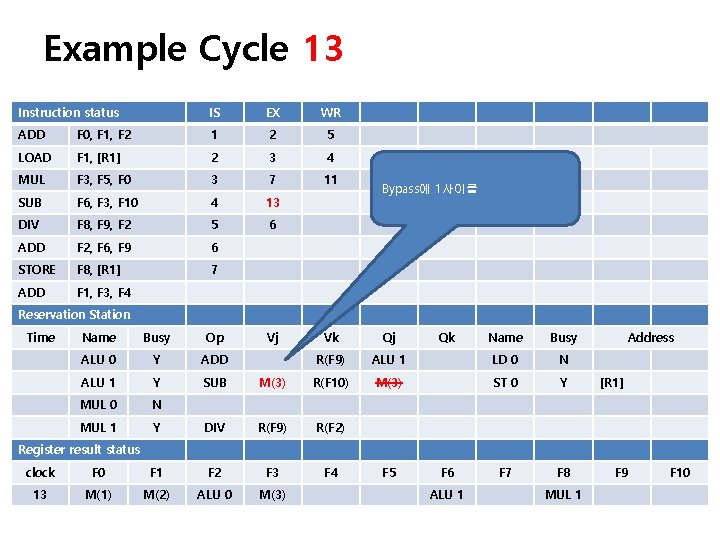

Example Cycle 13 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 13 DIV F 8, F 9, F 2 5 6 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 Bypass에 1사이클 Reservation Station Time Name Busy Op ALU 0 Y ADD ALU 1 Y SUB MUL 0 N MUL 1 Y Vj Vk Qj R(F 9) M(3) R(F 10) DIV R(F 9) R(F 2) F 4 Qk Name Busy ALU 1 LD 0 N M(3) ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 13 M(1) M(2) ALU 0 M(3) F 5 F 6 ALU 1 MUL 1 F 9 F 10

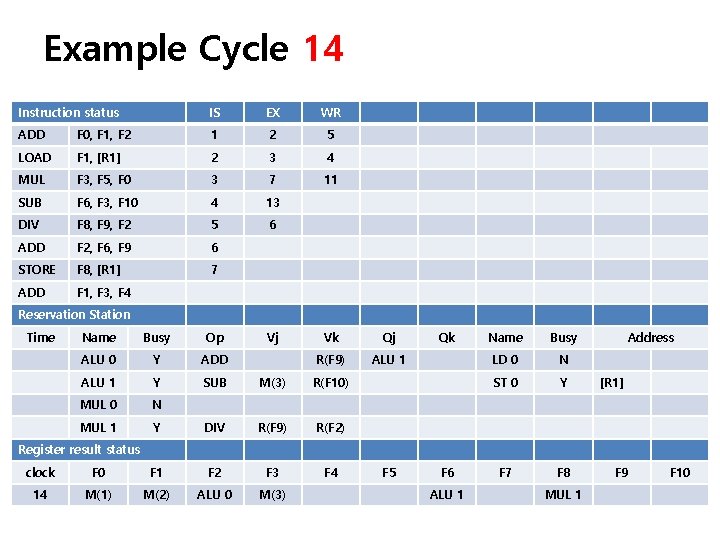

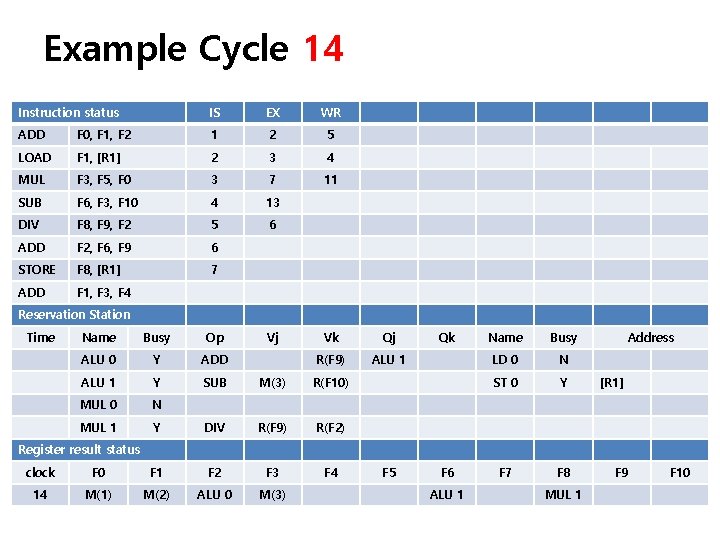

Example Cycle 14 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 13 DIV F 8, F 9, F 2 5 6 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 Reservation Station Time Name Busy Op Vj Vk Qj ALU 0 Y ADD R(F 9) ALU 1 Y SUB M(3) R(F 10) MUL 0 N MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy LD 0 N ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 14 M(1) M(2) ALU 0 M(3) F 5 F 6 ALU 1 MUL 1 F 9 F 10

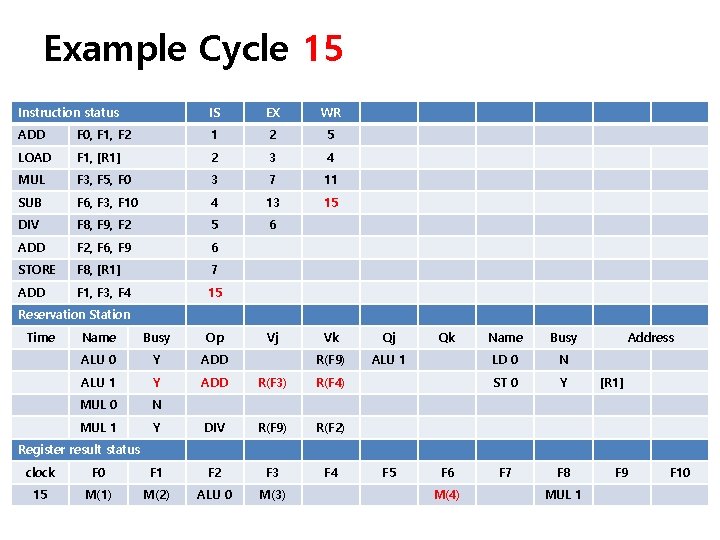

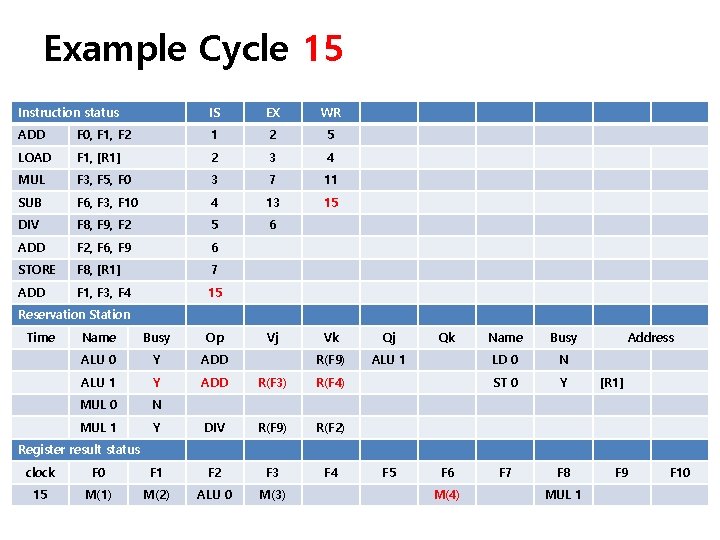

Example Cycle 15 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 13 15 DIV F 8, F 9, F 2 5 6 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 15 Reservation Station Time Name Busy Op Vj Vk Qj ALU 0 Y ADD R(F 9) ALU 1 Y ADD R(F 3) R(F 4) MUL 0 N MUL 1 Y DIV R(F 9) R(F 2) F 4 Qk Name Busy LD 0 N ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 15 M(1) M(2) ALU 0 M(3) F 5 F 6 M(4) MUL 1 F 9 F 10

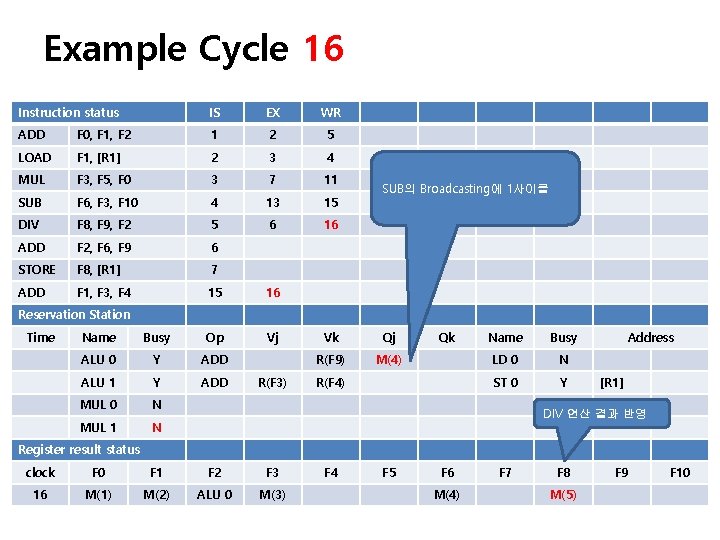

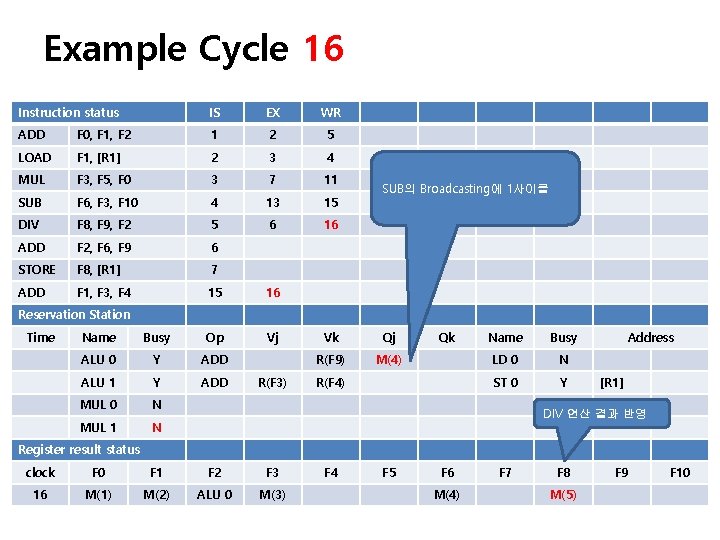

Example Cycle 16 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 13 15 DIV F 8, F 9, F 2 5 6 16 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 15 16 Vj SUB의 Broadcasting에 1사이클 Reservation Station Time Name Busy Op ALU 0 Y ADD ALU 1 Y ADD MUL 0 N MUL 1 N R(F 3) Vk Qj R(F 9) M(4) Qk R(F 4) Name Busy LD 0 N ST 0 Y Address [R 1] DIV 연산 결과 반영 Register result status clock F 0 F 1 F 2 F 3 16 M(1) M(2) ALU 0 M(3) F 4 F 5 F 6 M(4) F 7 F 8 M(5) F 9 F 10

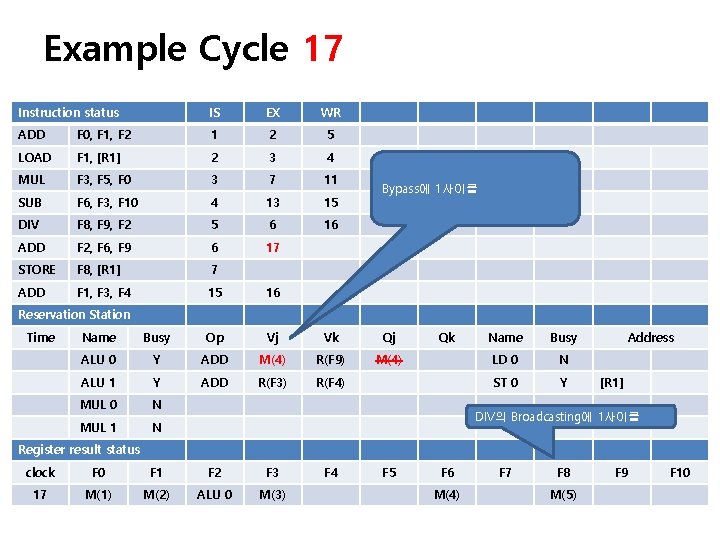

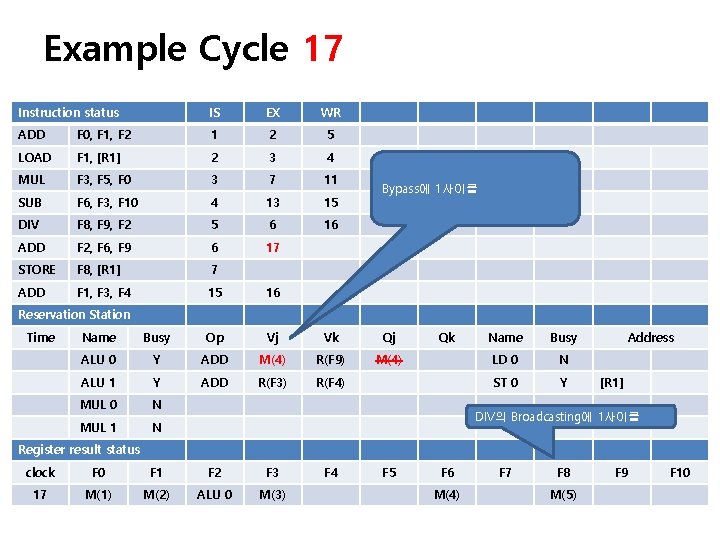

Example Cycle 17 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 13 15 DIV F 8, F 9, F 2 5 6 16 ADD F 2, F 6, F 9 6 17 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 15 16 Bypass에 1사이클 Reservation Station Time Name Busy Op Vj Vk Qj ALU 0 Y ADD M(4) R(F 9) M(4) ALU 1 Y ADD R(F 3) R(F 4) MUL 0 N MUL 1 N Qk Name Busy LD 0 N ST 0 Y Address [R 1] DIV의 Broadcasting에 1사이클 Register result status clock F 0 F 1 F 2 F 3 17 M(1) M(2) ALU 0 M(3) F 4 F 5 F 6 M(4) F 7 F 8 M(5) F 9 F 10

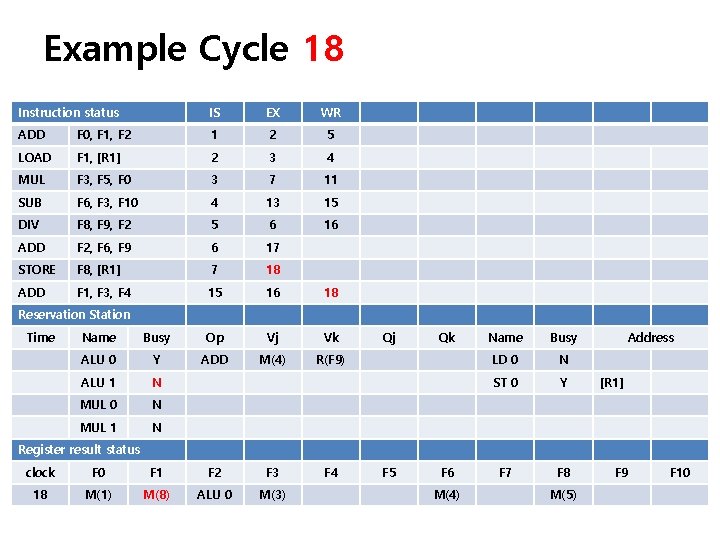

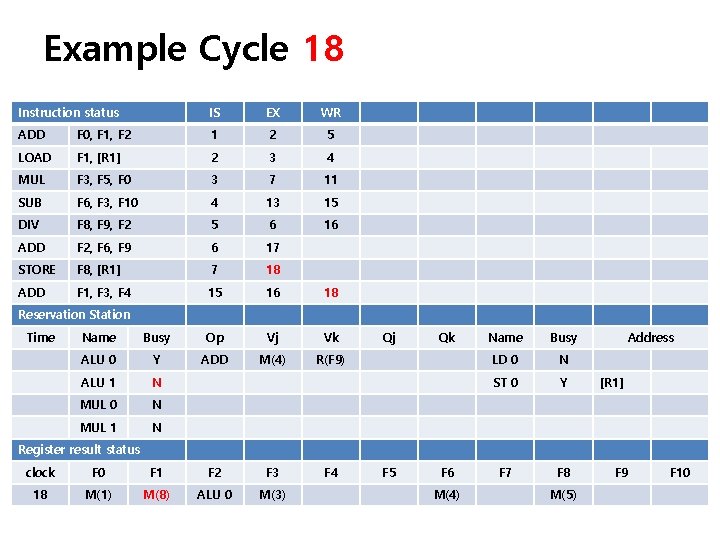

Example Cycle 18 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 13 15 DIV F 8, F 9, F 2 5 6 16 ADD F 2, F 6, F 9 6 17 STORE F 8, [R 1] 7 18 ADD F 1, F 3, F 4 15 16 18 Reservation Station Time Name Busy Op Vj Vk ALU 0 Y ADD M(4) R(F 9) ALU 1 N MUL 0 N MUL 1 N Qj Qk Name Busy LD 0 N ST 0 Y F 7 F 8 Address [R 1] Register result status clock F 0 F 1 F 2 F 3 18 M(1) M(8) ALU 0 M(3) F 4 F 5 F 6 M(4) M(5) F 9 F 10

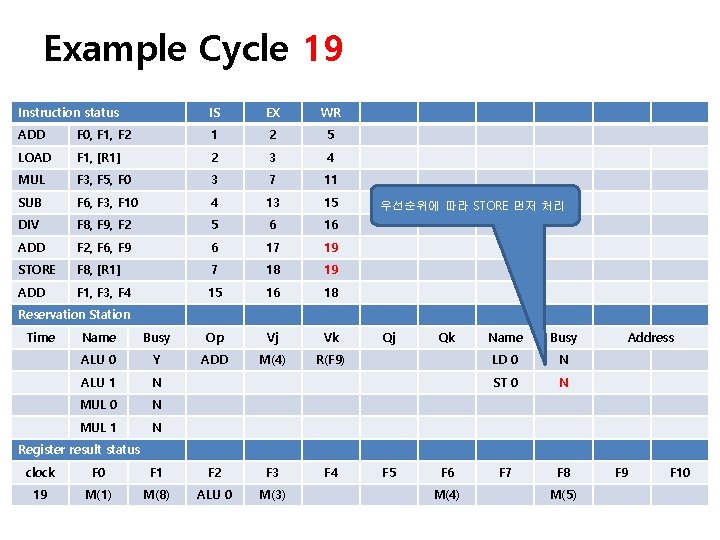

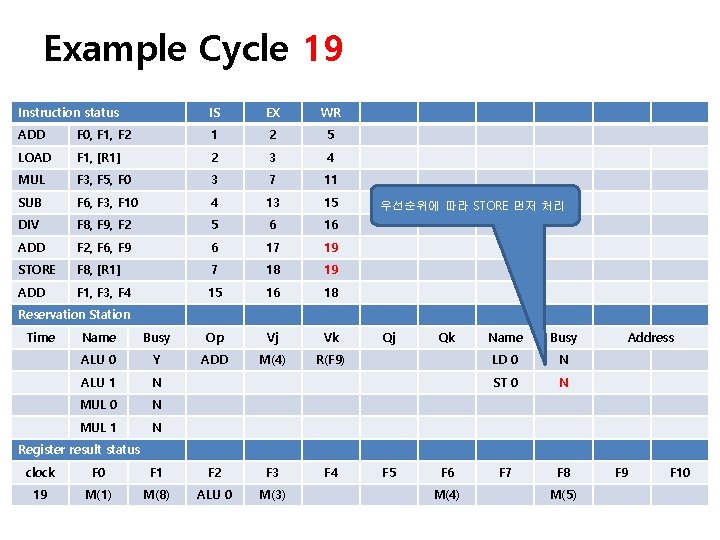

Example Cycle 19 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 13 15 DIV F 8, F 9, F 2 5 6 16 ADD F 2, F 6, F 9 6 17 19 STORE F 8, [R 1] 7 18 19 ADD F 1, F 3, F 4 15 16 18 우선순위에 따라 STORE 먼저 처리 Reservation Station Time Name Busy Op Vj Vk ALU 0 Y ADD M(4) R(F 9) ALU 1 N MUL 0 N MUL 1 N Qj Qk Name Busy LD 0 N ST 0 N F 7 F 8 Address Register result status clock F 0 F 1 F 2 F 3 19 M(1) M(8) ALU 0 M(3) F 4 F 5 F 6 M(4) M(5) F 9 F 10

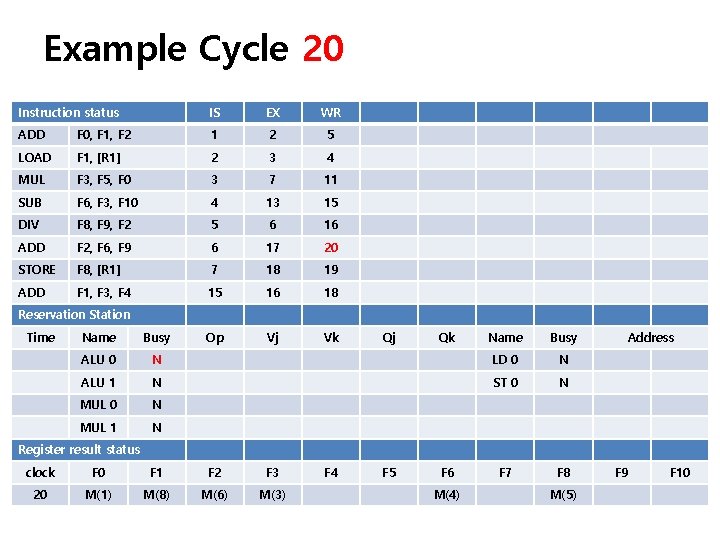

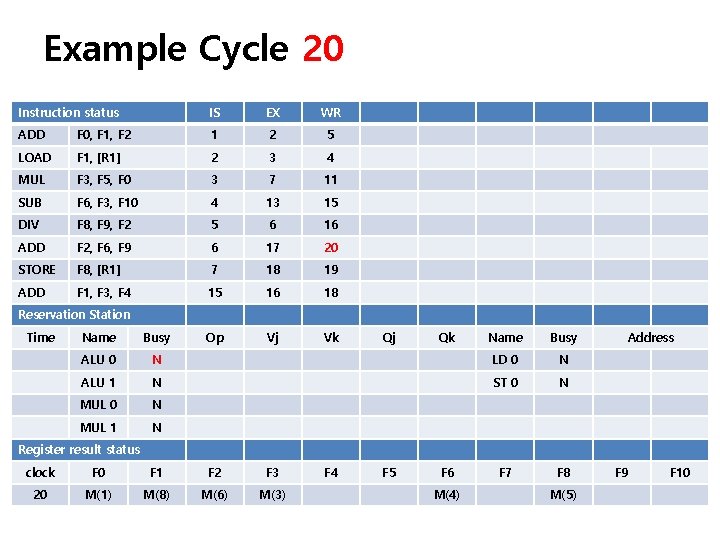

Example Cycle 20 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 13 15 DIV F 8, F 9, F 2 5 6 16 ADD F 2, F 6, F 9 6 17 20 STORE F 8, [R 1] 7 18 19 ADD F 1, F 3, F 4 15 16 18 Op Vj Vk Reservation Station Time Name Busy ALU 0 Qj Qk Name Busy N LD 0 N ALU 1 N ST 0 N MUL 1 N F 7 F 8 Address Register result status clock F 0 F 1 F 2 F 3 20 M(1) M(8) M(6) M(3) F 4 F 5 F 6 M(4) M(5) F 9 F 10