Tomasulo Algorithm Example 2 1 Tomasulo Example LD

- Slides: 16

Tomasulo Algorithm Example 2 1

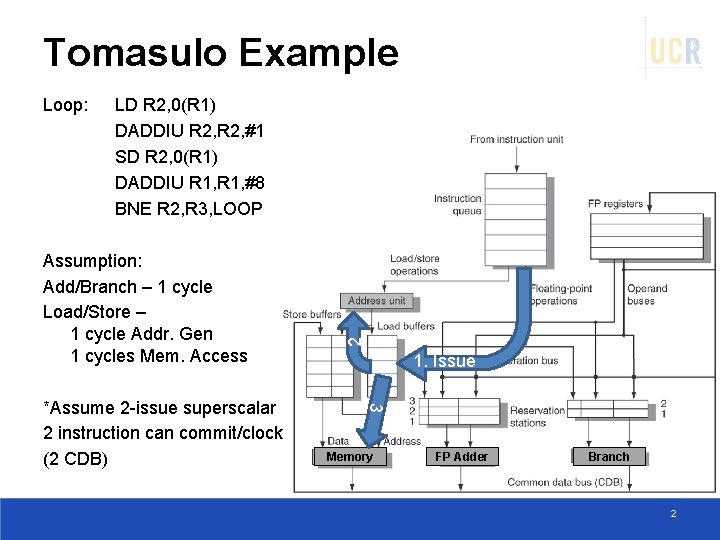

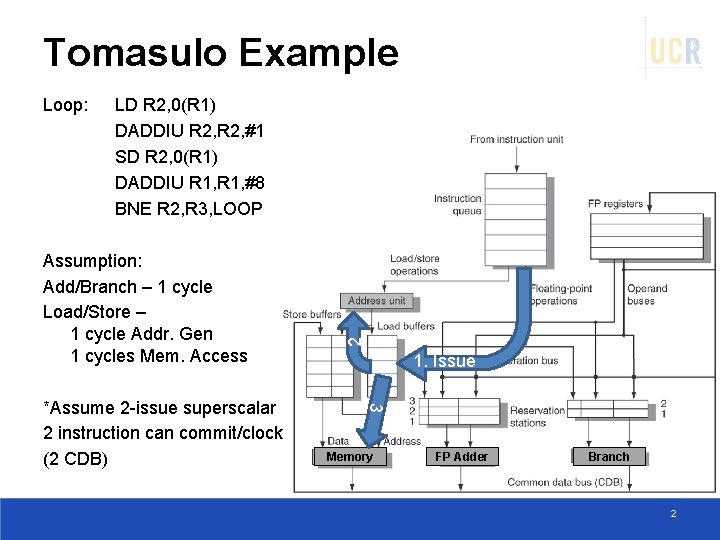

Tomasulo Example LD R 2, 0(R 1) DADDIU R 2, #1 SD R 2, 0(R 1) DADDIU R 1, #8 BNE R 2, R 3, LOOP Assumption: Add/Branch – 1 cycle Load/Store – 1 cycle Addr. Gen 1 cycles Mem. Access 1. Issue 3 *Assume 2 -issue superscalar 2 instruction can commit/clock (2 CDB) 2 Loop: Memory FP Adder Branch 2

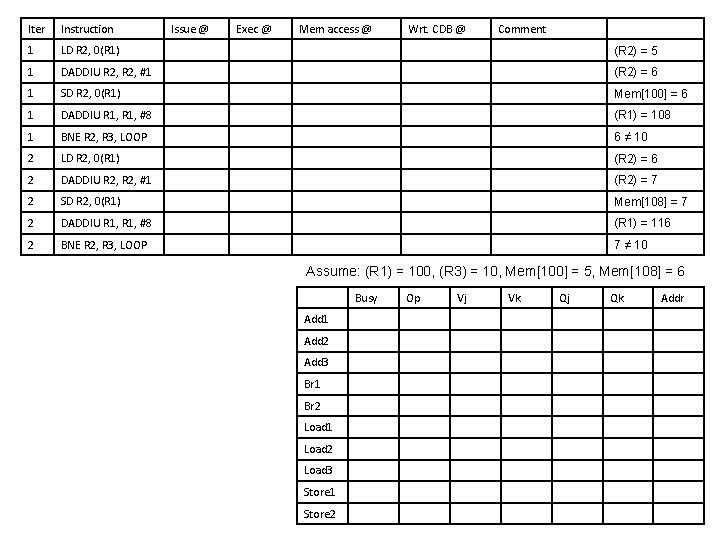

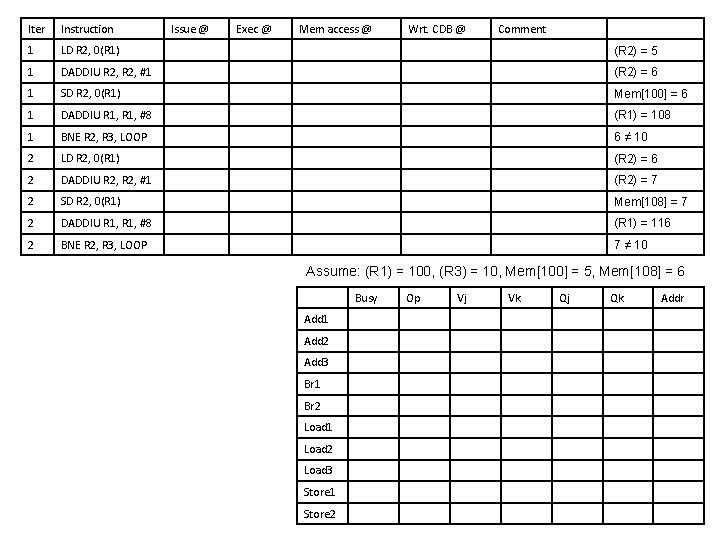

Iter Instruction Issue @ Exec @ Mem access @ Wrt. CDB @ Comment 1 LD R 2, 0(R 1) (R 2) = 5 1 DADDIU R 2, #1 (R 2) = 6 1 SD R 2, 0(R 1) Mem[100] = 6 1 DADDIU R 1, #8 (R 1) = 108 1 BNE R 2, R 3, LOOP 6 ≠ 10 2 LD R 2, 0(R 1) (R 2) = 6 2 DADDIU R 2, #1 (R 2) = 7 2 SD R 2, 0(R 1) Mem[108] = 7 2 DADDIU R 1, #8 (R 1) = 116 2 BNE R 2, R 3, LOOP 7 ≠ 10 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Busy Add 1 Add 2 Add 3 Br 1 Br 2 Load 1 Load 2 Load 3 Store 1 Store 2 Op Vj Vk Qj Qk Addr

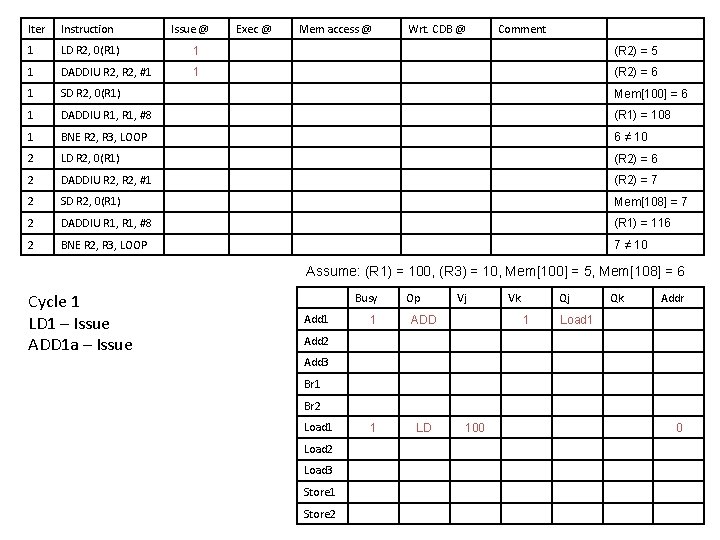

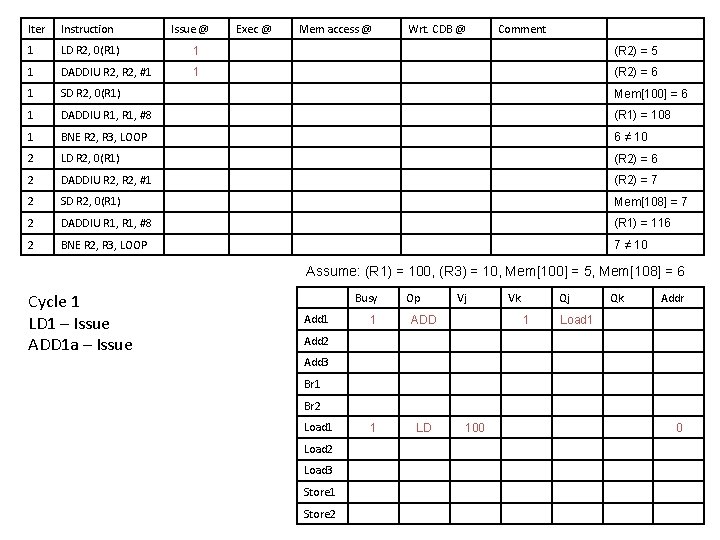

Iter Instruction Issue @ Exec @ Mem access @ Wrt. CDB @ Comment 1 LD R 2, 0(R 1) 1 (R 2) = 5 1 DADDIU R 2, #1 1 (R 2) = 6 1 SD R 2, 0(R 1) Mem[100] = 6 1 DADDIU R 1, #8 (R 1) = 108 1 BNE R 2, R 3, LOOP 6 ≠ 10 2 LD R 2, 0(R 1) (R 2) = 6 2 DADDIU R 2, #1 (R 2) = 7 2 SD R 2, 0(R 1) Mem[108] = 7 2 DADDIU R 1, #8 (R 1) = 116 2 BNE R 2, R 3, LOOP 7 ≠ 10 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 1 LD 1 – Issue ADD 1 a – Issue Busy Add 1 Op 1 ADD 1 LD Vj Vk Qj 1 Qk Addr Load 1 Add 2 Add 3 Br 1 Br 2 Load 1 Load 2 Load 3 Store 1 Store 2 100 0

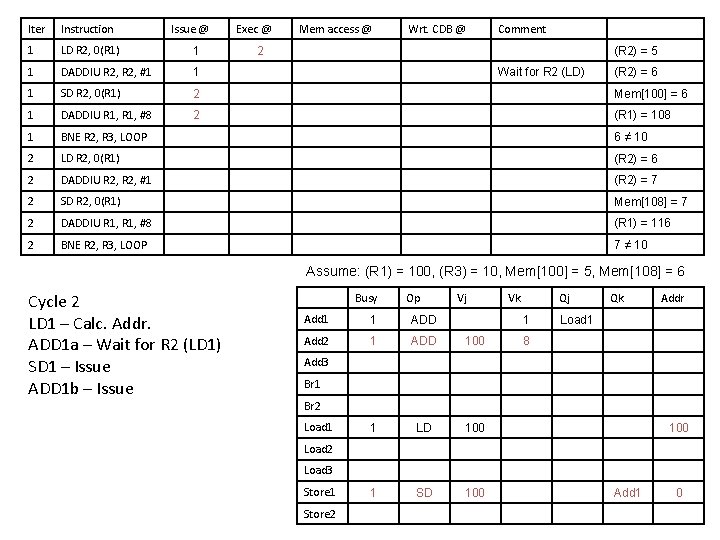

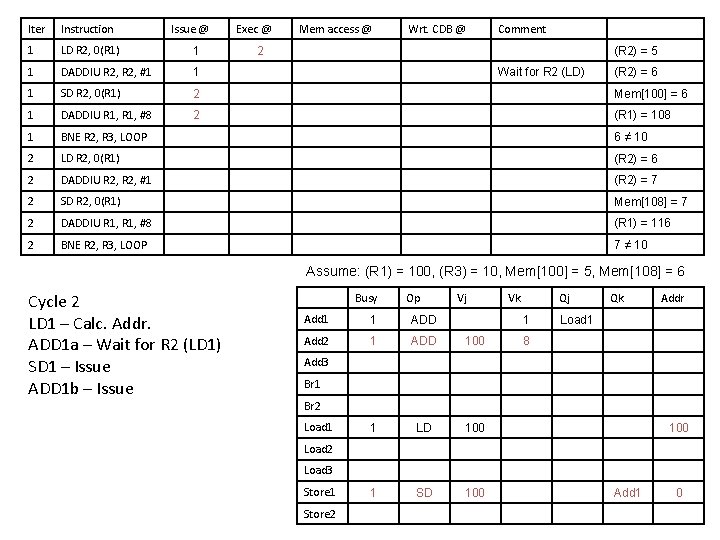

Iter Instruction Issue @ Exec @ Mem access @ Wrt. CDB @ Comment 1 LD R 2, 0(R 1) 1 1 DADDIU R 2, #1 1 1 SD R 2, 0(R 1) 2 Mem[100] = 6 1 DADDIU R 1, #8 2 (R 1) = 108 1 BNE R 2, R 3, LOOP 6 ≠ 10 2 LD R 2, 0(R 1) (R 2) = 6 2 DADDIU R 2, #1 (R 2) = 7 2 SD R 2, 0(R 1) Mem[108] = 7 2 DADDIU R 1, #8 (R 1) = 116 2 BNE R 2, R 3, LOOP 7 ≠ 10 2 (R 2) = 5 Wait for R 2 (LD) (R 2) = 6 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 2 LD 1 – Calc. Addr. ADD 1 a – Wait for R 2 (LD 1) SD 1 – Issue ADD 1 b – Issue Busy Op Vj Add 1 1 ADD Add 2 1 ADD 100 1 LD 100 1 SD 100 Vk Qj 1 Qk Addr Load 1 8 Add 3 Br 1 Br 2 Load 1 100 Load 2 Load 3 Store 1 Store 2 Add 1 0

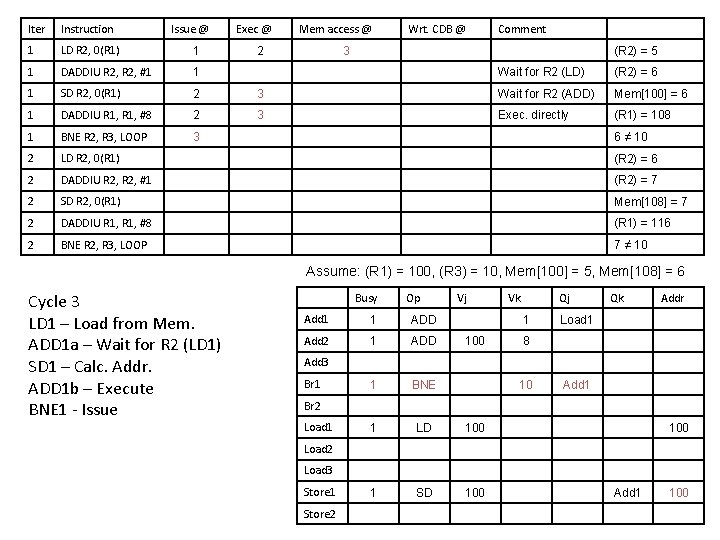

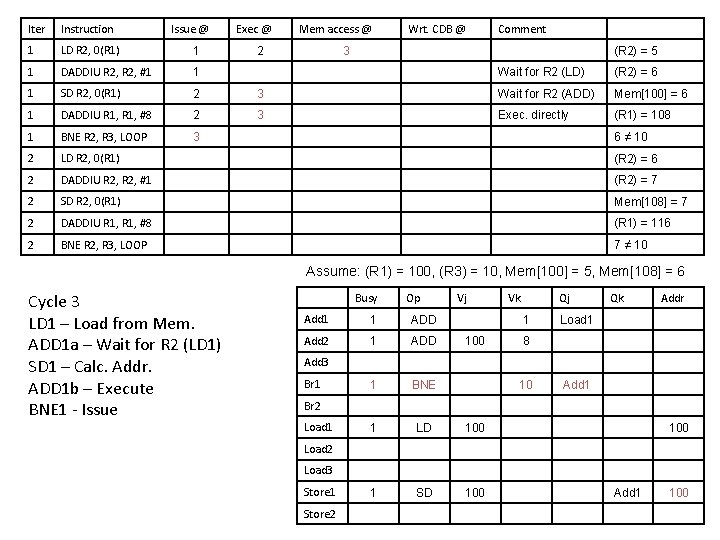

Iter Instruction Issue @ Exec @ Mem access @ 1 LD R 2, 0(R 1) 1 1 DADDIU R 2, #1 1 1 SD R 2, 0(R 1) 2 1 DADDIU R 1, #8 2 1 BNE R 2, R 3, LOOP 3 2 LD R 2, 0(R 1) (R 2) = 6 2 DADDIU R 2, #1 (R 2) = 7 2 SD R 2, 0(R 1) Mem[108] = 7 2 DADDIU R 1, #8 (R 1) = 116 2 BNE R 2, R 3, LOOP 7 ≠ 10 2 Wrt. CDB @ Comment 3 (R 2) = 5 Wait for R 2 (LD) (R 2) = 6 3 Wait for R 2 (ADD) Mem[100] = 6 3 Exec. directly (R 1) = 108 6 ≠ 10 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 3 LD 1 – Load from Mem. ADD 1 a – Wait for R 2 (LD 1) SD 1 – Calc. Addr. ADD 1 b – Execute BNE 1 - Issue Busy Op Vj Add 1 1 ADD Add 2 1 ADD 1 BNE 1 LD 100 1 SD 100 Vk Qj 1 100 Qk Addr Load 1 8 Add 3 Br 1 10 Add 1 Br 2 Load 1 100 Load 2 Load 3 Store 1 Store 2 Add 1 100

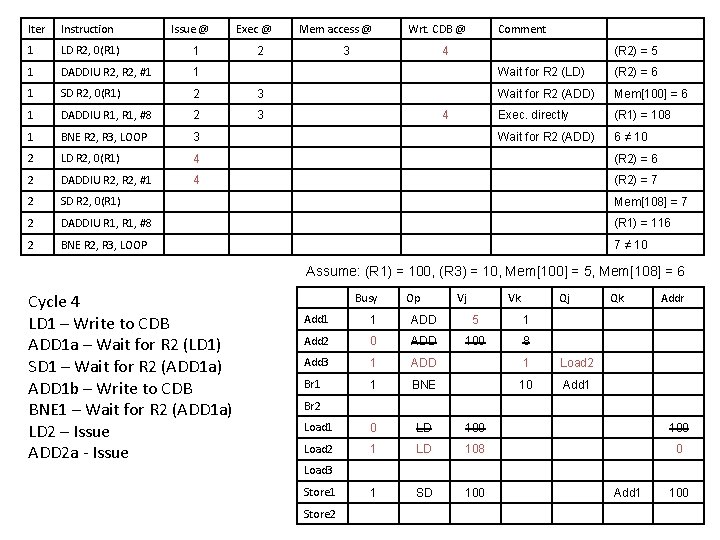

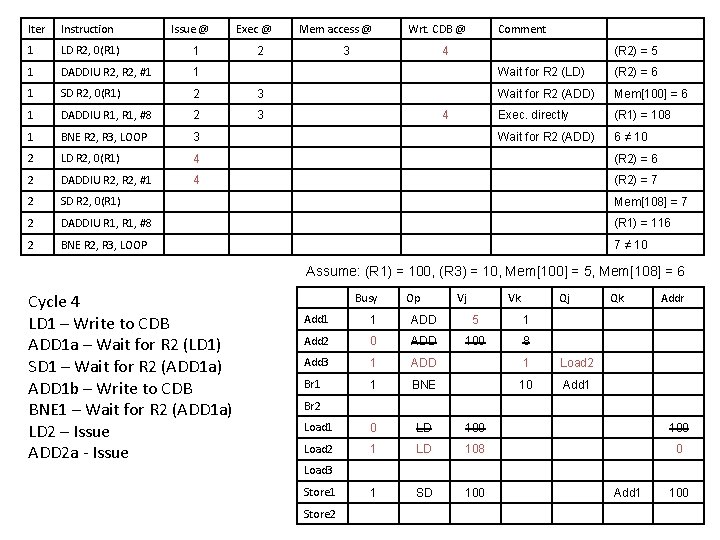

Iter Instruction Issue @ Exec @ Mem access @ 1 LD R 2, 0(R 1) 1 1 DADDIU R 2, #1 1 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 3 2 LD R 2, 0(R 1) 4 (R 2) = 6 2 DADDIU R 2, #1 4 (R 2) = 7 2 SD R 2, 0(R 1) Mem[108] = 7 2 DADDIU R 1, #8 (R 1) = 116 2 BNE R 2, R 3, LOOP 7 ≠ 10 2 Wrt. CDB @ 3 Comment 4 (R 2) = 5 4 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 Wait for R 2 (ADD) 6 ≠ 10 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 4 LD 1 – Write to CDB ADD 1 a – Wait for R 2 (LD 1) SD 1 – Wait for R 2 (ADD 1 a) ADD 1 b – Write to CDB BNE 1 – Wait for R 2 (ADD 1 a) LD 2 – Issue ADD 2 a - Issue Busy Op Vj Vk Qj Qk Addr Add 1 1 ADD 5 1 Add 2 0 ADD 100 8 Add 3 1 ADD 1 Load 2 Br 1 1 BNE 10 Add 1 Load 1 0 LD 100 Load 2 1 LD 108 0 1 SD 100 Br 2 Load 3 Store 1 Store 2 Add 1 100

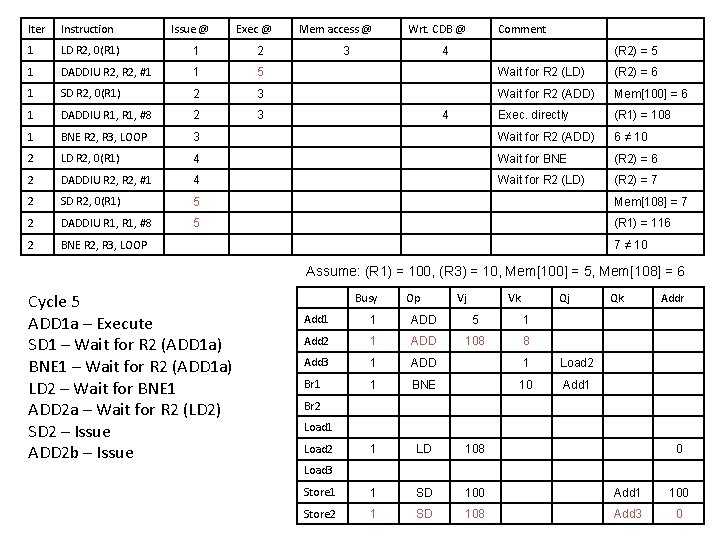

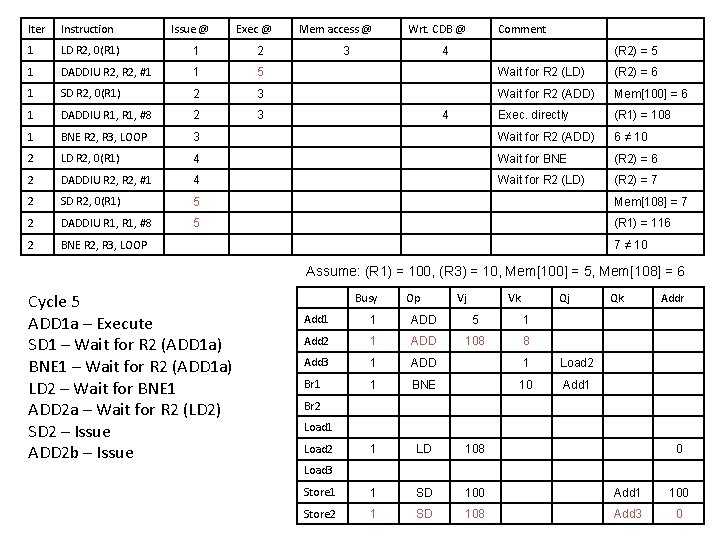

Iter Instruction Issue @ Exec @ Mem access @ Wrt. CDB @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 Wait for R 2 (LD) (R 2) = 6 1 SD R 2, 0(R 1) 2 3 Wait for R 2 (ADD) Mem[100] = 6 1 DADDIU R 1, #8 2 3 Exec. directly (R 1) = 108 1 BNE R 2, R 3, LOOP 3 Wait for R 2 (ADD) 6 ≠ 10 2 LD R 2, 0(R 1) 4 Wait for BNE (R 2) = 6 2 DADDIU R 2, #1 4 Wait for R 2 (LD) (R 2) = 7 2 SD R 2, 0(R 1) 5 Mem[108] = 7 2 DADDIU R 1, #8 5 (R 1) = 116 2 BNE R 2, R 3, LOOP 3 Comment 4 (R 2) = 5 4 7 ≠ 10 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 5 ADD 1 a – Execute SD 1 – Wait for R 2 (ADD 1 a) BNE 1 – Wait for R 2 (ADD 1 a) LD 2 – Wait for BNE 1 ADD 2 a – Wait for R 2 (LD 2) SD 2 – Issue ADD 2 b – Issue Busy Op Vj Vk Qj Qk Addr Add 1 1 ADD 5 1 Add 2 1 ADD 108 8 Add 3 1 ADD 1 Load 2 Br 1 1 BNE 10 Add 1 1 LD 108 Store 1 1 SD 100 Add 1 100 Store 2 1 SD 108 Add 3 0 Br 2 Load 1 Load 2 0 Load 3

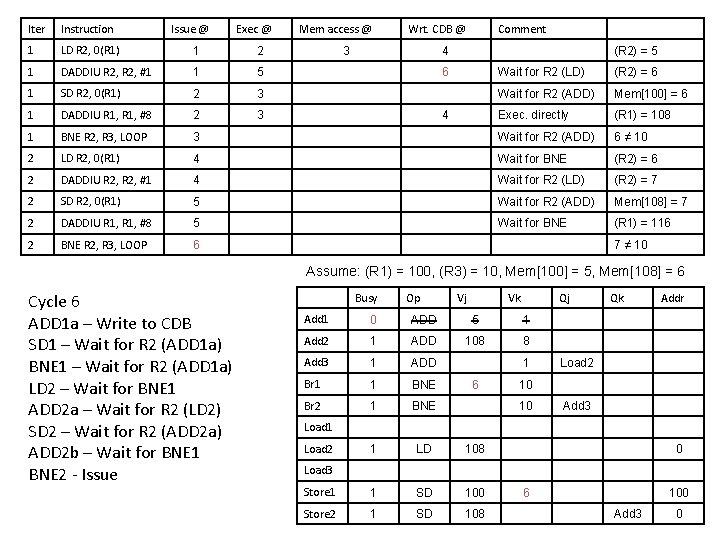

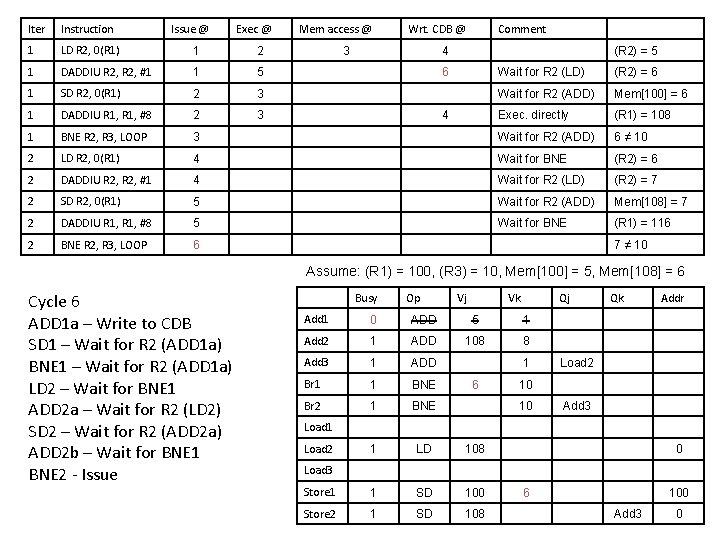

Iter Instruction Issue @ Exec @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 2 Mem access @ Wrt. CDB @ 3 Comment 4 (R 2) = 5 6 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 3 Wait for R 2 (ADD) 6 ≠ 10 LD R 2, 0(R 1) 4 Wait for BNE (R 2) = 6 2 DADDIU R 2, #1 4 Wait for R 2 (LD) (R 2) = 7 2 SD R 2, 0(R 1) 5 Wait for R 2 (ADD) Mem[108] = 7 2 DADDIU R 1, #8 5 Wait for BNE (R 1) = 116 2 BNE R 2, R 3, LOOP 6 4 7 ≠ 10 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 6 ADD 1 a – Write to CDB SD 1 – Wait for R 2 (ADD 1 a) BNE 1 – Wait for R 2 (ADD 1 a) LD 2 – Wait for BNE 1 ADD 2 a – Wait for R 2 (LD 2) SD 2 – Wait for R 2 (ADD 2 a) ADD 2 b – Wait for BNE 1 BNE 2 - Issue Busy Op Vj Vk Qj Add 1 0 ADD 5 1 Add 2 1 ADD 108 8 Add 3 1 ADD Br 1 1 BNE Br 2 1 BNE 1 LD 108 Store 1 1 SD 100 Store 2 1 SD 108 1 6 Qk Addr Load 2 10 10 Add 3 Load 1 Load 2 0 Load 3 6 100 Add 3 0

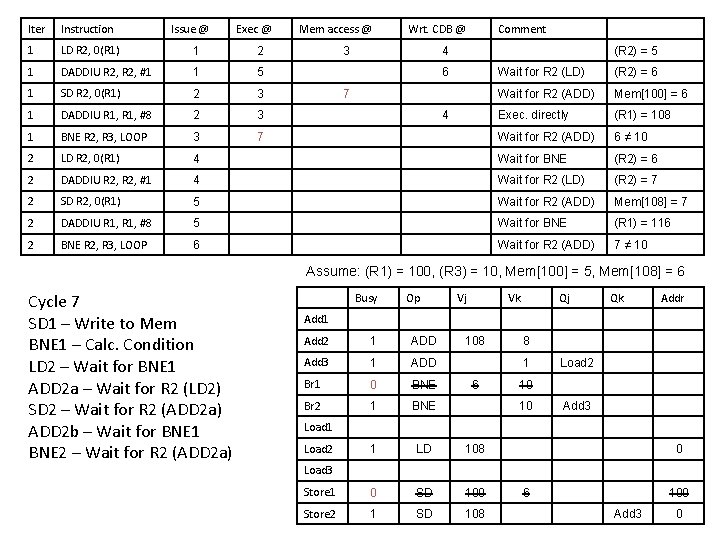

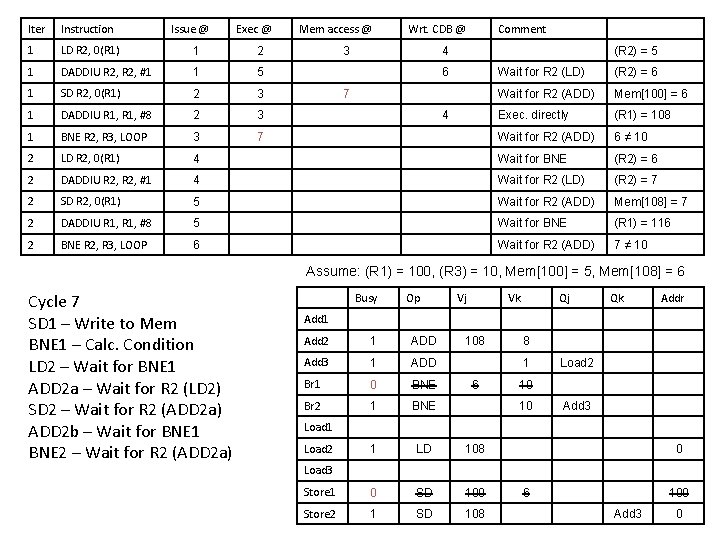

Iter Instruction Issue @ Exec @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 3 7 2 LD R 2, 0(R 1) 2 Mem access @ Wrt. CDB @ 3 Comment 4 (R 2) = 5 6 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 Wait for R 2 (ADD) 6 ≠ 10 4 Wait for BNE (R 2) = 6 DADDIU R 2, #1 4 Wait for R 2 (LD) (R 2) = 7 2 SD R 2, 0(R 1) 5 Wait for R 2 (ADD) Mem[108] = 7 2 DADDIU R 1, #8 5 Wait for BNE (R 1) = 116 2 BNE R 2, R 3, LOOP 6 Wait for R 2 (ADD) 7 ≠ 10 7 4 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 7 SD 1 – Write to Mem BNE 1 – Calc. Condition LD 2 – Wait for BNE 1 ADD 2 a – Wait for R 2 (LD 2) SD 2 – Wait for R 2 (ADD 2 a) ADD 2 b – Wait for BNE 1 BNE 2 – Wait for R 2 (ADD 2 a) Busy Op Vj Vk Qj Qk Addr Add 1 Add 2 1 ADD Add 3 1 ADD Br 1 0 BNE Br 2 1 BNE 1 LD 108 Store 1 0 SD 100 Store 2 1 SD 108 8 1 6 Load 2 10 10 Add 3 Load 1 Load 2 0 Load 3 6 100 Add 3 0

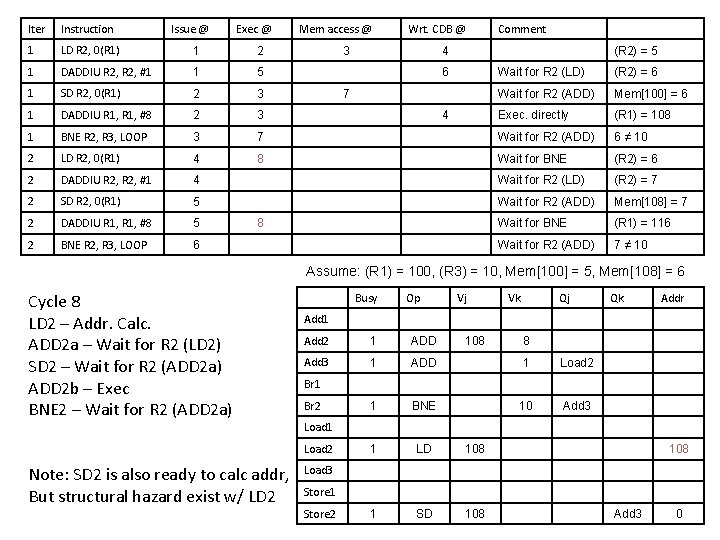

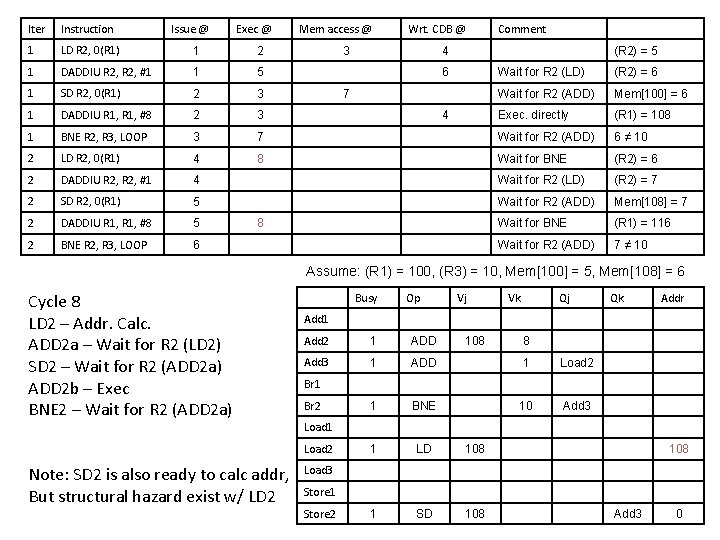

Iter Instruction Issue @ Exec @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 3 2 LD R 2, 0(R 1) 4 2 DADDIU R 2, #1 2 Mem access @ Wrt. CDB @ 3 Comment 4 (R 2) = 5 6 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 7 Wait for R 2 (ADD) 6 ≠ 10 8 Wait for BNE (R 2) = 6 4 Wait for R 2 (LD) (R 2) = 7 SD R 2, 0(R 1) 5 Wait for R 2 (ADD) Mem[108] = 7 2 DADDIU R 1, #8 5 Wait for BNE (R 1) = 116 2 BNE R 2, R 3, LOOP 6 Wait for R 2 (ADD) 7 ≠ 10 7 4 8 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 8 LD 2 – Addr. Calc. ADD 2 a – Wait for R 2 (LD 2) SD 2 – Wait for R 2 (ADD 2 a) ADD 2 b – Exec BNE 2 – Wait for R 2 (ADD 2 a) Busy Vj Vk Qj Qk Addr Add 1 Add 2 1 ADD Add 3 1 ADD 1 Load 2 1 BNE 10 Add 3 1 LD 108 1 SD 108 8 Br 1 Br 2 Load 1 Load 2 Note: SD 2 is also ready to calc addr, But structural hazard exist w/ LD 2 Op 108 Load 3 Store 1 Store 2 Add 3 0

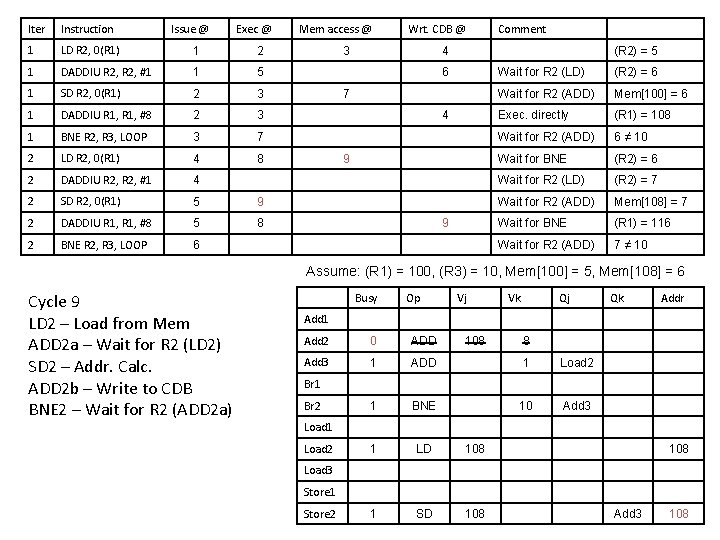

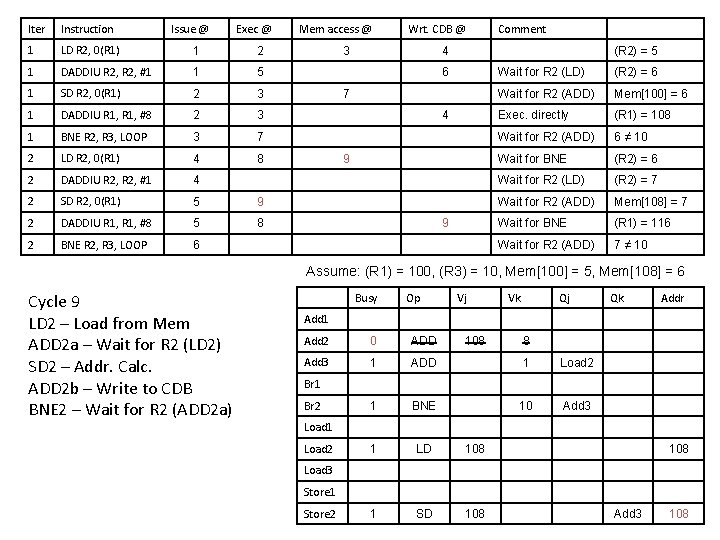

Iter Instruction Issue @ Exec @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 3 7 2 LD R 2, 0(R 1) 4 8 2 DADDIU R 2, #1 4 2 SD R 2, 0(R 1) 5 9 2 DADDIU R 1, #8 5 8 2 BNE R 2, R 3, LOOP 6 Mem access @ Wrt. CDB @ 3 Comment 4 (R 2) = 5 6 7 4 9 9 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 Wait for R 2 (ADD) 6 ≠ 10 Wait for BNE (R 2) = 6 Wait for R 2 (LD) (R 2) = 7 Wait for R 2 (ADD) Mem[108] = 7 Wait for BNE (R 1) = 116 Wait for R 2 (ADD) 7 ≠ 10 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 9 LD 2 – Load from Mem ADD 2 a – Wait for R 2 (LD 2) SD 2 – Addr. Calc. ADD 2 b – Write to CDB BNE 2 – Wait for R 2 (ADD 2 a) Busy Op Vj Vk Qj Qk Addr Add 1 Add 2 0 ADD Add 3 1 ADD 1 Load 2 1 BNE 10 Add 3 1 LD 108 1 SD 108 8 Br 1 Br 2 Load 1 Load 2 108 Load 3 Store 1 Store 2 Add 3 108

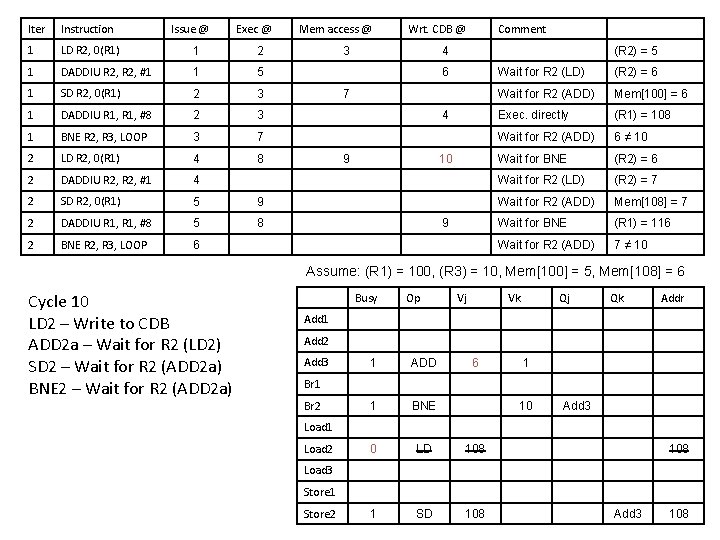

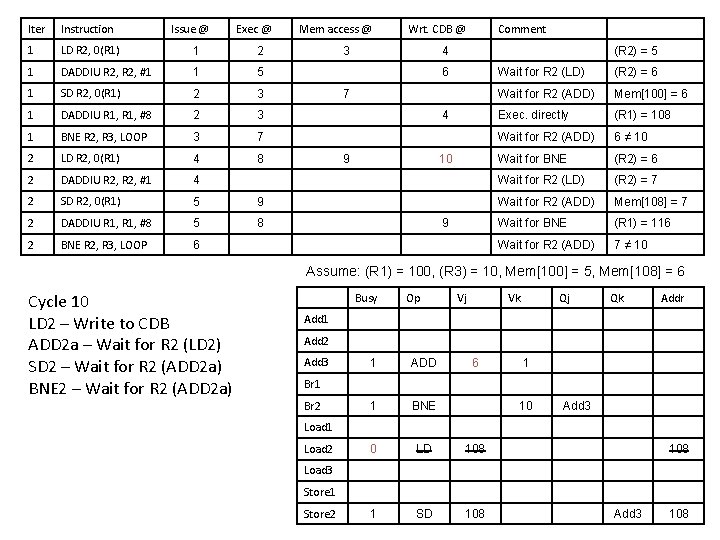

Iter Instruction Issue @ Exec @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 3 7 2 LD R 2, 0(R 1) 4 8 2 DADDIU R 2, #1 4 2 SD R 2, 0(R 1) 5 9 2 DADDIU R 1, #8 5 8 2 BNE R 2, R 3, LOOP 6 Mem access @ Wrt. CDB @ 3 Comment 4 (R 2) = 5 6 7 4 9 10 9 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 Wait for R 2 (ADD) 6 ≠ 10 Wait for BNE (R 2) = 6 Wait for R 2 (LD) (R 2) = 7 Wait for R 2 (ADD) Mem[108] = 7 Wait for BNE (R 1) = 116 Wait for R 2 (ADD) 7 ≠ 10 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 10 LD 2 – Write to CDB ADD 2 a – Wait for R 2 (LD 2) SD 2 – Wait for R 2 (ADD 2 a) BNE 2 – Wait for R 2 (ADD 2 a) Busy Op Vj Vk Qj Qk Addr Add 1 Add 2 Add 3 1 ADD 6 1 BNE 0 LD 108 1 SD 108 1 Br 2 10 Add 3 Load 1 Load 2 108 Load 3 Store 1 Store 2 Add 3 108

Iter Instruction Issue @ Exec @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 3 7 2 LD R 2, 0(R 1) 4 8 2 DADDIU R 2, #1 4 2 SD R 2, 0(R 1) 2 2 Mem access @ Wrt. CDB @ 3 Comment 4 (R 2) = 5 6 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 Wait for R 2 (ADD) 6 ≠ 10 Wait for BNE (R 2) = 6 11 Wait for R 2 (LD) (R 2) = 7 5 9 Wait for R 2 (ADD) Mem[108] = 7 DADDIU R 1, #8 5 8 Wait for BNE (R 1) = 116 BNE R 2, R 3, LOOP 6 Wait for R 2 (ADD) 7 ≠ 10 7 4 9 10 9 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 11 ADD 2 a – Exec SD 2 – Wait for R 2 (ADD 2 a) BNE 2 – Wait for R 2 (ADD 2 a) Busy Op Vj Vk Qj Qk Addr Add 1 Add 2 Add 3 1 ADD 1 BNE 1 SD 6 1 Br 2 10 Add 3 Load 1 Load 2 Load 3 Store 1 Store 2 108 Add 3 108

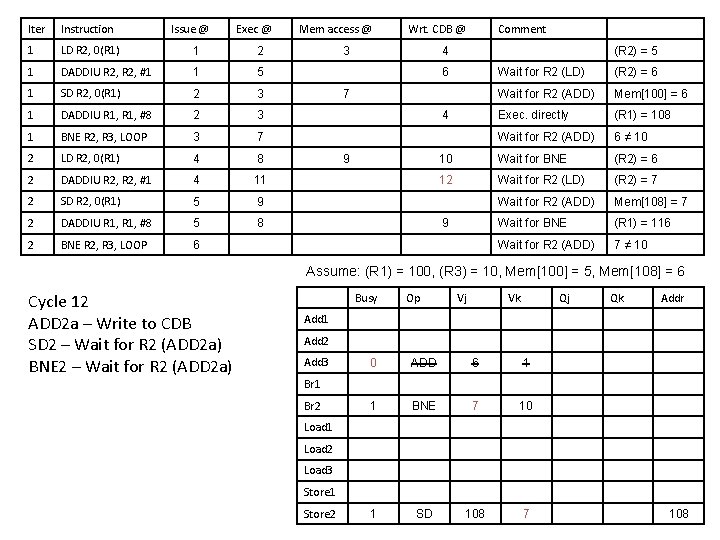

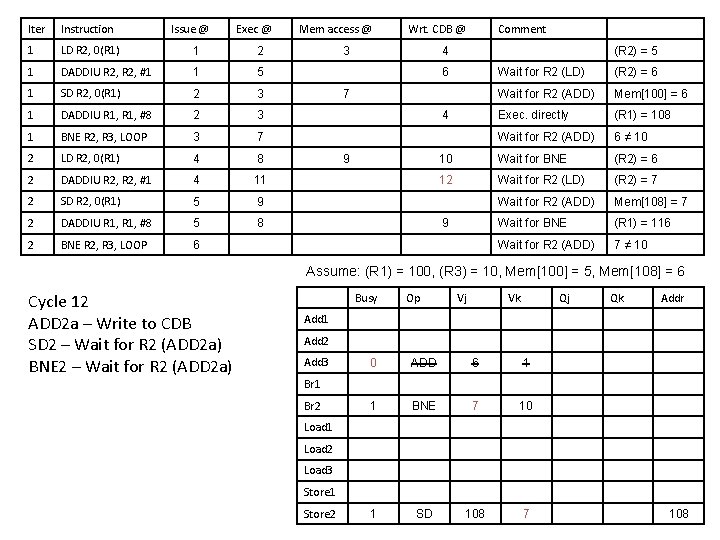

Iter Instruction Issue @ Exec @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 3 7 2 LD R 2, 0(R 1) 4 8 2 DADDIU R 2, #1 4 11 2 SD R 2, 0(R 1) 5 9 2 DADDIU R 1, #8 5 8 2 BNE R 2, R 3, LOOP 6 Mem access @ Wrt. CDB @ 3 Comment 4 (R 2) = 5 6 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 Wait for R 2 (ADD) 6 ≠ 10 10 Wait for BNE (R 2) = 6 12 Wait for R 2 (LD) (R 2) = 7 Wait for R 2 (ADD) Mem[108] = 7 Wait for BNE (R 1) = 116 Wait for R 2 (ADD) 7 ≠ 10 7 4 9 9 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 12 ADD 2 a – Write to CDB SD 2 – Wait for R 2 (ADD 2 a) BNE 2 – Wait for R 2 (ADD 2 a) Busy Op Vj Vk Qj Qk Addr Add 1 Add 2 Add 3 0 ADD 6 1 1 BNE 7 10 1 SD 108 7 Br 1 Br 2 Load 1 Load 2 Load 3 Store 1 Store 2 108

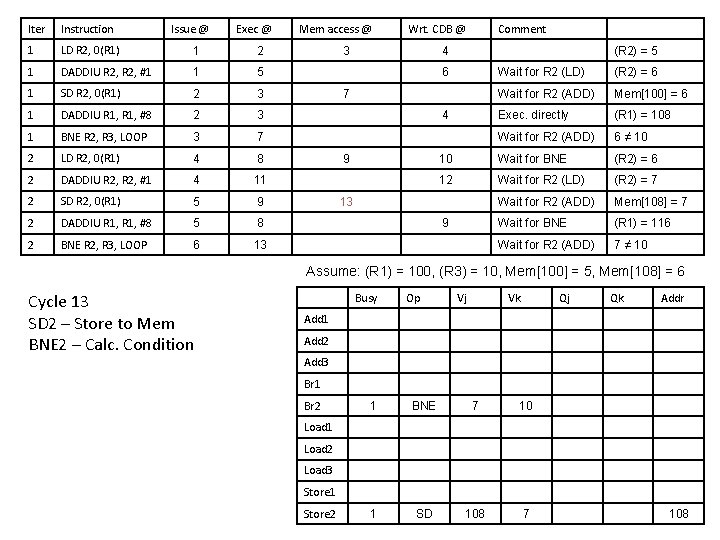

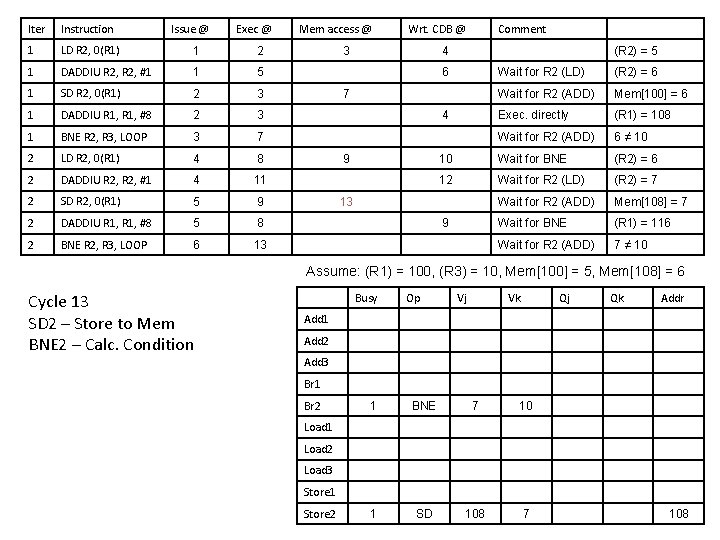

Iter Instruction Issue @ Exec @ 1 LD R 2, 0(R 1) 1 2 1 DADDIU R 2, #1 1 5 1 SD R 2, 0(R 1) 2 3 1 DADDIU R 1, #8 2 3 1 BNE R 2, R 3, LOOP 3 7 2 LD R 2, 0(R 1) 4 8 2 DADDIU R 2, #1 4 11 2 SD R 2, 0(R 1) 5 9 2 DADDIU R 1, #8 5 8 2 BNE R 2, R 3, LOOP 6 13 Mem access @ Wrt. CDB @ 3 Comment 4 (R 2) = 5 6 Wait for R 2 (LD) (R 2) = 6 Wait for R 2 (ADD) Mem[100] = 6 Exec. directly (R 1) = 108 Wait for R 2 (ADD) 6 ≠ 10 10 Wait for BNE (R 2) = 6 12 Wait for R 2 (LD) (R 2) = 7 Wait for R 2 (ADD) Mem[108] = 7 Wait for BNE (R 1) = 116 Wait for R 2 (ADD) 7 ≠ 10 7 4 9 13 9 Assume: (R 1) = 100, (R 3) = 10, Mem[100] = 5, Mem[108] = 6 Cycle 13 SD 2 – Store to Mem BNE 2 – Calc. Condition Busy Op Vj Vk Qj Qk Addr Add 1 Add 2 Add 3 Br 1 Br 2 1 BNE 7 10 1 SD 108 7 Load 1 Load 2 Load 3 Store 1 Store 2 108