To Generate a Single Test Vector to detect

- Slides: 9

To Generate a Single Test Vector to detect all/most number of faults in a given set Project by: Arvind Raghuraman Course Project ELEC 7250 4/28/05 Raghuraman: ELEC 7250 1

Problem Statement l The Objective of the project is to determine a test vector that could detect all/most number of faults in a given set. l As a suggested improvement investigation was done on extending the algorithm developed for test set compaction. 4/28/05 Raghuraman: ELEC 7250 2

Background work Major Combinational ATPG Algorithms: • D-Algorithm (Roth) -- 1966 • PODEM (Goel) – 1981 Advanced ATPG Algorithms: • • FAN – Multiple Backtrace (1983) TOPS – Dominators (1987) SOCRATES – Learning (1988) Legal Assignments (1990) EST – Search space learning (1991) BDD Test generation (1991) Implication Graphs and Transitive Closure (1988 - 97) Recursive Learning (1995) 4/28/05 Raghuraman: ELEC 7250 3

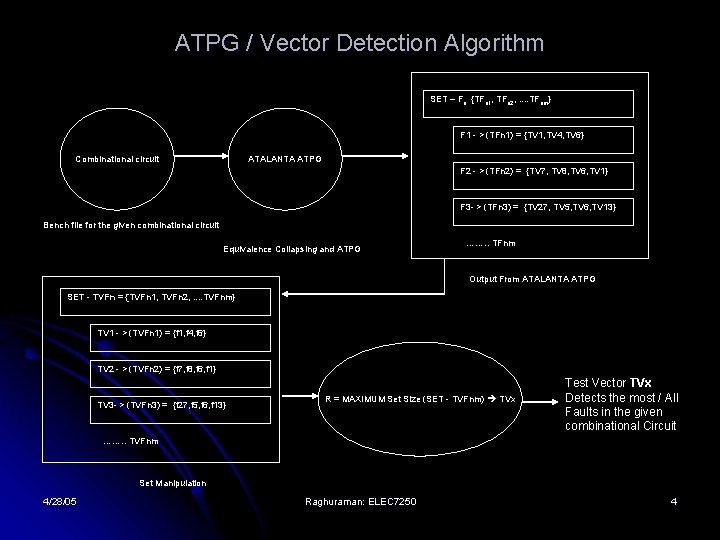

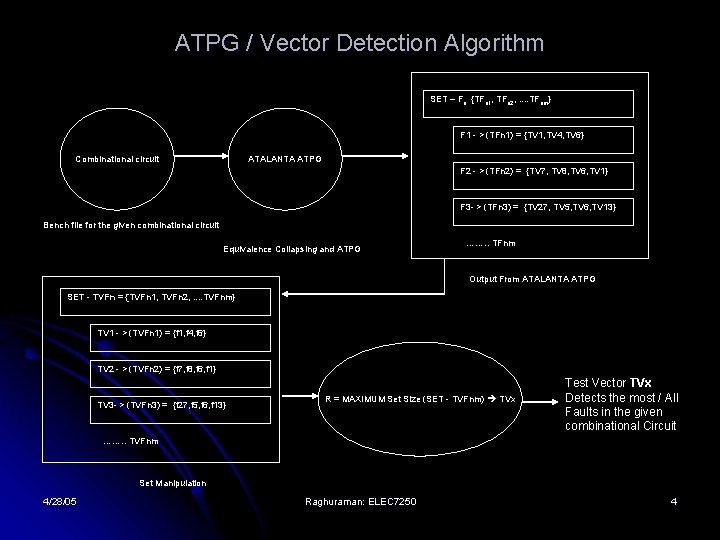

ATPG / Vector Detection Algorithm SET – Fn {TFn 1, TFn 2, . . TFnm} F 1 - > (TFn 1) = {TV 1, TV 4, TV 6} Combinational circuit ATALANTA ATPG F 2 - > (TFn 2) = {TV 7, TV 8, TV 6, TV 1} F 3 - > (TFn 3) = {TV 27, TV 5, TV 6, TV 13} Bench file for the given combinational circuit Equivalence Collapsing and ATPG ……. . TFnm Output From ATALANTA ATPG SET - TVFn = {TVFn 1, TVFn 2, . . TVFnm} TV 1 - > (TVFn 1) = {f 1, f 4, f 6} TV 2 - > (TVFn 2) = {f 7, f 8, f 6, f 1} TV 3 - > (TVFn 3) = {f 27, f 5, f 6, f 13} R = MAXIMUM Set Size (SET - TVFnm) TVx Test Vector TVx Detects the most / All Faults in the given combinational Circuit ……. . TVFnm Set Manipulation 4/28/05 Raghuraman: ELEC 7250 4

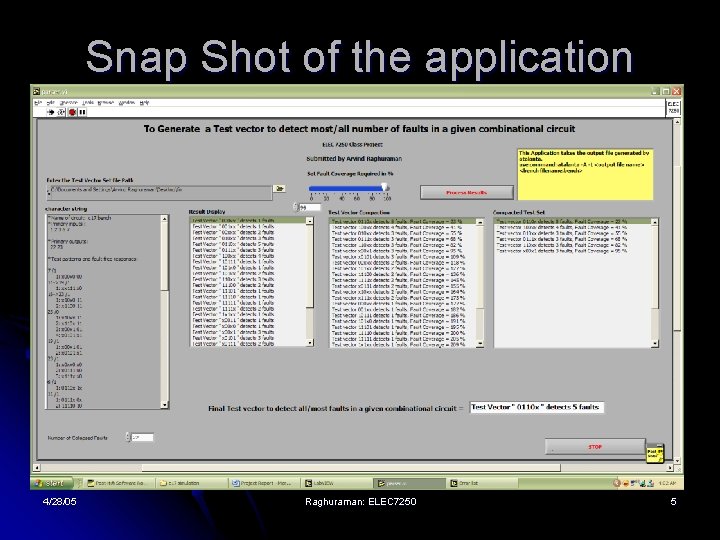

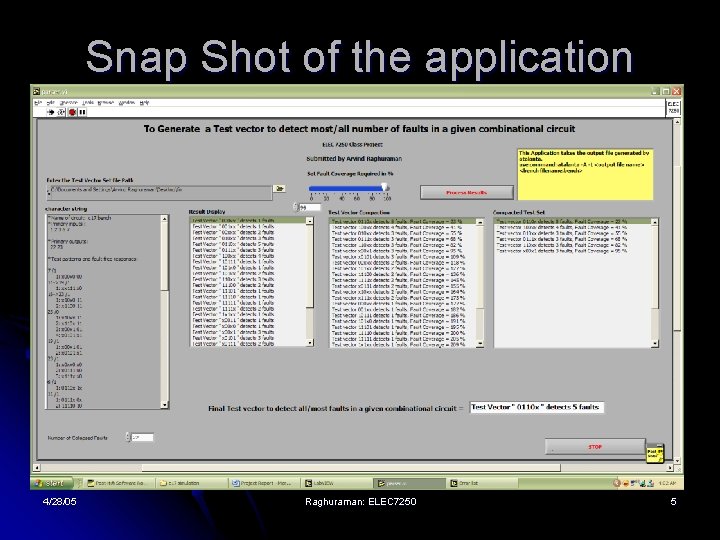

Snap Shot of the application 4/28/05 Raghuraman: ELEC 7250 5

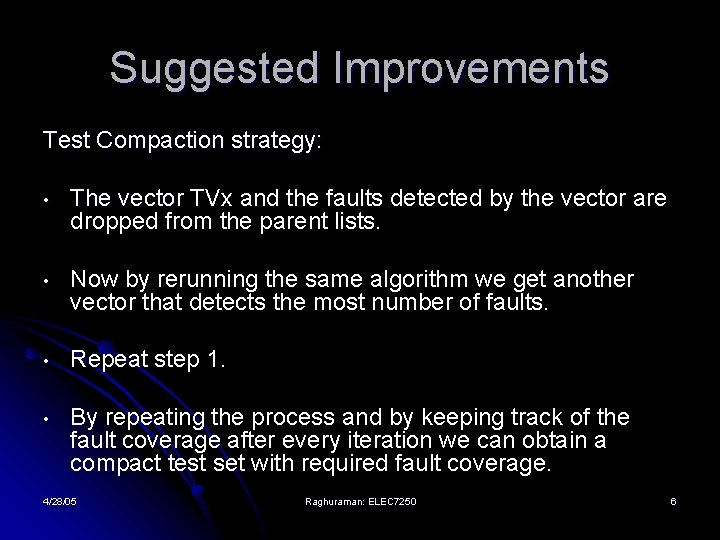

Suggested Improvements Test Compaction strategy: • The vector TVx and the faults detected by the vector are dropped from the parent lists. • Now by rerunning the same algorithm we get another vector that detects the most number of faults. • Repeat step 1. • By repeating the process and by keeping track of the fault coverage after every iteration we can obtain a compact test set with required fault coverage. 4/28/05 Raghuraman: ELEC 7250 6

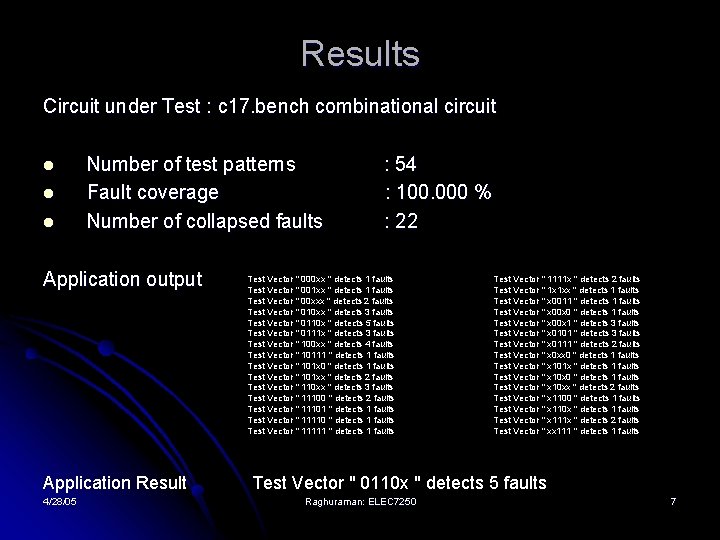

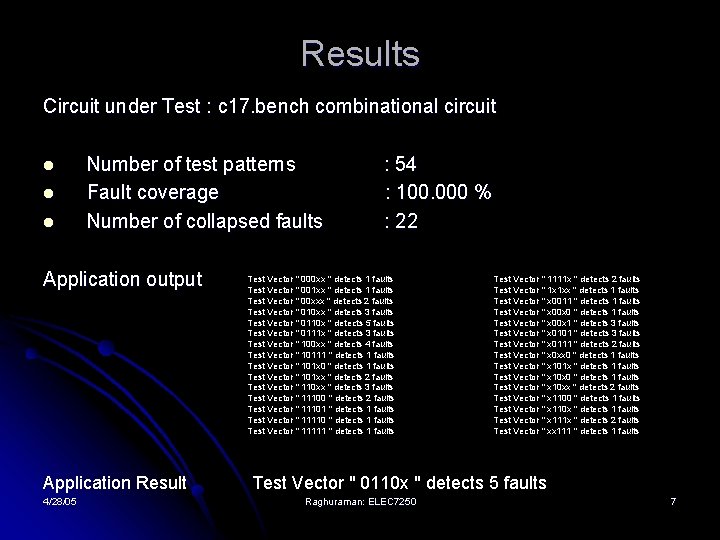

Results Circuit under Test : c 17. bench combinational circuit l l l Number of test patterns Fault coverage Number of collapsed faults Application output Application Result 4/28/05 : 54 : 100. 000 % : 22 Test Vector " 000 xx " detects 1 faults Test Vector " 001 xx " detects 1 faults Test Vector " 00 xxx " detects 2 faults Test Vector " 010 xx " detects 3 faults Test Vector " 0110 x " detects 5 faults Test Vector " 0111 x " detects 3 faults Test Vector " 100 xx " detects 4 faults Test Vector " 10111 " detects 1 faults Test Vector " 101 x 0 " detects 1 faults Test Vector " 101 xx " detects 2 faults Test Vector " 110 xx " detects 3 faults Test Vector " 11100 " detects 2 faults Test Vector " 11101 " detects 1 faults Test Vector " 11110 " detects 1 faults Test Vector " 11111 " detects 1 faults Test Vector " 1111 x " detects 2 faults Test Vector " 1 x 1 xx " detects 1 faults Test Vector " x 0011 " detects 1 faults Test Vector " x 00 x 0 " detects 1 faults Test Vector " x 00 x 1 " detects 3 faults Test Vector " x 0101 " detects 3 faults Test Vector " x 0111 " detects 2 faults Test Vector " x 0 xx 0 " detects 1 faults Test Vector " x 101 x " detects 1 faults Test Vector " x 10 x 0 " detects 1 faults Test Vector " x 10 xx " detects 2 faults Test Vector " x 1100 " detects 1 faults Test Vector " x 110 x " detects 1 faults Test Vector " x 111 x " detects 2 faults Test Vector " xx 111 " detects 1 faults Test Vector " 0110 x " detects 5 faults Raghuraman: ELEC 7250 7

Conclusion l l l The Application developed correctly identifies the test vector of interest. The proposed strategy for test compaction should be tested on other circuits and its performance should be ascertained. The Application can be used as a Generic Tool for any combinational circuits, it can directly accept the output file from ATALANTA and generate the test vector of interest. 4/28/05 Raghuraman: ELEC 7250 8

References l Class Lecture Notes ELEC 7250 l Essentials of Electronic Testing, Michael L. Bushnell, Vishwani D. Agarwal 4/28/05 Raghuraman: ELEC 7250 9