Tng quan v nhng u th MSP 430

- Slides: 35

Tổng quan và những ưu thế MSP 430 1. Tổng quan về VĐK họ MSP 430 2. Ưu thế của MSP 430

Tổng quan về MSP 430 là họ vi điều khiển cấu trúc RISC 16 -bit được sản xuất bởi công ty Texas Instruments (Mỹ). MSP là viết tắt của “ MIXED SIGNAL MICROCONTROLER”. Là dòng vi điều khiển siêu tiết kiệm năng lượng , sử dụng nguồn thấp, khoảng điện áp nguồn cấp từ 1. 8 V-3. 6 V. Chip MSP 430 là giải pháp thích hợp cho những ứng dụng yêu cầu trộn tín hiệu>

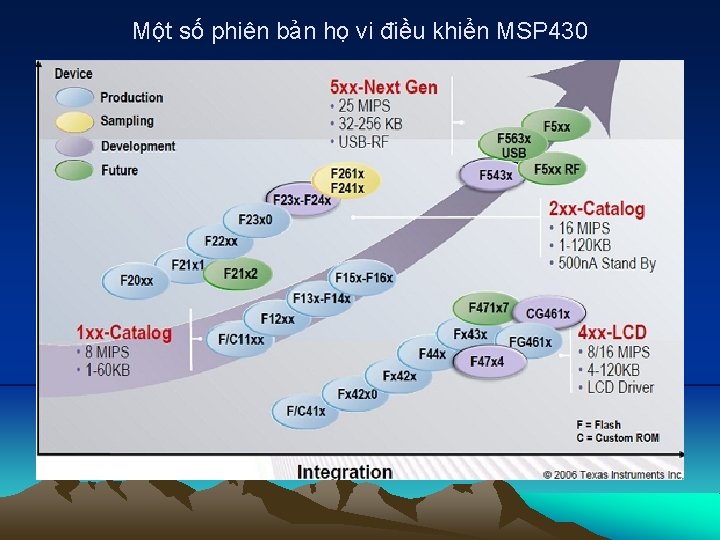

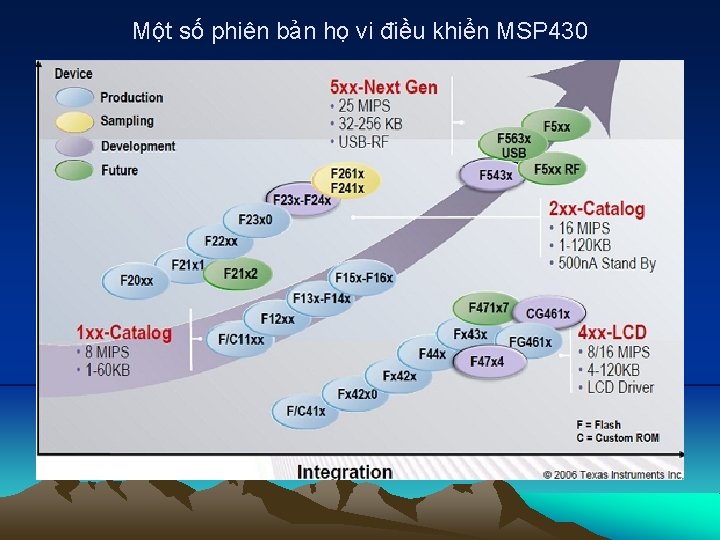

Tổng quan về MSP 430 • MSP 430 chứa 16 bit RISC CPU, các ngoại vi và hệ thống bộ định thời linh hoạt được kết nối với nhau theo cấu trúc VON-NEUMANN, có các Bus liên kết như: Bus địa chỉ bộ nhớ ( MAB), Bus dữ liệu bộ nhớ ( MDB). Đây là một bộ xử lý hiện đại với các mô đun bộ nhớ tương tự và nhứng kết nối ngoại vi tín hiệu số, MSP 430 đã đưa ra được những giải pháp tốt cho những nhu cầu ứng dụng với tín hiệu hỗn tạp. MSP 430 có một số phiên bản như: MSP 430 x 1 xx, MSP 430 x 2 xx, MSP 430 x 3 xx, MSP 430 x 4 xx, MSP 430 x 5 xx.

Một số phiên bản họ vi điều khiển MSP 430

Tổng quan về MSP 430 Dưới đây là những đặc điểm tổng quát của họ vi điều khiển MSP 430: + Cấu trúc sử dụng nguồn thấp giúp kéo dài tuổi thọ của Pin - Duy trì 0. 1μA dòng nuôi RAM. - Chỉ 0. 8μA real- time clock. - 250 μA/ MIPS. + Bộ tương tự hiệu suất cao cho các phép đo chính xác - 12 bit hoặc 10 bit ADC-200 kskp, cảm biến nhiệt độ, Vref. - 12 bit DAC. - Bộ giám sát điện áp nguồn.

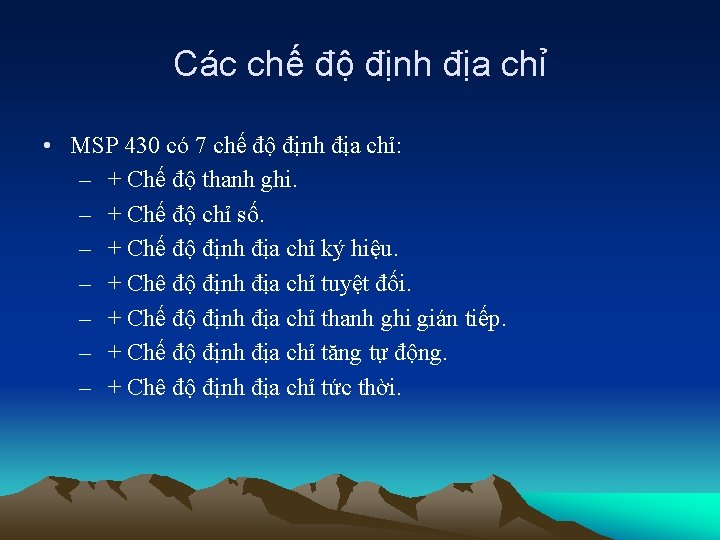

Tổng quan về MSP 430 + 16 bit RISC CPU cho phép được nhiều ứng dụng, thể hiện một phần ở kích thước Code lập trình. - Thanh ghi lớn nên loại trừ được trường hợp tắt nghẽn tập tin khi đang làm việc. - Thiết kế nhỏ gọn làm giảm lượng tiêu thụ điện và giảm giá thành. - Có 7 chế độ định địa chỉ. - Khả năng ngắt theo véc tơ lớn. + Trong lập trình cho bộ nhớ Flash cho phép thay đổi Code một cách linh hoạt, phạm vi rộng, bộ nhớ Flash còn có thể lưu lại như nhật ký của dữ liệu.

Ưu thế của MSP 430 • Công nghệ CMOS tiêu thụ năng lượng thấp, nguồn nuôi RAM 0. 1 -m. A, 0. 8 -m. A Tiêu chuẩn Analog cho phép đo chính xác • Bộ so sánh điện áp thấp, có khả năng kết nối với thiết bị ngoại vi cực kỳ thông minh. Tiêu chuẩn Analog cho phép đo chính xác.

Ưu thế của MSP 430 • Bộ giám sát điện áp 16 -bit RISC CPU cho phép ứng dụng mới tại một phần nhỏ của kích thước mã. • Hệ thống lập trình Flash bên trong cho phép thay đổi mã mềm dẻo. • Bộ định thời cảnh giới (WDT). Có chức năng là thực hiện khởi động lại hệ thống sau khi xuất hiện vấn đề ở phần mềm.

TÌM HIỂU VỀ KIT LAUCHPAD MSP 430

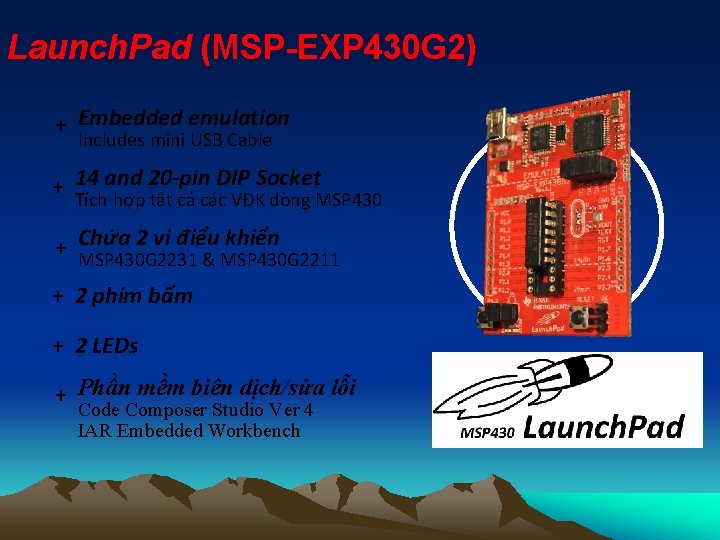

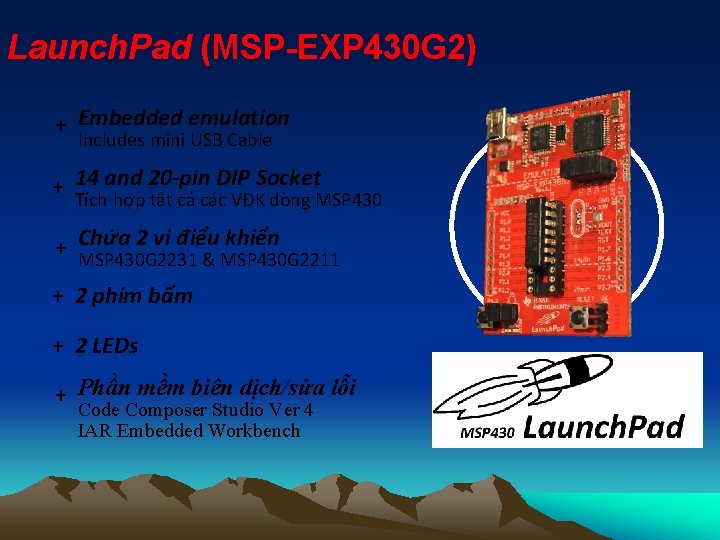

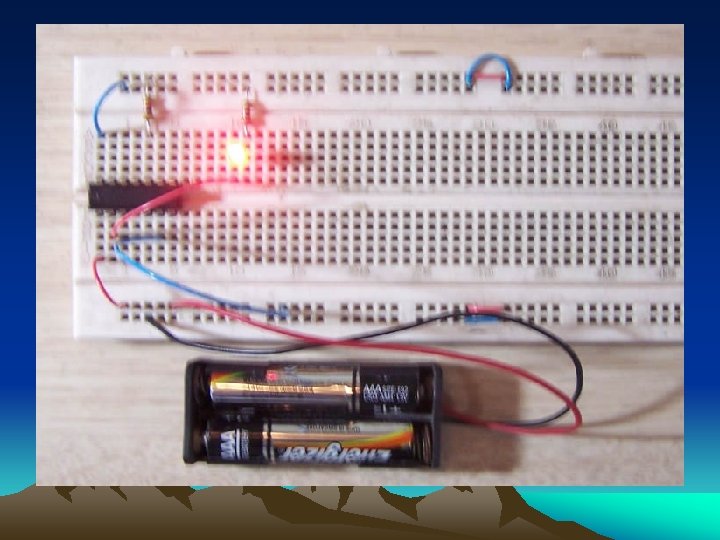

Launch. Pad (MSP-EXP 430 G 2) + Embedded emulation Includes mini USB Cable + 14 and 20 -pin DIP Socket Tích hợp tất cả các VĐK dòng MSP 430 2 vi điểu khiển + Chứa MSP 430 G 2231 & MSP 430 G 2211 + 2 phím bấm + 2 LEDs + Phần mềm biên dịch/sửa lỗi Code Composer Studio Ver 4 IAR Embedded Workbench

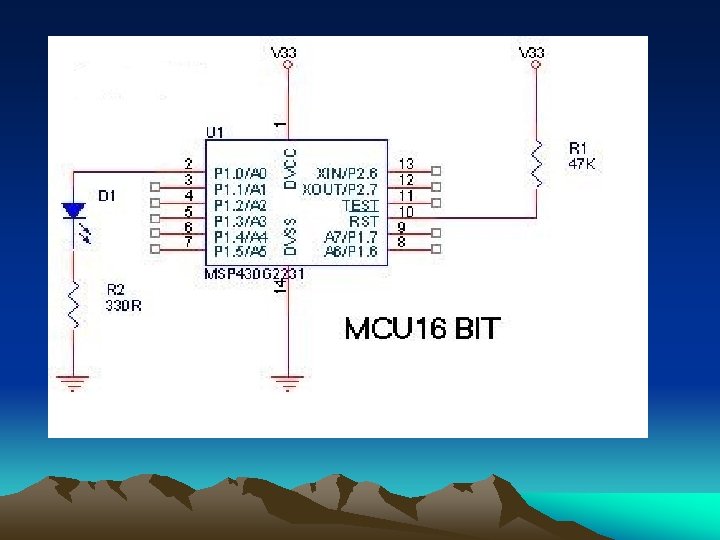

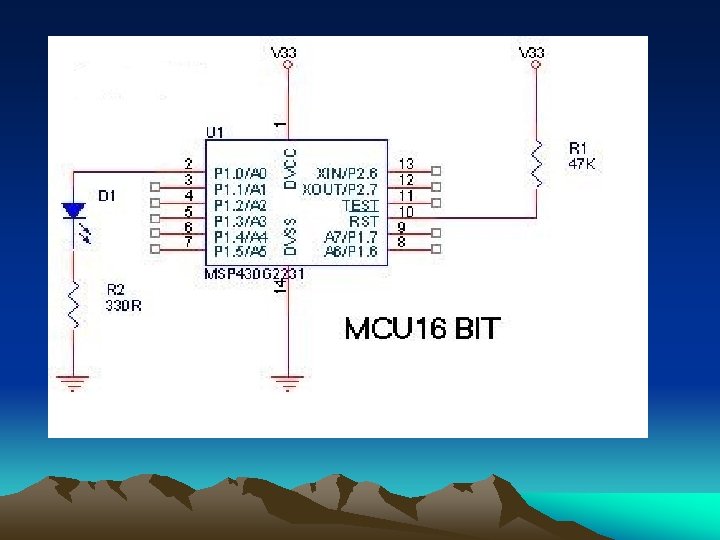

Vi điều khiển MSP 430 G 2231 là dòng vi điều khiển 16 bit Đặc trưng: Nguồn nuôi thấp từ 1. 8 đến 3. 3 V Tiết kiệm năng lượng Cấu trúc 16 bit RISC, chu ky lệnh 62. 5 ns Bộ nhớ chương trình 2 KB Flash Bộ nhớ RAM 128 byte Xung nhip tối đa 16 MHz 10 IO pin ADC 10 bit, tốc độ 200 ksps 01 Timer 16 bit( Timer A) Lập trình On. Board Với 51 lệnh

Ngôn ngữ lập trình (Language): Có thể lập trình hoạt động với ngôn ngữ Assemble và C. Trình biên dịch (Compiler): Hiện nay có rất nhiều chương trình biên dịch như: CCS hỗ trợ lập trình Assemble và C, IAR. Mạch nạp (Programmer): Các vi điều khiển dòng MSP 430 hỗ trợ chuẩn nạp serial. Mạch phát triển (Develope Board): Launch. Pad msp 430 G 2

Số chân vào ra: 14 Mỗi IO của MSP 430 được quản lý bởi các thanh ghi: Px. IN, Px. OUT, Px. DIR, Px. REN, Px. DS, Px. SEL. - Px. IN: thanh ghi ngõ vào, chứa giá trị logic tại các chân tương ứng khi nó được cấu hình là ngõ vào. - Px. OUT: thanh ghi ngõ ra, chứa giá trị logic ghi ra các chân tương ứng của port khi nó được cấu hình là ngõ ra, tắt điện trở kéo lên. - Px. DIR: thanh ghi chọn hướng, mỗi bit của thanh ghi Px. DIR cho phép chọn hướng cho từng chân I/O riêng lẻ tương ứng. Không phụ thuộc chức năng được chọn cho I/O - Px. REN: Thanh ghi cho phép điện trở kéo lên/kéo xuống, việc chọn kéo lên hay xuống là do thanh ghi Px. OUT quyết định.

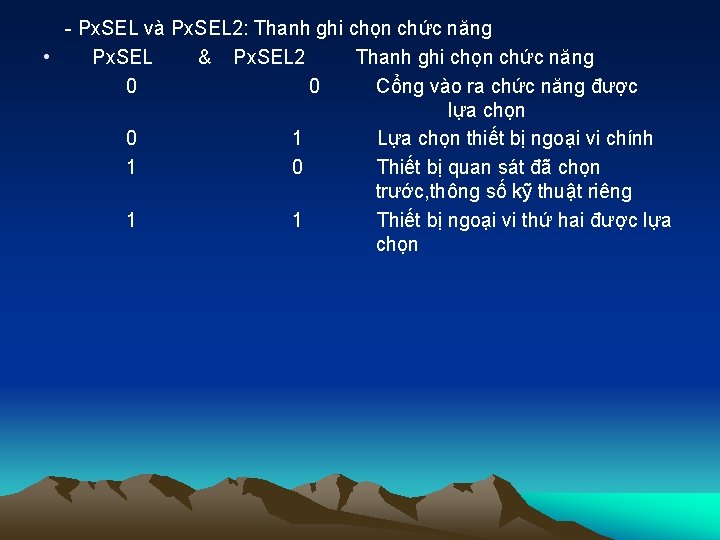

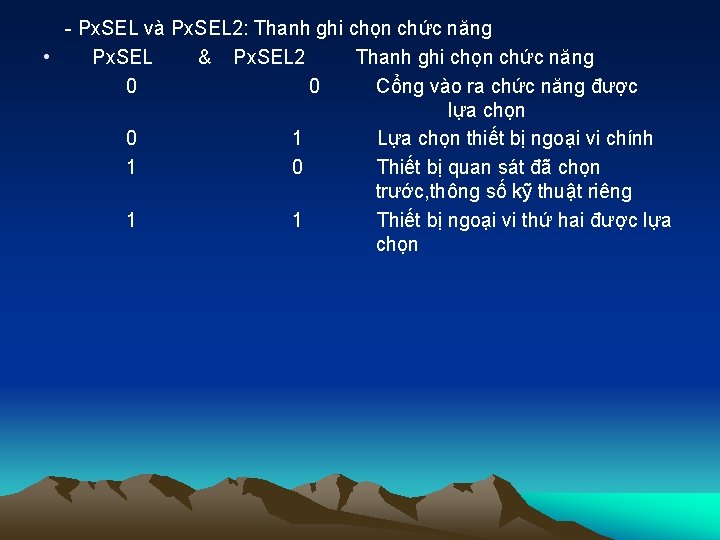

- Px. SEL và Px. SEL 2: Thanh ghi chọn chức năng • Px. SEL & Px. SEL 2 Thanh ghi chọn chức năng 0 0 Cổng vào ra chức năng được lựa chọn 0 1 Lựa chọn thiết bị ngoại vi chính 1 0 Thiết bị quan sát đã chọn trước, thông số kỹ thuật riêng 1 1 Thiết bị ngoại vi thứ hai được lựa chọn

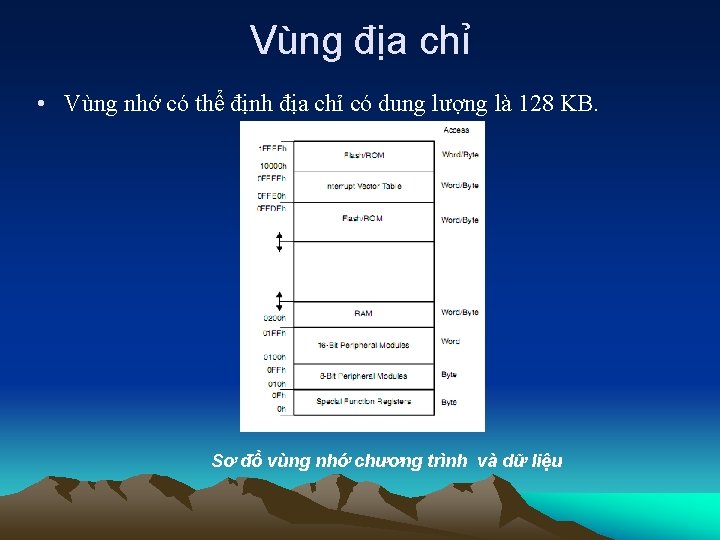

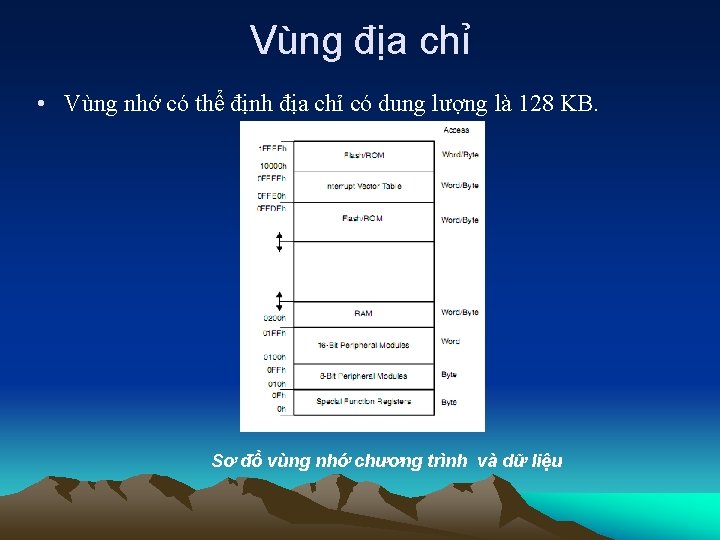

Vùng địa chỉ • Vùng nhớ có thể định địa chỉ có dung lượng là 128 KB. Sơ đồ vùng nhớ chương trình và dữ liệu

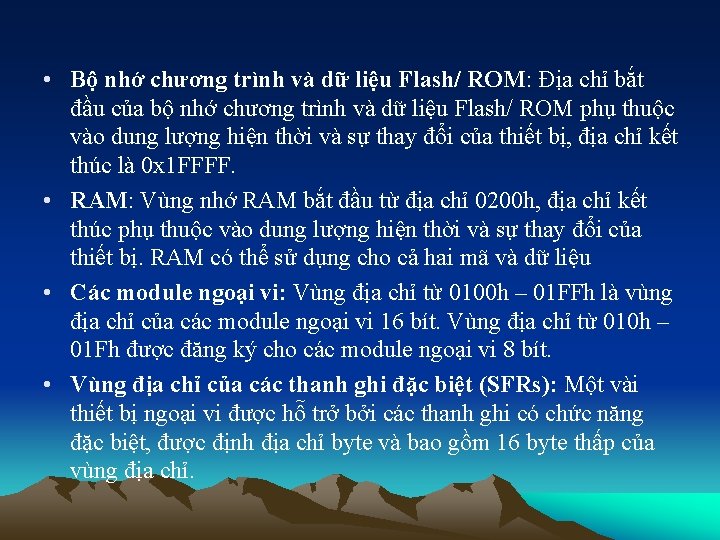

• Bộ nhớ chương trình và dữ liệu Flash/ ROM: Địa chỉ bắt đầu của bộ nhớ chương trình và dữ liệu Flash/ ROM phụ thuộc vào dung lượng hiện thời và sự thay đổi của thiết bị, địa chỉ kết thúc là 0 x 1 FFFF. • RAM: Vùng nhớ RAM bắt đầu từ địa chỉ 0200 h, địa chỉ kết thúc phụ thuộc vào dung lượng hiện thời và sự thay đổi của thiết bị. RAM có thể sử dụng cho cả hai mã và dữ liệu • Các module ngoại vi: Vùng địa chỉ từ 0100 h – 01 FFh là vùng địa chỉ của các module ngoại vi 16 bít. Vùng địa chỉ từ 010 h – 01 Fh được đăng ký cho các module ngoại vi 8 bít. • Vùng địa chỉ của các thanh ghi đặc biệt (SFRs): Một vài thiết bị ngoại vi được hỗ trở bởi các thanh ghi có chức năng đặc biệt, được định địa chỉ byte và bao gồm 16 byte thấp của vùng địa chỉ.

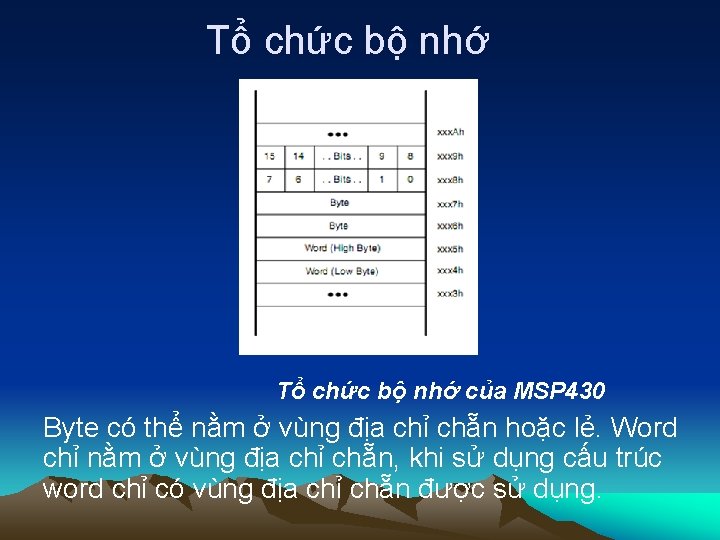

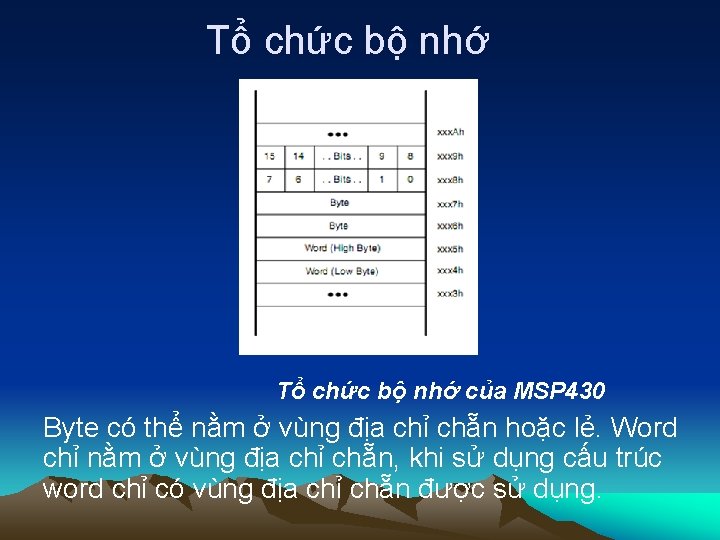

Tổ chức bộ nhớ của MSP 430 Byte có thể nằm ở vùng địa chỉ chẵn hoặc lẻ. Word chỉ nằm ở vùng địa chỉ chẵn, khi sử dụng cấu trúc word chỉ có vùng địa chỉ chẵn được sử dụng.

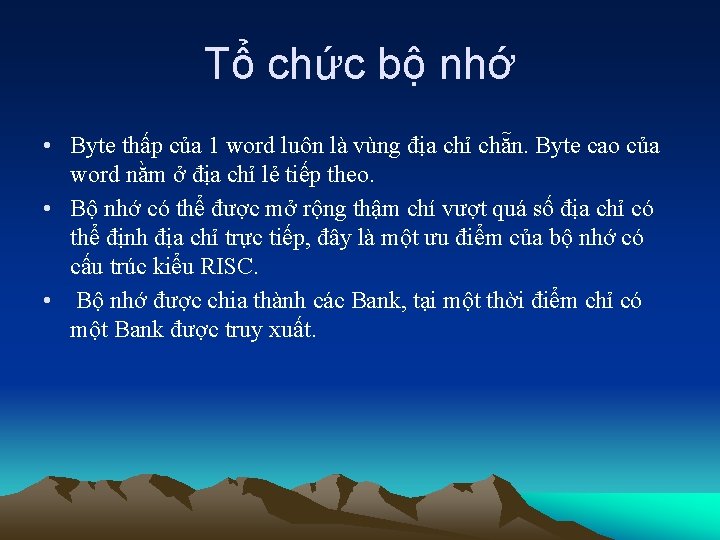

Tổ chức bộ nhớ • Byte thấp của 1 word luôn là vùng địa chỉ chẵn. Byte cao của word nằm ở địa chỉ lẻ tiếp theo. • Bộ nhớ có thể được mở rộng thậm chí vượt quá số địa chỉ có thể định địa chỉ trực tiếp, đây là một ưu điểm của bộ nhớ có cấu trúc kiểu RISC. • Bộ nhớ được chia thành các Bank, tại một thời điểm chỉ có một Bank được truy xuất.

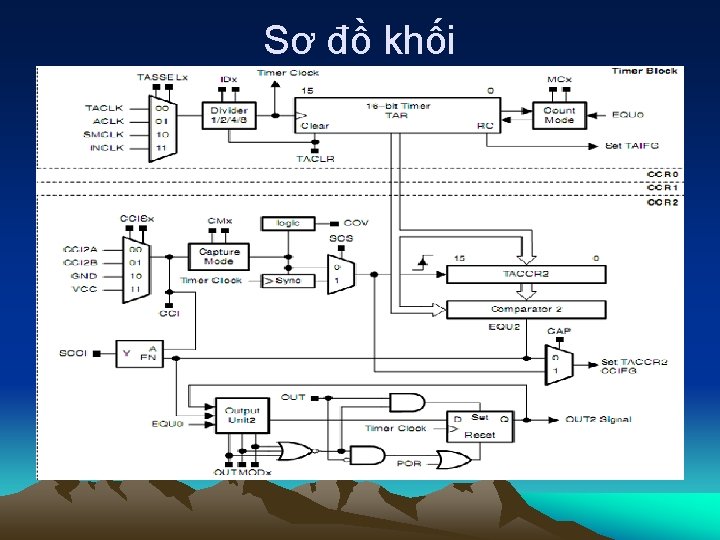

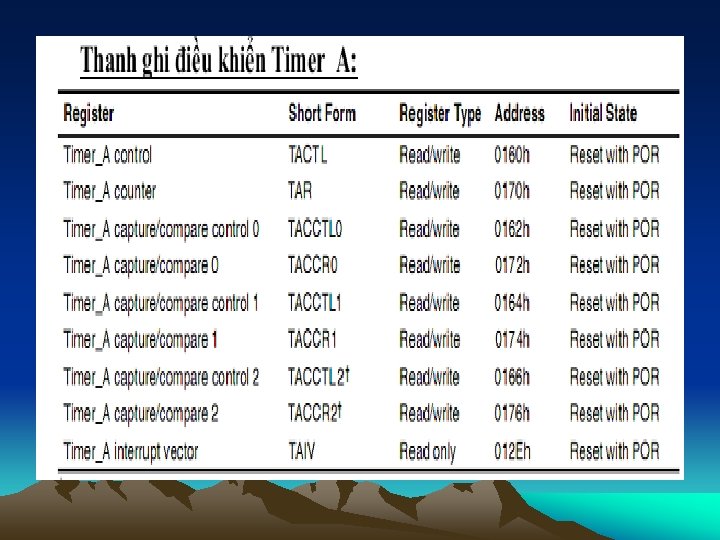

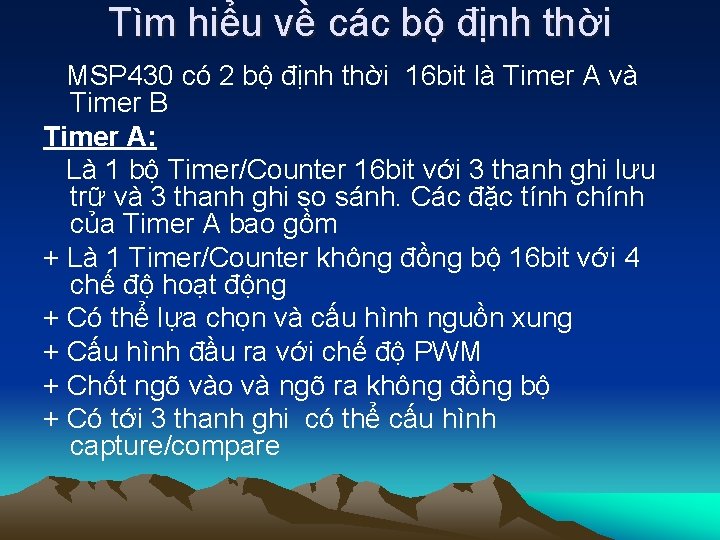

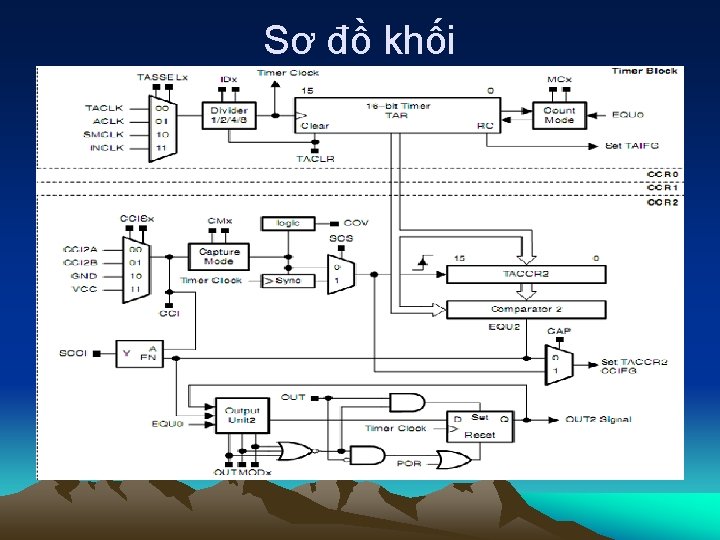

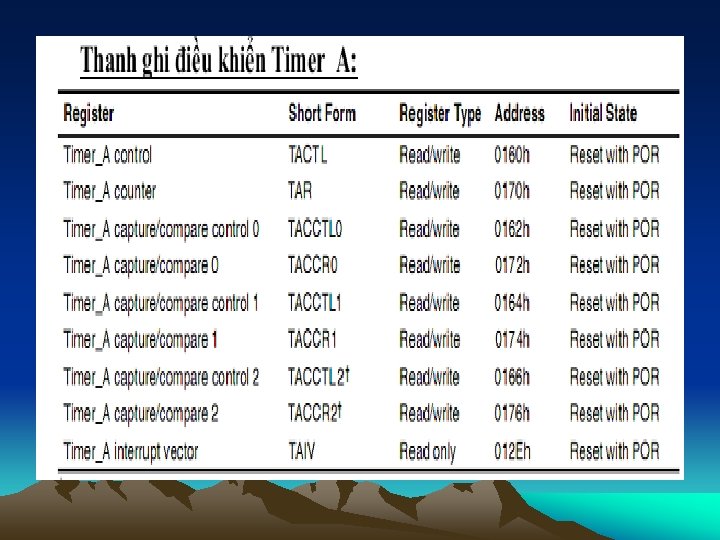

Tìm hiểu về các bộ định thời MSP 430 có 2 bộ định thời 16 bit là Timer A và Timer B Timer A: Là 1 bộ Timer/Counter 16 bit với 3 thanh ghi lưu trữ và 3 thanh ghi so sánh. Các đặc tính chính của Timer A bao gồm + Là 1 Timer/Counter không đồng bộ 16 bit với 4 chế độ hoạt động + Có thể lựa chọn và cấu hình nguồn xung + Cấu hình đầu ra với chế độ PWM + Chốt ngõ vào và ngõ ra không đồng bộ + Có tới 3 thanh ghi có thể cấu hình capture/compare

Timer hoạt động ở chế độ Counter 16 Bit: Ở chế độ Counter giá trị thanh ghi TAR tăng hoặc giảm theo cạnh lên của xung clock (tùy thuộc vào chế độ hoạt động). Giá trị thanh ghi TAR có thể được ghi hoặc đọc bởi phần mềm. Nó có khả năng tạo một ngắt khi đếm tràn. Thanh ghi TAR có thể bị xóa khi set bit TACLR. Việc set bit TACLR đồng thời cũng xóa giá trị lựa chọn cho bộ chia xung hoặc chế độ đếm lên hay đếm xuống. Lựa chọn nguồn xung và bộ chia xung: Timer có thể lựa chọn nguồn từ xung từ ACLK, SMCLK hoặc sử dụng nguồn xung ngoài thông qua TACLK hoặc INCLK. Nguồn xung được lựa chọn nhờ bít TASSELx. Các nguồn xung được chọn có thể đã được chia 2, 4 hoặc 8. Bộ chia xung được reset khi set bit TACLR.

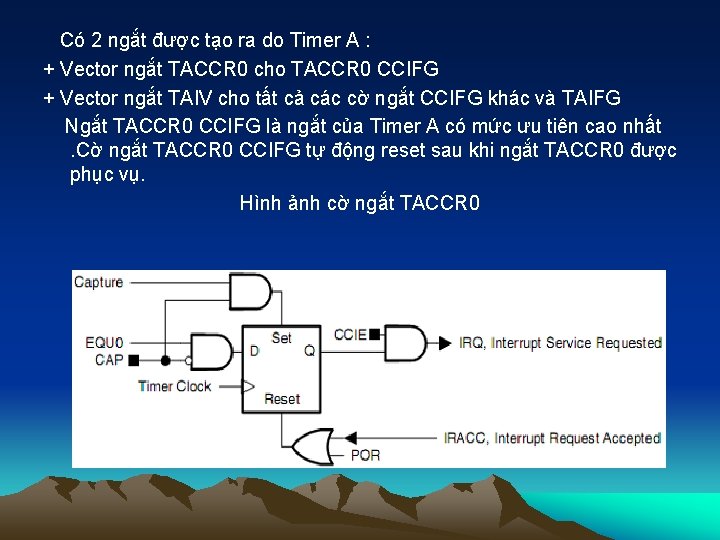

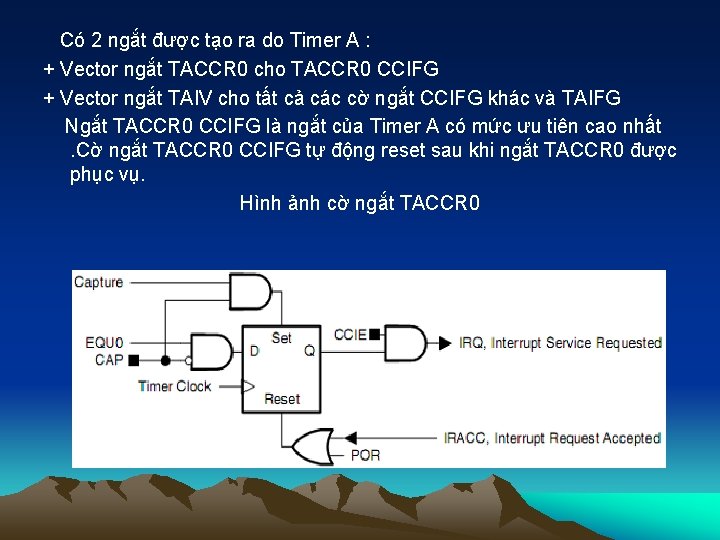

Có 2 ngắt được tạo ra do Timer A : + Vector ngắt TACCR 0 cho TACCR 0 CCIFG + Vector ngắt TAIV cho tất cả các cờ ngắt CCIFG khác và TAIFG Ngắt TACCR 0 CCIFG là ngắt của Timer A có mức ưu tiên cao nhất. Cờ ngắt TACCR 0 CCIFG tự động reset sau khi ngắt TACCR 0 được phục vụ. Hình ảnh cờ ngắt TACCR 0

Kích hoạt Timer: Timer có thể được kích hoạt hoặc kích hoạt lại bằng cách sau đây: + Timer đếm khi MCx > 0 và nguồn xung đã được kích hoạt. + Khi timer đang hoạt động ở chế độ đếm lên hoặc đếm xuống. Có thể dừng timer bằng cách ghi TACCR 0 = 0. Timer sẽ kích hoạt trở lại khi giá trị ghi vào TACCR 0 khác 0. Giá trị đếm lên sẽ bắt đầu từ 0. Các chế độ hoạt động của Timer: Timer hoạt động ở 4 chế độ: + Chế độ dừng + Chế độ đếm lên + Chế độ tiếp tục + Chế độ đếm lên/xuống Các chế độ này được lựa chọn bằng bit MCx.

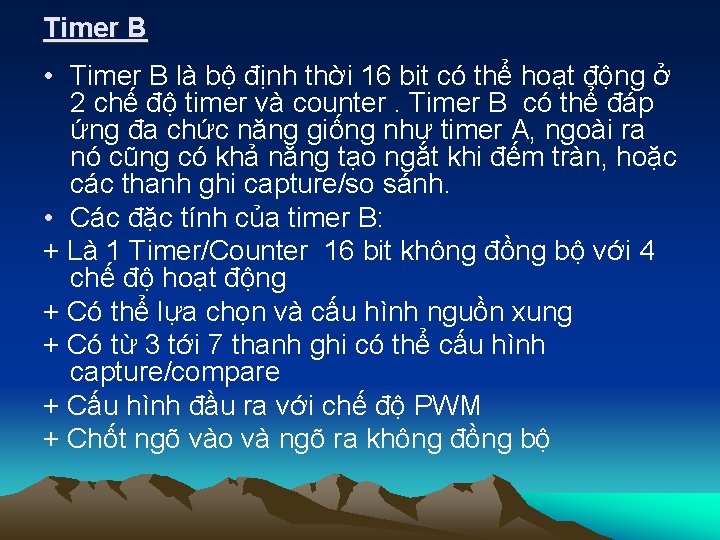

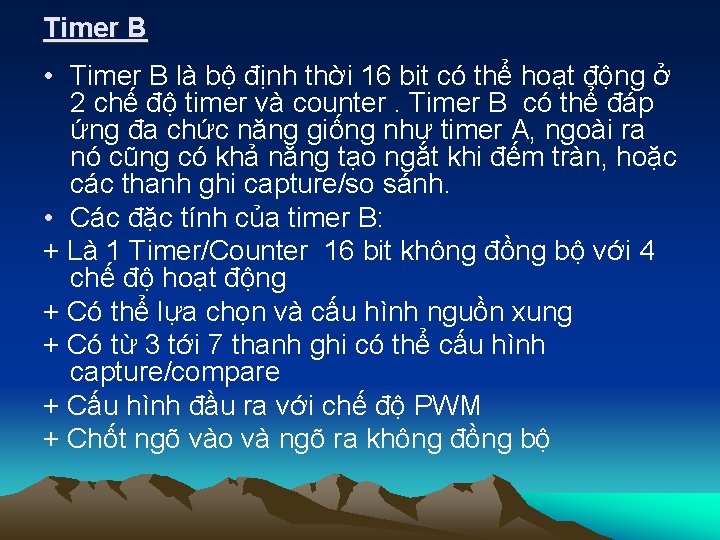

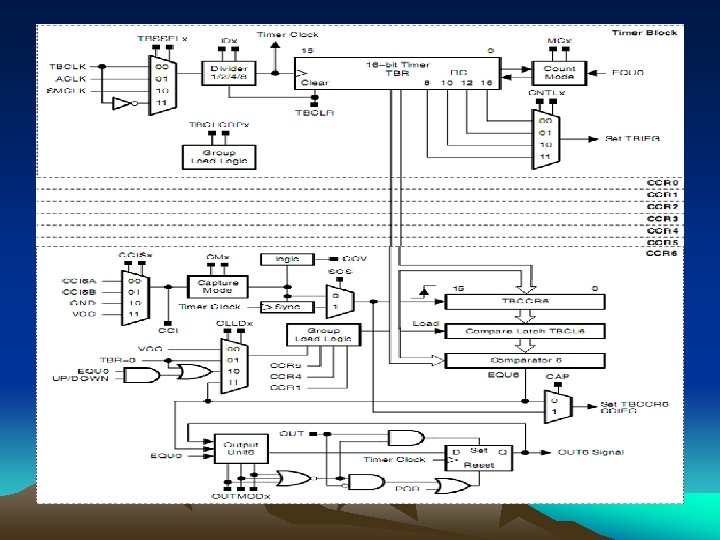

Timer B • Timer B là bộ định thời 16 bit có thể hoạt động ở 2 chế độ timer và counter. Timer B có thể đáp ứng đa chức năng giống như timer A, ngoài ra nó cũng có khả năng tạo ngắt khi đếm tràn, hoặc các thanh ghi capture/so sánh. • Các đặc tính của timer B: + Là 1 Timer/Counter 16 bit không đồng bộ với 4 chế độ hoạt động + Có thể lựa chọn và cấu hình nguồn xung + Có từ 3 tới 7 thanh ghi có thể cấu hình capture/compare + Cấu hình đầu ra với chế độ PWM + Chốt ngõ vào và ngõ ra không đồng bộ

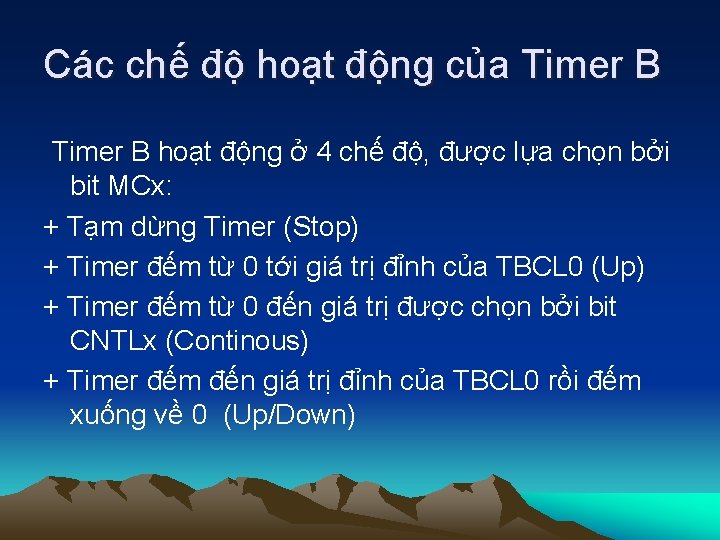

Các chế độ hoạt động của Timer B hoạt động ở 4 chế độ, được lựa chọn bởi bit MCx: + Tạm dừng Timer (Stop) + Timer đếm từ 0 tới giá trị đỉnh của TBCL 0 (Up) + Timer đếm từ 0 đến giá trị được chọn bởi bit CNTLx (Continous) + Timer đếm đến giá trị đỉnh của TBCL 0 rồi đếm xuống về 0 (Up/Down)

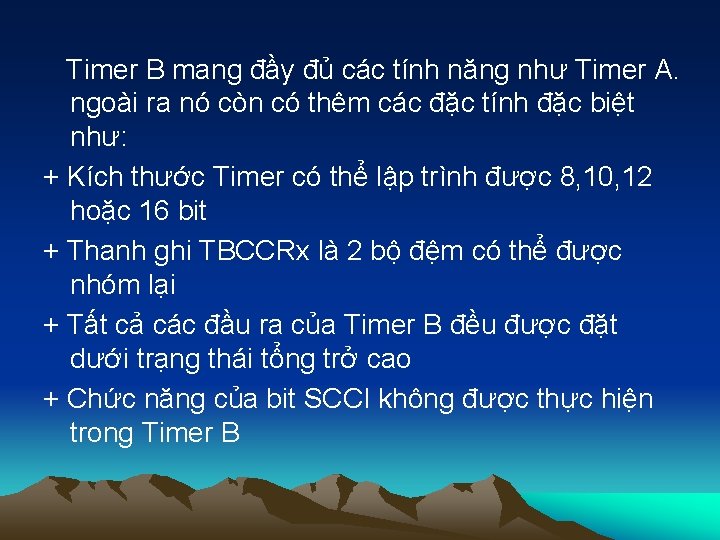

Timer B mang đầy đủ các tính năng như Timer A. ngoài ra nó còn có thêm các đặc tính đặc biệt như: + Kích thước Timer có thể lập trình được 8, 10, 12 hoặc 16 bit + Thanh ghi TBCCRx là 2 bộ đệm có thể được nhóm lại + Tất cả các đầu ra của Timer B đều được đặt dưới trạng thái tổng trở cao + Chức năng của bit SCCI không được thực hiện trong Timer B

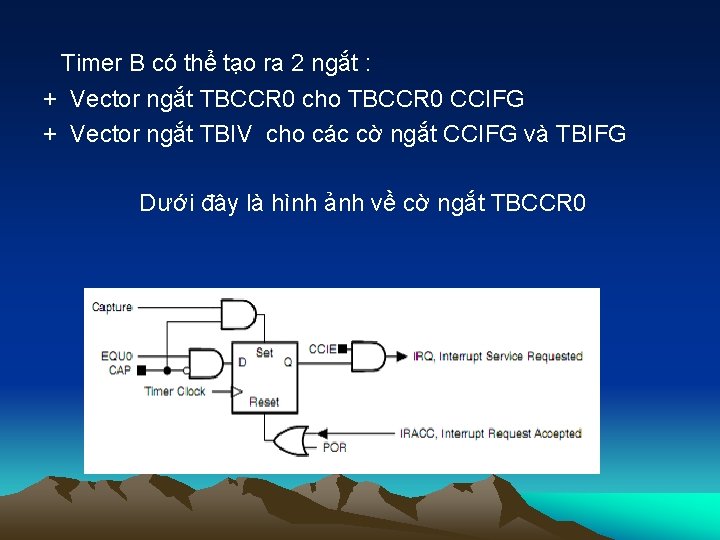

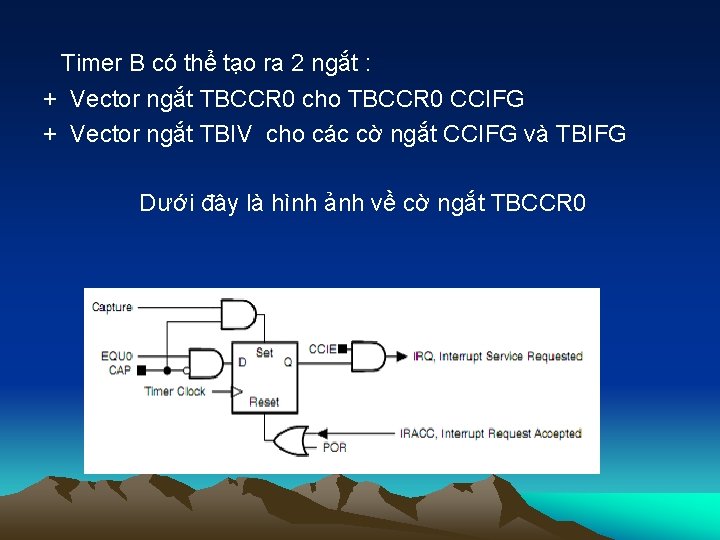

Timer B có thể tạo ra 2 ngắt : + Vector ngắt TBCCR 0 cho TBCCR 0 CCIFG + Vector ngắt TBIV cho các cờ ngắt CCIFG và TBIFG Dưới đây là hình ảnh về cờ ngắt TBCCR 0

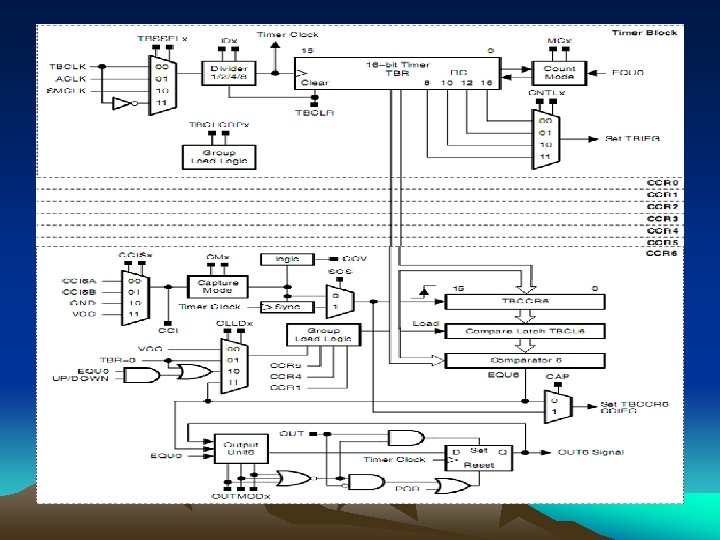

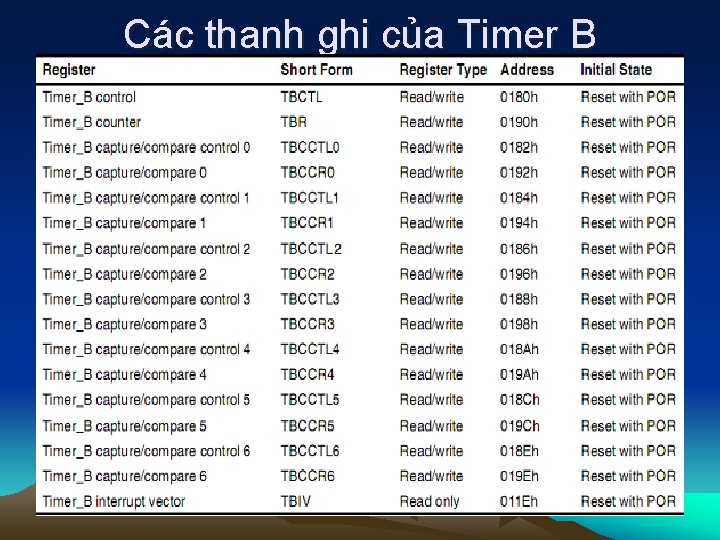

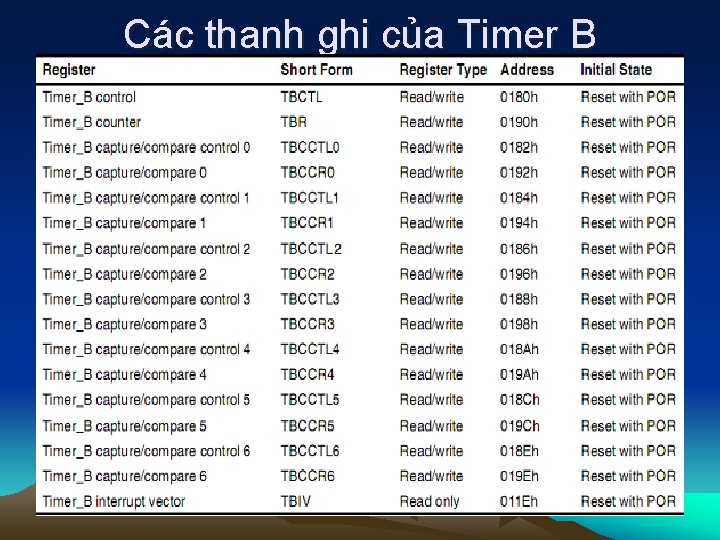

Các thanh ghi của Timer B

END!! Cảm ơn thầy giáo và các bạn đã quan tâm theo dõi