TMS 320 C 6000 Architectural Overview Learning Objectives

TMS 320 C 6000 Architectural Overview

Learning Objectives u u Describe C 6000 CPU architecture. Introduce some basic instructions. Describe the C 6000 memory map. Provide an overview of the peripherals.

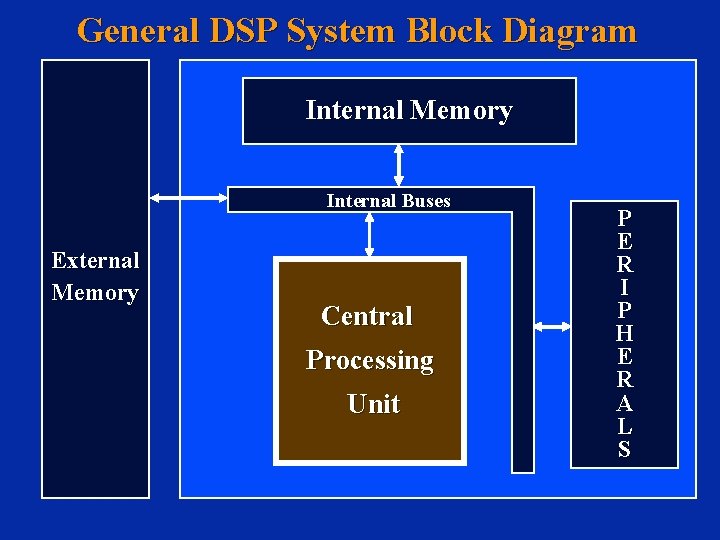

General DSP System Block Diagram Internal Memory Internal Buses External Memory Central Processing Unit P E R I P H E R A L S

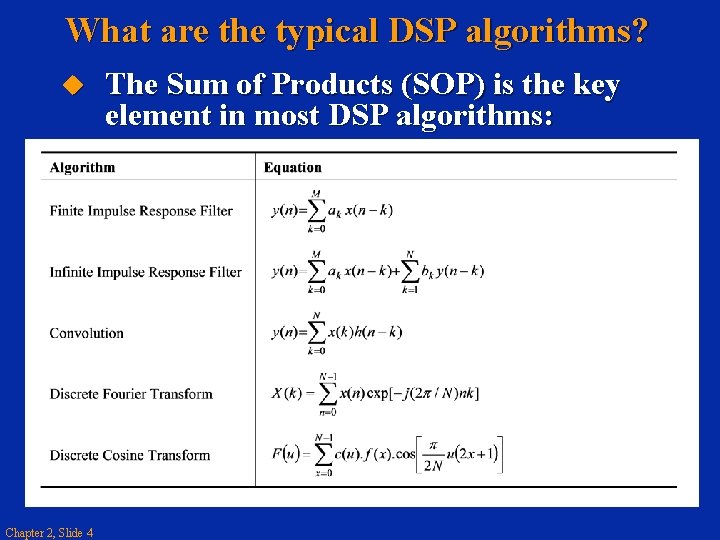

What are the typical DSP algorithms? u Chapter 2, Slide 4 The Sum of Products (SOP) is the key element in most DSP algorithms:

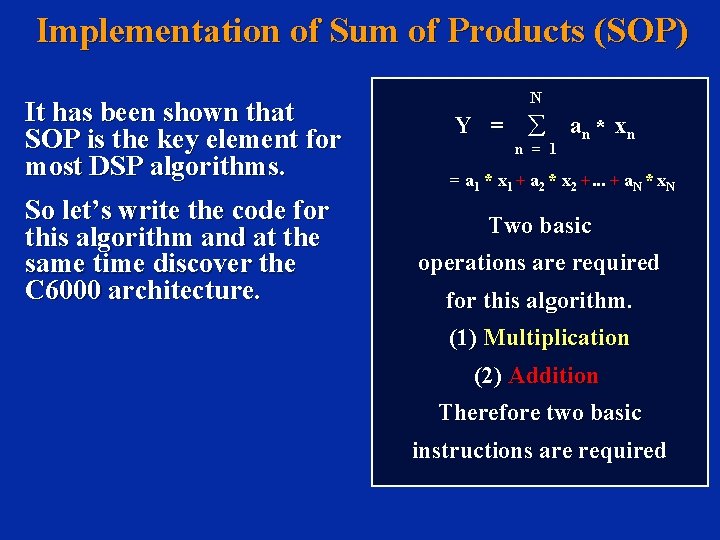

Implementation of Sum of Products (SOP) It has been shown that SOP is the key element for most DSP algorithms. So let’s write the code for this algorithm and at the same time discover the C 6000 architecture. N Y = å an * xn n = 1 = a 1 * x 1 + a 2 * x 2 +. . . + a. N * x. N Two basic operations are required for this algorithm. (1) Multiplication (2) Addition Therefore two basic instructions are required

Implementation of Sum of Products (SOP) So let’s implement the SOP algorithm! N Y = å an * xn n = 1 = a 1 * x 1 + a 2 * x 2 +. . . + a. N * x. N The implementation in this module will be done in assembly. Two basic operations are required for this algorithm. (1) Multiplication (2) Addition Therefore two basic instructions are required

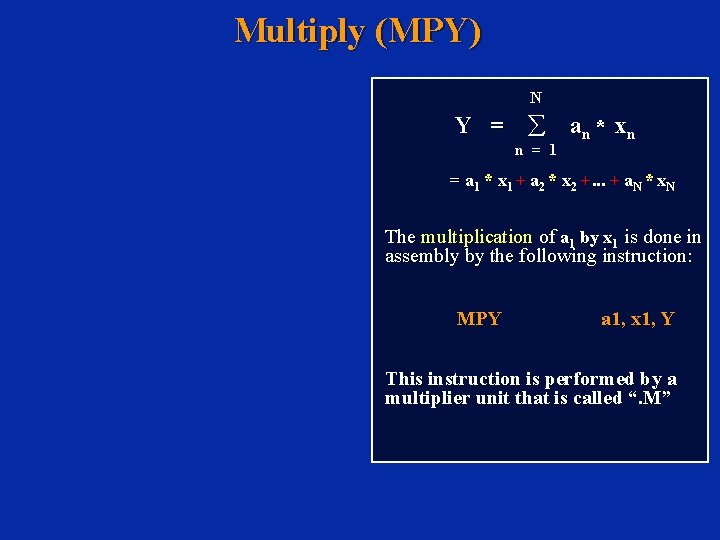

Multiply (MPY) N Y = å an * xn n = 1 = a 1 * x 1 + a 2 * x 2 +. . . + a. N * x. N The multiplication of a 1 by x 1 is done in assembly by the following instruction: MPY a 1, x 1, Y This instruction is performed by a multiplier unit that is called “. M”

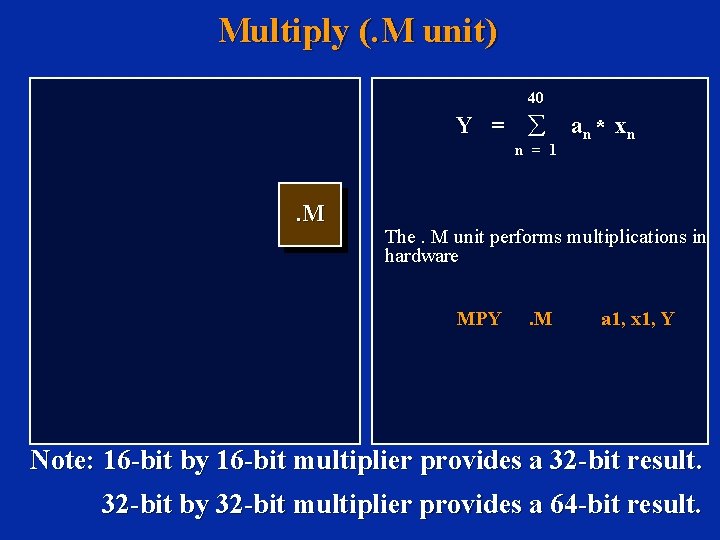

Multiply (. M unit) 40 Y = å an * xn n = 1 . M The. M unit performs multiplications in hardware MPY . M a 1, x 1, Y Note: 16 -bit by 16 -bit multiplier provides a 32 -bit result. 32 -bit by 32 -bit multiplier provides a 64 -bit result.

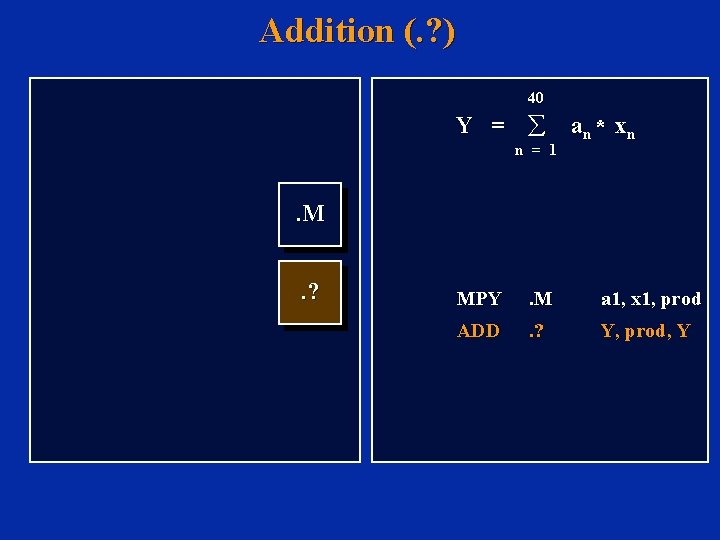

Addition (. ? ) 40 Y = å an * xn n = 1 . M. ? MPY . M a 1, x 1, prod ADD . ? Y, prod, Y

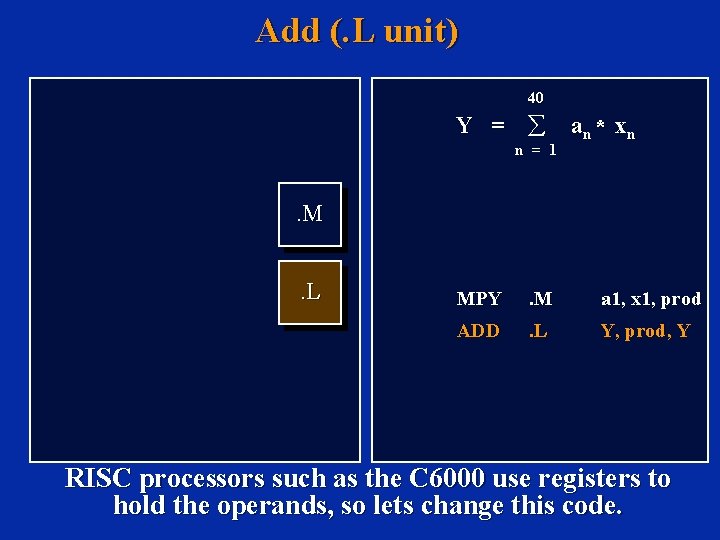

Add (. L unit) 40 Y = å an * xn n = 1 . M. L MPY . M a 1, x 1, prod ADD . L Y, prod, Y RISC processors such as the C 6000 use registers to hold the operands, so lets change this code.

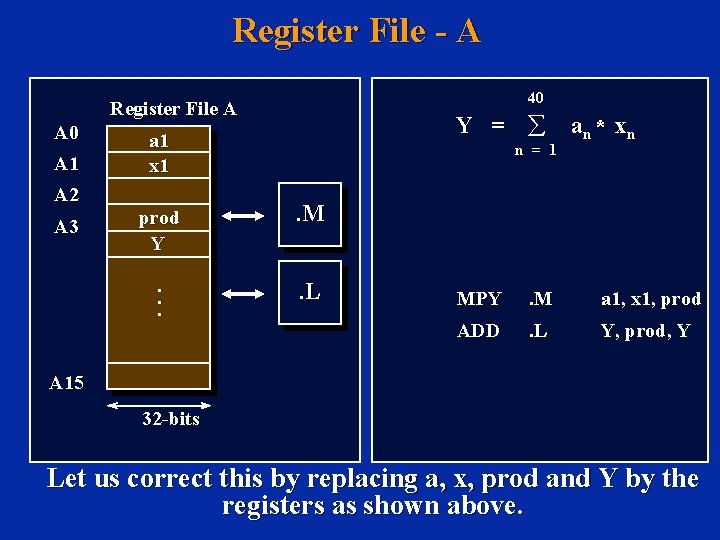

Register File - A 40 Register File A A 0 A 1 A 2 A 3 Y = å an * xn a 1 x 1 n = 1 prod Y . M . . L MPY . M a 1, x 1, prod ADD . L Y, prod, Y A 15 32 -bits Let us correct this by replacing a, x, prod and Y by the registers as shown above.

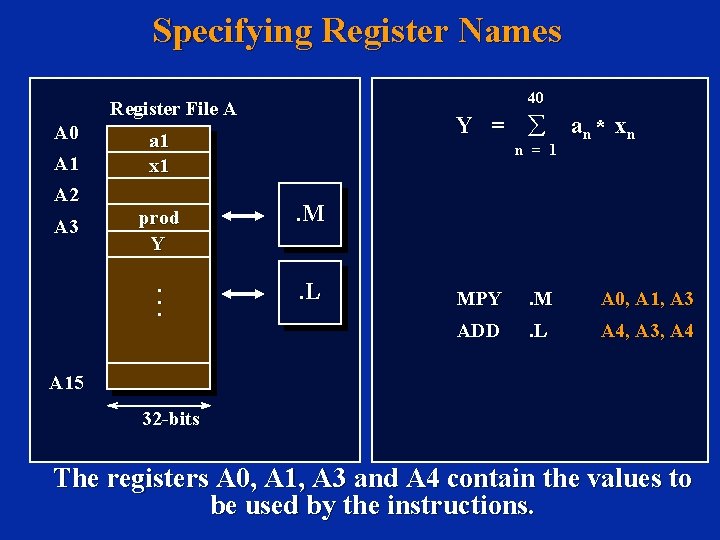

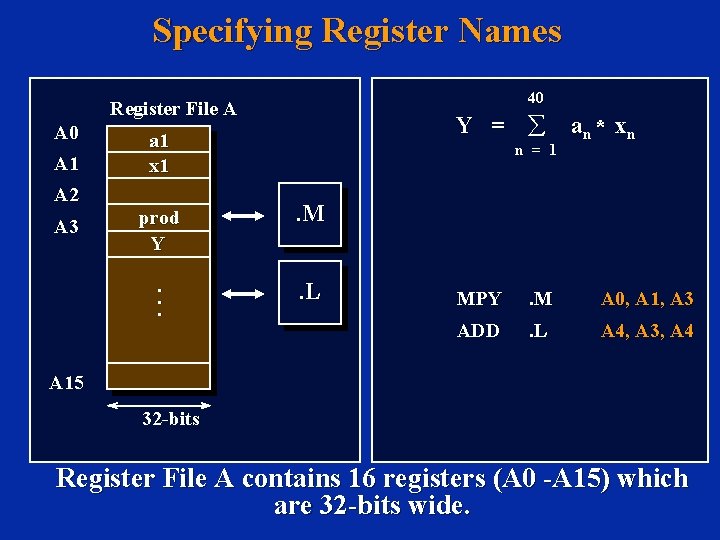

Specifying Register Names 40 Register File A A 0 A 1 A 2 A 3 Y = å an * xn a 1 x 1 n = 1 prod Y . M . . L MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 A 15 32 -bits The registers A 0, A 1, A 3 and A 4 contain the values to be used by the instructions.

Specifying Register Names 40 Register File A A 0 A 1 A 2 A 3 Y = å an * xn a 1 x 1 n = 1 prod Y . M . . L MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 A 15 32 -bits Register File A contains 16 registers (A 0 -A 15) which are 32 -bits wide.

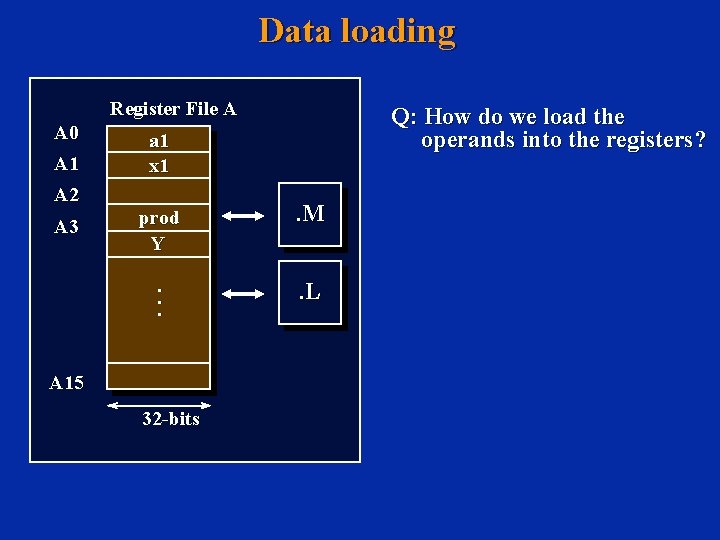

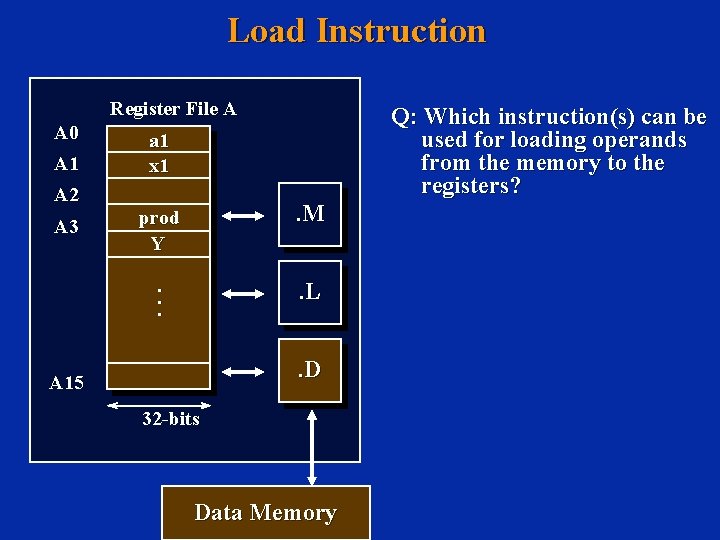

Data loading Register File A A 0 A 1 A 2 A 3 Q: How do we load the operands into the registers? a 1 x 1 prod Y . M . . L A 15 32 -bits

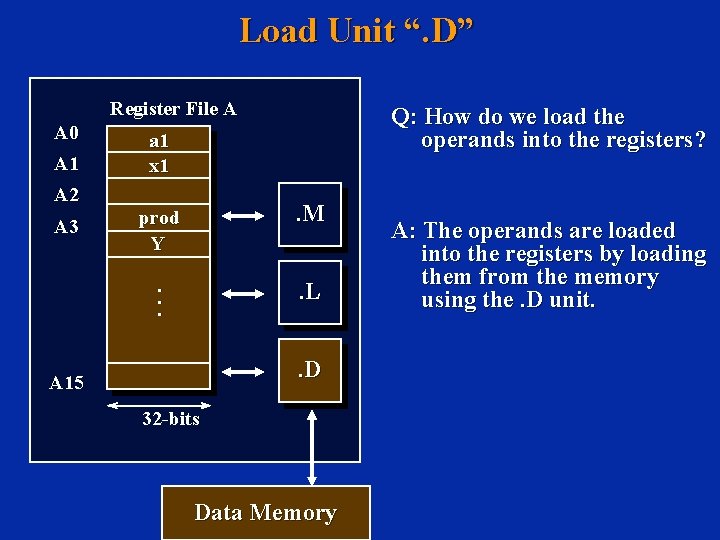

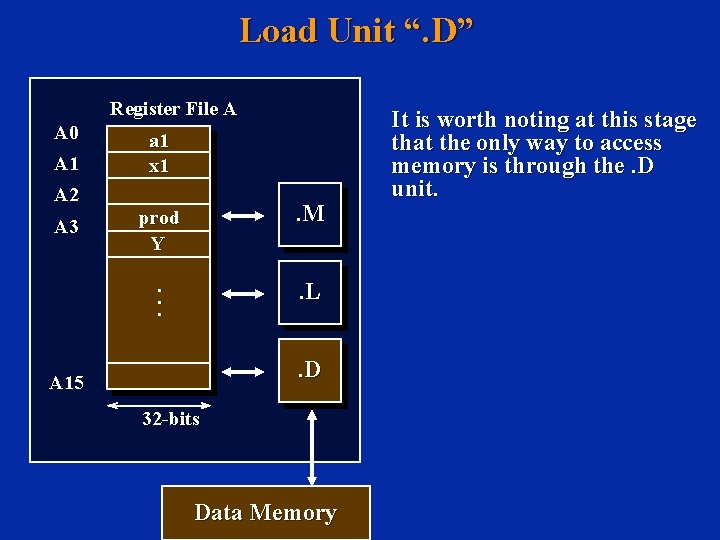

Load Unit “. D” Register File A A 0 A 1 A 2 A 3 Q: How do we load the operands into the registers? a 1 x 1 prod Y . M . . L. D A 15 32 -bits Data Memory A: The operands are loaded into the registers by loading them from the memory using the. D unit.

Load Unit “. D” Register File A A 0 A 1 A 2 A 3 a 1 x 1 prod Y . M . . L. D A 15 32 -bits Data Memory It is worth noting at this stage that the only way to access memory is through the. D unit.

Load Instruction Register File A A 0 A 1 A 2 A 3 Q: Which instruction(s) can be used for loading operands from the memory to the registers? a 1 x 1 prod Y . M . . L. D A 15 32 -bits Data Memory

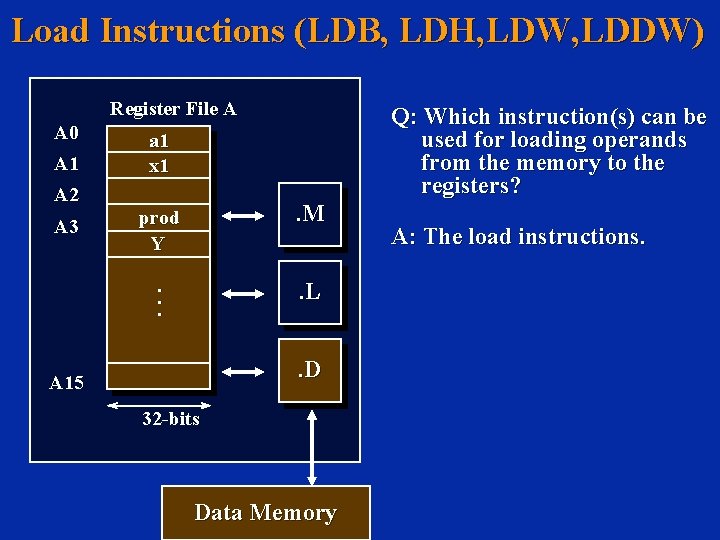

Load Instructions (LDB, LDH, LDW, LDDW) Register File A A 0 A 1 A 2 A 3 Q: Which instruction(s) can be used for loading operands from the memory to the registers? a 1 x 1 prod Y . M . . L. D A 15 32 -bits Data Memory A: The load instructions.

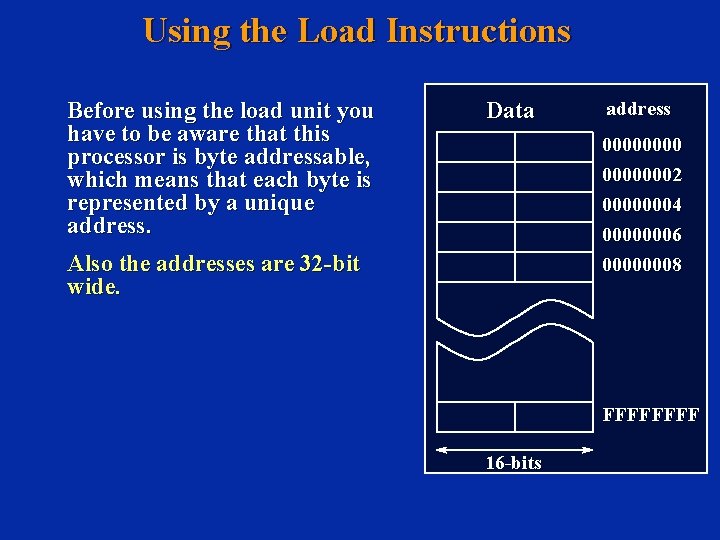

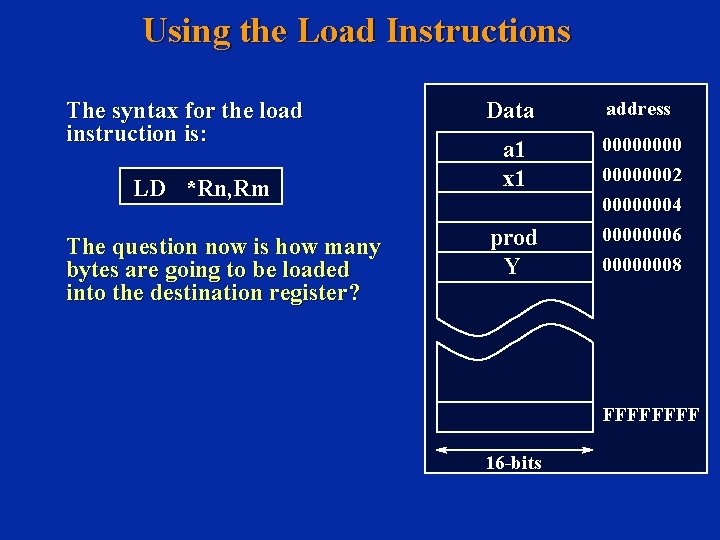

Using the Load Instructions Before using the load unit you have to be aware that this processor is byte addressable, which means that each byte is represented by a unique address. Data address 00000002 00000004 00000006 00000008 Also the addresses are 32 -bit wide. FFFF 16 -bits

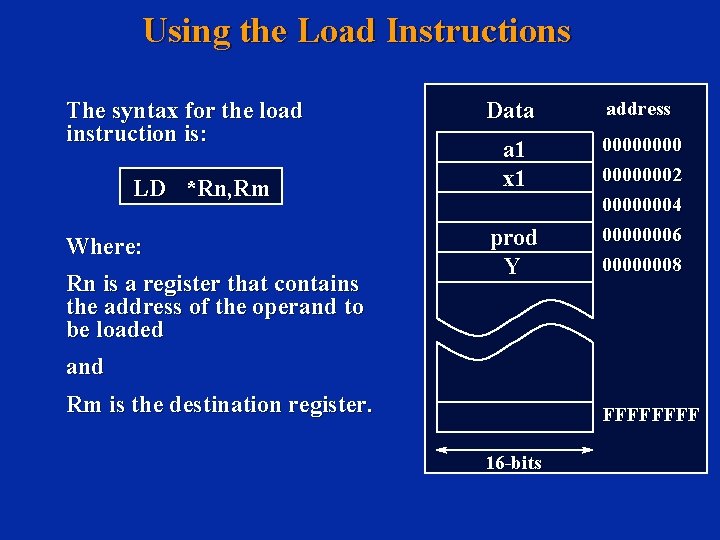

Using the Load Instructions The syntax for the load instruction is: LD *Rn, Rm Where: Rn is a register that contains the address of the operand to be loaded Data address a 1 x 1 00000002 00000004 00000006 00000008 prod Y and Rm is the destination register. FFFF 16 -bits

Using the Load Instructions The syntax for the load instruction is: LD *Rn, Rm The question now is how many bytes are going to be loaded into the destination register? Data address a 1 x 1 00000002 00000004 00000006 00000008 prod Y FFFF 16 -bits

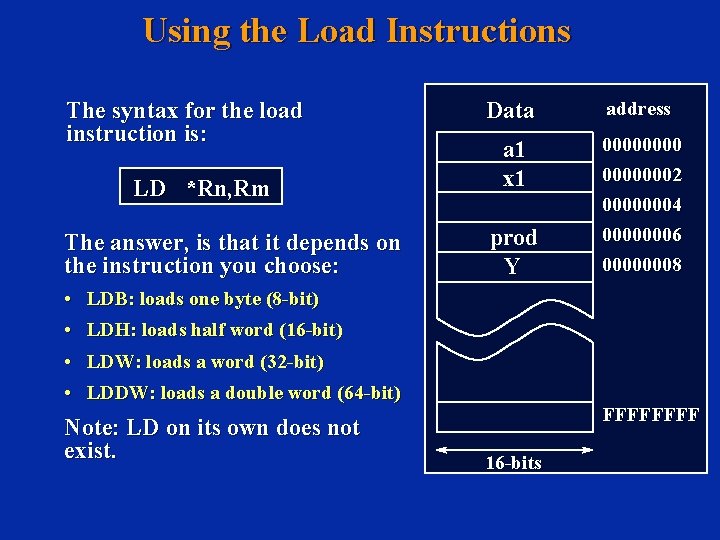

Using the Load Instructions The syntax for the load instruction is: LD *Rn, Rm The answer, is that it depends on the instruction you choose: Data address a 1 x 1 00000002 00000004 00000006 00000008 prod Y • LDB: loads one byte (8 -bit) • LDH: loads half word (16 -bit) • LDW: loads a word (32 -bit) • LDDW: loads a double word (64 -bit) Note: LD on its own does not exist. FFFF 16 -bits

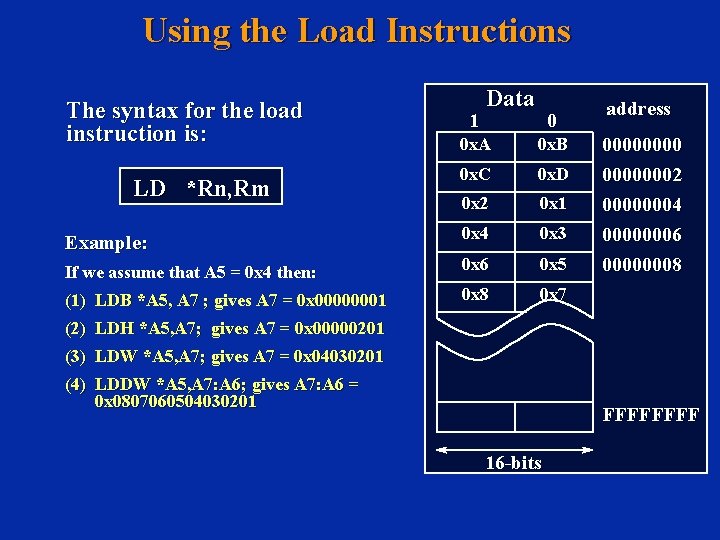

Using the Load Instructions The syntax for the load instruction is: 1 Data 0 0 x. A 0 x. B 0 x. C 0 x. D 0 x 2 0 x 1 0 x 4 0 x 3 If we assume that A 5 = 0 x 4 then: 0 x 6 0 x 5 (1) LDB *A 5, A 7 ; gives A 7 = 0 x 00000001 0 x 8 0 x 7 LD *Rn, Rm Example: address 00000002 00000004 00000006 00000008 (2) LDH *A 5, A 7; gives A 7 = 0 x 00000201 (3) LDW *A 5, A 7; gives A 7 = 0 x 04030201 (4) LDDW *A 5, A 7: A 6; gives A 7: A 6 = 0 x 0807060504030201 FFFF 16 -bits

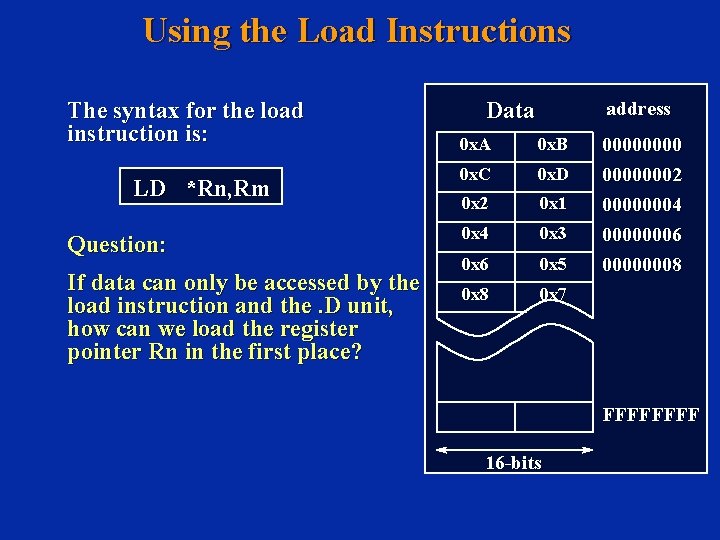

Using the Load Instructions The syntax for the load instruction is: LD *Rn, Rm Question: If data can only be accessed by the load instruction and the. D unit, how can we load the register pointer Rn in the first place? Data address 0 x. A 0 x. B 0 x. C 0 x. D 0 x 2 0 x 1 0 x 4 0 x 3 0 x 6 0 x 5 0 x 8 0 x 7 00000002 00000004 00000006 00000008 FFFF 16 -bits

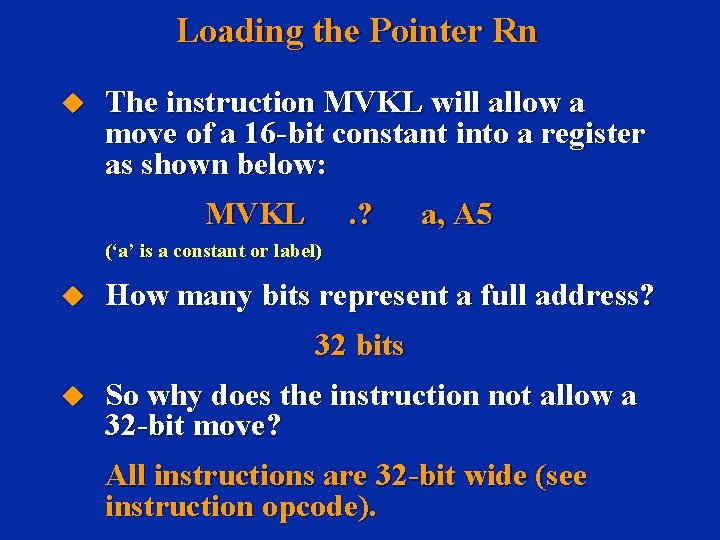

Loading the Pointer Rn u The instruction MVKL will allow a move of a 16 -bit constant into a register as shown below: MVKL . ? a, A 5 (‘a’ is a constant or label) u How many bits represent a full address? 32 bits u So why does the instruction not allow a 32 -bit move? All instructions are 32 -bit wide (see instruction opcode).

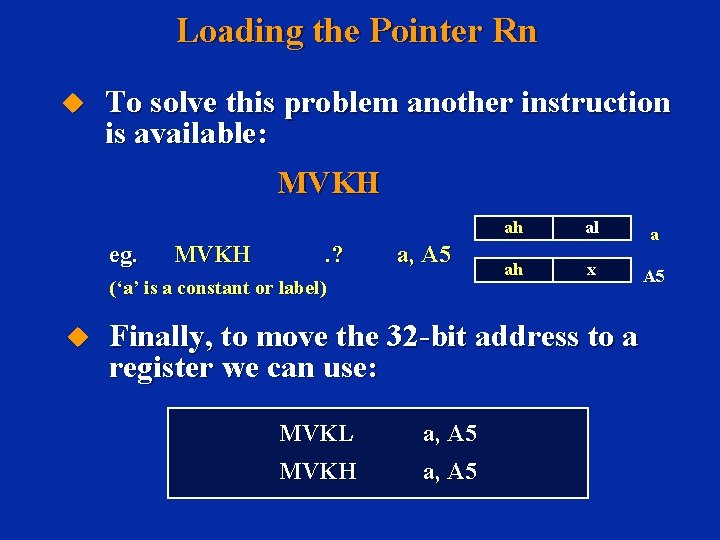

Loading the Pointer Rn u To solve this problem another instruction is available: MVKH eg. MVKH . ? a, A 5 (‘a’ is a constant or label) u ah al a ah x A 5 Finally, to move the 32 -bit address to a register we can use: MVKL a, A 5 MVKH a, A 5

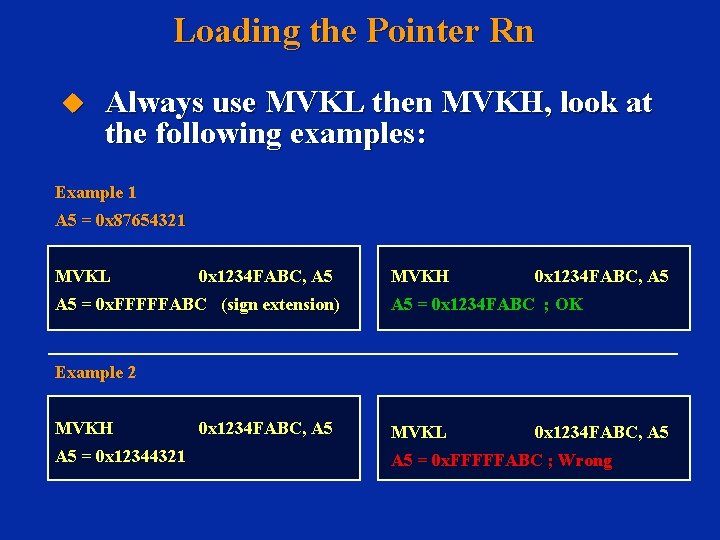

Loading the Pointer Rn u Always use MVKL then MVKH, look at the following examples: Example 1 A 5 = 0 x 87654321 MVKL 0 x 1234 FABC, A 5 = 0 x. FFFFFABC (sign extension) MVKH 0 x 1234 FABC, A 5 = 0 x 1234 FABC ; OK Example 2 MVKH A 5 = 0 x 12344321 0 x 1234 FABC, A 5 MVKL 0 x 1234 FABC, A 5 = 0 x. FFFFFABC ; Wrong

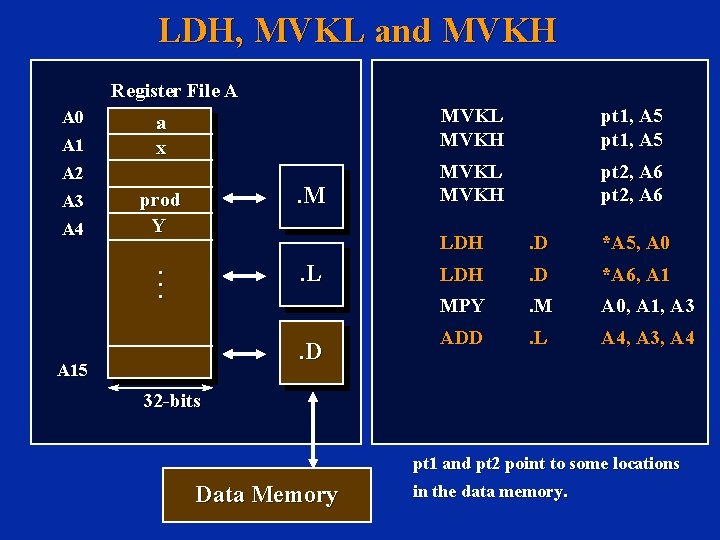

LDH, MVKL and MVKH Register File A A 0 A 1 a x A 2 A 3 A 4 prod Y . M . . L. D A 15 MVKL MVKH pt 1, A 5 MVKL MVKH pt 2, A 6 LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 32 -bits pt 1 and pt 2 point to some locations Data Memory in the data memory.

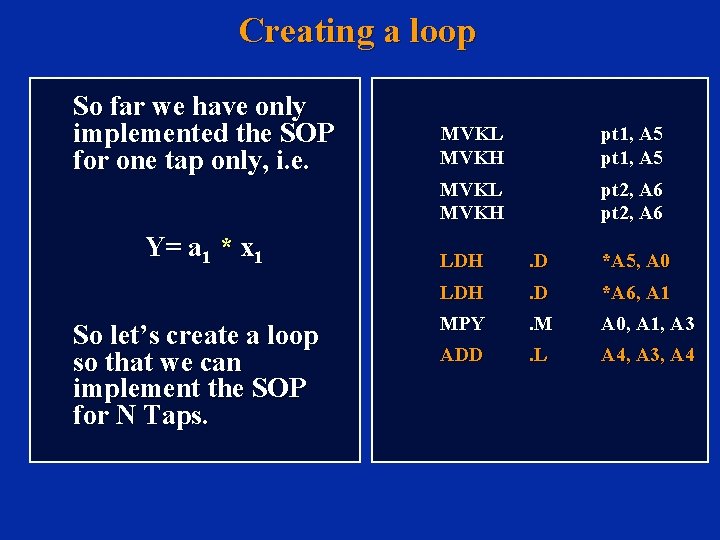

Creating a loop So far we have only implemented the SOP for one tap only, i. e. Y= a 1 * x 1 So let’s create a loop so that we can implement the SOP for N Taps. MVKL MVKH pt 1, A 5 MVKL MVKH pt 2, A 6 LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4

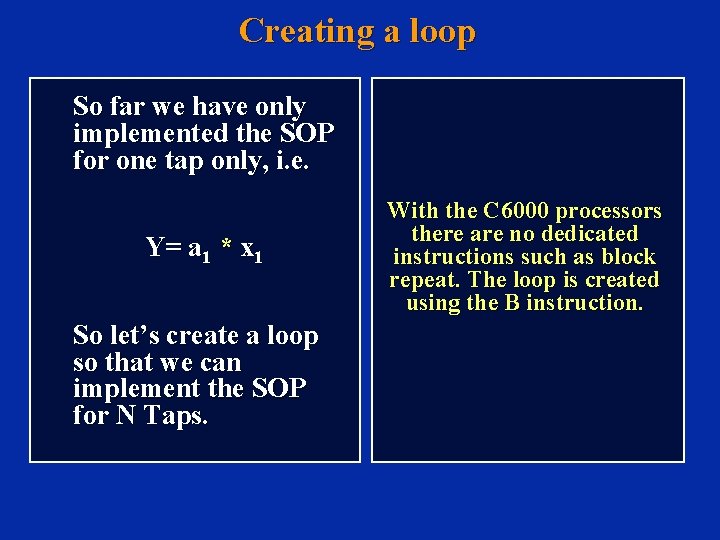

Creating a loop So far we have only implemented the SOP for one tap only, i. e. Y= a 1 * x 1 So let’s create a loop so that we can implement the SOP for N Taps. With the C 6000 processors there are no dedicated instructions such as block repeat. The loop is created using the B instruction.

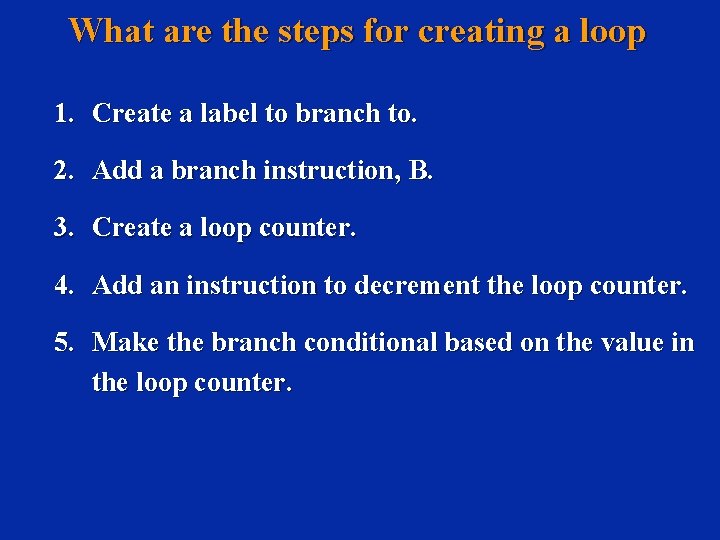

What are the steps for creating a loop 1. Create a label to branch to. 2. Add a branch instruction, B. 3. Create a loop counter. 4. Add an instruction to decrement the loop counter. 5. Make the branch conditional based on the value in the loop counter.

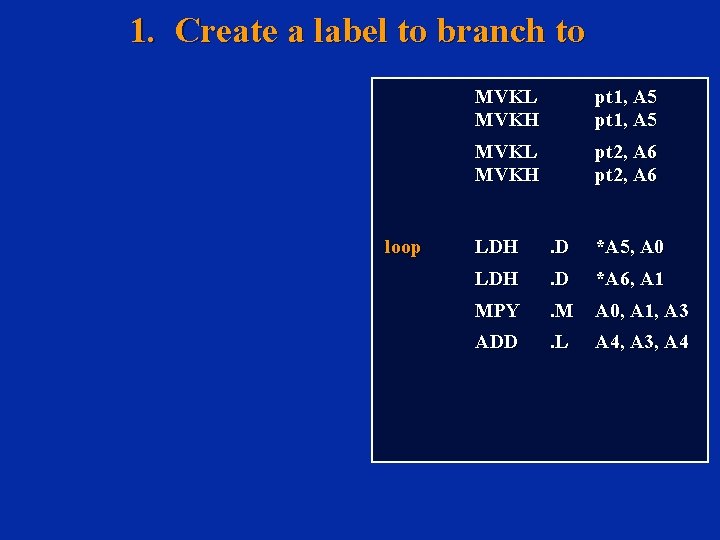

1. Create a label to branch to loop MVKL MVKH pt 1, A 5 MVKL MVKH pt 2, A 6 LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4

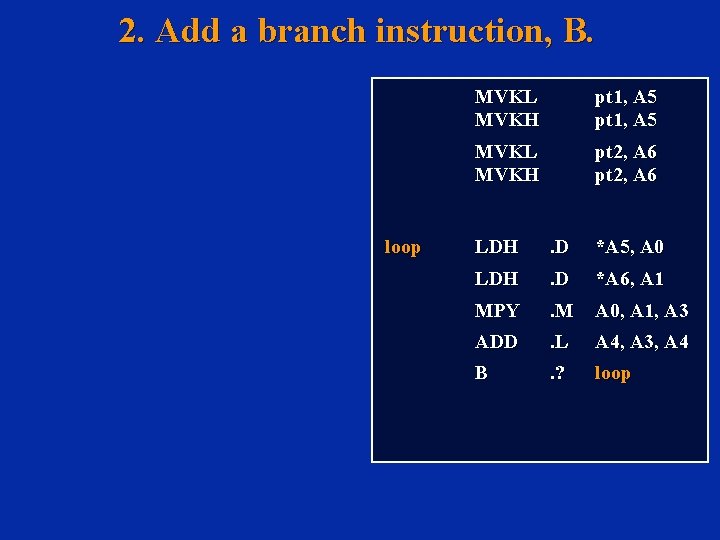

2. Add a branch instruction, B. loop MVKL MVKH pt 1, A 5 MVKL MVKH pt 2, A 6 LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 B . ? loop

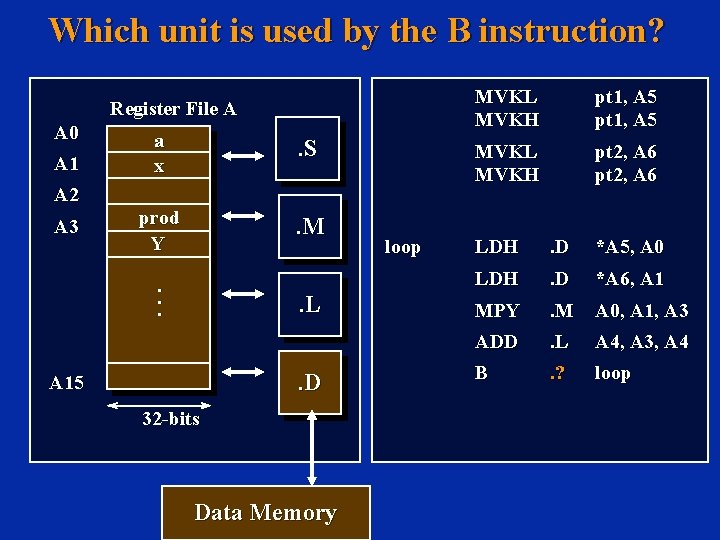

Which unit is used by the B instruction? Register File A A 0 A 1 A 2 A 3 a x . S prod Y . M. M . . L. L. D. D A 15 32 -bits Data Memory loop MVKL MVKH pt 1, A 5 MVKL MVKH pt 2, A 6 LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 B . ? loop

Which unit is used by the B instruction? Register File A A 0 A 1 A 2 A 3 a x . S prod Y . M. M . . L. L. D. D A 15 32 -bits Data Memory loop MVKL. S MVKH. S pt 1, A 5 MVKL. S MVKH. S pt 2, A 6 LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 B . S loop

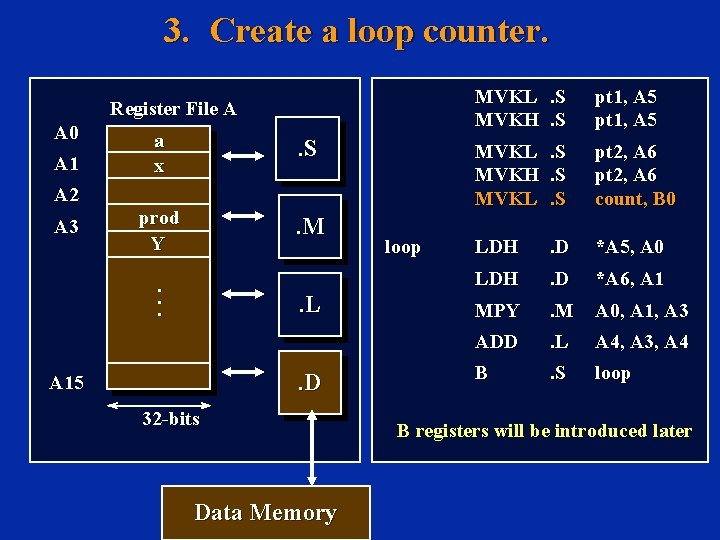

3. Create a loop counter. Register File A A 0 A 1 A 2 A 3 a x . S prod Y . M. M . . L. L. D. D A 15 32 -bits Data Memory loop MVKL. S MVKH. S pt 1, A 5 MVKL. S MVKH. S MVKL. S pt 2, A 6 count, B 0 LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 B . S loop B registers will be introduced later

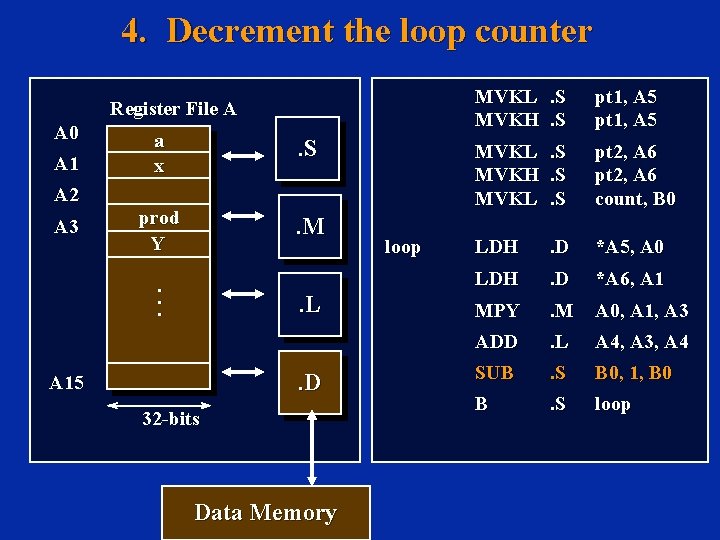

4. Decrement the loop counter Register File A A 0 A 1 A 2 A 3 a x . S prod Y . M. M . . L. L. D. D A 15 32 -bits Data Memory loop MVKL. S MVKH. S pt 1, A 5 MVKL. S MVKH. S MVKL. S pt 2, A 6 count, B 0 LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 SUB . S B 0, 1, B 0 B . S loop

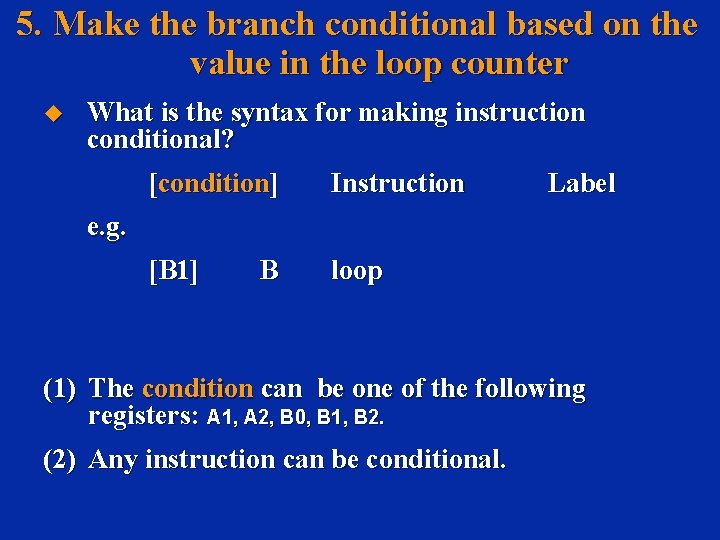

5. Make the branch conditional based on the value in the loop counter u What is the syntax for making instruction conditional? [condition] Instruction [B 1] loop Label e. g. B (1) The condition can be one of the following registers: A 1, A 2, B 0, B 1, B 2. (2) Any instruction can be conditional.

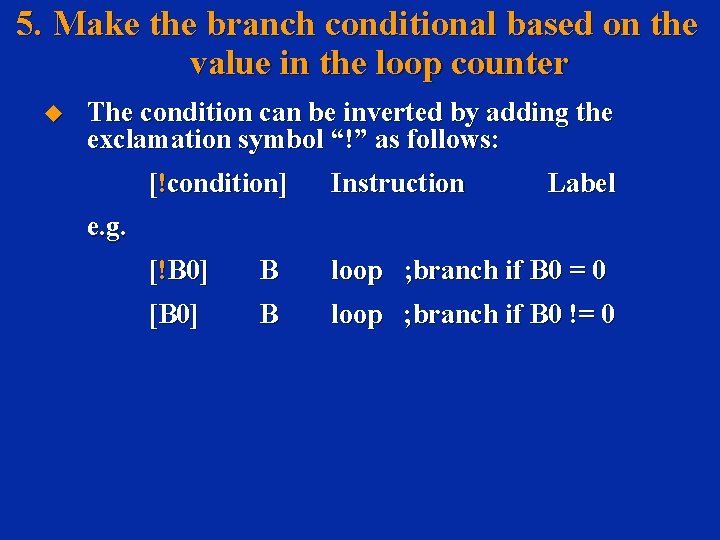

5. Make the branch conditional based on the value in the loop counter u The condition can be inverted by adding the exclamation symbol “!” as follows: [!condition] Instruction Label [!B 0] B loop ; branch if B 0 = 0 [B 0] B loop ; branch if B 0 != 0 e. g.

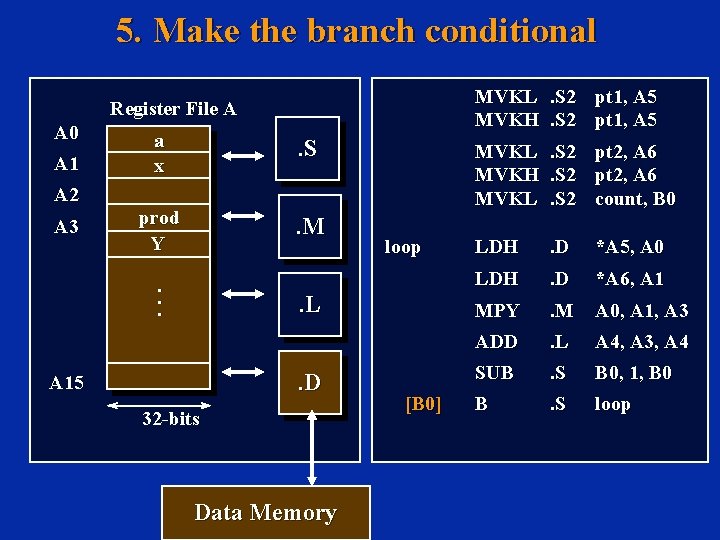

5. Make the branch conditional MVKL. S 2 pt 1, A 5 MVKH. S 2 pt 1, A 5 Register File A A 0 A 1 A 2 A 3 a x . S prod Y . M. M . . L. L. D. D A 15 32 -bits Data Memory MVKL. S 2 pt 2, A 6 MVKH. S 2 pt 2, A 6 MVKL. S 2 count, B 0 loop [B 0] LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 SUB . S B 0, 1, B 0 B . S loop

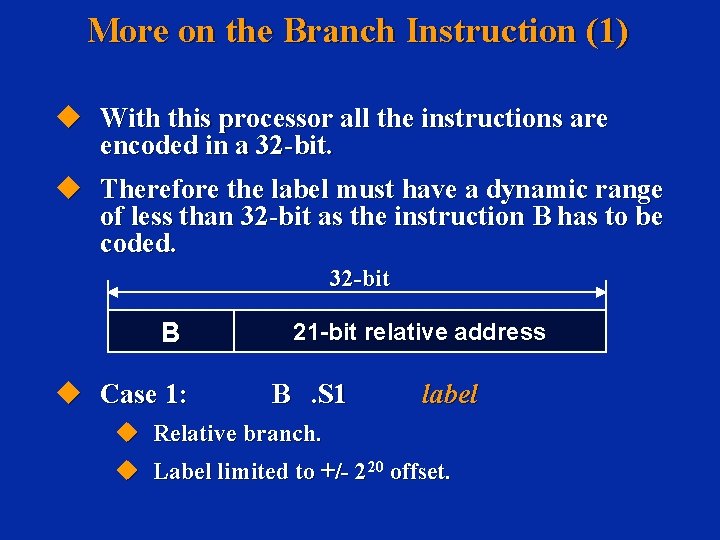

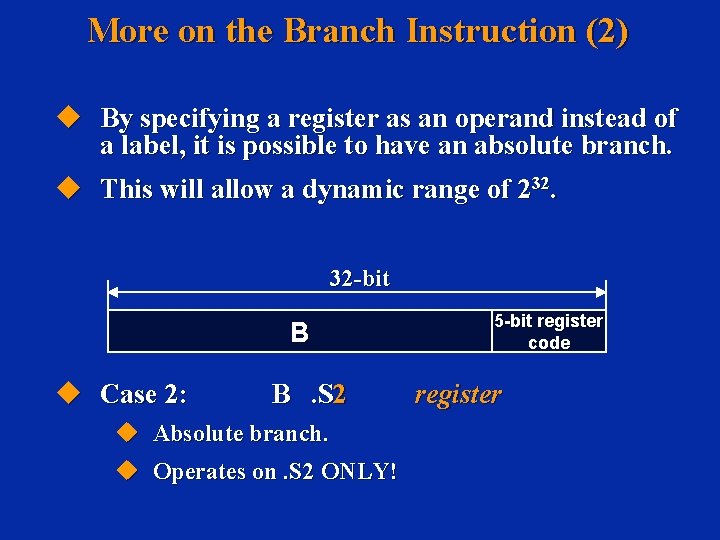

More on the Branch Instruction (1) u With this processor all the instructions are encoded in a 32 -bit. u Therefore the label must have a dynamic range of less than 32 -bit as the instruction B has to be coded. 32 -bit B u Case 1: 21 -bit relative address B. S 1 label u Relative branch. u Label limited to +/- 220 offset.

More on the Branch Instruction (2) u By specifying a register as an operand instead of a label, it is possible to have an absolute branch. u This will allow a dynamic range of 232. 32 -bit B u Case 2: B. S 2 u Absolute branch. u Operates on. S 2 ONLY! 5 -bit register code register

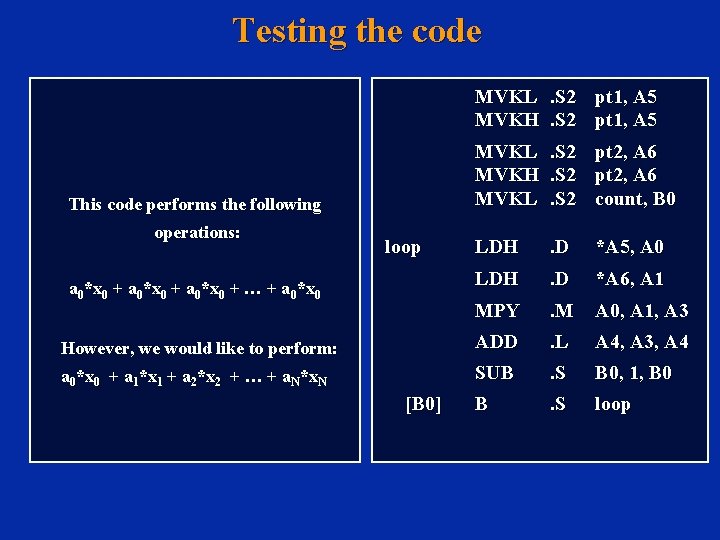

Testing the code MVKL. S 2 pt 1, A 5 MVKH. S 2 pt 1, A 5 MVKL. S 2 pt 2, A 6 MVKH. S 2 pt 2, A 6 MVKL. S 2 count, B 0 This code performs the following operations: loop LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 However, we would like to perform: ADD . L A 4, A 3, A 4 a 0*x 0 + a 1*x 1 + a 2*x 2 + … + a. N*x. N SUB . S B 0, 1, B 0 B . S loop a 0*x 0 + … + a 0*x 0 [B 0]

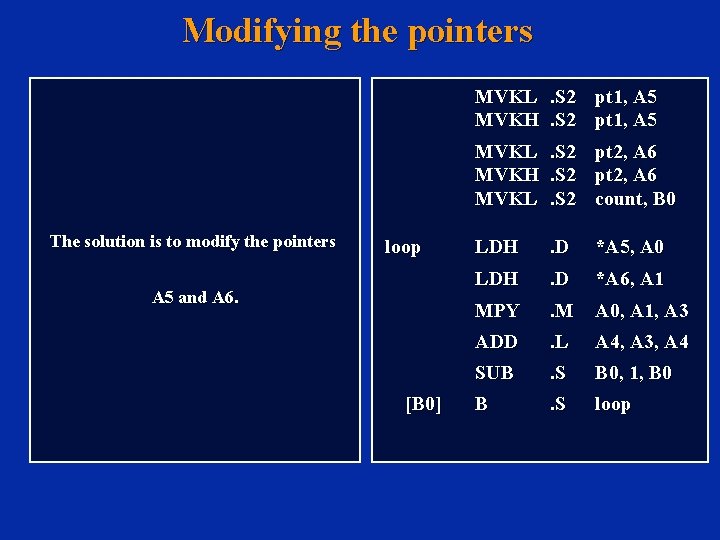

Modifying the pointers MVKL. S 2 pt 1, A 5 MVKH. S 2 pt 1, A 5 MVKL. S 2 pt 2, A 6 MVKH. S 2 pt 2, A 6 MVKL. S 2 count, B 0 The solution is to modify the pointers loop A 5 and A 6. [B 0] LDH . D *A 5, A 0 LDH . D *A 6, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 SUB . S B 0, 1, B 0 B . S loop

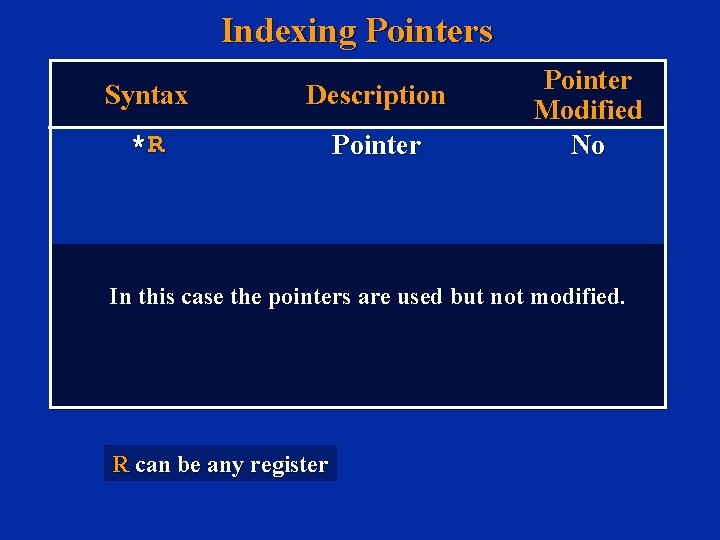

Indexing Pointers Syntax Description *R Pointer Modified No In this case the pointers are used but not modified. R can be any register

![Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] Pointer + Pre-offset - Pre-offset Pointer Modified Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] Pointer + Pre-offset - Pre-offset Pointer Modified](http://slidetodoc.com/presentation_image/25a40b6c0c710471f20a26eb4a2f5d20/image-46.jpg)

Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] Pointer + Pre-offset - Pre-offset Pointer Modified No No No In this case the pointers are modified BEFORE being used and RESTORED to their previous values. [disp] specifies the number of elements size in DW (64 -bit), W (32 -bit), H (16 -bit), or B (8 -bit). w disp = R or 5 -bit constant. w R can be any register. w

![Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] Pointer + Pre-offset - Pre-offset Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] Pointer + Pre-offset - Pre-offset](http://slidetodoc.com/presentation_image/25a40b6c0c710471f20a26eb4a2f5d20/image-47.jpg)

Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] Pointer + Pre-offset - Pre-offset Pre-increment Pre-decrement Pointer Modified No No No Yes In this case the pointers are modified BEFORE being used and NOT RESTORED to their Previous Values.

![Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] *R++[disp] *R--[disp] Pointer + Pre-offset Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] *R++[disp] *R--[disp] Pointer + Pre-offset](http://slidetodoc.com/presentation_image/25a40b6c0c710471f20a26eb4a2f5d20/image-48.jpg)

Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] *R++[disp] *R--[disp] Pointer + Pre-offset - Pre-offset Pre-increment Pre-decrement Post-increment Post-decrement Pointer Modified No No No Yes Yes In this case the pointers are modified AFTER being used and NOT RESTORED to their Previous Values.

![Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] *R++[disp] *R--[disp] Pointer + Pre-offset Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] *R++[disp] *R--[disp] Pointer + Pre-offset](http://slidetodoc.com/presentation_image/25a40b6c0c710471f20a26eb4a2f5d20/image-49.jpg)

Indexing Pointers Syntax Description *R *+R[disp] *-R[disp] *++R[disp] *--R[disp] *R++[disp] *R--[disp] Pointer + Pre-offset - Pre-offset Pre-increment Pre-decrement Post-increment Post-decrement w w w Pointer Modified No No No Yes Yes [disp] specifies # elements - size in DW, W, H, or B. disp = R or 5 -bit constant. R can be any register.

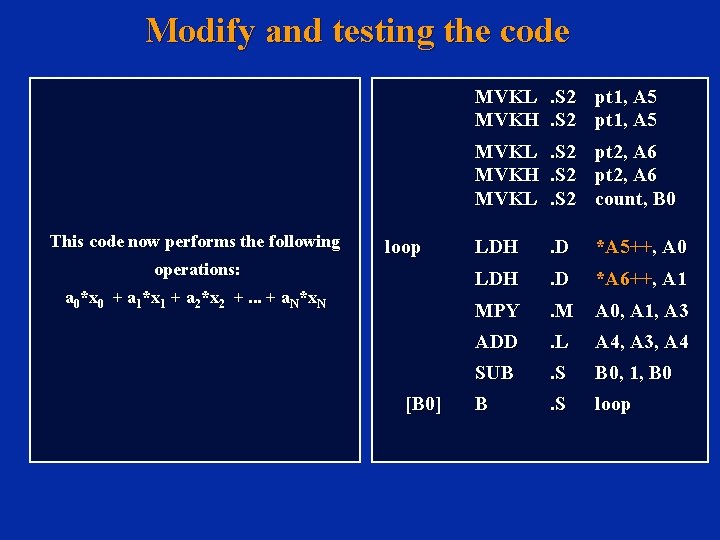

Modify and testing the code MVKL. S 2 pt 1, A 5 MVKH. S 2 pt 1, A 5 MVKL. S 2 pt 2, A 6 MVKH. S 2 pt 2, A 6 MVKL. S 2 count, B 0 This code now performs the following loop operations: a 0*x 0 + a 1*x 1 + a 2*x 2 +. . . + a. N*x. N [B 0] LDH . D *A 5++, A 0 LDH . D *A 6++, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 SUB . S B 0, 1, B 0 B . S loop

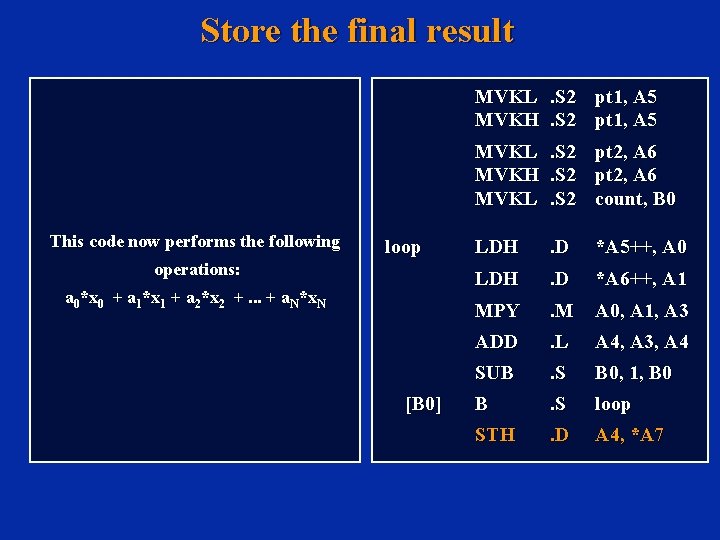

Store the final result MVKL. S 2 pt 1, A 5 MVKH. S 2 pt 1, A 5 MVKL. S 2 pt 2, A 6 MVKH. S 2 pt 2, A 6 MVKL. S 2 count, B 0 This code now performs the following loop operations: a 0*x 0 + a 1*x 1 + a 2*x 2 +. . . + a. N*x. N [B 0] LDH . D *A 5++, A 0 LDH . D *A 6++, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 SUB . S B 0, 1, B 0 B . S loop STH . D A 4, *A 7

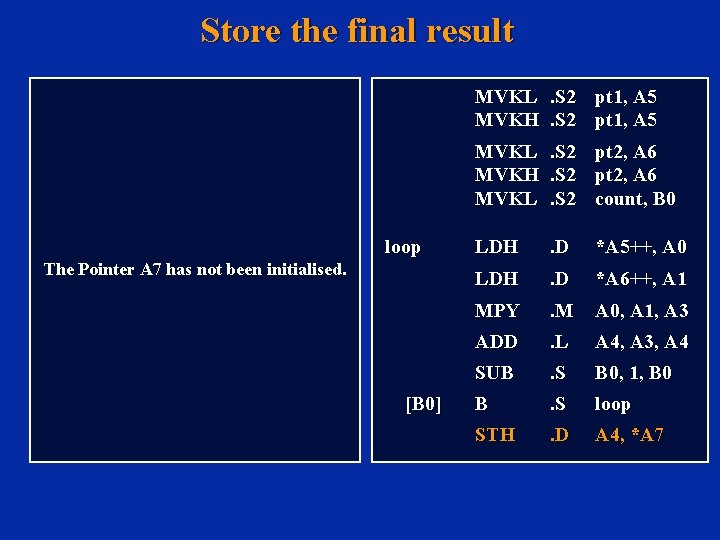

Store the final result MVKL. S 2 pt 1, A 5 MVKH. S 2 pt 1, A 5 MVKL. S 2 pt 2, A 6 MVKH. S 2 pt 2, A 6 MVKL. S 2 count, B 0 loop The Pointer A 7 has not been initialised. [B 0] LDH . D *A 5++, A 0 LDH . D *A 6++, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 SUB . S B 0, 1, B 0 B . S loop STH . D A 4, *A 7

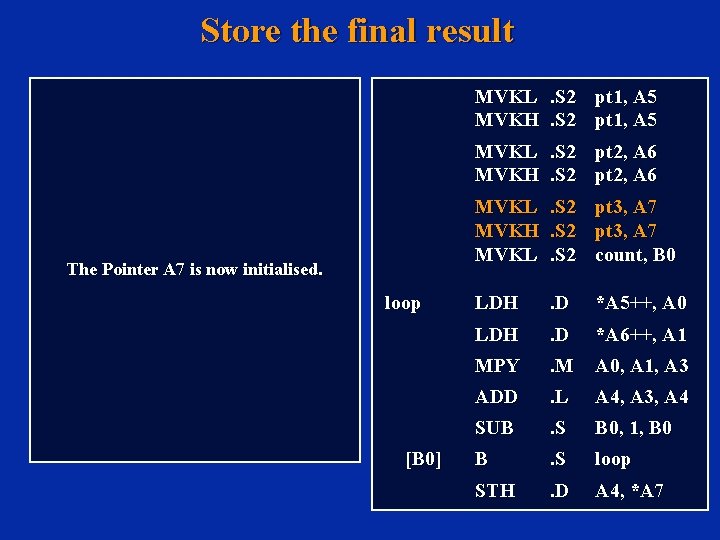

Store the final result MVKL. S 2 pt 1, A 5 MVKH. S 2 pt 1, A 5 MVKL. S 2 pt 2, A 6 MVKH. S 2 pt 2, A 6 MVKL. S 2 pt 3, A 7 MVKH. S 2 pt 3, A 7 MVKL. S 2 count, B 0 The Pointer A 7 is now initialised. loop [B 0] LDH . D *A 5++, A 0 LDH . D *A 6++, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 SUB . S B 0, 1, B 0 B . S loop STH . D A 4, *A 7

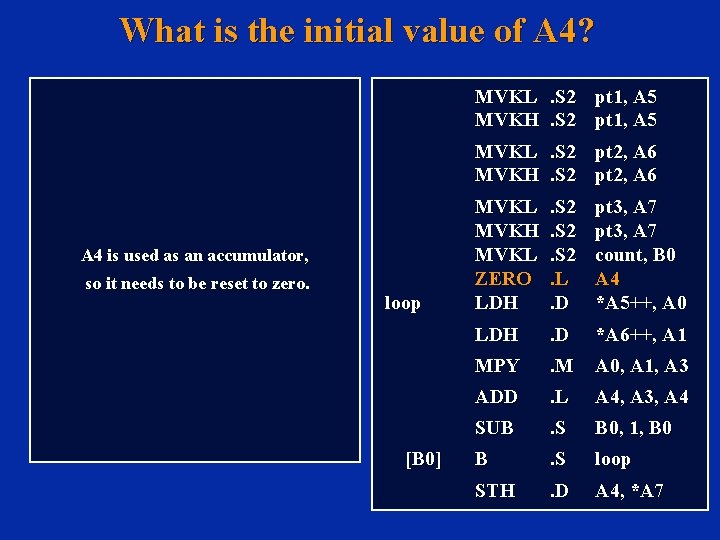

What is the initial value of A 4? MVKL. S 2 pt 1, A 5 MVKH. S 2 pt 1, A 5 MVKL. S 2 pt 2, A 6 MVKH. S 2 pt 2, A 6 A 4 is used as an accumulator, so it needs to be reset to zero. loop [B 0] MVKL MVKH MVKL ZERO LDH . S 2. L. D pt 3, A 7 count, B 0 A 4 *A 5++, A 0 LDH . D *A 6++, A 1 MPY . M A 0, A 1, A 3 ADD . L A 4, A 3, A 4 SUB . S B 0, 1, B 0 B . S loop STH . D A 4, *A 7

- Slides: 54