TMicro D Integration for SOI Pixel Detector Makoto

- Slides: 33

T-Micro 3 D Integration for SOI Pixel Detector Makoto Motoyoshi (T-Micro) PIXEL 2012 Sept. 03, 2012 @Inawashiro Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

Contents 1. Motivation Device target 2. Technologies and issues SOI Pixel detector process flow Yield process issues and counter measurements 3. Cost down technique of 3 D stacking 4. Summary PIXEL 2012 Sept. 03, 2012 @Inawashiro 2 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

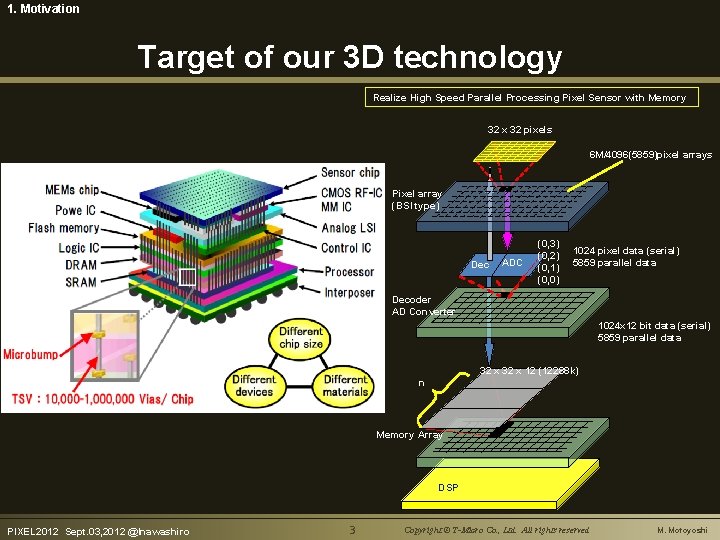

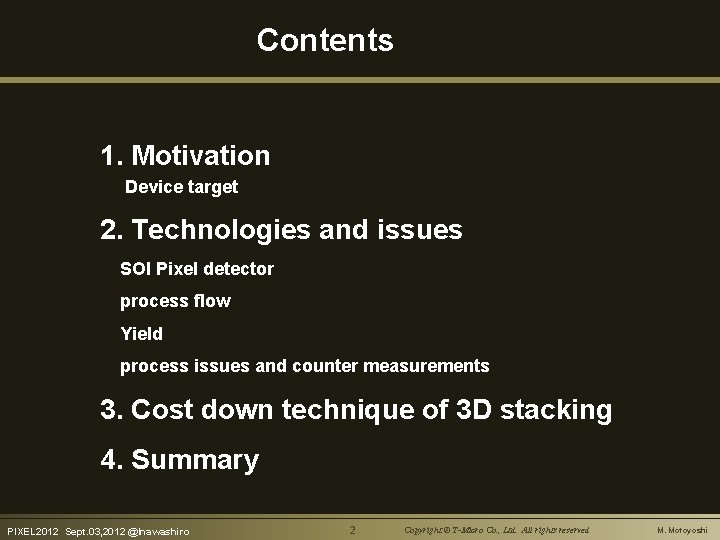

1. Motivation Target of our 3 D technology Realize High Speed Parallel Processing Pixel Sensor with Memory 32 x 32 pixels 6 M/4096(5859)pixel arrays Pixel array (BSI type) Dec ADC (0, 3) (0, 2) (0, 1) (0, 0) 1024 pixel data (serial) 5859 parallel data Decoder AD Converter 1024 x 12 bit data (serial) 5859 parallel data 32 x 12 (12288 k) n Memory Array DSP PIXEL 2012 Sept. 03, 2012 @Inawashiro 3 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

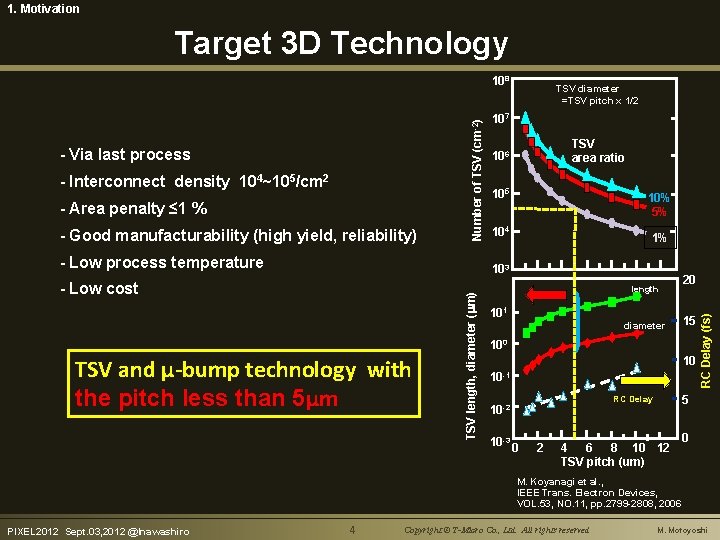

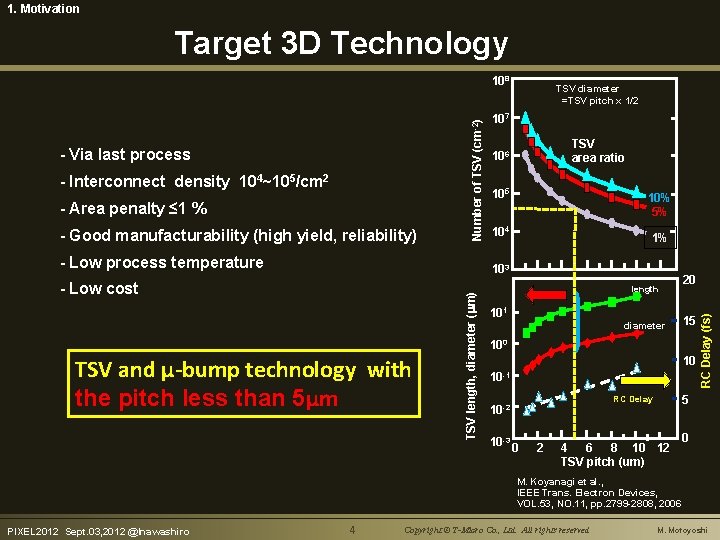

1. Motivation Target 3 D Technology - Interconnect density 104~105/cm 2 - Area penalty ≤ 1 % - Good manufacturability (high yield, reliability) - Low process temperature TSV diameter =TSV pitch x 1/2 107 TSV area ratio 106 105 10% 5% 104 1% - Low cost TSV and μ-bump technology with the pitch less than 5μm TSV length, diameter (mm) 103 length 101 diameter 20 15 100 10 10 -1 10 -3 5 RC Delay 10 -2 0 2 RC Delay (fs) - Via last process Number of TSV (cm-2) 108 4 6 8 10 12 TSV pitch (um) 0 M. Koyanagi et al. , IEEE Trans. Electron Devices, VOL. 53, NO. 11, pp. 2799 -2808, 2006 PIXEL 2012 Sept. 03, 2012 @Inawashiro 4 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

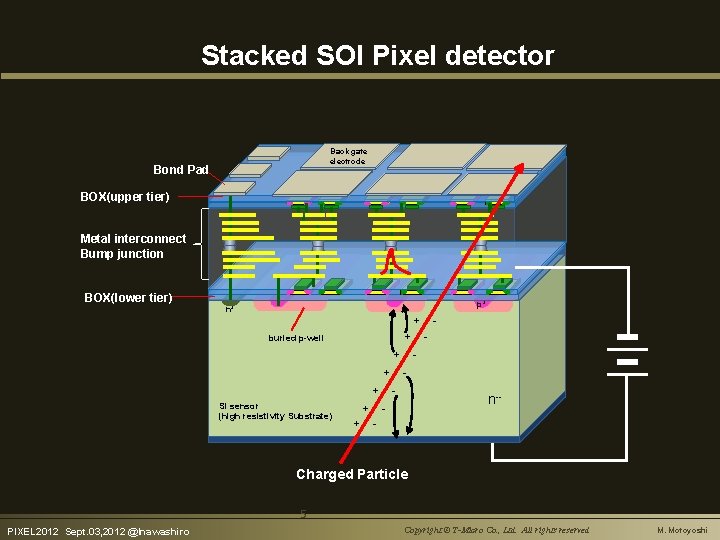

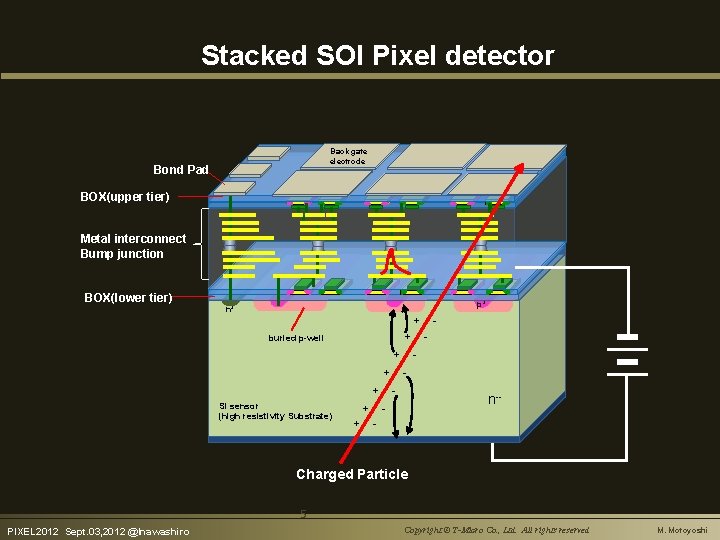

Stacked SOI Pixel detector Back gate electrode Bond Pad BOX(upper tier) Metal interconnect Bump junction BOX(lower tier) p+ n+ + + buried p-well + + + Si sensor (high resistivity Substrate) + + - - - n-- - Charged Particle 5 PIXEL 2012 Sept. 03, 2012 @Inawashiro Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

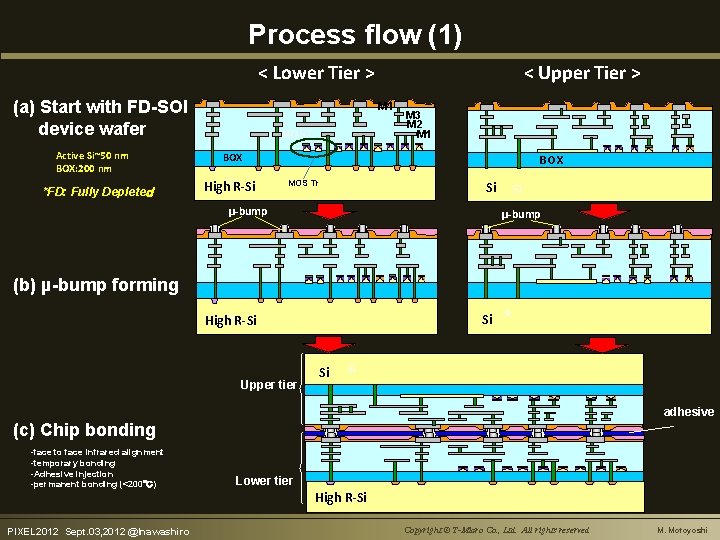

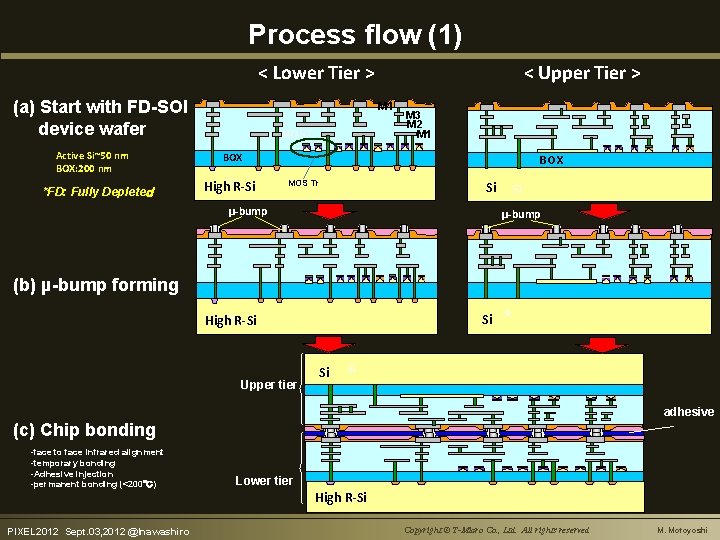

Process flow (1) < Lower Tier > (a) Start with FD-SOI device wafer Active Si~50 nm BOX: 200 nm *FD: Fully Depleted < Upper Tier > M 4 MOST M 3 M 2 M 1 BOX High. Si. R-Si BOX MOS Tr Si µ-bump (b) µ-bump forming Si High. Si. R-Si Upper tier Si Si Si adhesive (c) Chip bonding -face to face infrared alignment -temporary bonding -Adhesive injection -permanent bonding (<200℃) PIXEL 2012 Sept. 03, 2012 @Inawashiro Lower tier Si High R-Si Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

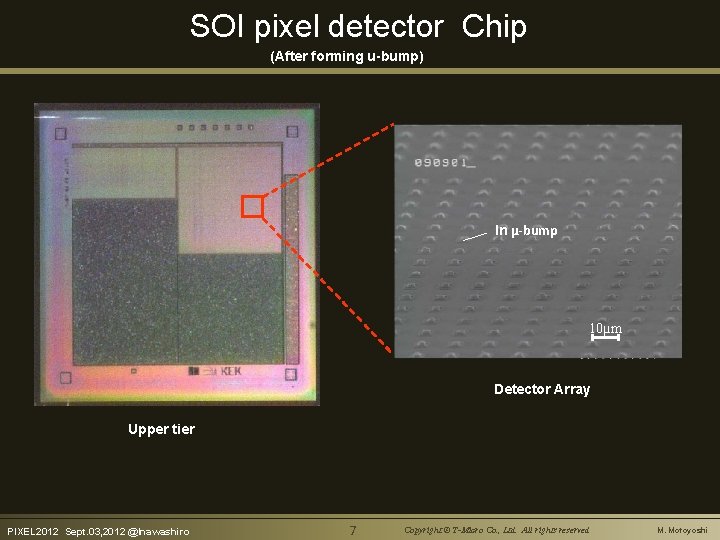

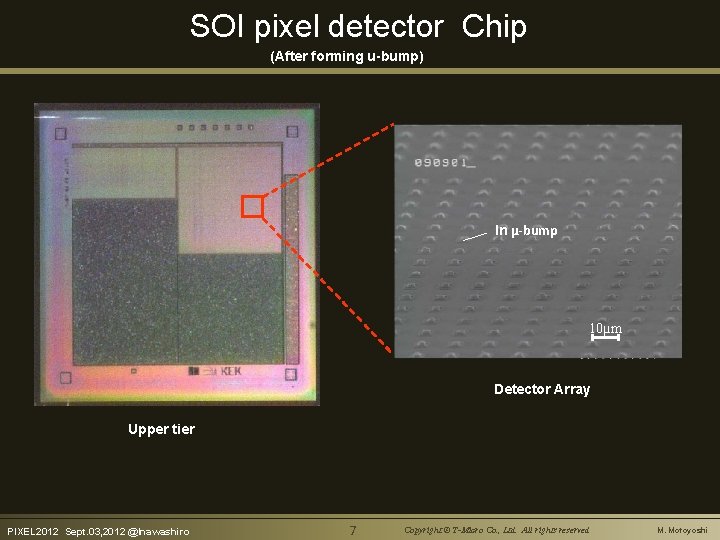

SOI pixel detector Chip (After forming u-bump) In μ-bump 10µm Detector Array Upper tier PIXEL 2012 Sept. 03, 2012 @Inawashiro 7 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

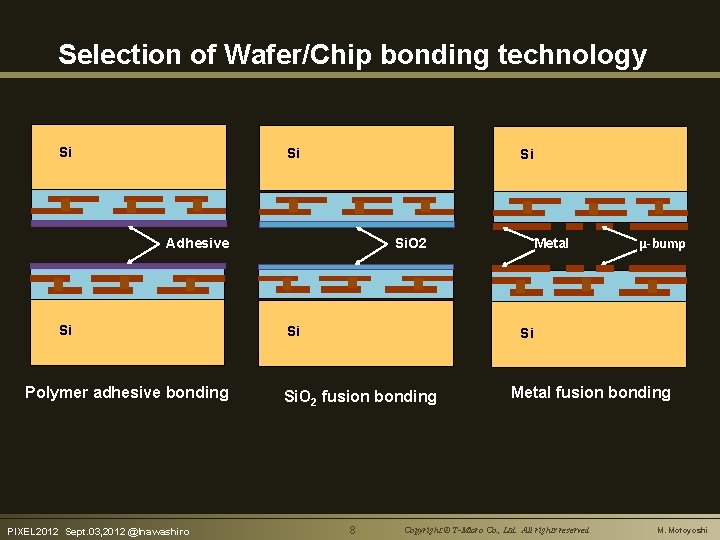

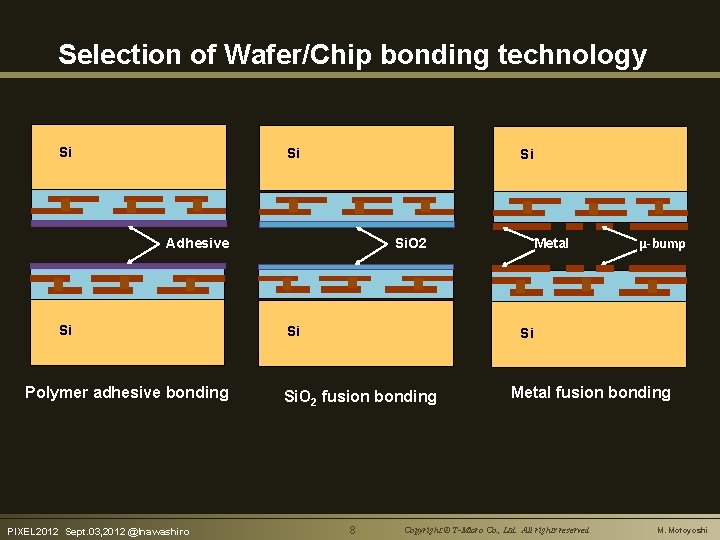

Selection of Wafer/Chip bonding technology Si Si Si Adhesive Si Polymer adhesive bonding PIXEL 2012 Sept. 03, 2012 @Inawashiro Si. O 2 Si Metal μ-bump Si Si. O 2 fusion bonding 8 Metal fusion bonding Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

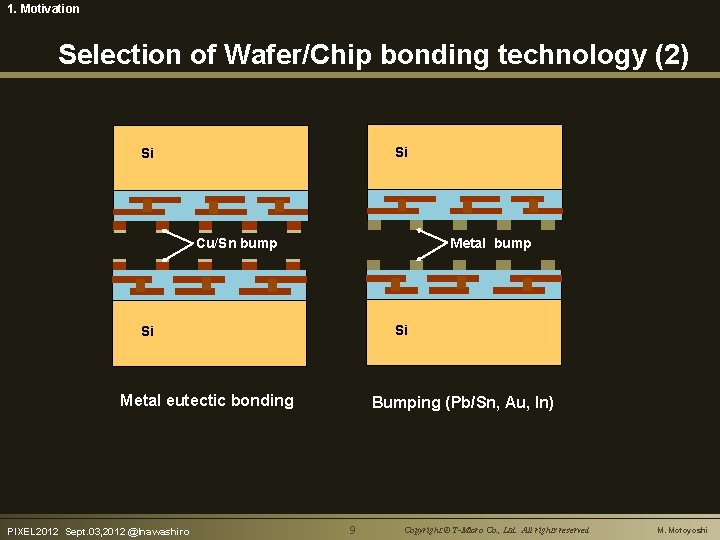

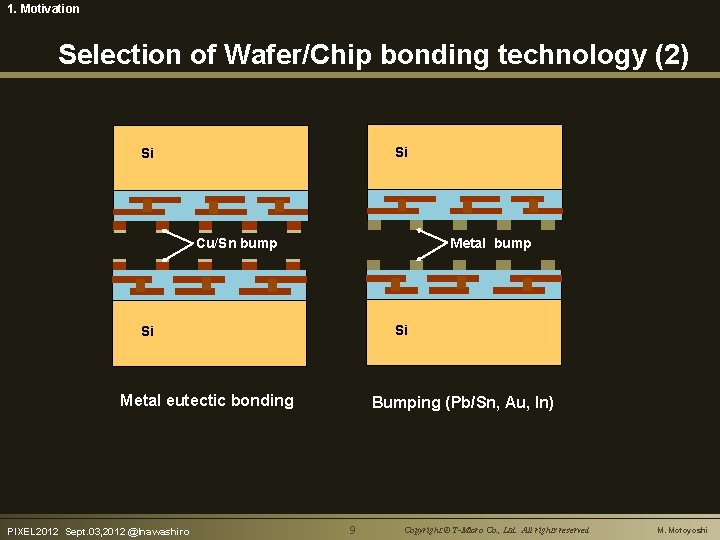

1. Motivation Selection of Wafer/Chip bonding technology (2) Si Si Metal bump Cu/Sn bump Si Si Metal eutectic bonding PIXEL 2012 Sept. 03, 2012 @Inawashiro Bumping (Pb/Sn, Au, In) 9 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

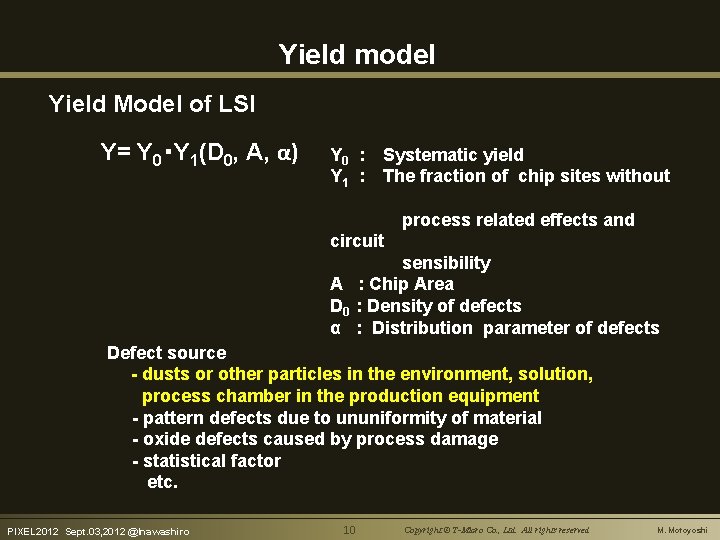

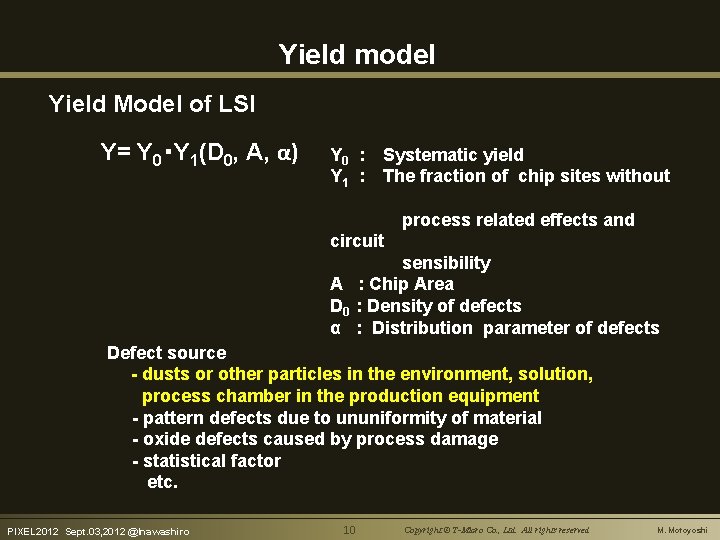

Yield model Yield Model of LSI Y= Y 0・Y 1(D 0, A, α) Y 0 : Systematic yield Y 1 : The fraction of chip sites without process related effects and circuit sensibility A : Chip Area D 0 : Density of defects α : Distribution parameter of defects Defect source - dusts or other particles in the environment, solution, process chamber in the production equipment - pattern defects due to ununiformity of material - oxide defects caused by process damage - statistical factor etc. PIXEL 2012 Sept. 03, 2012 @Inawashiro 10 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

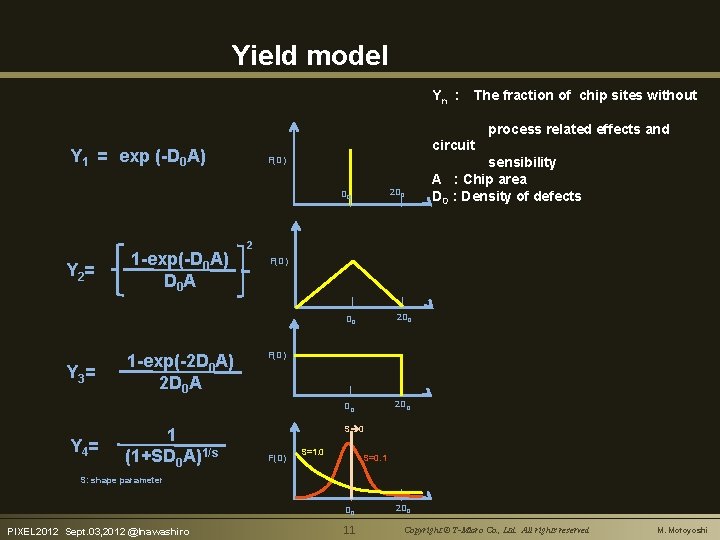

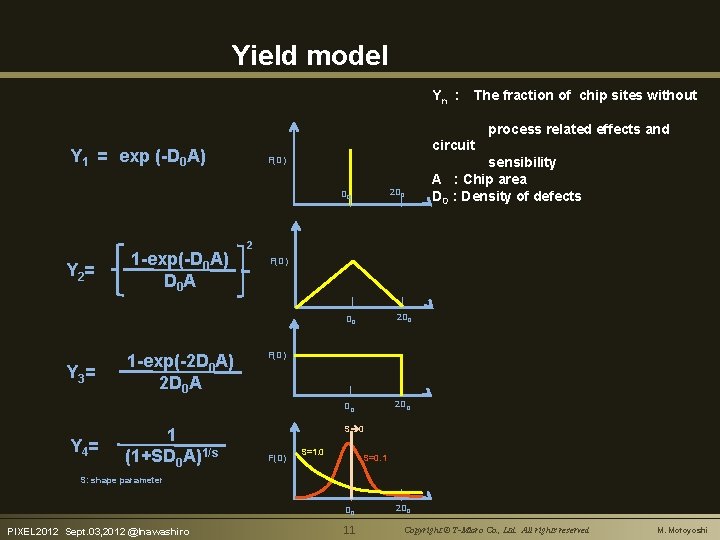

Yield model Y 1 = exp (-D 0 A) F(D) 2 D 0 Y 2= Y 3= Y 4= 1 -exp(-D 0 A) D 0 A 1 -exp(-2 D 0 A) 2 D 0 A 1 (1+SD 0 A)1/s Yn : The fraction of chip sites without process related effects and circuit sensibility A : Chip area D 0 : Density of defects 2 F(D) D 0 2 D 0 F(D) S=1. 0 S=0. 1 S: shape parameter D 0 PIXEL 2012 Sept. 03, 2012 @Inawashiro 11 2 D 0 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

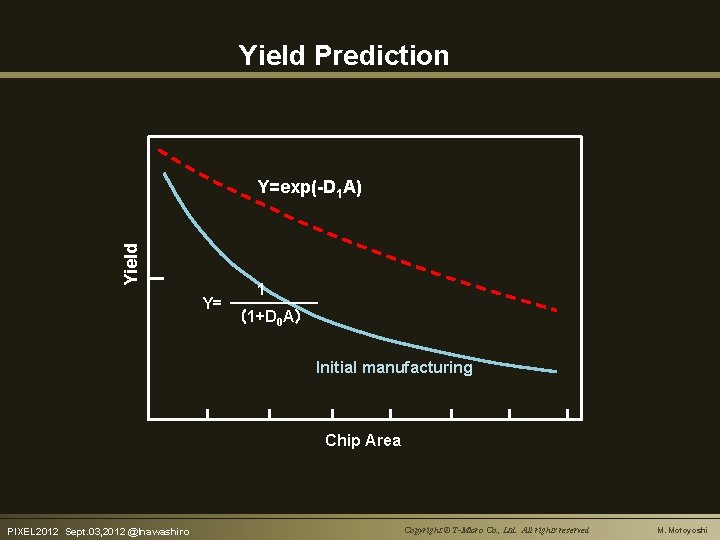

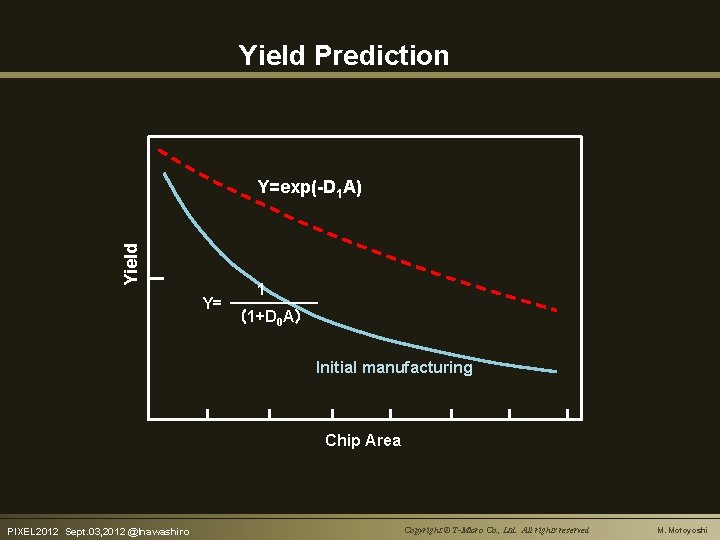

Yield Prediction Yield Y=exp(-D 1 A) Y= 1 (1+D 0 A) Initial manufacturing Chip Area PIXEL 2012 Sept. 03, 2012 @Inawashiro Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

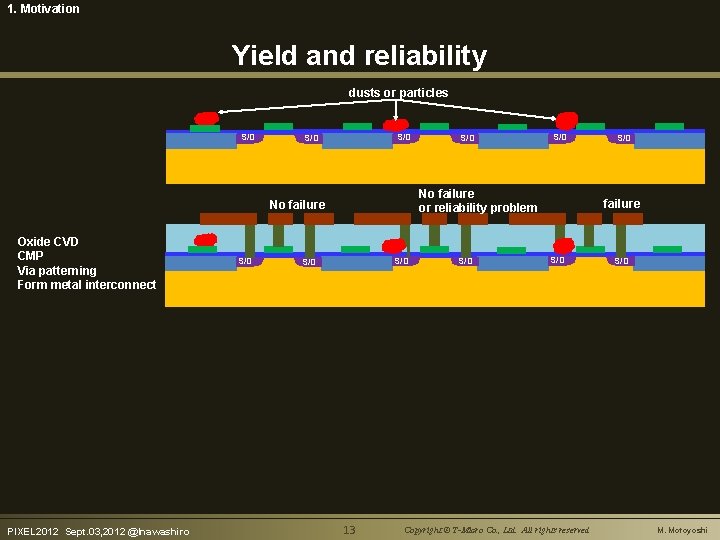

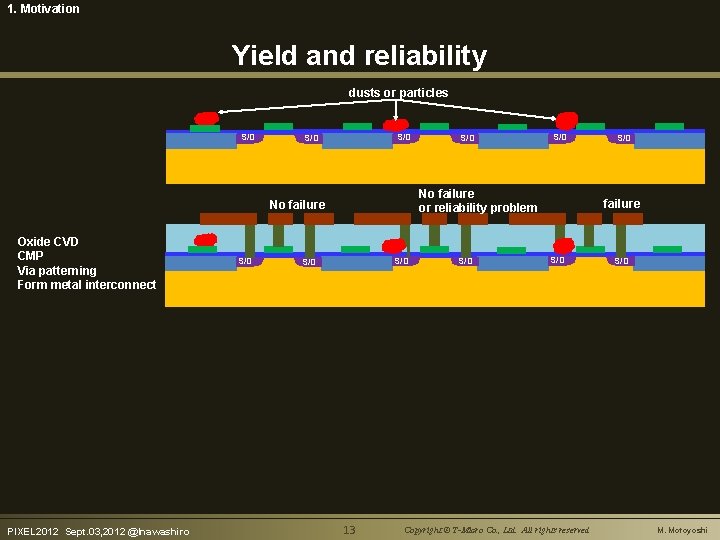

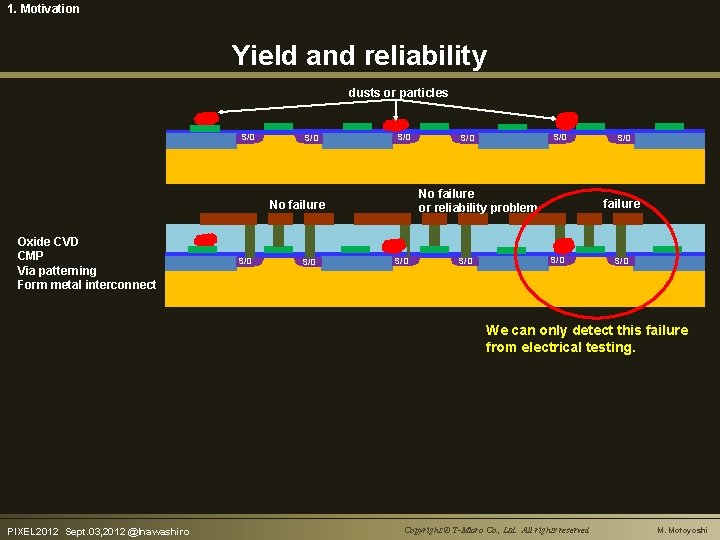

1. Motivation Yield and reliability dusts or particles S/D S/D PIXEL 2012 Sept. 03, 2012 @Inawashiro S/D No failure or reliability problem No failure Oxide CVD CMP Via patterning Form metal interconnect S/D S/D 13 S/D failure S/D Copyright © T-Micro Co. , Ltd. All rights reserved S/D M. Motoyoshi

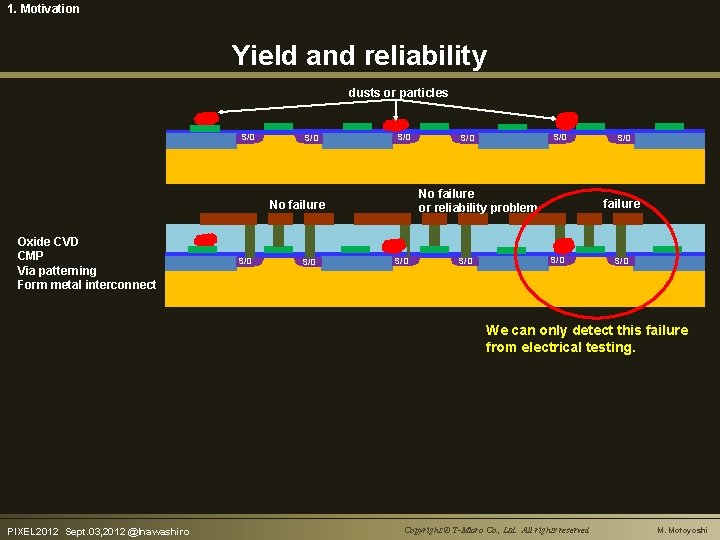

1. Motivation Yield and reliability dusts or particles S/D S/D No failure or reliability problem No failure Oxide CVD CMP Via patterning Form metal interconnect S/D S/D failure S/D We can only detect this failure from electrical testing. PIXEL 2012 Sept. 03, 2012 @Inawashiro Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

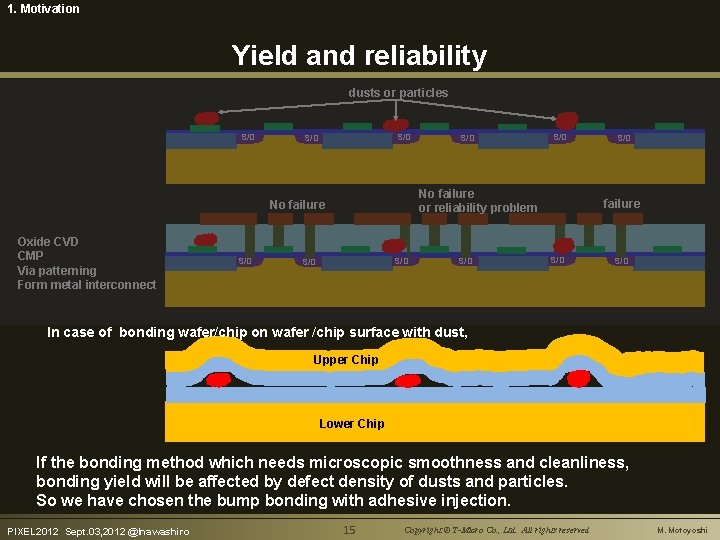

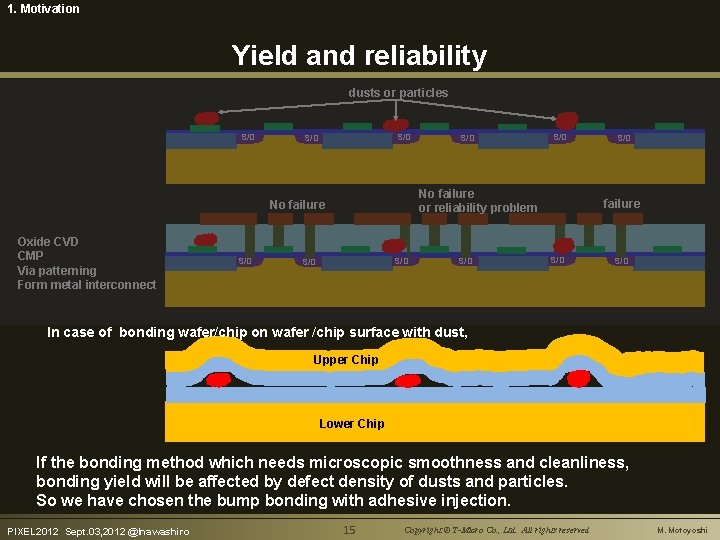

1. Motivation Yield and reliability dusts or particles S/D S/D S/D No failure or reliability problem No failure Oxide CVD CMP Via patterning Form metal interconnect S/D S/D S/D failure S/D In case of bonding wafer/chip on wafer /chip surface with dust, Upper Chip Lower Chip If the bonding method which needs microscopic smoothness and cleanliness, bonding yield will be affected by defect density of dusts and particles. So we have chosen the bump bonding with adhesive injection. PIXEL 2012 Sept. 03, 2012 @Inawashiro 15 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

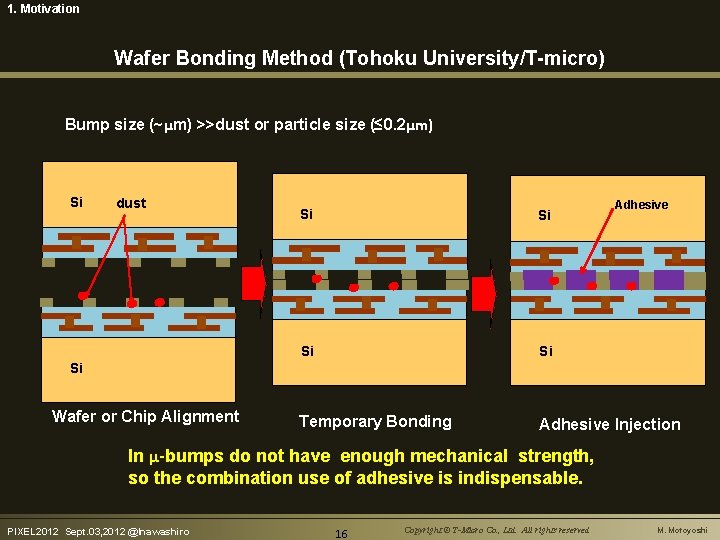

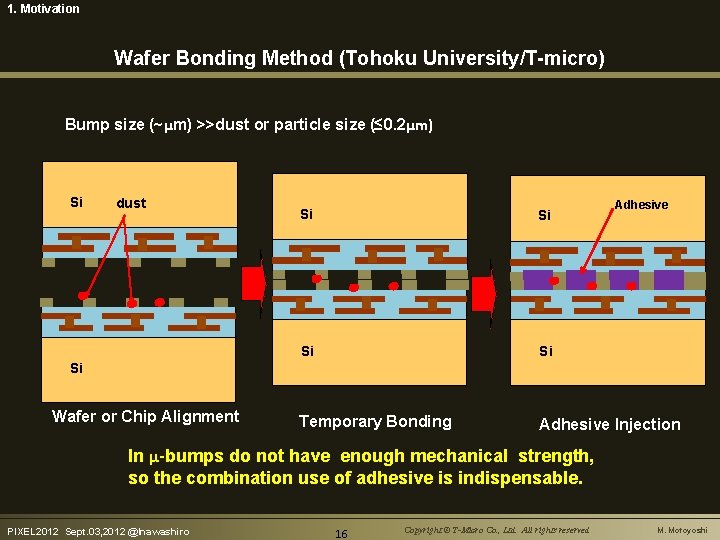

1. Motivation Wafer Bonding Method (Tohoku University/T-micro) Bump size (~μm) >>dust or particle size (≤ 0. 2μm) Si dust Adhesive Si Si Temporary Bonding Adhesive Injection Si Wafer or Chip Alignment In μ-bumps do not have enough mechanical strength, so the combination use of adhesive is indispensable. PIXEL 2012 Sept. 03, 2012 @Inawashiro 16 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

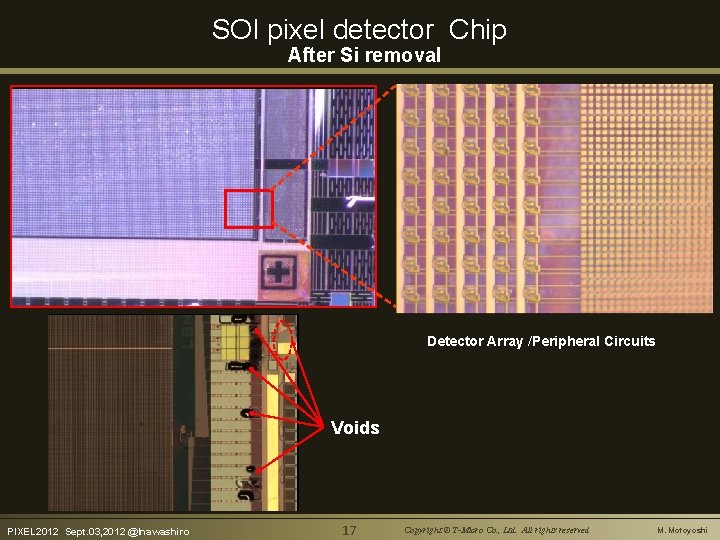

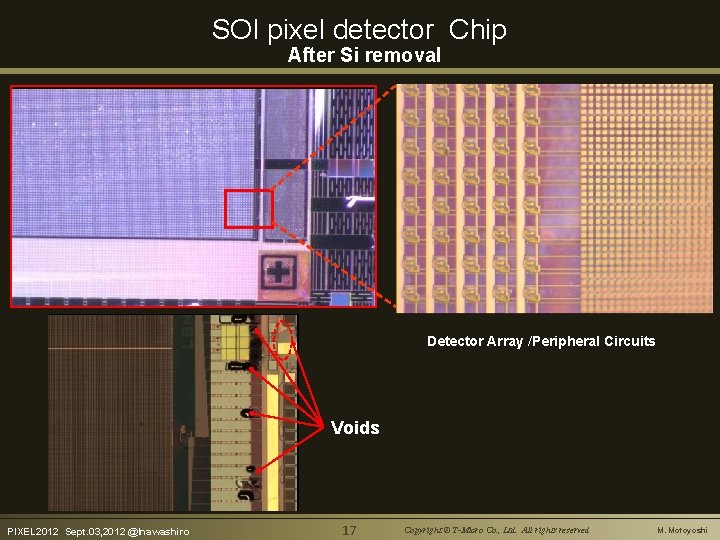

SOI pixel detector Chip After Si removal Detector Array /Peripheral Circuits Voids PIXEL 2012 Sept. 03, 2012 @Inawashiro 17 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

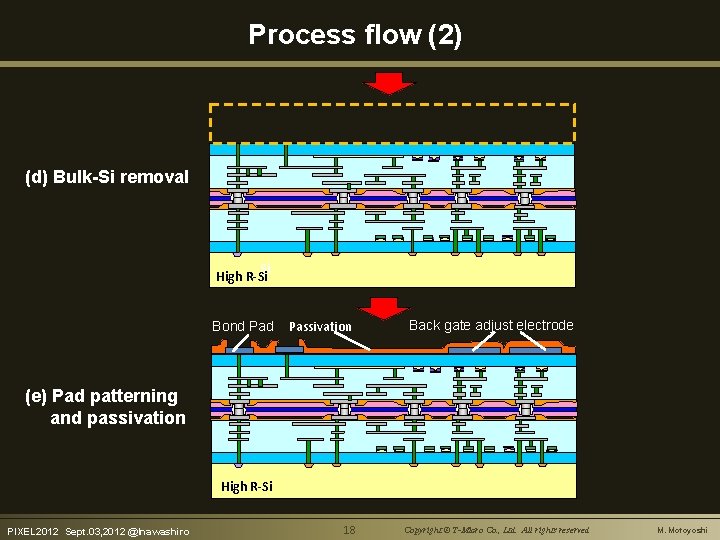

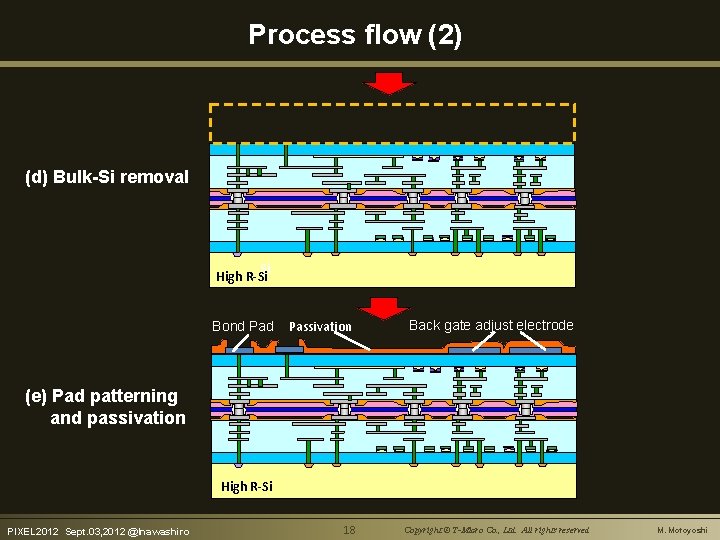

Process flow (2) (d) Bulk-Si removal Si High R-Si Bond Passivation Back gate adjust electrode (e) Pad patterning and passivation High R-Si PIXEL 2012 Sept. 03, 2012 @Inawashiro 18 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

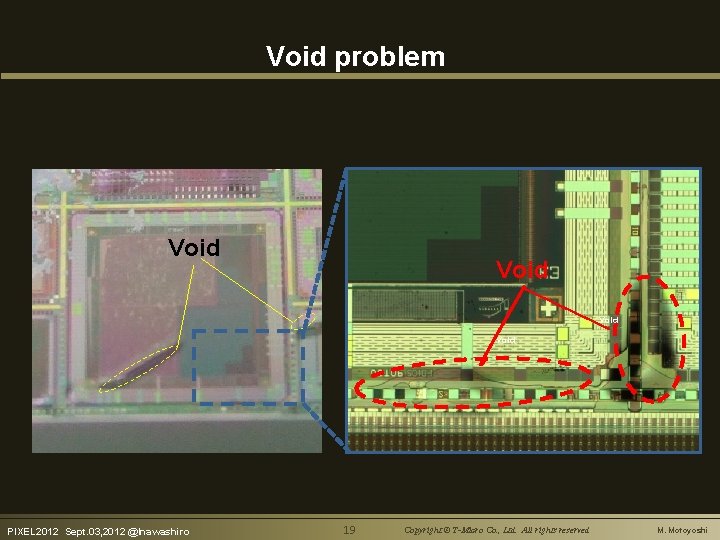

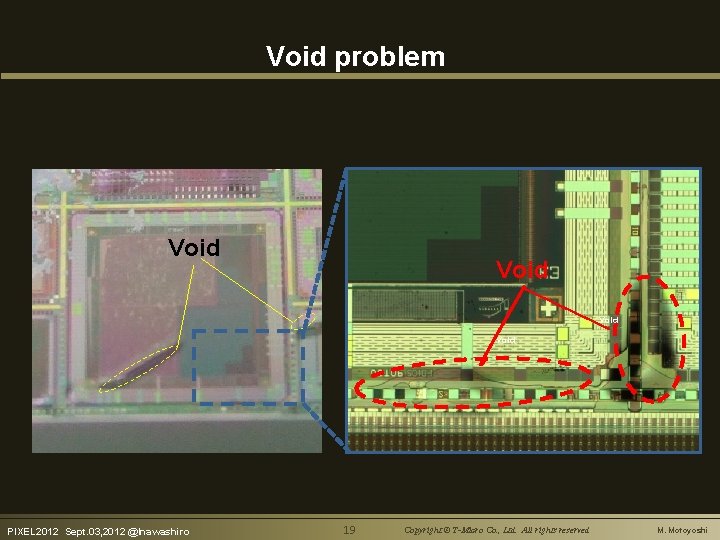

Void problem Void PIXEL 2012 Sept. 03, 2012 @Inawashiro 19 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

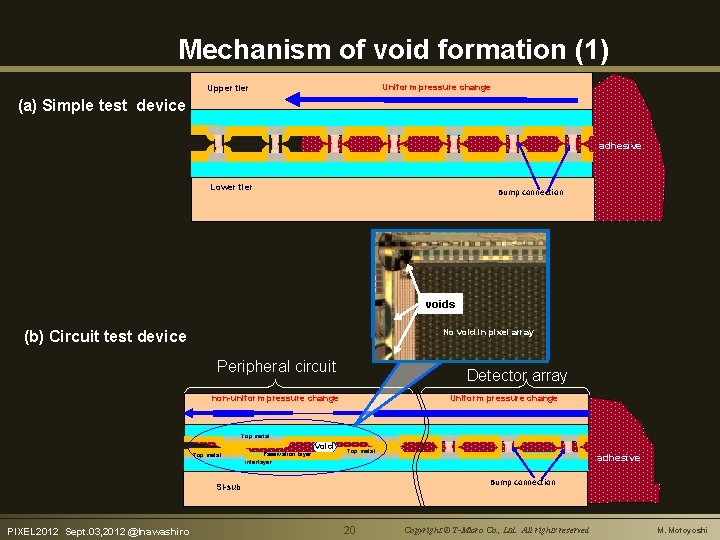

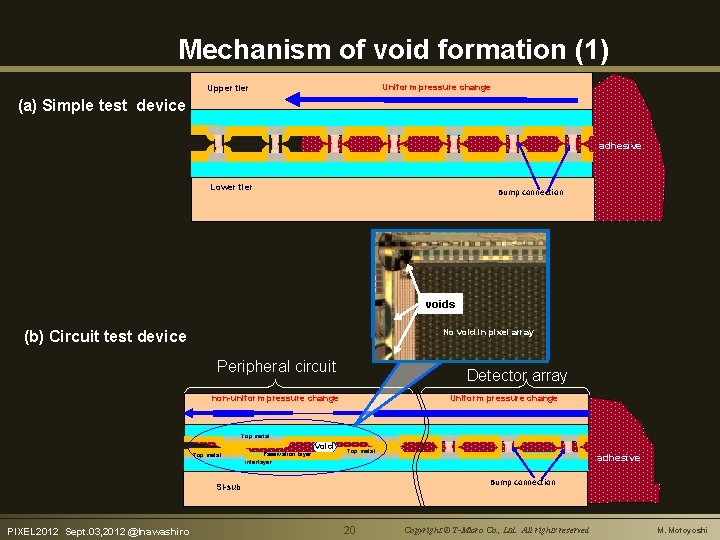

Mechanism of void formation (1) Uniform pressure change Upper tier (a) Simple test device adhesive Lower tier Bump connection voids No void in pixel array (b) Circuit test device Peripheral circuit Detector array non-uniform pressure change Uniform pressure change Top metal Passivation layer interlayer void Top metal Bump connection Si-sub PIXEL 2012 Sept. 03, 2012 @Inawashiro adhesive 20 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

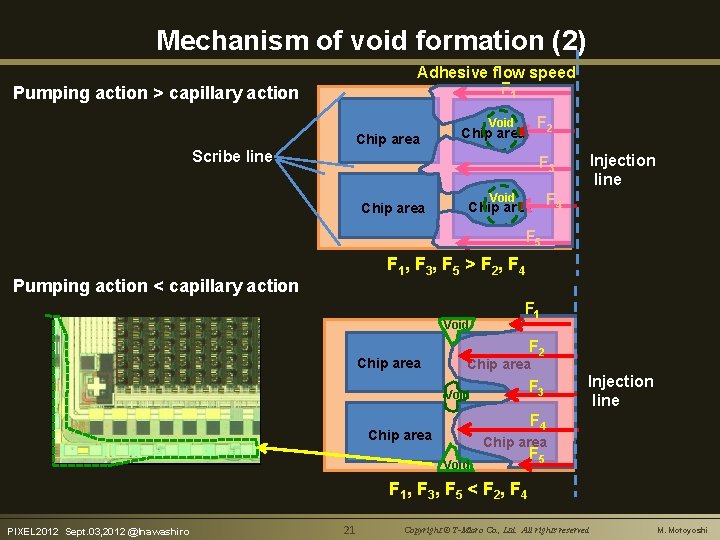

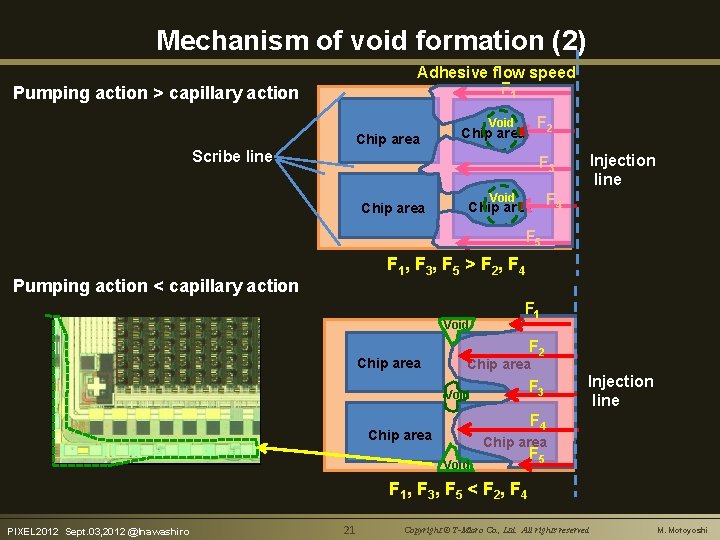

Mechanism of void formation (2) Adhesive flow speed F 1 Pumping action > capillary action F 2 Void Chip area Scribe line F 3 Chip area Void Chip area Injection line F 4 F 5 F 1 , F 3 , F 5 > F 2 , F 4 Pumping action < capillary action Void Chip area F 1 F 2 Chip area F 3 Void Injection line F 4 Chip area Void F 5 F 1 , F 3 , F 5 < F 2 , F 4 PIXEL 2012 Sept. 03, 2012 @Inawashiro 21 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

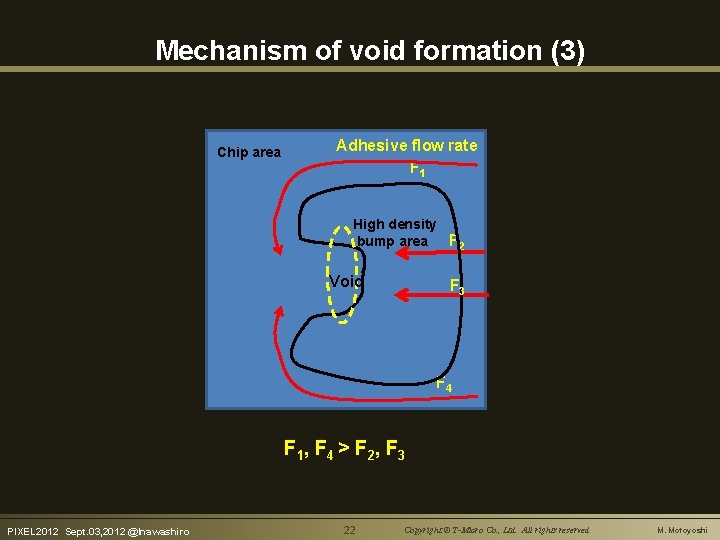

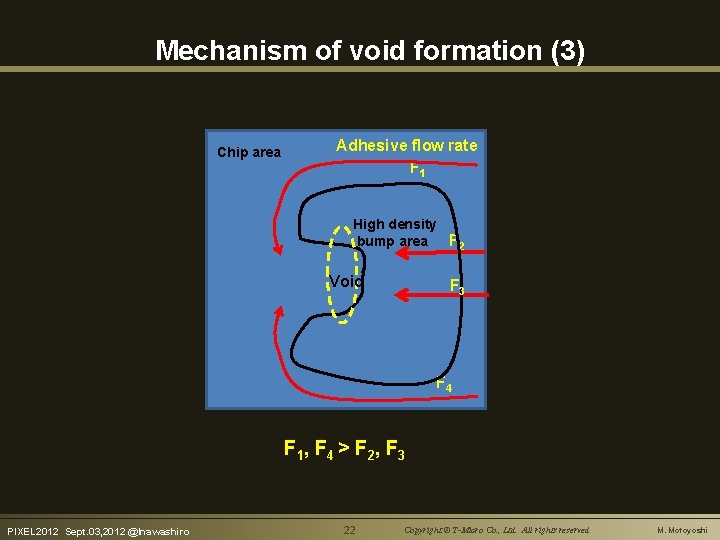

Mechanism of void formation (3) Chip area Adhesive flow rate F 1 High density F 2 bump area Void F 3 F 4 F 1 , F 4 > F 2 , F 3 PIXEL 2012 Sept. 03, 2012 @Inawashiro 22 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

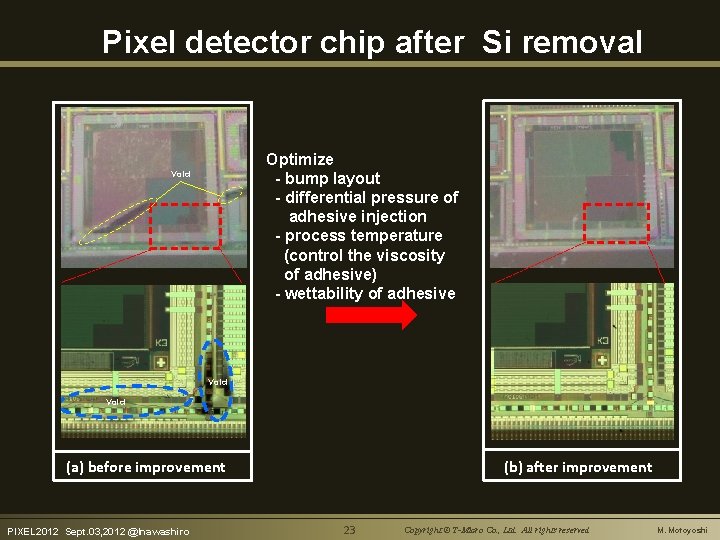

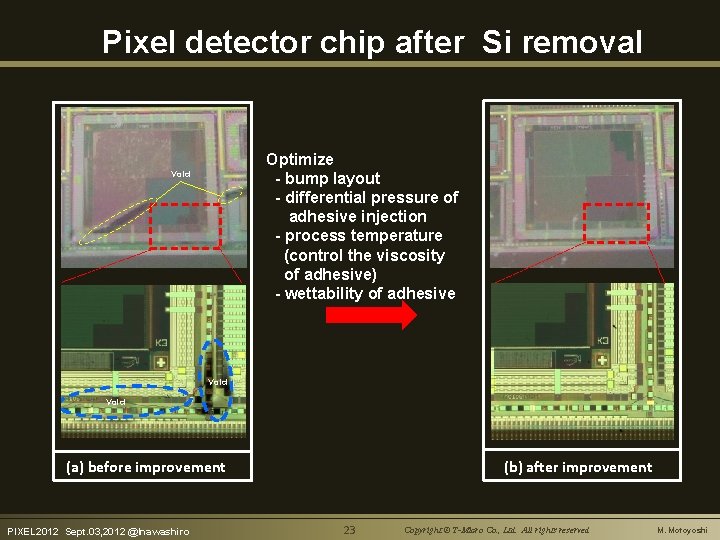

Pixel detector chip after Si removal Optimize - bump layout - differential pressure of adhesive injection - process temperature (control the viscosity of adhesive) - wettability of adhesive Void (a) before improvement PIXEL 2012 Sept. 03, 2012 @Inawashiro (b) after improvement 23 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

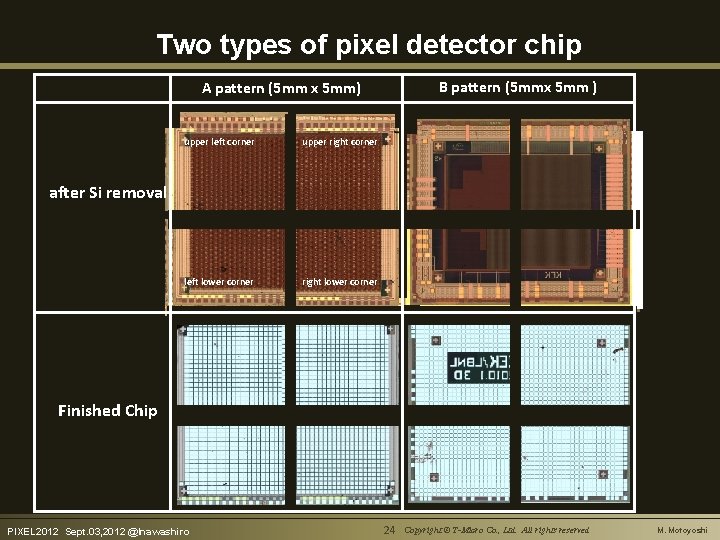

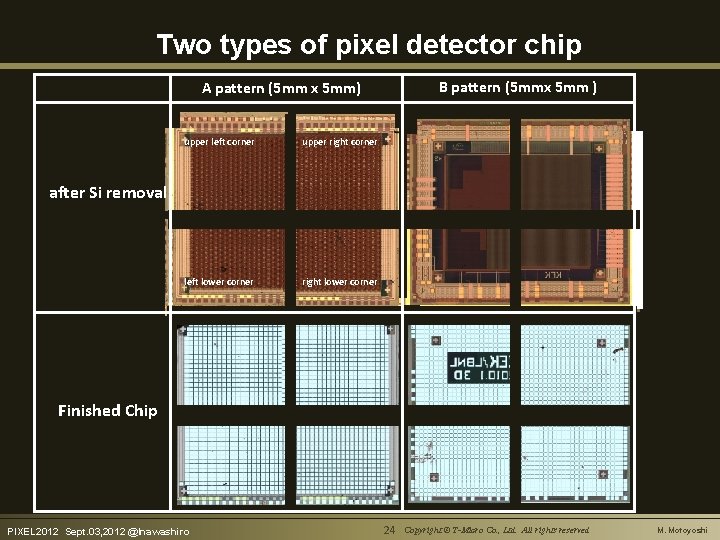

Two types of pixel detector chip B pattern (5 mmx 5 mm ) A pattern (5 mm x 5 mm) upper left corner upper right corner left lower corner right lower corner after Si removal Finished Chip PIXEL 2012 Sept. 03, 2012 @Inawashiro 24 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

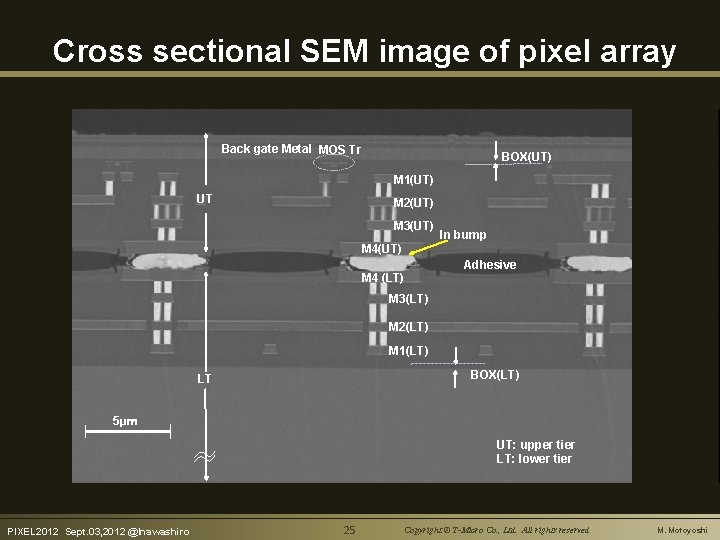

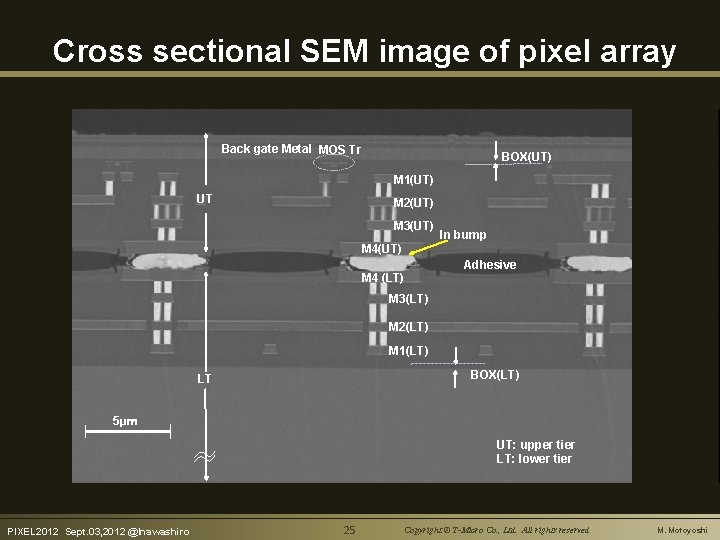

Cross sectional SEM image of pixel array Back gate Metal MOS Tr BOX(UT) M 1(UT) UT M 2(UT) M 3(UT) In bump M 4(UT) M 4 (LT) Adhesive M 3(LT) M 2(LT) M 1(LT) BOX(LT) LT 5μm UT: upper tier LT: lower tier PIXEL 2012 Sept. 03, 2012 @Inawashiro 25 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

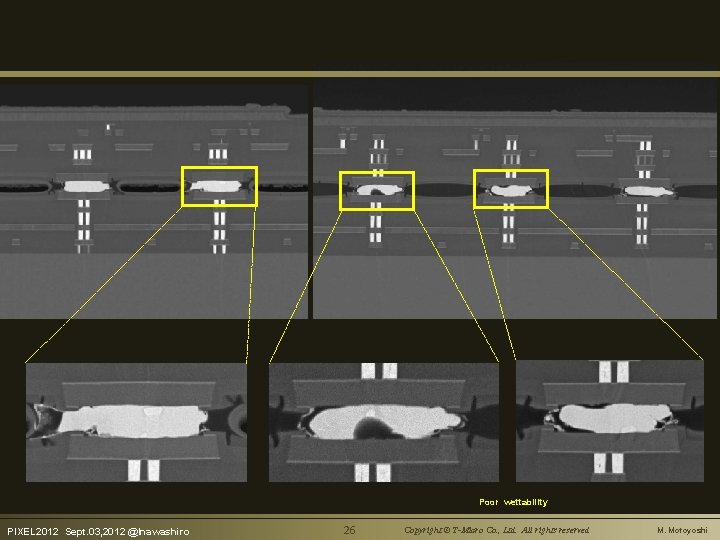

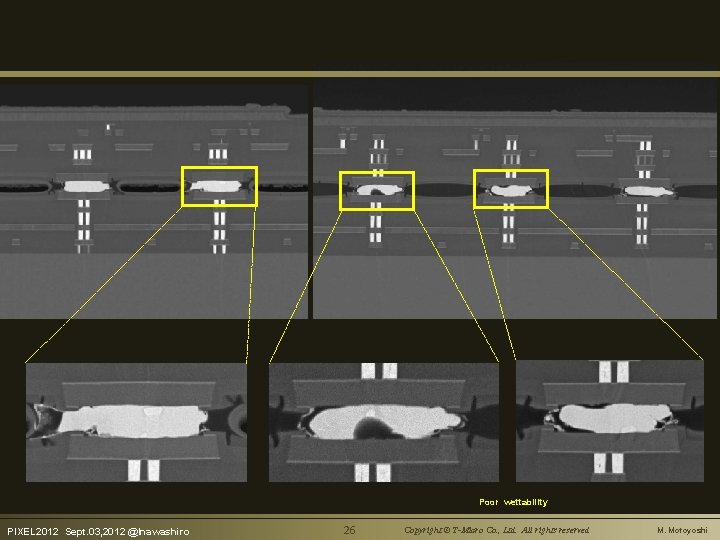

Poor wettability PIXEL 2012 Sept. 03, 2012 @Inawashiro 26 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

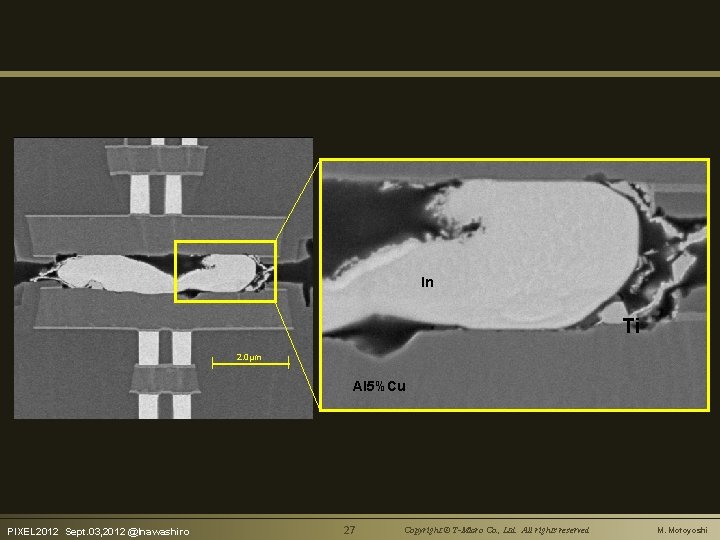

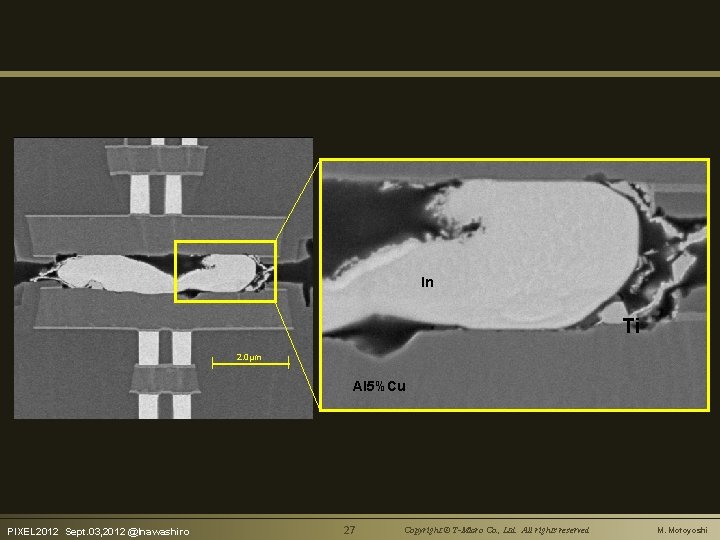

In Ti 2. 0μm Al 5%Cu PIXEL 2012 Sept. 03, 2012 @Inawashiro 27 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

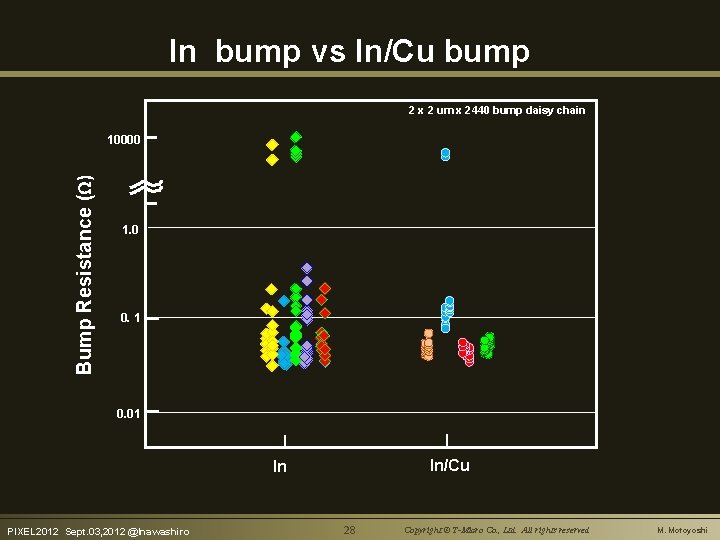

In bump vs In/Cu bump 2 x 2 um x 2440 bump daisy chain Bump Resistance (Ω) 10000 1. 0 0. 1 0. 01 In/Cu In PIXEL 2012 Sept. 03, 2012 @Inawashiro 28 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

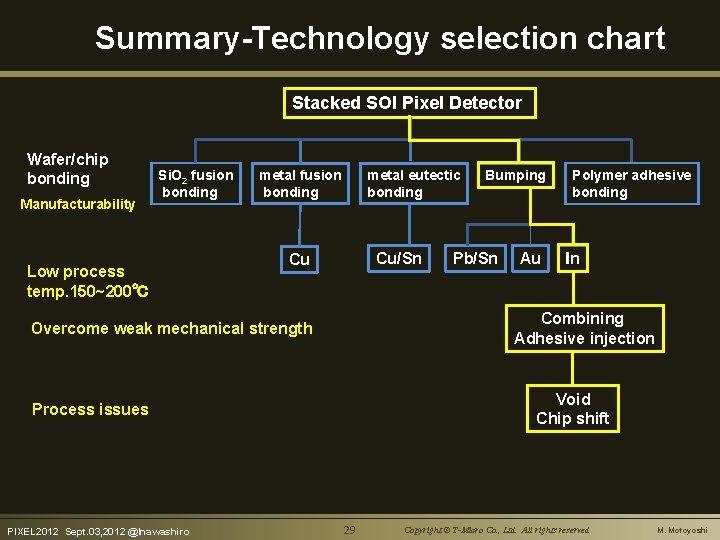

Summary-Technology selection chart Stacked SOI Pixel Detector Wafer/chip bonding Manufacturability Si. O 2 fusion bonding Low process temp. 150~200℃ metal fusion bonding metal eutectic bonding Cu/Sn Cu Pb/Sn Au Polymer adhesive bonding In Combining Adhesive injection Overcome weak mechanical strength Void Chip shift Process issues PIXEL 2012 Sept. 03, 2012 @Inawashiro Bumping 29 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

Prototype of 8” Self-Assembled Chip Bonder PIXEL 2012 Sept. 03, 2012 @Inawashiro Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

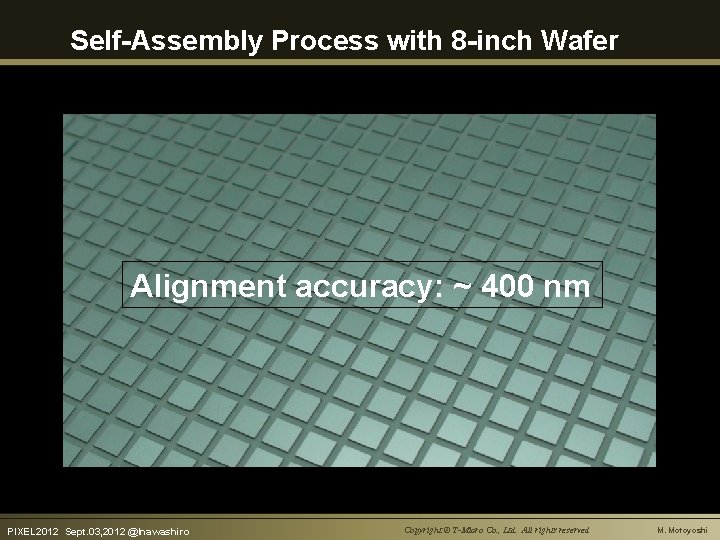

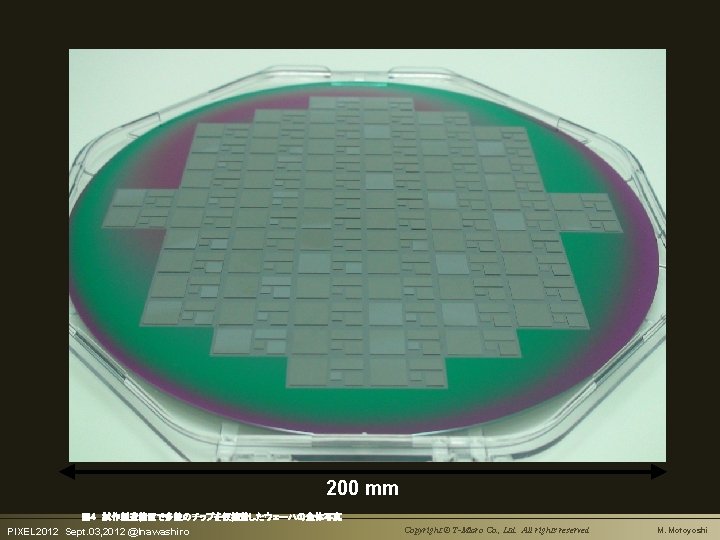

Self-Assembly Process with 8 -inch Wafer Simultaneously picked-up 500 chips (5 mm× 5 mm) Multi-chip pick-up plate KGD Liquid 180 mm KGDs Self-assembled KGDs Alignment accuracy: ~ 400 nm Chip release Self-assembly Hydrophilic bonding area 150 mm Liquid on hydrophilic area formed on the wafer A large number of self-assembled chips Liquid array on an 8 -inch wafer PIXEL 2012 Sept. 03, 2012 @Inawashiro 50 m m Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

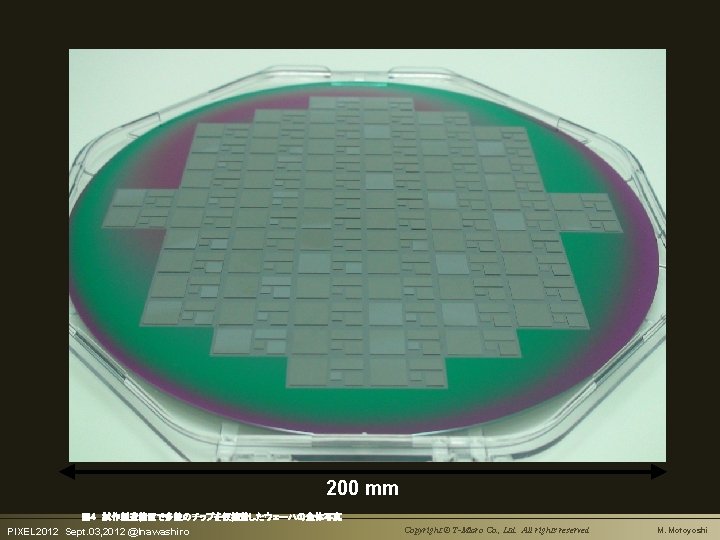

200 mm 図4 試作製造装置で多数のチップを仮接着したウェーハの全体写真 PIXEL 2012 Sept. 03, 2012 @Inawashiro Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi

Conclusion - 3 D LSI Integration technology using minimum 5μm pitch bump is verified using SOI stacked pixel detector as circuit level test device. - In this technology, adhesive injection is found the key technology. Optimizing layout, process parameter and adhesive injection method, this process have completed without void. - The dispersion of bump resistance is still high, the following optimization are still ongoing. Improvement of wettability between bump and pad Introducing the new Cu/In IMC bonding - In further development of wafer /chip bonding with few μm pitch bump , it might be necessary to optimize the gap between tiers and volume of bump metal. PIXEL 2012 Sept. 03, 2012 @Inawashiro 33 Copyright © T-Micro Co. , Ltd. All rights reserved M. Motoyoshi