TM Case Study Complex MultiCore Virtual Platform Enablement

TM Case Study: Complex Multi-Core Virtual Platform Enablement Using TLM 2. 0 to cosimulate Diverse Simulation Models in a Multithreaded Environment April 9, 2012 Navaneet Kumar, Sandeep Jain, Rajesh Jain Networking & Multimedia Solutions Group Updated Jan 2012 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc. .

Outline • • • Virtual Platform – Challenges & Requirement Significance of TLM 2. 0 TLM LT Methodology TLM LT Adapter Moving to Multi -Threading Challenges and Learning’s of Multi-Threading Challenges and Learning’s of DMI Performance result Conclusion References TM 2 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

Virtual Platform – Challenges & Requirement • So. Cs are becoming more complex day by day − • High-fidelity models developed by different divisions and teams in a large organization follow diverse modeling framework − • Porting all the complex models to a common modeling framework is no easy task Timely availability of Virtual Platform is critical − • Today’s So. C contain multiple heterogeneous cores, hardware accelerators, peripherals, complex memory hierarchy with hardware supported coherency Useful for Software driver development A common methodology and infrastructure is required − To enable interoperability of such diverse simulation models − To demonstrate quick virtual platform integration and co-simulation TM 3 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

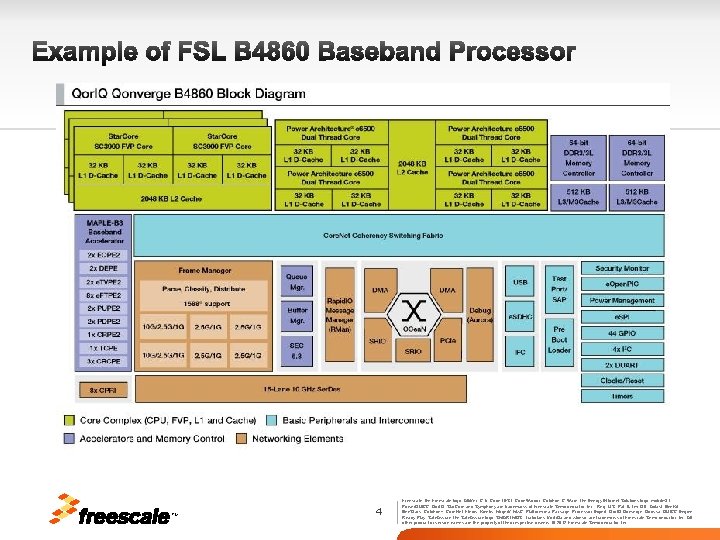

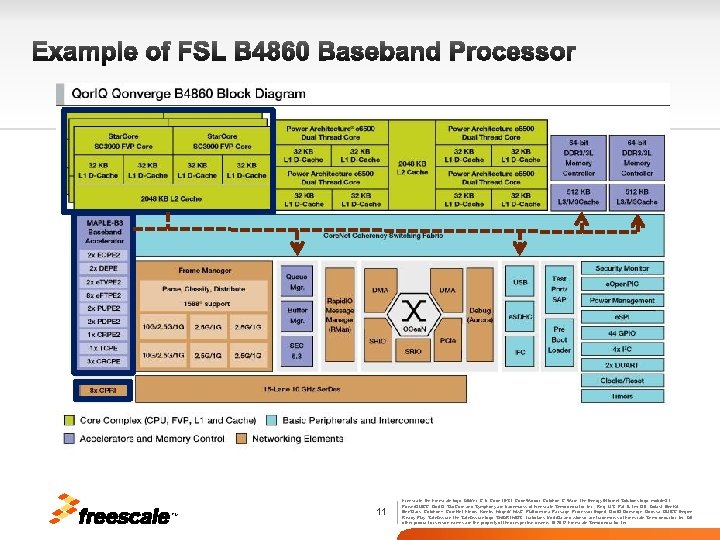

Example of FSL B 4860 Baseband Processor TM 4 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

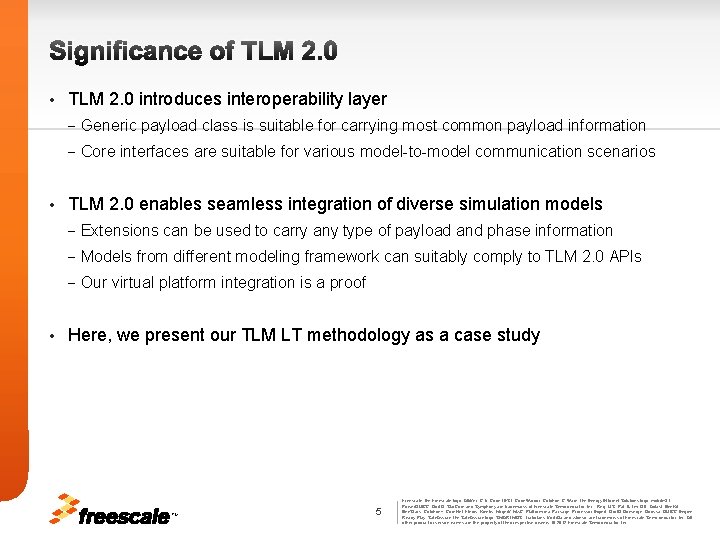

Significance of TLM 2. 0 • • • TLM 2. 0 introduces interoperability layer − Generic payload class is suitable for carrying most common payload information − Core interfaces are suitable for various model-to-model communication scenarios TLM 2. 0 enables seamless integration of diverse simulation models − Extensions can be used to carry any type of payload and phase information − Models from different modeling framework can suitably comply to TLM 2. 0 APIs − Our virtual platform integration is a proof Here, we present our TLM LT methodology as a case study TM 5 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

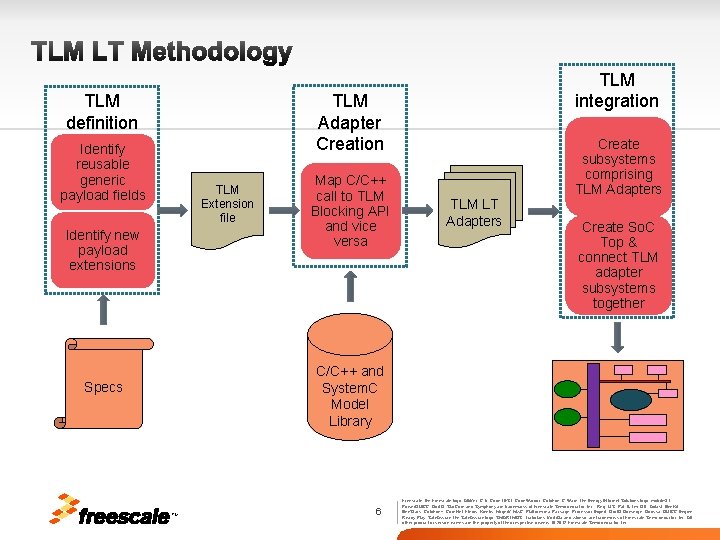

TLM LT Methodology TLM integration TLM Adapter Creation TLM definition Identify reusable generic payload fields TLM Extension file Identify new payload extensions Map C/C++ call to TLM Blocking API and vice versa TLM LT Adapters Create subsystems comprising TLM Adapters Create So. C Top & connect TLM adapter subsystems together C/C++ and System. C Model Library Specs TM 6 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

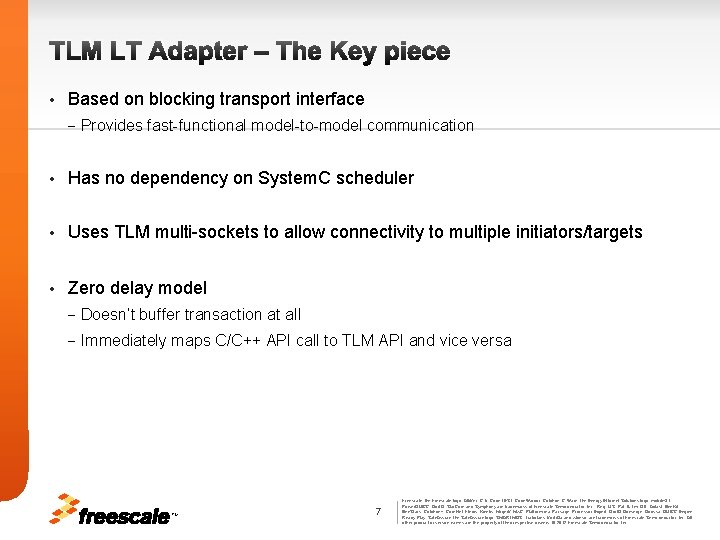

TLM LT Adapter – The Key piece • Based on blocking transport interface − Provides fast-functional model-to-model communication • Has no dependency on System. C scheduler • Uses TLM multi-sockets to allow connectivity to multiple initiators/targets • Zero delay model − Doesn’t buffer transaction at all − Immediately maps C/C++ API call to TLM API and vice versa TM 7 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

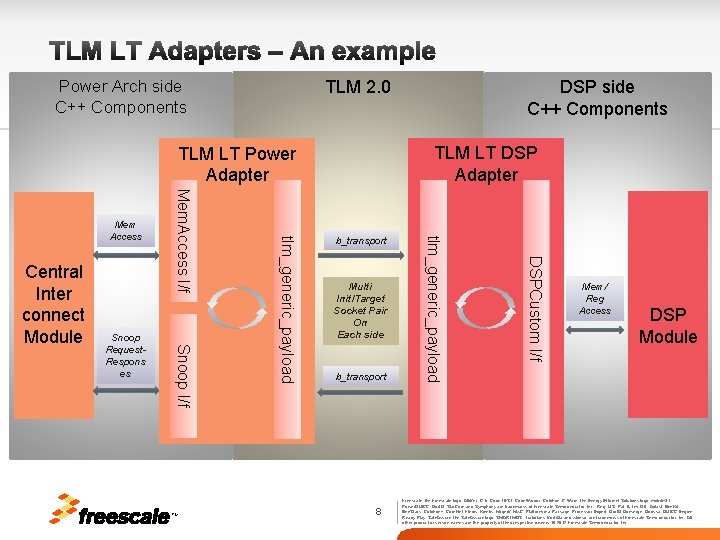

TLM LT Adapters – An example TLM 2. 0 Power Arch side C++ Components TLM LT DSP Adapter TLM LT Power Adapter b_transport 8 DSPCustom I/f Multi Init/Target Socket Pair On Each side tlm_generic_payload TM tlm_generic_payload Snoop Request. Respons es Snoop I/f Central Inter connect Module Mem. Access I/f Mem Access DSP side C++ Components Mem/ Reg Access DSP Module Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

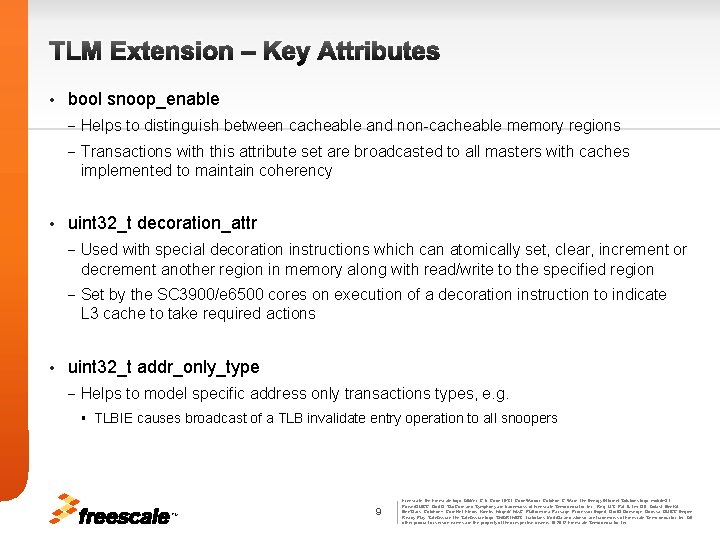

TLM Extension – Key Attributes • • • bool snoop_enable − Helps to distinguish between cacheable and non-cacheable memory regions − Transactions with this attribute set are broadcasted to all masters with caches implemented to maintain coherency uint 32_t decoration_attr − Used with special decoration instructions which can atomically set, clear, increment or decrement another region in memory along with read/write to the specified region − Set by the SC 3900/e 6500 cores on execution of a decoration instruction to indicate L 3 cache to take required actions uint 32_t addr_only_type − Helps to model specific address only transactions types, e. g. § TLBIE causes broadcast of a TLB invalidate entry operation to all snoopers TM 9 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

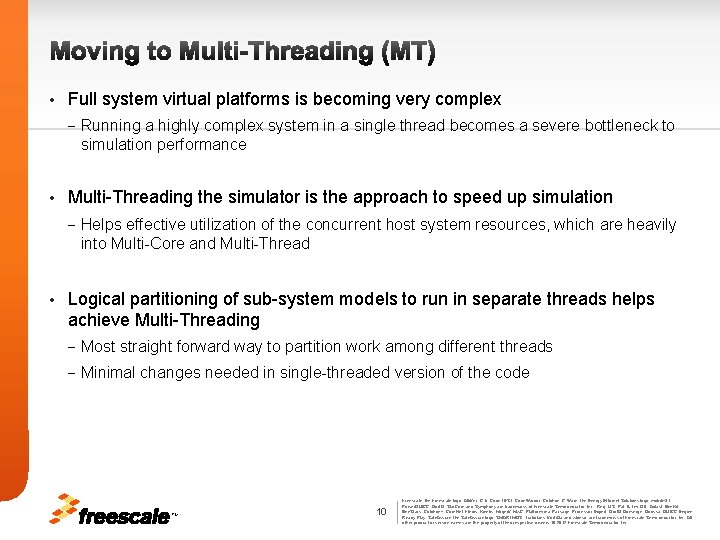

Moving to Multi-Threading (MT) • Full system virtual platforms is becoming very complex − • Multi-Threading the simulator is the approach to speed up simulation − • Running a highly complex system in a single thread becomes a severe bottleneck to simulation performance Helps effective utilization of the concurrent host system resources, which are heavily into Multi-Core and Multi-Thread Logical partitioning of sub-system models to run in separate threads helps achieve Multi-Threading − Most straight forward way to partition work among different threads − Minimal changes needed in single-threaded version of the code TM 10 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

Example of FSL B 4860 Baseband Processor TM 11 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

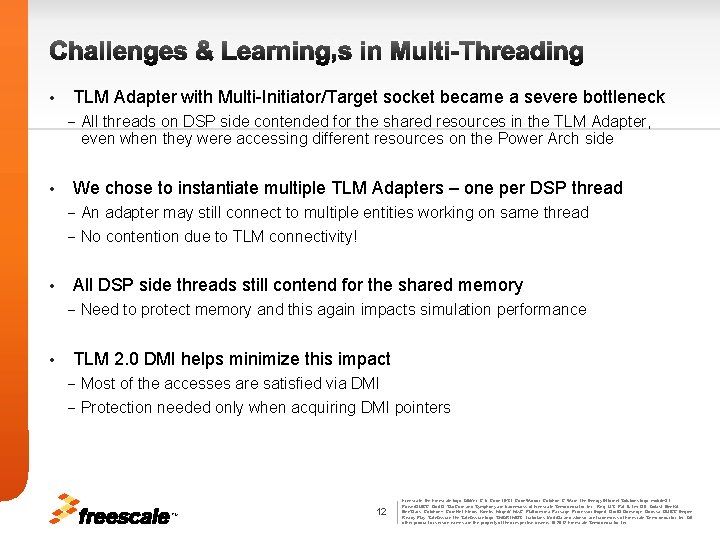

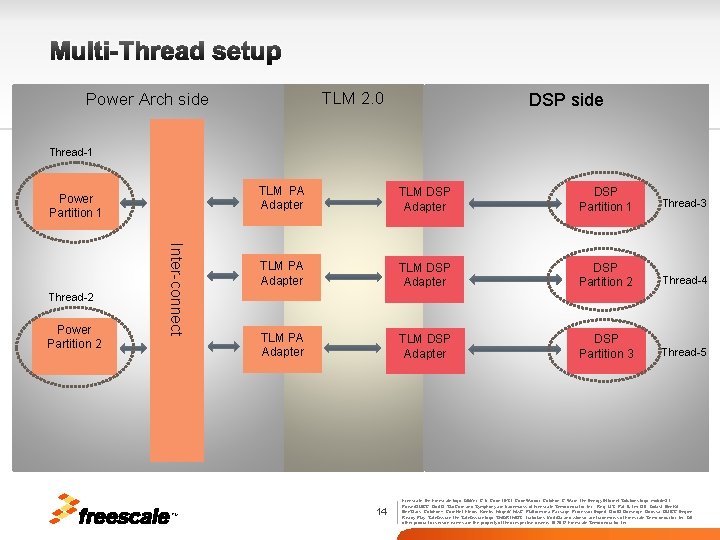

Challenges & Learning’s in Multi-Threading • TLM Adapter with Multi-Initiator/Target socket became a severe bottleneck − • All threads on DSP side contended for the shared resources in the TLM Adapter, even when they were accessing different resources on the Power Arch side We chose to instantiate multiple TLM Adapters – one per DSP thread An adapter may still connect to multiple entities working on same thread − No contention due to TLM connectivity! − • All DSP side threads still contend for the shared memory − • Need to protect memory and this again impacts simulation performance TLM 2. 0 DMI helps minimize this impact Most of the accesses are satisfied via DMI − Protection needed only when acquiring DMI pointers − TM 12 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

Challenges and Learning’s with DMI • • DMI should be used cautiously! − Causes any bus snooping capabilities provided by the interconnect model to be bypassed − Certain device models have internal caches and these needs to be kept coherent with the main memory − If a master modifies certain memory region via DMI and if this region is present in one of the cache models, then there is no way keep the system coherent! We employed a mechanism to allow DMI while maintaining coherency − DMI acquire succeeds only if a memory region is not already cached − All requests to cached region go via interconnect model – no DMI, snoop broadcast if asked − Whenever a new region is cached, DMI invalidates is sent to all masters to prevent them from using DMI for such regions TM 13 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

Multi-Thread setup TLM 2. 0 Power Arch side DSP side Thread-1 Power Partition 2 Inter-connect Thread-2 TM TLM PA Adapter TLM DSP Adapter DSP Partition 1 Thread-3 TLM PA Adapter TLM DSP Adapter DSP Partition 2 Thread-4 TLM PA Adapter TLM DSP Adapter DSP Partition 3 Thread-5 14 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

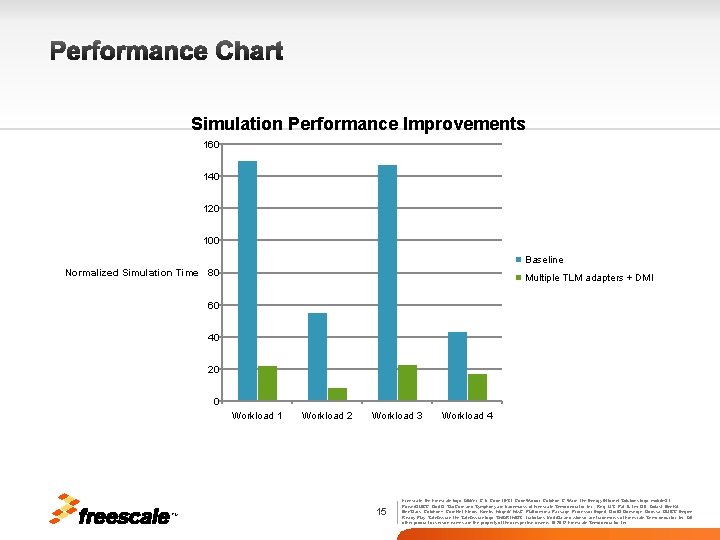

Performance Chart Simulation Performance Improvements 160 140 120 100 Baseline Normalized Simulation Time 80 Multiple TLM adapters + DMI 60 40 20 0 Workload 1 TM Workload 2 Workload 3 15 Workload 4 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

Conclusion • TLM 2. 0 based methodology is a good technique to integrate and co-simulate diverse LT simulation models − • TLM Adapters can be designed and deployed in a smart way that ensures coherency Multi-threading is the way to go − Great speed-up for virtual platform simulation TM 16 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

References • System. C IEEE 1666 -2011 Language Reference Manual • http: //www. freescale. com TM 17 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

Thank You! TM 18 Freescale, the Freescale logo, Alti. Vec, C-5, Code. TEST, Code. Warrior, Cold. Fire, C-Ware, the Energy Efficient Solutions logo, mobile. GT, Power. QUICC, Qor. IQ, Star. Core and Symphony are trademarks of Freescale Semiconductor, Inc. , Reg. U. S. Pat. & Tm. Off. Airfast, Bee. Kit, Bee. Stack, Cold. Fire+, Core. Net, Flexis, Kinetis, Magni. V, MXC, Platform in a Package, Processor Expert, Qor. IQ Qonverge, Qorivva, QUICC Engine, Ready Play, Safe. Assure, the Safe. Assure logo, SMARTMOS, Turbo. Link, Vorti. Qa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

TM

- Slides: 19