TK 2633 Microprocessor Interfacing Lecture 6 Control Instructions

- Slides: 30

TK 2633: Microprocessor & Interfacing Lecture 6: Control Instructions Ass Prof Dr Masri Ayob

OBJECTIVES n n n 12/5/2020 Explain the operation of the unconditional and conditional jump instructions. Describe the flags tested by each conditional jump instruction. Explain the operation of the unconditional and conditional call and return instructions. Show the stack functions when used by the call and return instructions. Describe the operation of the instructions: NOP, RST, STC, CMC, RIM, SIM, and HLT. Prepared by: Dr Masri Ayob 2

Control Instructions n n Allow computers to make decisions and change the flow of the programme based on the results outcome. Two main forms: n n 12/5/2020 JUMP instructions: n Allow programme to jump to any memory locations. CALL instructions n Allow a group of instructions (subroutine) to be reused by the program in many different places. Prepared by: Dr Masri Ayob 3

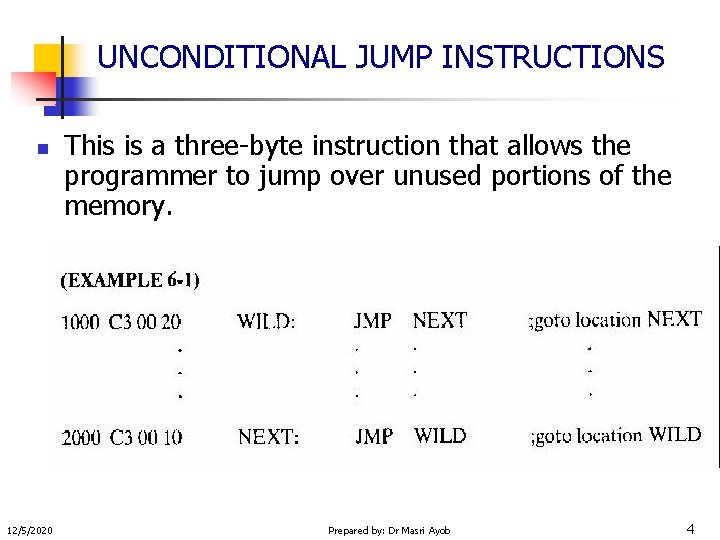

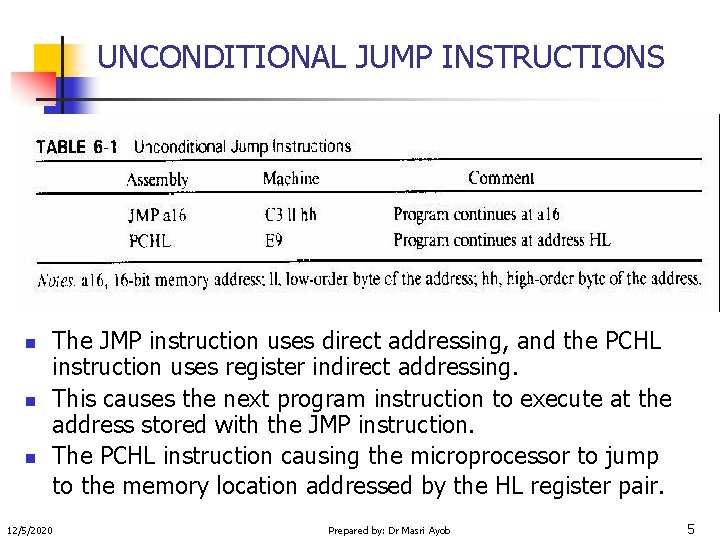

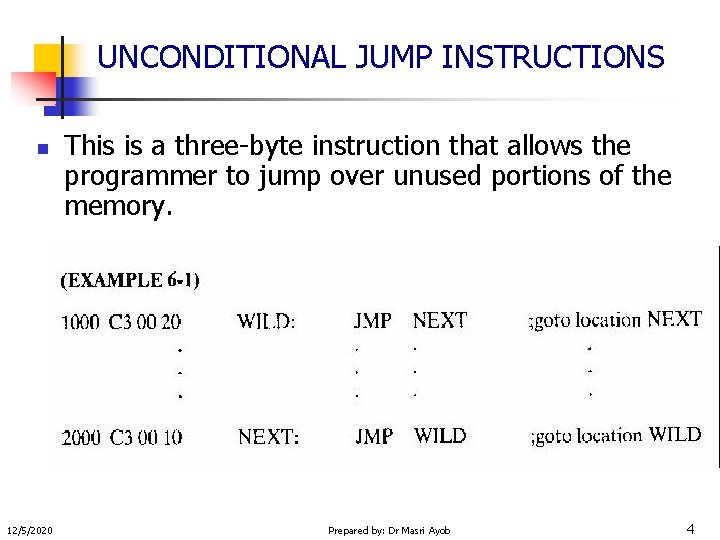

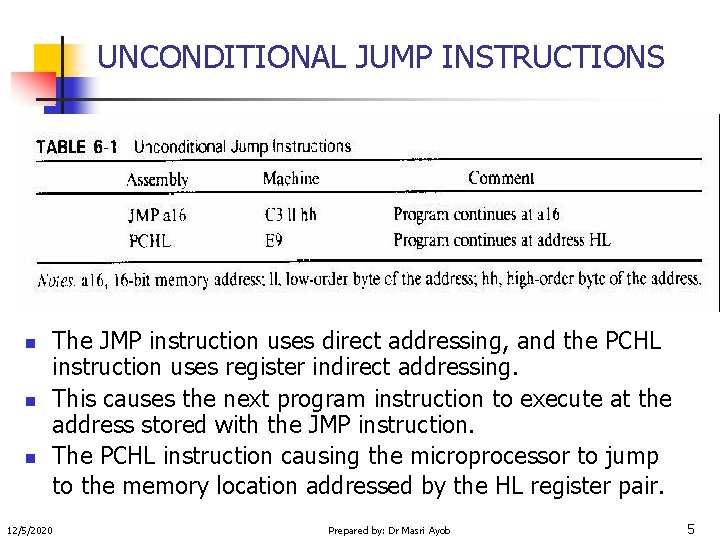

UNCONDITIONAL JUMP INSTRUCTIONS n 12/5/2020 This is a three-byte instruction that allows the programmer to jump over unused portions of the memory. Prepared by: Dr Masri Ayob 4

UNCONDITIONAL JUMP INSTRUCTIONS n n n The JMP instruction uses direct addressing, and the PCHL instruction uses register indirect addressing. This causes the next program instruction to execute at the address stored with the JMP instruction. The PCHL instruction causing the microprocessor to jump to the memory location addressed by the HL register pair. 12/5/2020 Prepared by: Dr Masri Ayob 5

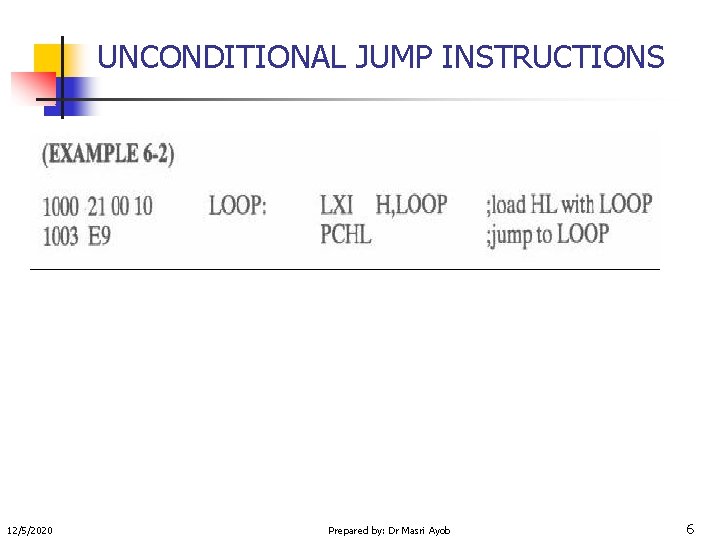

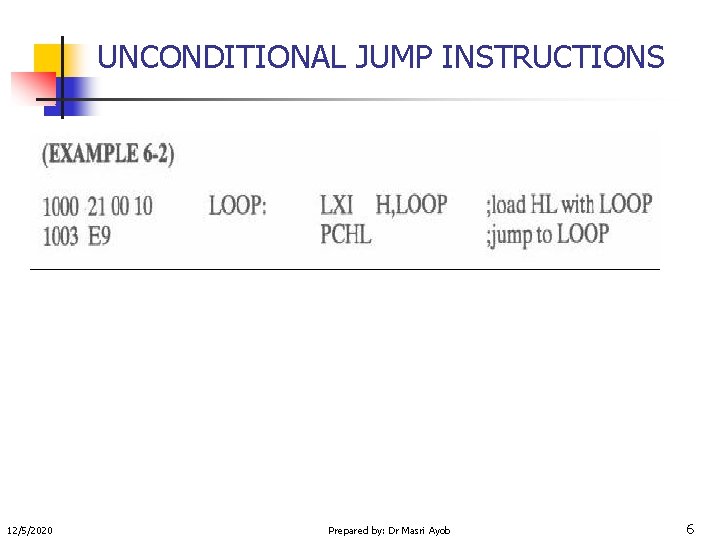

UNCONDITIONAL JUMP INSTRUCTIONS 12/5/2020 Prepared by: Dr Masri Ayob 6

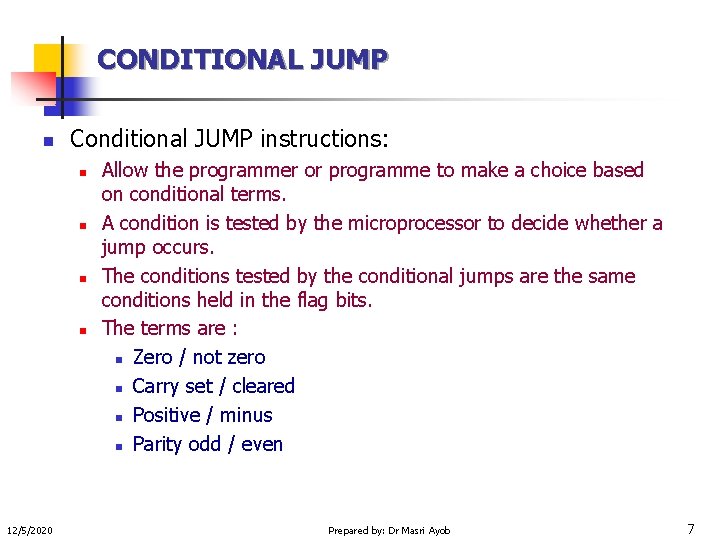

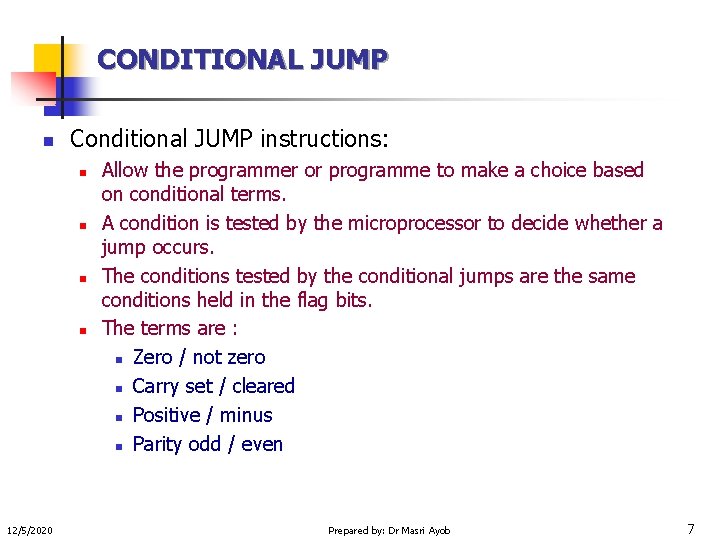

CONDITIONAL JUMP n Conditional JUMP instructions: n n 12/5/2020 Allow the programmer or programme to make a choice based on conditional terms. A condition is tested by the microprocessor to decide whether a jump occurs. The conditions tested by the conditional jumps are the same conditions held in the flag bits. The terms are : n Zero / not zero n Carry set / cleared n Positive / minus n Parity odd / even Prepared by: Dr Masri Ayob 7

CONDITIONAL JUMP INSTRUCTIONS 12/5/2020 Prepared by: Dr Masri Ayob 8

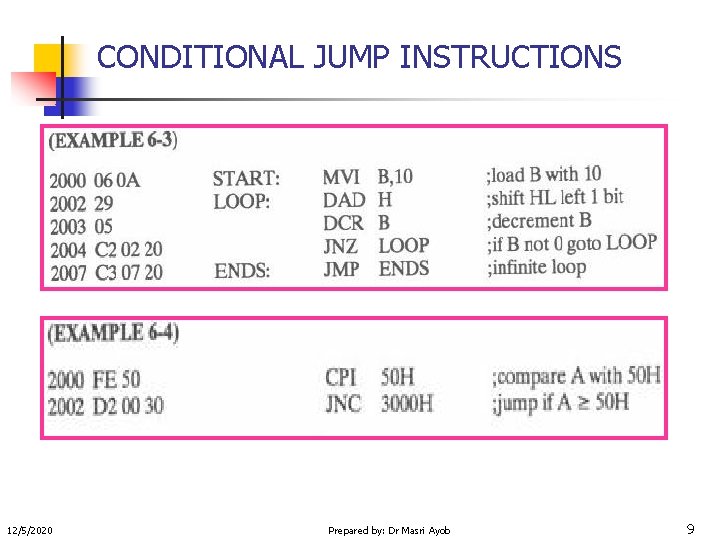

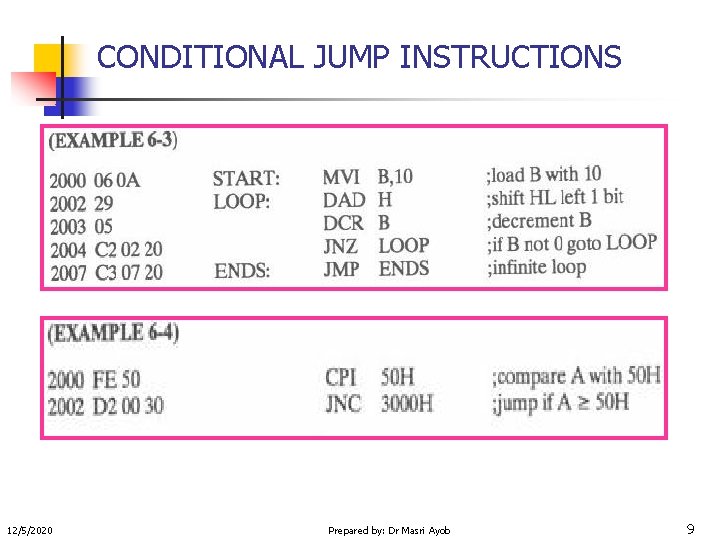

CONDITIONAL JUMP INSTRUCTIONS 12/5/2020 Prepared by: Dr Masri Ayob 9

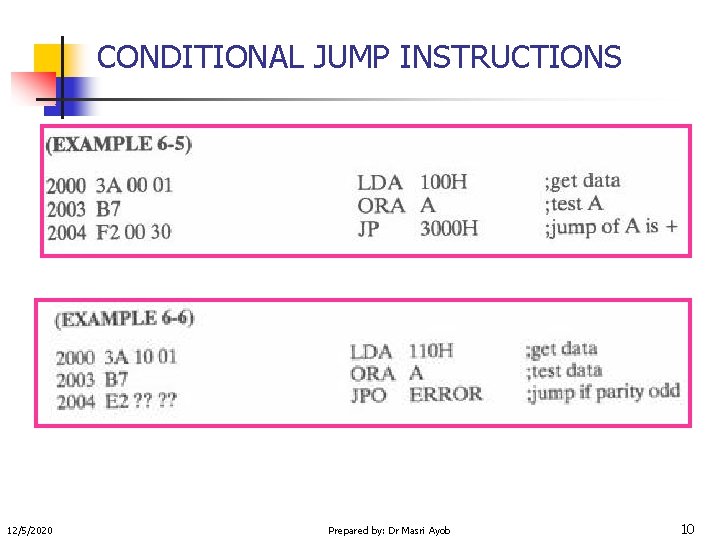

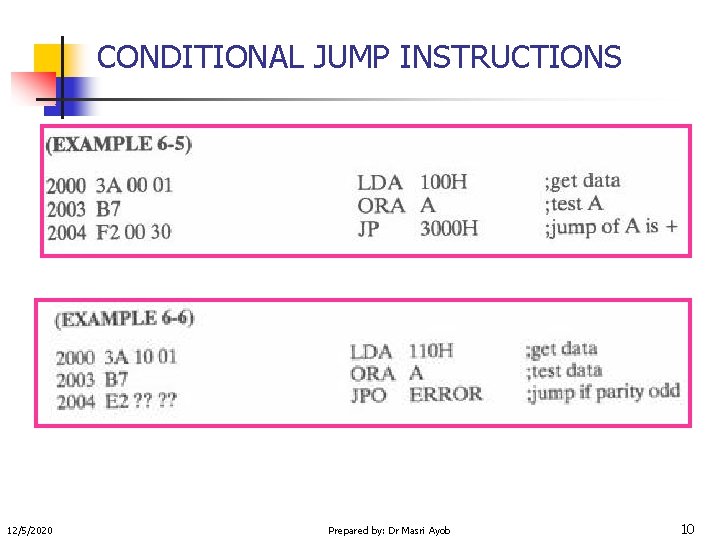

CONDITIONAL JUMP INSTRUCTIONS 12/5/2020 Prepared by: Dr Masri Ayob 10

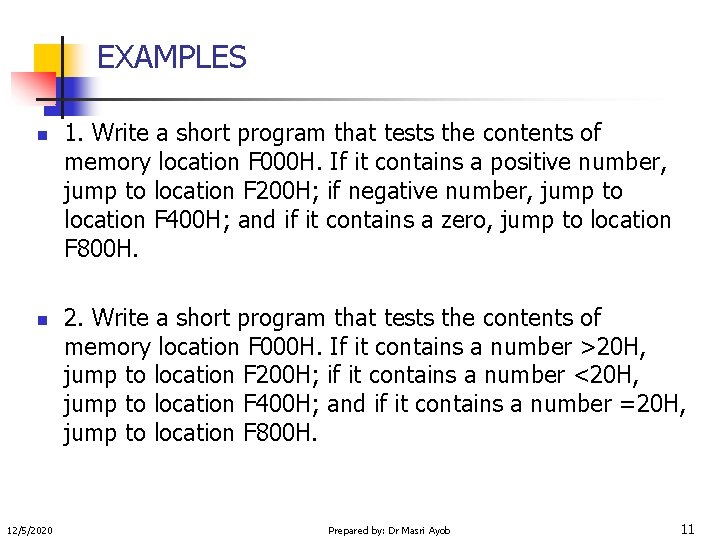

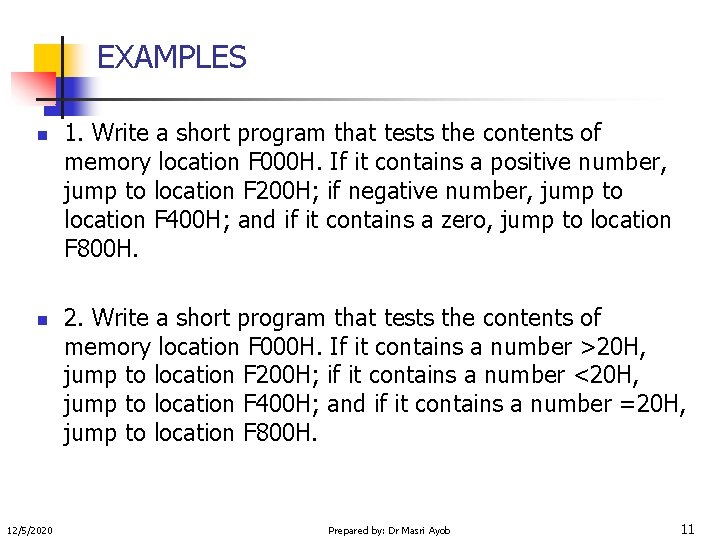

EXAMPLES n n 12/5/2020 1. Write a short program that tests the contents of memory location F 000 H. If it contains a positive number, jump to location F 200 H; if negative number, jump to location F 400 H; and if it contains a zero, jump to location F 800 H. 2. Write a short program that tests the contents of memory location F 000 H. If it contains a number >20 H, jump to location F 200 H; if it contains a number <20 H, jump to location F 400 H; and if it contains a number =20 H, jump to location F 800 H. Prepared by: Dr Masri Ayob 11

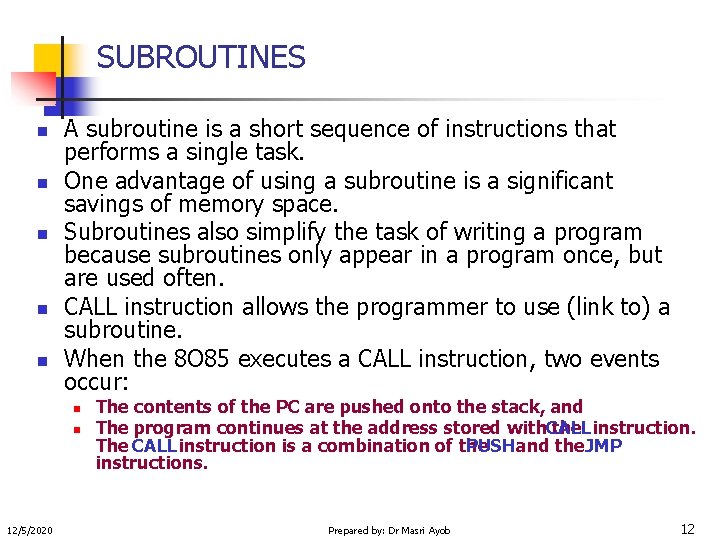

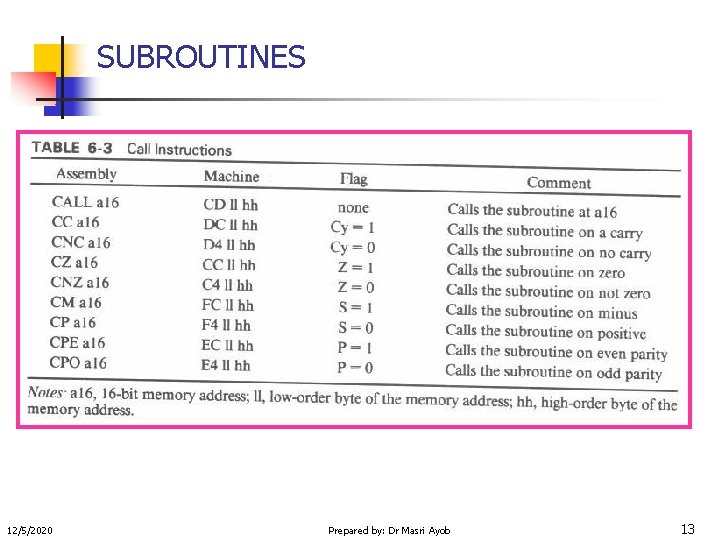

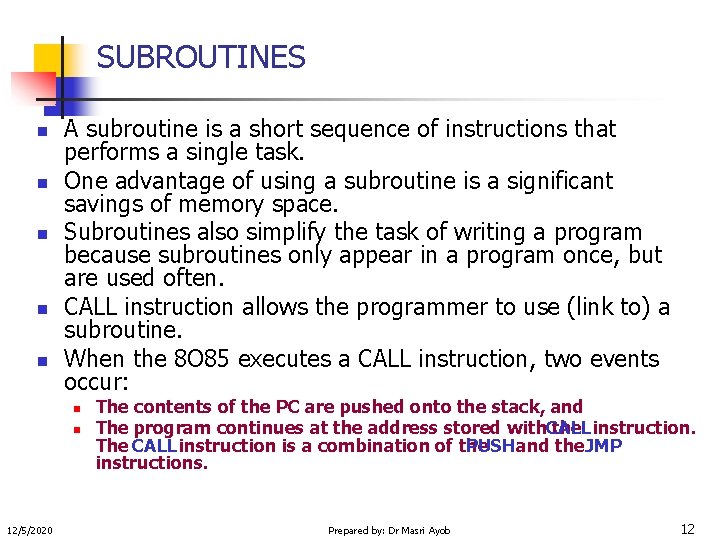

SUBROUTINES n n n A subroutine is a short sequence of instructions that performs a single task. One advantage of using a subroutine is a significant savings of memory space. Subroutines also simplify the task of writing a program because subroutines only appear in a program once, but are used often. CALL instruction allows the programmer to use (link to) a subroutine. When the 8 O 85 executes a CALL instruction, two events occur: n n 12/5/2020 The contents of the PC are pushed onto the stack, and The program continues at the address stored with. CALL the instruction. The CALL instruction is a combination of the PUSHand the. JMP instructions. Prepared by: Dr Masri Ayob 12

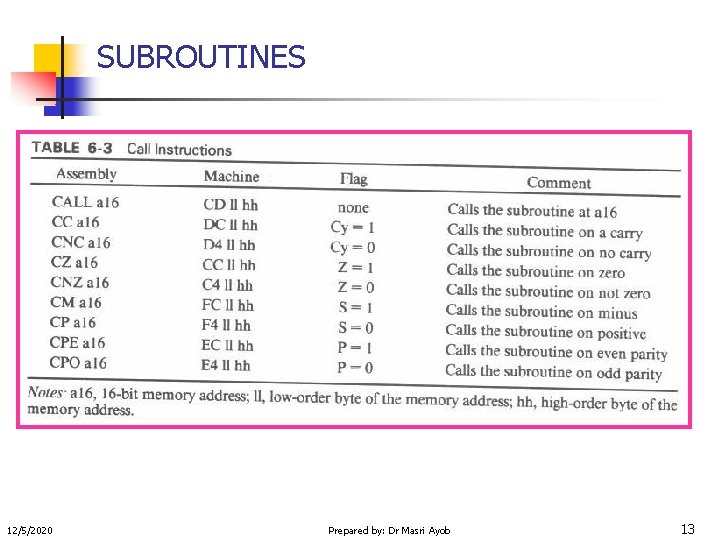

SUBROUTINES 12/5/2020 Prepared by: Dr Masri Ayob 13

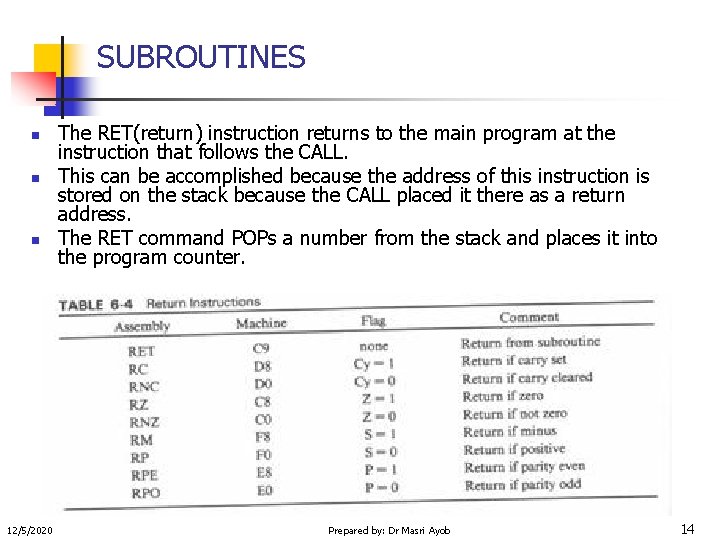

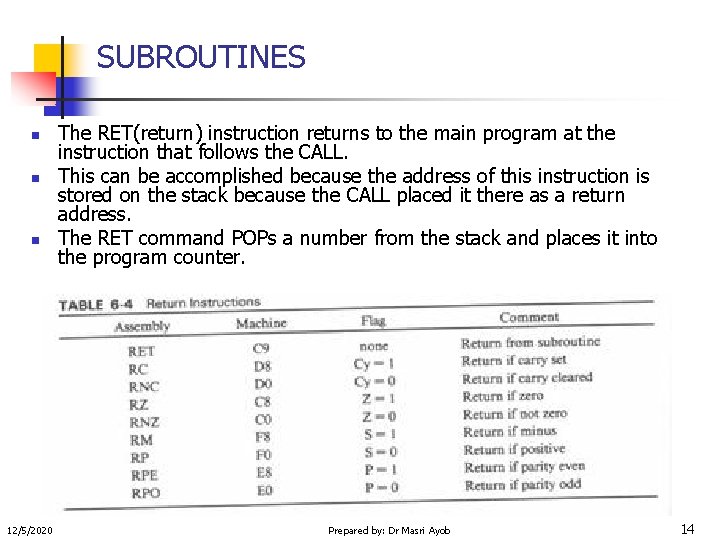

SUBROUTINES n n n 12/5/2020 The RET(return) instruction returns to the main program at the instruction that follows the CALL. This can be accomplished because the address of this instruction is stored on the stack because the CALL placed it there as a return address. The RET command POPs a number from the stack and places it into the program counter. Prepared by: Dr Masri Ayob 14

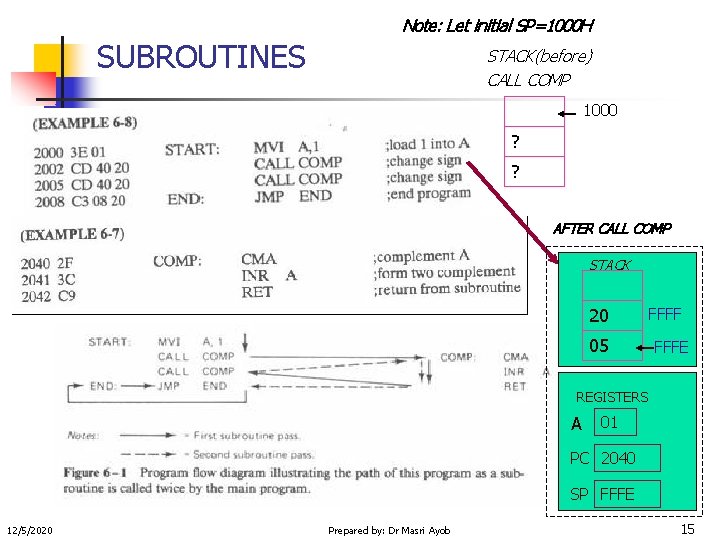

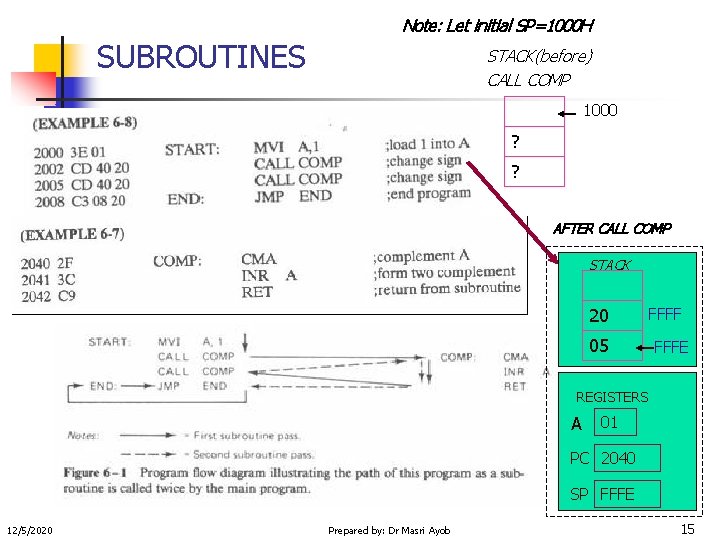

Note: Let initial SP=1000 H SUBROUTINES STACK(before) CALL COMP 1000 ? ? AFTER CALL COMP STACK 20 05 FFFF FFFE REGISTERS A 01 PC 2040 SP FFFE 12/5/2020 Prepared by: Dr Masri Ayob 15

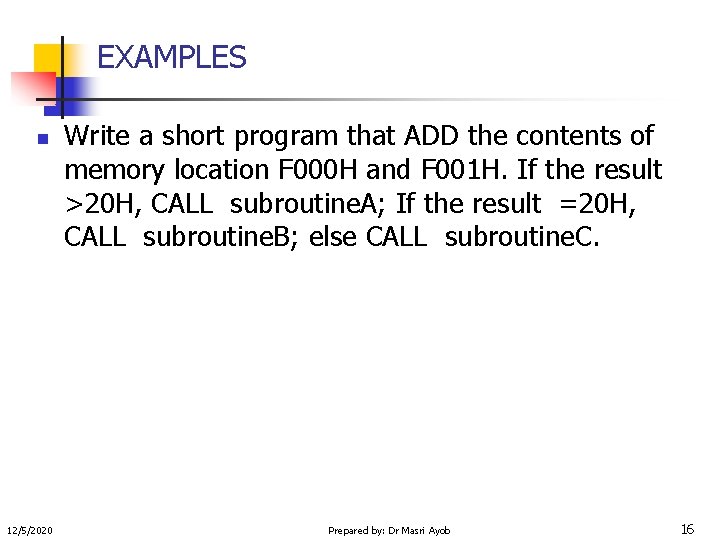

EXAMPLES n 12/5/2020 Write a short program that ADD the contents of memory location F 000 H and F 001 H. If the result >20 H, CALL subroutine. A; If the result =20 H, CALL subroutine. B; else CALL subroutine. C. Prepared by: Dr Masri Ayob 16

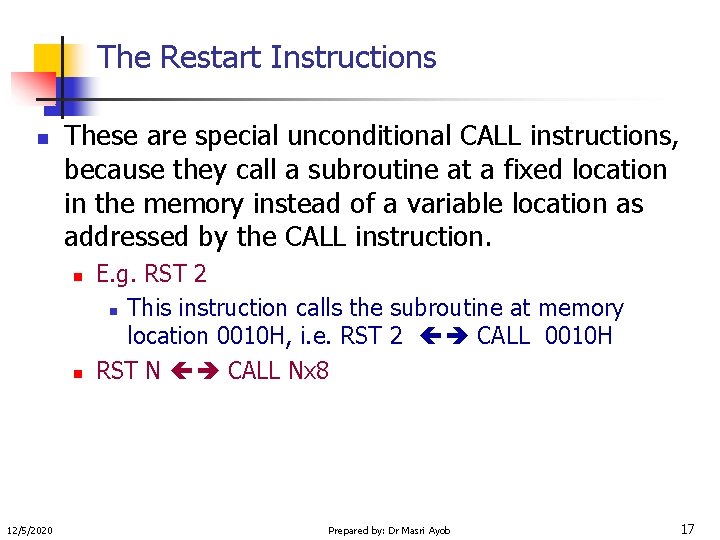

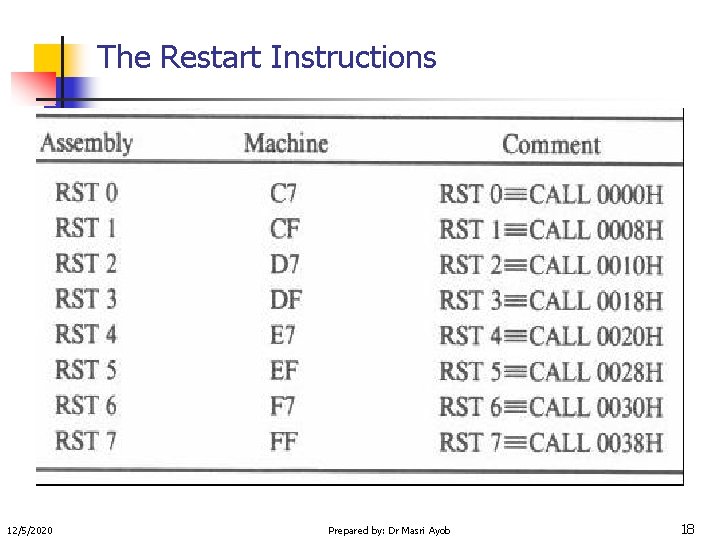

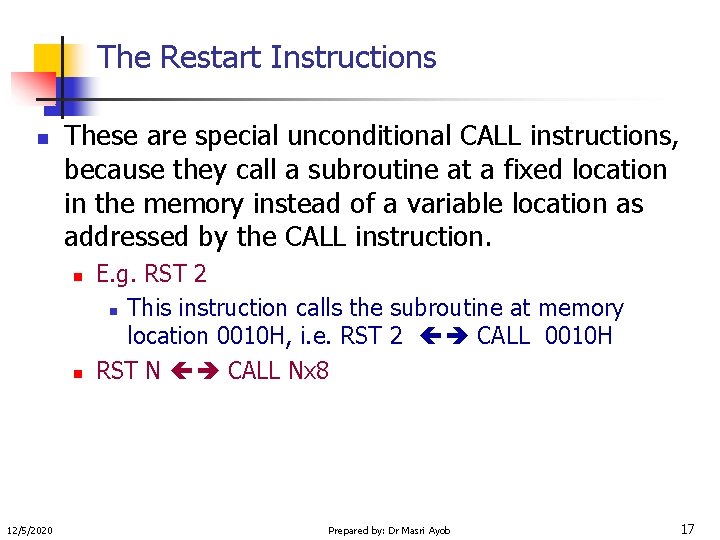

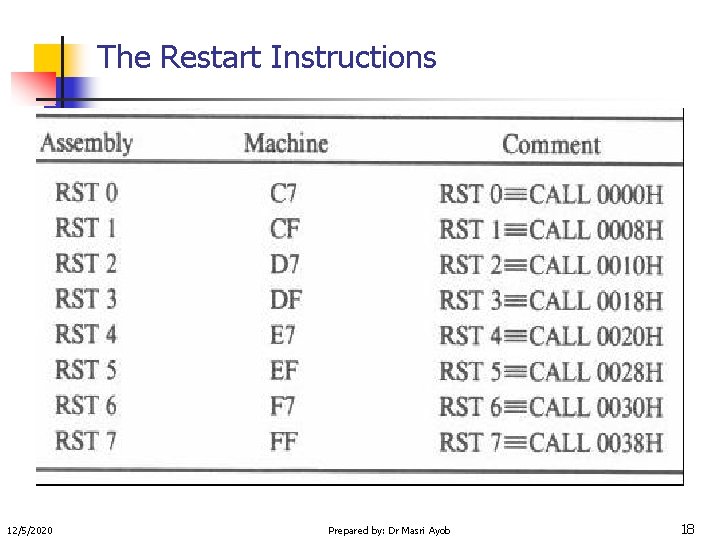

The Restart Instructions n These are special unconditional CALL instructions, because they call a subroutine at a fixed location in the memory instead of a variable location as addressed by the CALL instruction. n n 12/5/2020 E. g. RST 2 n This instruction calls the subroutine at memory location 0010 H, i. e. RST 2 CALL 0010 H RST N CALL Nx 8 Prepared by: Dr Masri Ayob 17

The Restart Instructions 12/5/2020 Prepared by: Dr Masri Ayob 18

MISCELLANEOUS INSTRUCTIONS n Program execution is stopped by the HLT (halt) instruction. n n n 12/5/2020 Execution only continues after a HLT instruction by activating reset or have an interrupt occur. Both the reset and the interrupt must come from the external hardware. The use of this command must be reserved for special purposes such as catastrophic system failure. Prepared by: Dr Masri Ayob 19

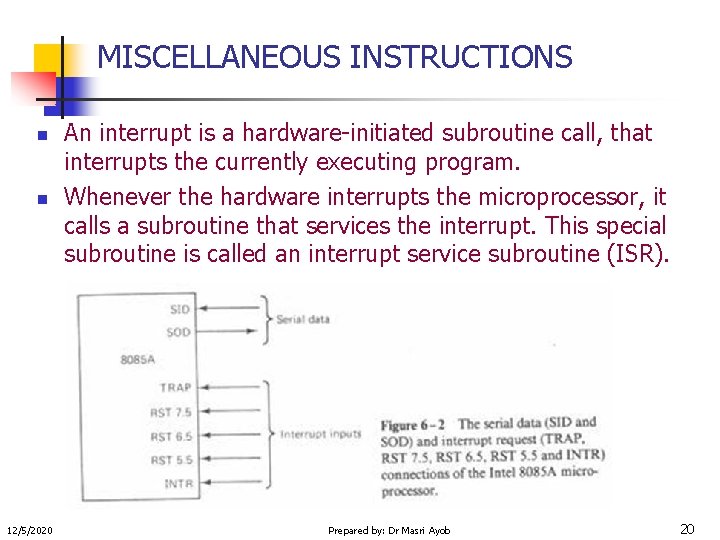

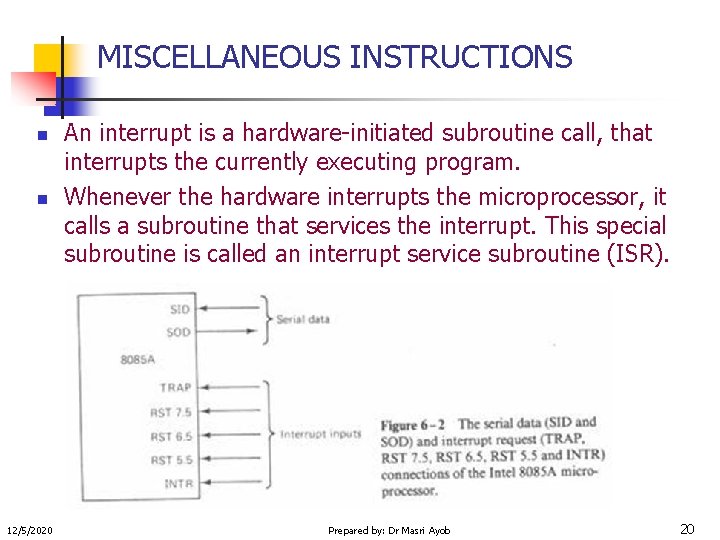

MISCELLANEOUS INSTRUCTIONS n n 12/5/2020 An interrupt is a hardware-initiated subroutine call, that interrupts the currently executing program. Whenever the hardware interrupts the microprocessor, it calls a subroutine that services the interrupt. This special subroutine is called an interrupt service subroutine (ISR). Prepared by: Dr Masri Ayob 20

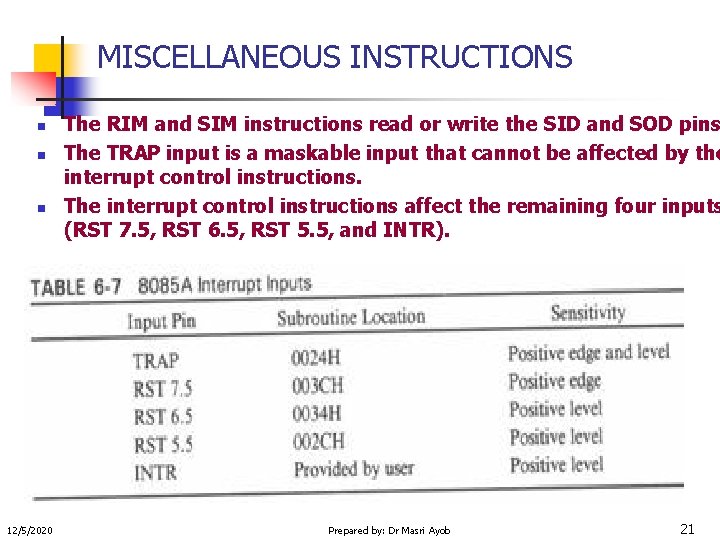

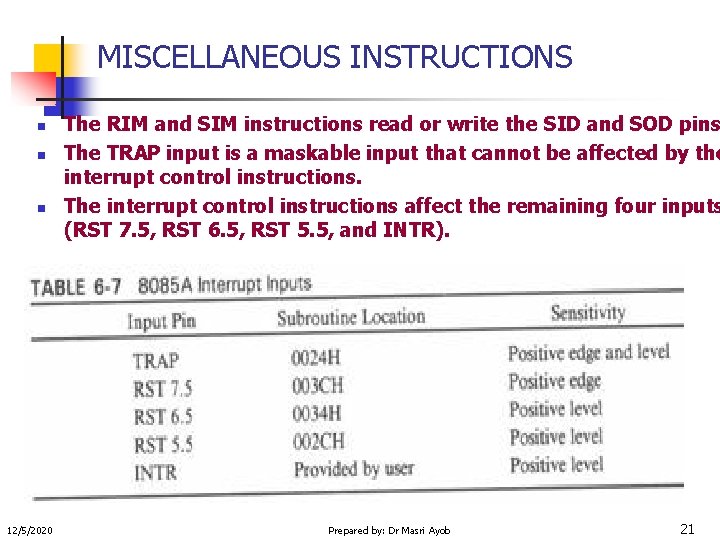

MISCELLANEOUS INSTRUCTIONS n n n 12/5/2020 The RIM and SIM instructions read or write the SID and SOD pins The TRAP input is a maskable input that cannot be affected by the interrupt control instructions. The interrupt control instructions affect the remaining four inputs (RST 7. 5, RST 6. 5, RST 5. 5, and INTR). Prepared by: Dr Masri Ayob 21

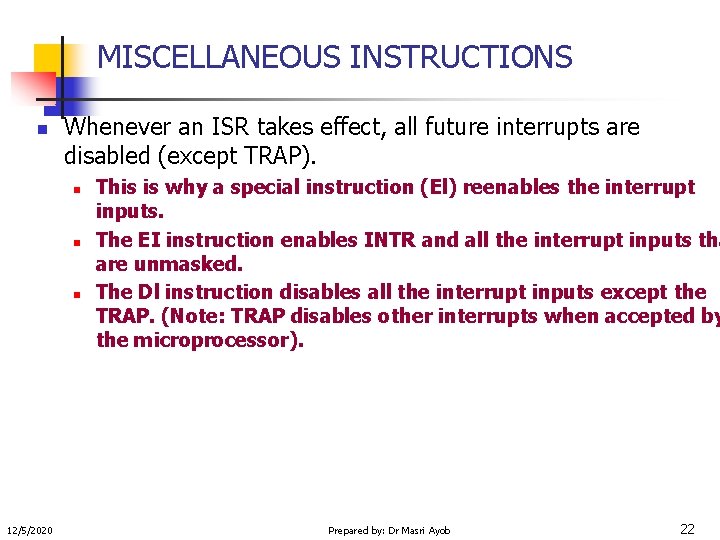

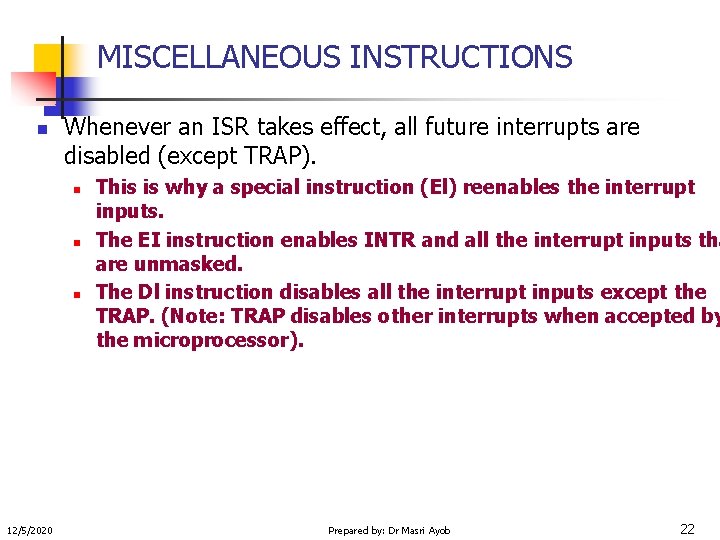

MISCELLANEOUS INSTRUCTIONS n Whenever an ISR takes effect, all future interrupts are disabled (except TRAP). n n n 12/5/2020 This is why a special instruction (El) reenables the interrupt inputs. The EI instruction enables INTR and all the interrupt inputs tha are unmasked. The Dl instruction disables all the interrupt inputs except the TRAP. (Note: TRAP disables other interrupts when accepted by the microprocessor). Prepared by: Dr Masri Ayob 22

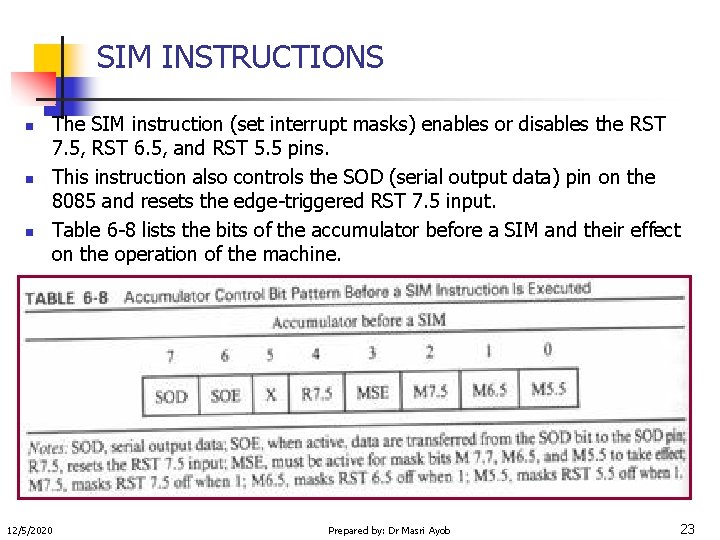

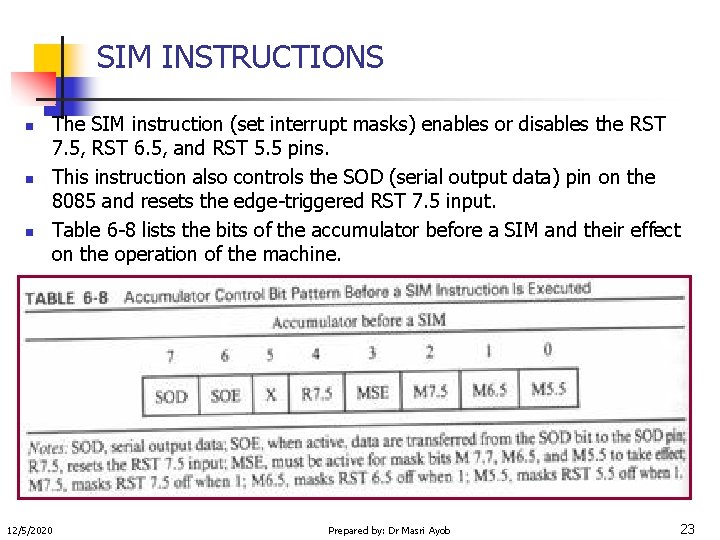

SIM INSTRUCTIONS n n n The SIM instruction (set interrupt masks) enables or disables the RST 7. 5, RST 6. 5, and RST 5. 5 pins. This instruction also controls the SOD (serial output data) pin on the 8085 and resets the edge-triggered RST 7. 5 input. Table 6 -8 lists the bits of the accumulator before a SIM and their effect on the operation of the machine. 12/5/2020 Prepared by: Dr Masri Ayob 23

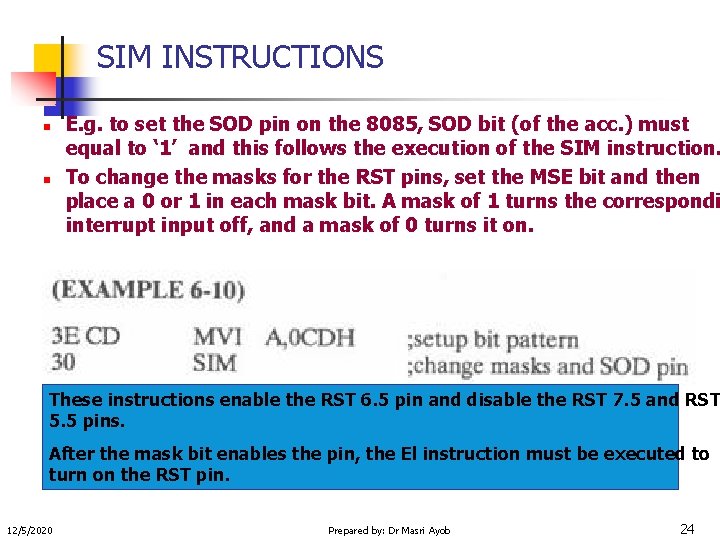

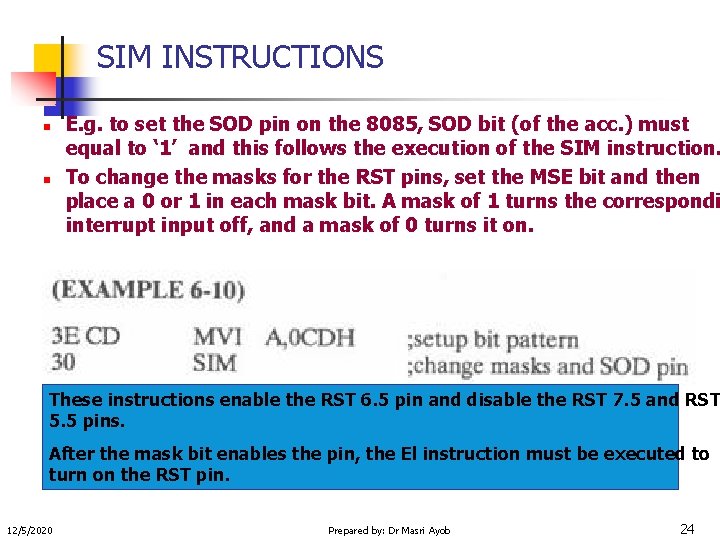

SIM INSTRUCTIONS n n E. g. to set the SOD pin on the 8085, SOD bit (of the acc. ) must equal to ‘ 1’ and this follows the execution of the SIM instruction. To change the masks for the RST pins, set the MSE bit and then place a 0 or 1 in each mask bit. A mask of 1 turns the correspondi interrupt input off, and a mask of 0 turns it on. These instructions enable the RST 6. 5 pin and disable the RST 7. 5 and RST 5. 5 pins. After the mask bit enables the pin, the El instruction must be executed to turn on the RST pin. 12/5/2020 Prepared by: Dr Masri Ayob 24

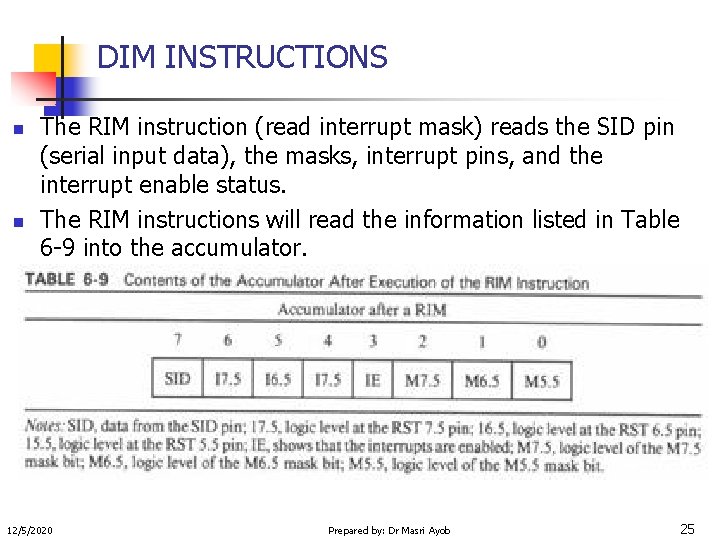

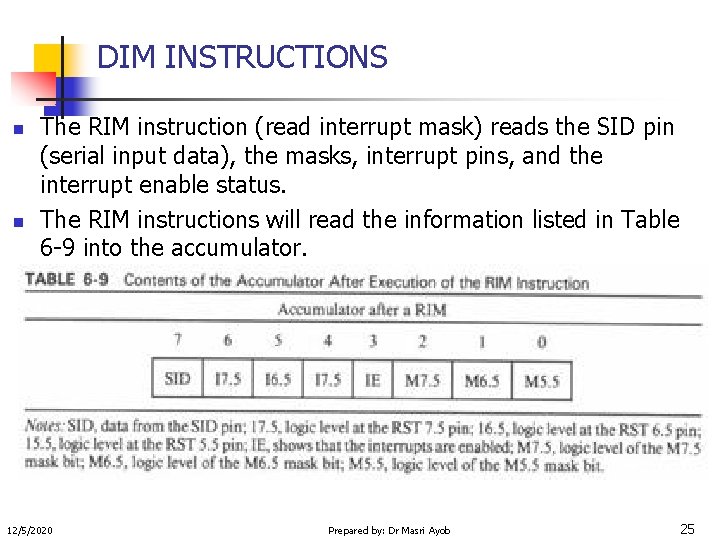

DIM INSTRUCTIONS n n The RIM instruction (read interrupt mask) reads the SID pin (serial input data), the masks, interrupt pins, and the interrupt enable status. The RIM instructions will read the information listed in Table 6 -9 into the accumulator. 12/5/2020 Prepared by: Dr Masri Ayob 25

DIM INSTRUCTIONS n The IE bit of the accumulator shows whether El or DI has been executed most recently. n This bit also changes whenever an interrupt takes effect, because interrupts always clear IE disabling future interrupts. . 12/5/2020 Prepared by: Dr Masri Ayob 26

SUMMARY n n n 12/5/2020 Program control instructions allow a program to jump around unused sections of the memory and allow the program to test the flag bits to make decisions. The unconditional jump (JMP) is a three-byte instruction that causes program execution to continue at the memory address stored with the instruction. The conditional jump instructions allow the flags (Z, C, S, and P) to be tested. If the outcome of the test is true, a jump occurs; if the outcome is false, the next sequential instruction in the program executes. Subroutines are short programs that perform one task, end with a return instruction, and can be used often from another program. The CALL instruction links to a subroutine. It does this by pushing the contents of the program counter onto the stack and jumping to the memory location stored in bytes 2 and 3 of the instruction. Prepared by: Dr Masri Ayob 27

SUMMARY n n 12/5/2020 The return address is the contents of the program counter placed on the stack by a CALL instruction. The return address is removed from the stack by the return (RET) instruction, which places it back into the program counter from the stack. Conditional call and return instructions work like the conditional jump instruction. If the condition tested is true, the call or return occurs, and if false, the next sequential instruction executes. Restarts (RST) are one-byte call instructions. The location called by a RST can be determined by multiplying the restart number times 8. For example, RST 5 is equivalent to a CALL 0028 H. The NOP instruction performs no operation and sometimes appears in time- delay software because it takes about 2 us to do nothing. Prepared by: Dr Masri Ayob 28

SUMMARY n n n 12/5/2020 The STC and CMC instructions set carry and complement carry, respectively. The HLT (halt) instruction halts execution until either a system reset or an interrupt. The 8085 A contains five interrupt inputs (TRAP, RST 7. 5, RST 6. 5, RST 5. 5, and INTR) and two serial data pins (SID and SOD). The RIM (read interrupt masks) and SIM (set interrupt masks) instructions control the interrupt structure of the 8085 A and the serial data pins. El (enable interrupts) and DI (disable interrupts) turn all the interrupts on and off except TRAP, which can never be disabled. The RST pins may still be disabled after an El, if the mask bits are set. Prepared by: Dr Masri Ayob 29

Thank you Q&A 12/5/2020 Prepared by: Dr Masri Ayob 30