TK 2633 8085 Memory Interface DR MASRI AYOB

TK 2633 8085 Memory Interface DR MASRI AYOB

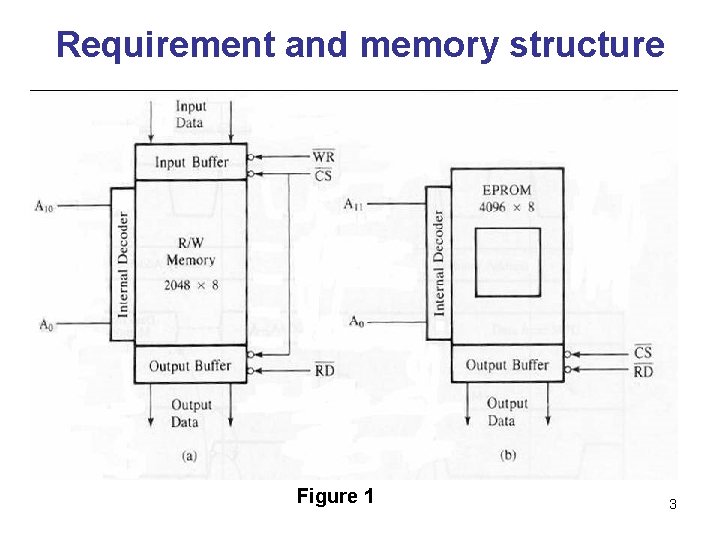

Requirement and memory structure • There are two types of memory: – RAM: read and write – ROM: read only • Figure 1 a shows the R/W memory chip: – – – – 2048 (2 k) size. 8 bit data input line and 8 bit data output line. 11 address lines, A 0 -A 10, one chip select, CS. RD: enable output buffer (penimbal keluaran). WR: enable input buffer (penimbal masukan). The internal decoder is used to decode the internal memory address. 2

Requirement and memory structure Figure 1 3

Requirement and memory structure • Figure 1 b shows the typical diagram of EPROM (Erasable Programmable ROM): – 4096 (4 k) size. – A quartz window on it, that use to receive direct UV light to erase programme. – 8 bit data output line. – 12 address lines, A 0 -A 11, – one chip select, CS. – RD: enable output buffer (penimbal keluaran). – The internal decoder is used to decode the internal memory address. • The technique to interface R/W and EPROM is the same except the EPROM does not require WR control signals. When the chip is programmed, the quartz window has to be covered to avoid accidental program erase. 4

Basic concept of interfacing memory chip. • The basic function of memory interfacing is that the μp should be able to read from and/or write into memory chip. • Therefore the μp has to: – Be able to select certain memory chip. – Identify memory location through memory address. – Enable input or output buffer as to read or write to the memory. 5

Basic concept of interfacing memory chip. • A few basic steps to undertake in chip interface design are: – Connect certain address lines from address bus of μp to address lines at memory chip. – Decode the rest of the address lines to generate Chip Select signal. – Generate control signals MEMR and MEMW. 6

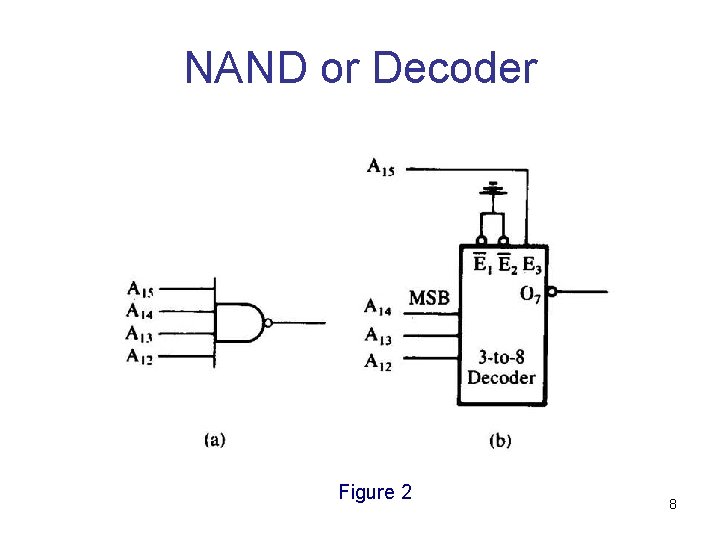

Decoding the address lines • Figure 2 shows two techniques to decode address lines: – Using the NAND gates. – Using the 3 -to-8 decoder. • The output of NAND gate can be activated when all the input A 12 -A 15 is at logic 1. 7

NAND or Decoder Figure 2 8

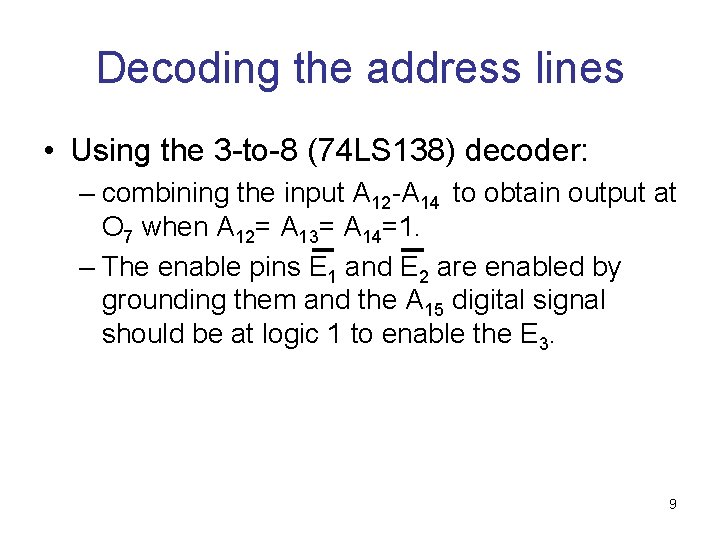

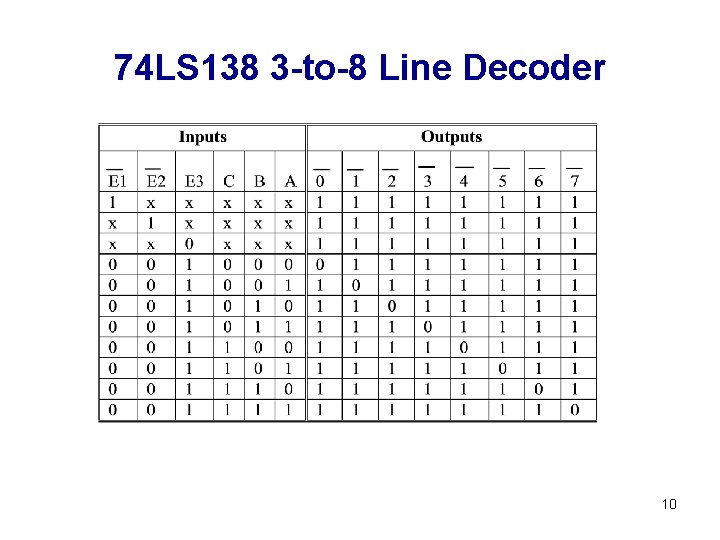

Decoding the address lines • Using the 3 -to-8 (74 LS 138) decoder: – combining the input A 12 -A 14 to obtain output at O 7 when A 12= A 13= A 14=1. – The enable pins E 1 and E 2 are enabled by grounding them and the A 15 digital signal should be at logic 1 to enable the E 3. 9

74 LS 138 3 -to-8 Line Decoder 10

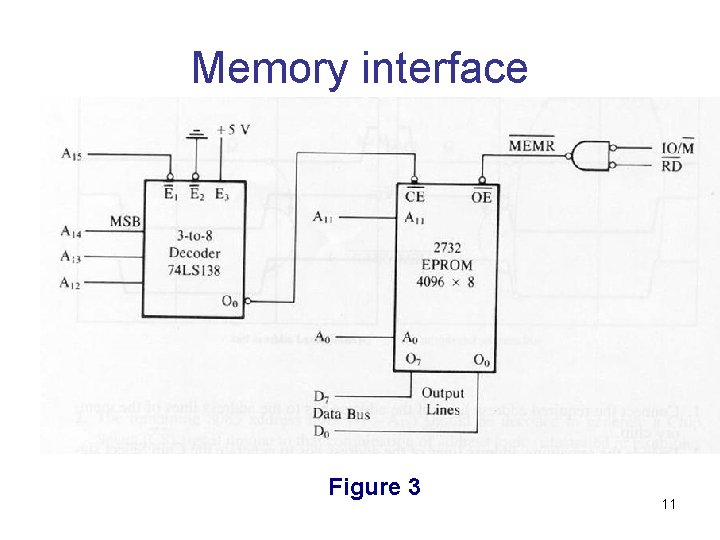

Memory interface Figure 3 11

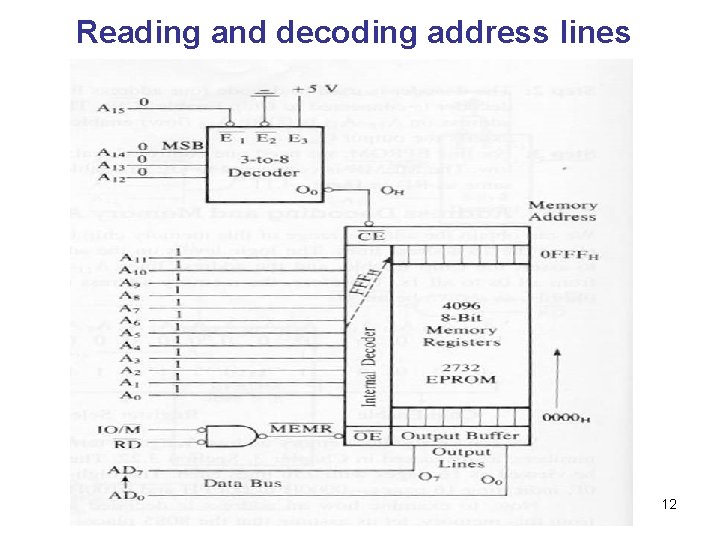

Reading and decoding address lines 12

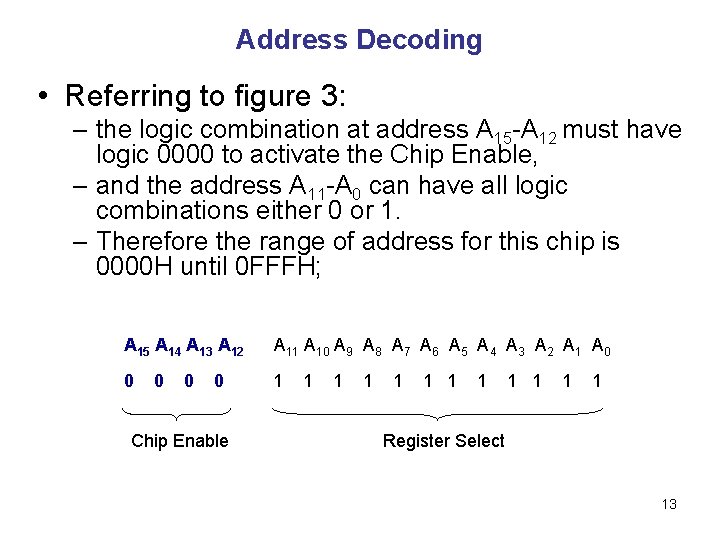

Address Decoding • Referring to figure 3: – the logic combination at address A 15 -A 12 must have logic 0000 to activate the Chip Enable, – and the address A 11 -A 0 can have all logic combinations either 0 or 1. – Therefore the range of address for this chip is 0000 H until 0 FFFH; A 15 A 14 A 13 A 12 A 11 A 10 A 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 0 1 0 0 0 Chip Enable 1 1 1 Register Select 13

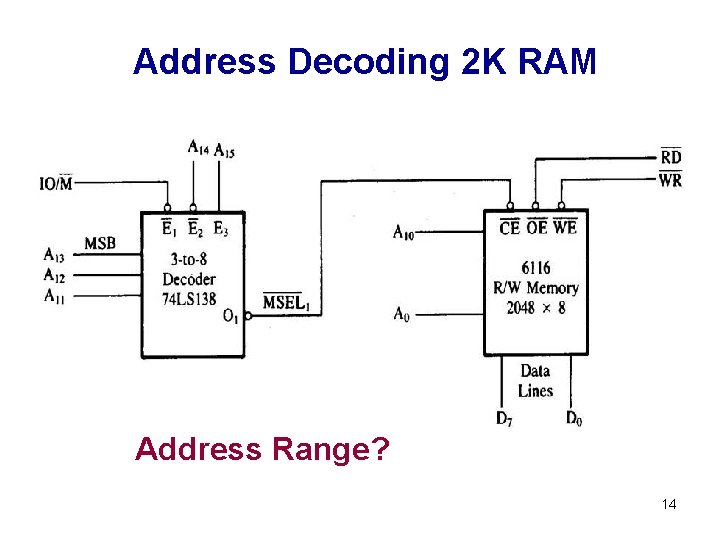

Address Decoding 2 K RAM Address Range? 14

Address Decoding Note: A 11 is not used for RAM. ROM RAM Address Range ? 15

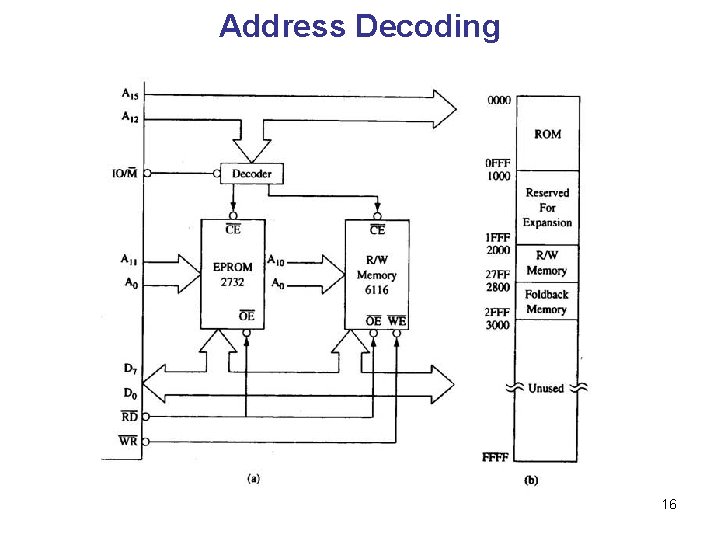

Address Decoding 16

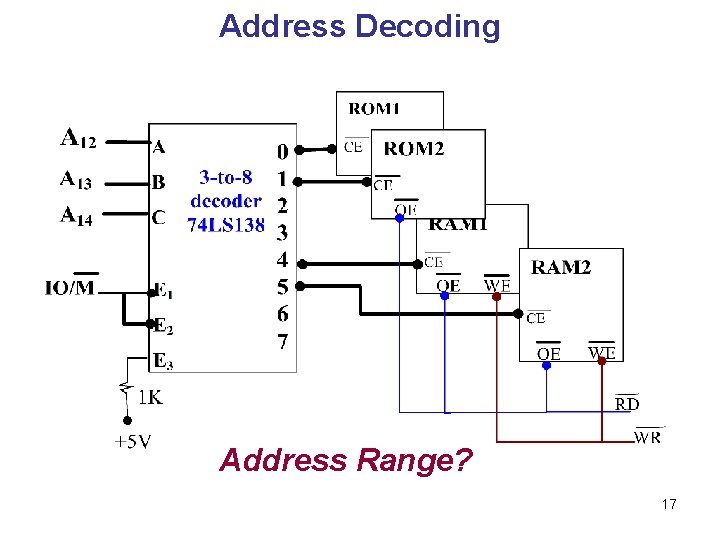

Address Decoding Address Range? 17

Thank you Q&A 18

- Slides: 18