TK 2123 COMPUTER ORGANISATION ARCHITECTURE Lecture 8 Inputoutput

- Slides: 50

TK 2123 COMPUTER ORGANISATION & ARCHITECTURE Lecture 8: Input/output Lecturer : Dr. Masri Ayob

Contents n This lecture will discuss: n n n 3/12/2021 Computer Modules. Input Output Techniques Interrupts. 2

Introduction n n I/O operations take up a lot of computer time much CPU time is wasted waiting for the completion of the I/O task. Several different techniques are combined to resolve the problem of synchronising and handling I/O between a variety of different I/O devices operating with different quantities of data at different speeds. 3/12/2021 3

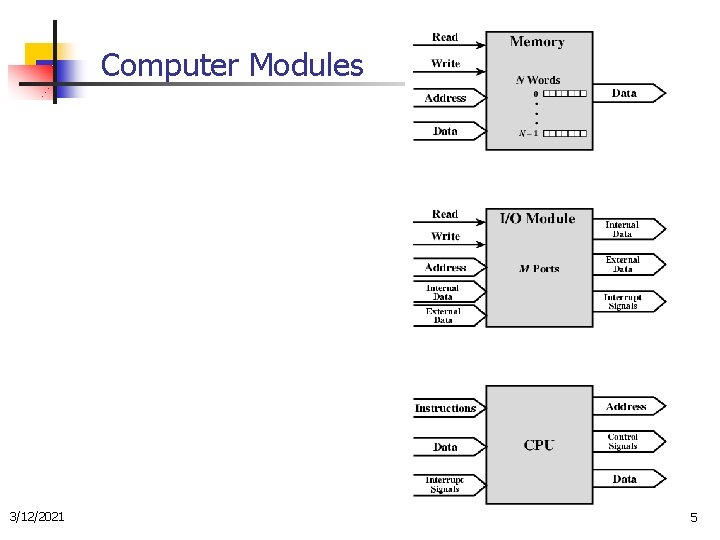

Connecting n n All the units must be connected Different type of connection for different type of unit n n n 3/12/2021 Memory Input/Output CPU 4

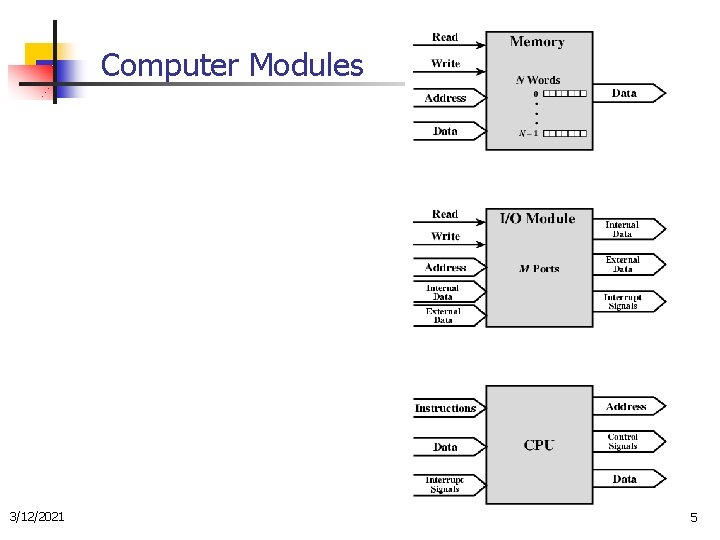

Computer Modules 3/12/2021 5

Memory Connection n Receives and sends data Receives addresses (of locations) Receives control signals n n n 3/12/2021 Read Write Timing 6

Input/Output Connection(1) n n Similar to memory from computer’s viewpoint Output n n n Receive data from computer Send data to peripheral Input n n 3/12/2021 Receive data from peripheral Send data to computer 7

Input/Output Connection(2) n n Receive control signals from computer Send control signals to peripherals n n Receive addresses from computer n n e. g. spin disk e. g. port number to identify peripheral Send interrupt signals (control) 3/12/2021 8

CPU Connection n n Reads instruction and data Writes out data (after processing) Sends control signals to other units Receives (& acts on) interrupts 3/12/2021 9

Input/Output Problems n Wide variety of peripherals n n n Delivering different amounts of data At different speeds In different formats All slower than CPU and RAM Need I/O modules 3/12/2021 10

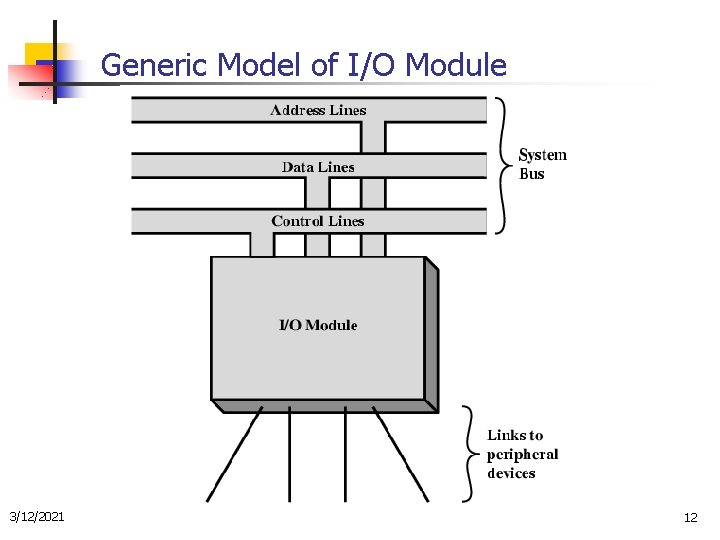

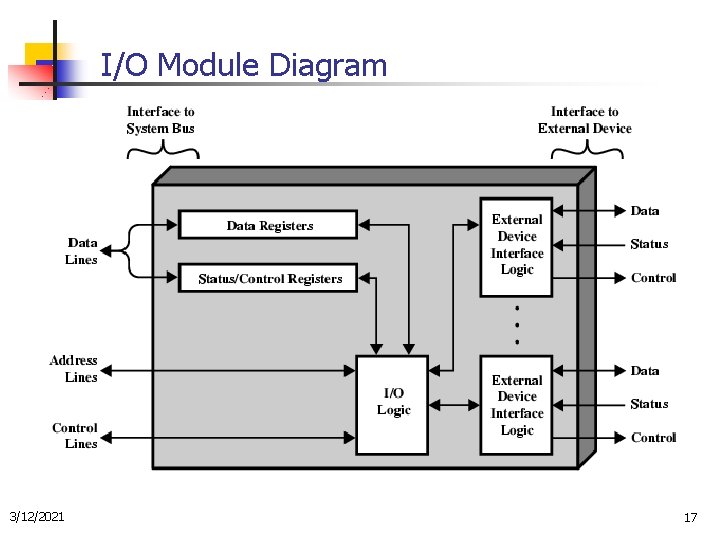

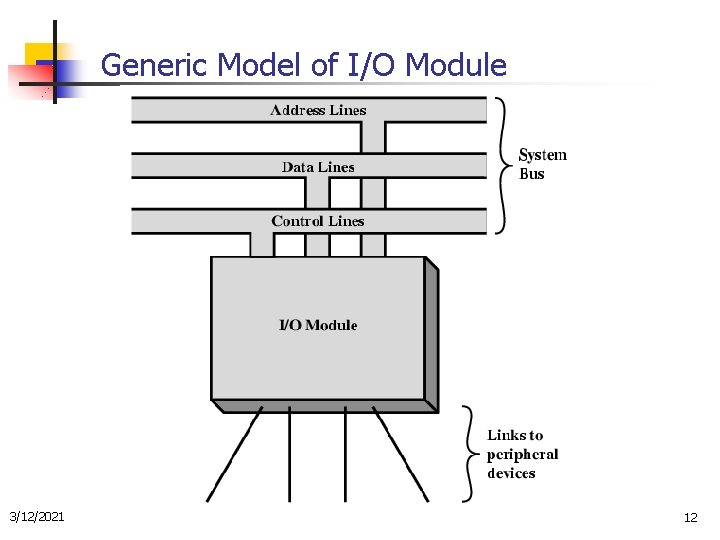

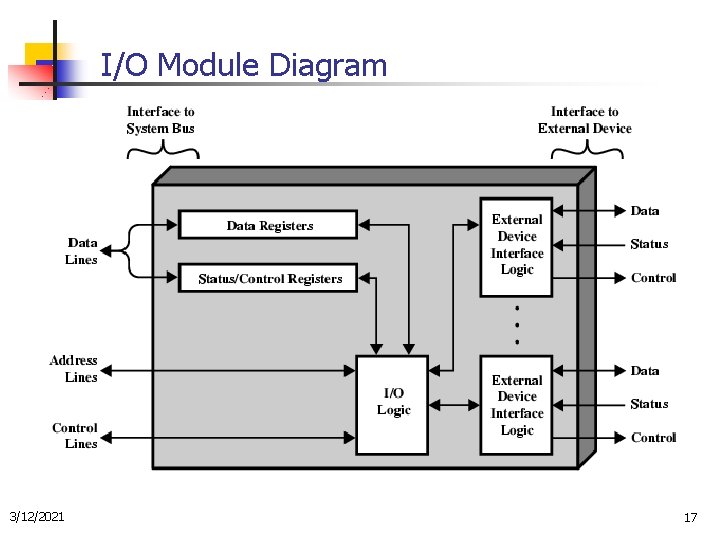

Input/Output Module n n Interface to CPU and Memory Interface to one or more peripherals 3/12/2021 11

Generic Model of I/O Module 3/12/2021 12

External Devices n Human readable n n Machine readable n n Screen, printer, keyboard Monitoring and control Communication n n 3/12/2021 Modem Network Interface Card (NIC) 13

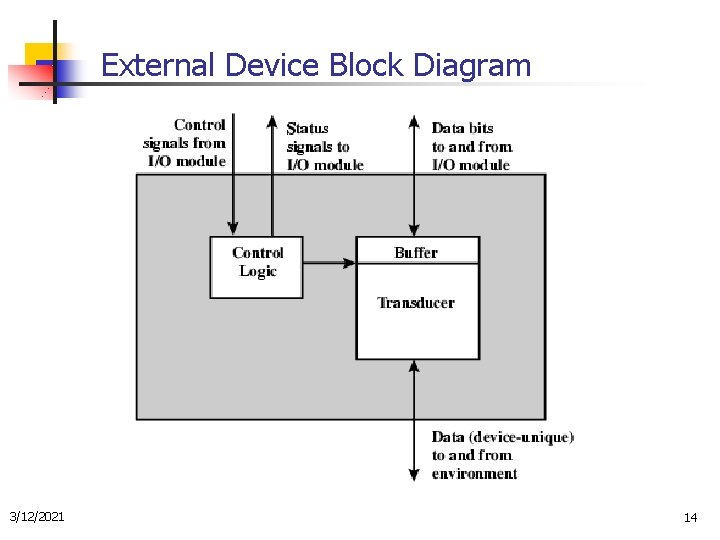

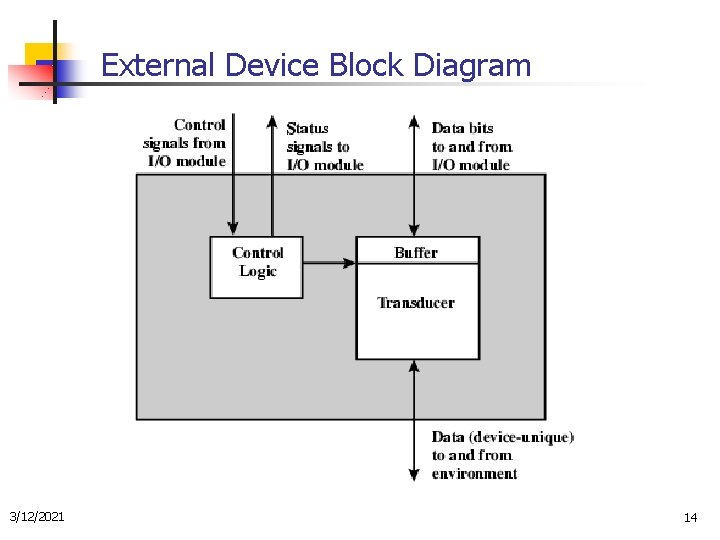

External Device Block Diagram 3/12/2021 14

I/O Module Function n n Control & Timing CPU Communication Device Communication Data Buffering Error Detection 3/12/2021 15

I/O Steps n n n CPU checks I/O module device status I/O module returns status If ready, CPU requests data transfer I/O module gets data from device I/O module transfers data to CPU Variations for output, DMA, etc. 3/12/2021 16

I/O Module Diagram 3/12/2021 17

I/O Module Decisions n n n Hide or reveal device properties to CPU Support multiple or single device Control device functions or leave for CPU 3/12/2021 18

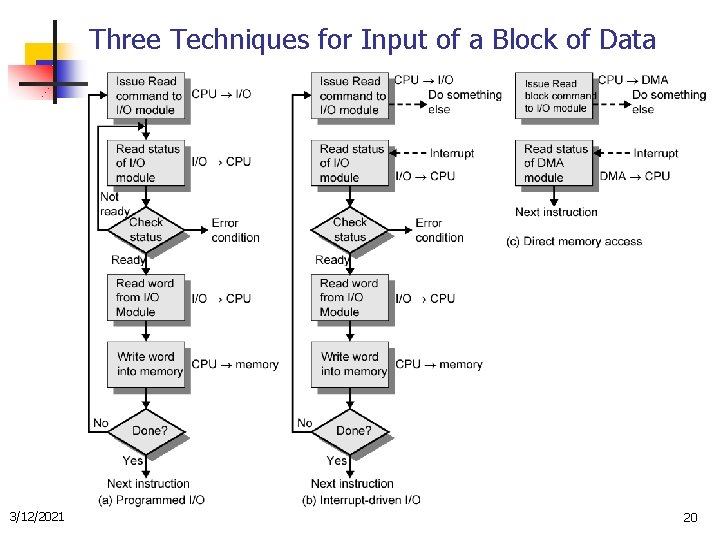

Input Output Techniques n n n Programmed Interrupt driven Direct Memory Access (DMA) 3/12/2021 19

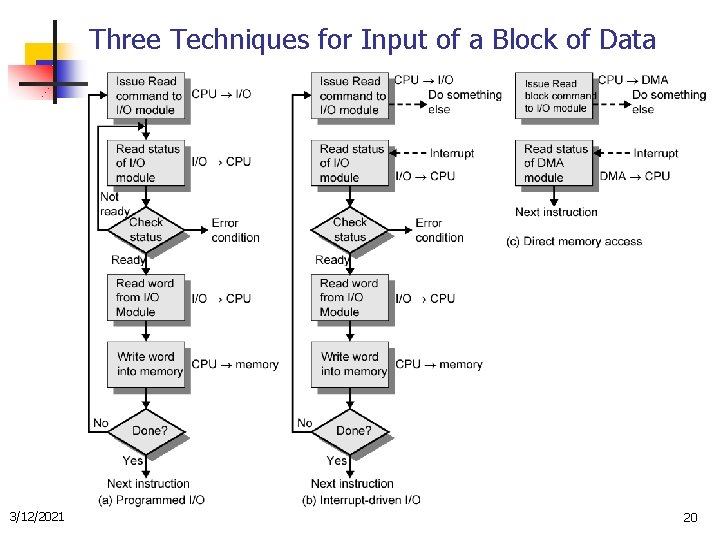

Three Techniques for Input of a Block of Data 3/12/2021 20

Programmed I/O n CPU has direct control over I/O n n n Sensing status Read/write commands Transferring data CPU waits for I/O module to complete operation Wastes CPU time 3/12/2021 21

Programmed I/O - detail n n n n CPU requests I/O operation I/O module performs operation I/O module sets status bits CPU checks status bits periodically - polling I/O module does not inform CPU directly I/O module does not interrupt CPU may wait or come back later 3/12/2021 22

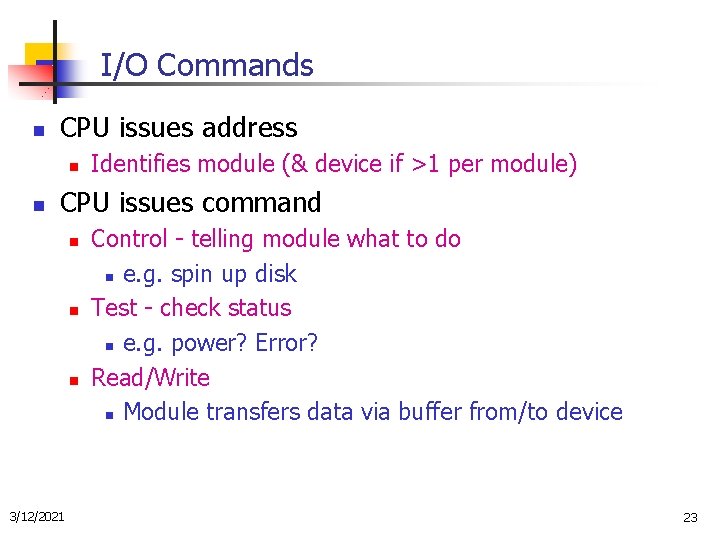

I/O Commands n CPU issues address n n Identifies module (& device if >1 per module) CPU issues command n n n 3/12/2021 Control - telling module what to do n e. g. spin up disk Test - check status n e. g. power? Error? Read/Write n Module transfers data via buffer from/to device 23

Addressing I/O Devices n n n Under programmed I/O data transfer is very like memory access (CPU viewpoint) Each device given unique identifier CPU commands contain identifier (address) 3/12/2021 24

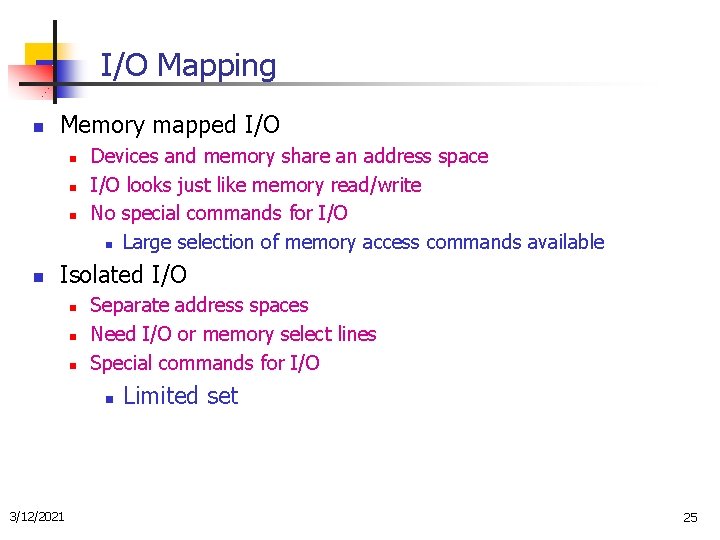

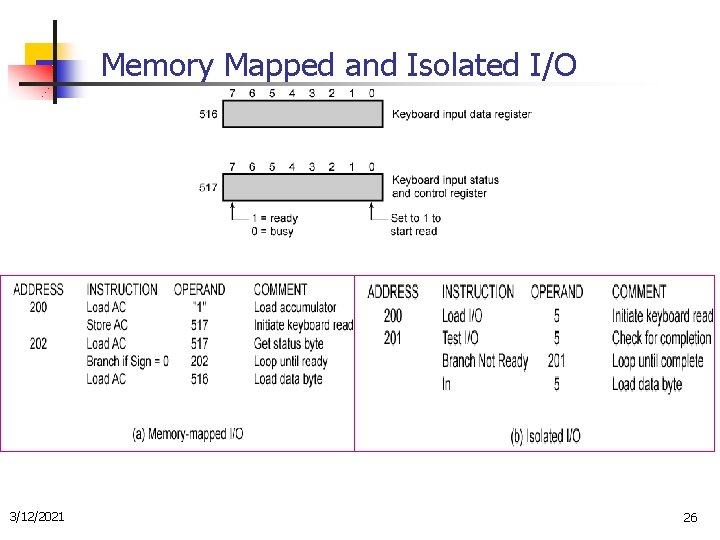

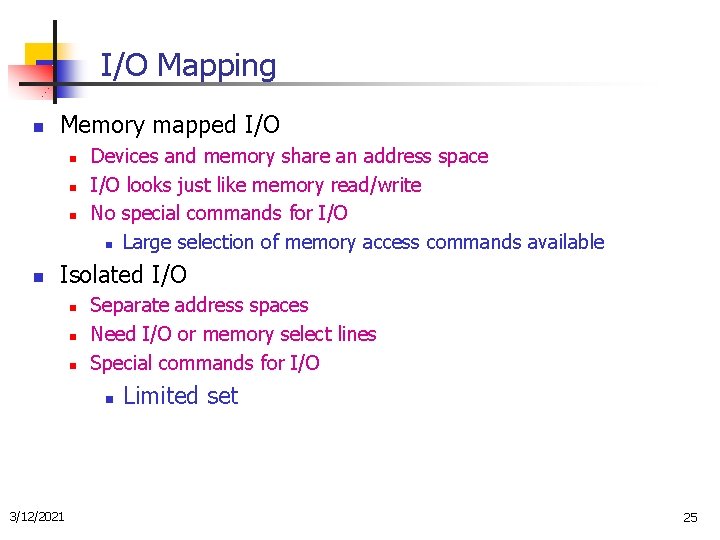

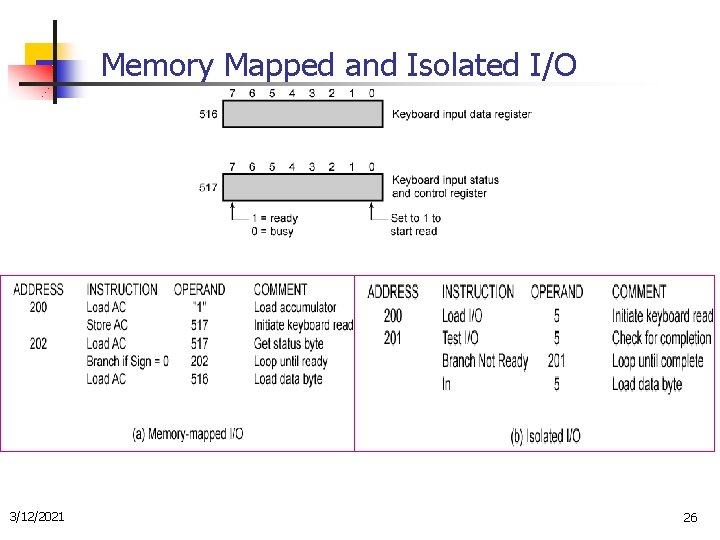

I/O Mapping n Memory mapped I/O n n Devices and memory share an address space I/O looks just like memory read/write No special commands for I/O n Large selection of memory access commands available Isolated I/O n n n Separate address spaces Need I/O or memory select lines Special commands for I/O n 3/12/2021 Limited set 25

Memory Mapped and Isolated I/O 3/12/2021 26

Interrupt Driven I/O n n n Overcomes CPU waiting No repeated CPU checking of device I/O module interrupts when ready 3/12/2021 27

Interrupts n n n n 3/12/2021 Mechanism by which other modules (e. g. I/O) may interrupt normal sequence of processing Allows to time share the CPU between several different programs at once. Modern computers provide interrupt capability by providing special control lines to the central processor known as interrupt lines. Program n e. g. overflow, division by zero Timer n Generated by internal processor timer n Used in pre-emptive multi-tasking I/O n from I/O controller Hardware failure n e. g. memory parity error 28

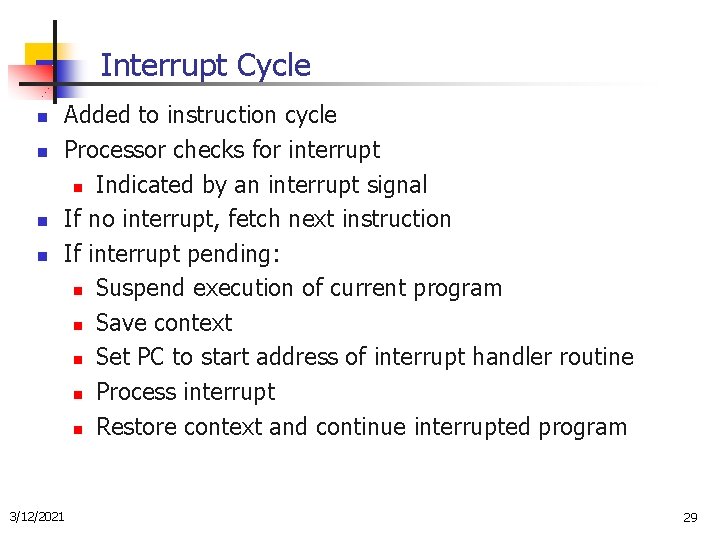

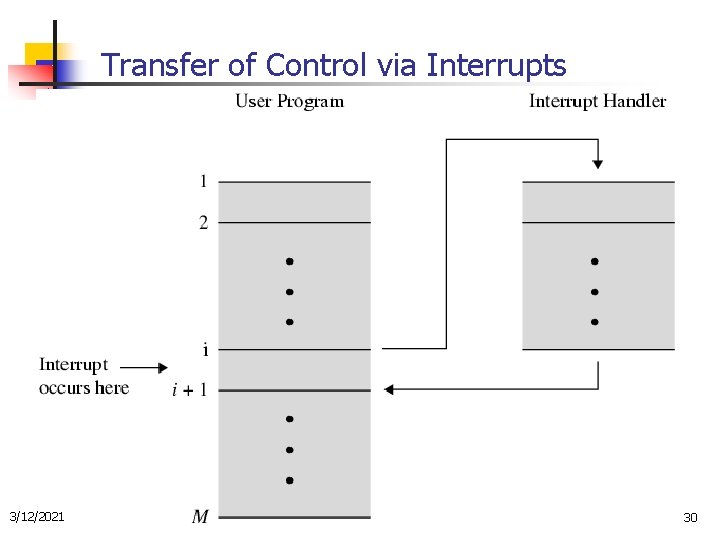

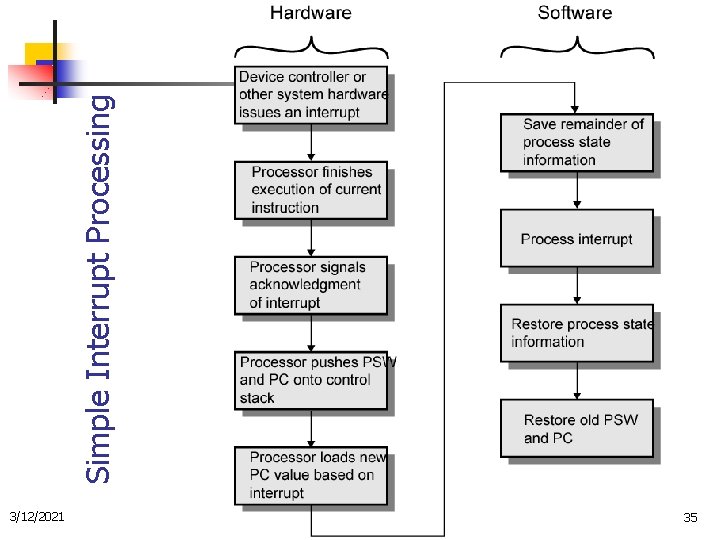

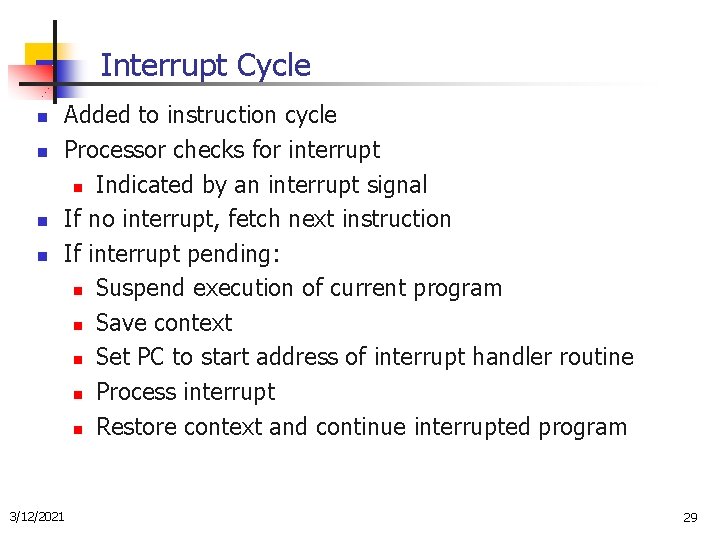

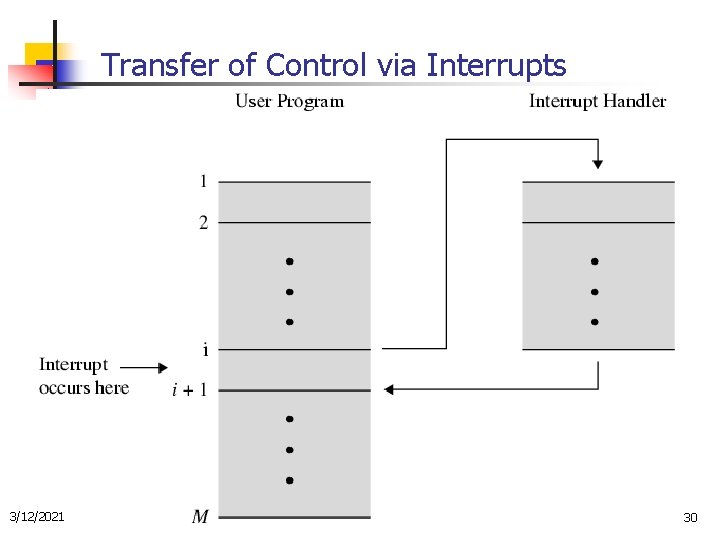

Interrupt Cycle n n Added to instruction cycle Processor checks for interrupt n Indicated by an interrupt signal If no interrupt, fetch next instruction If interrupt pending: n Suspend execution of current program n Save context n Set PC to start address of interrupt handler routine n Process interrupt n Restore context and continue interrupted program 3/12/2021 29

Transfer of Control via Interrupts 3/12/2021 30

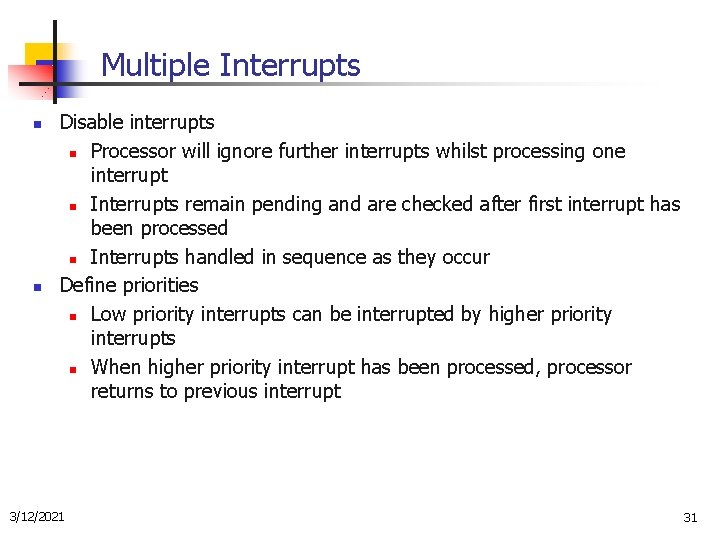

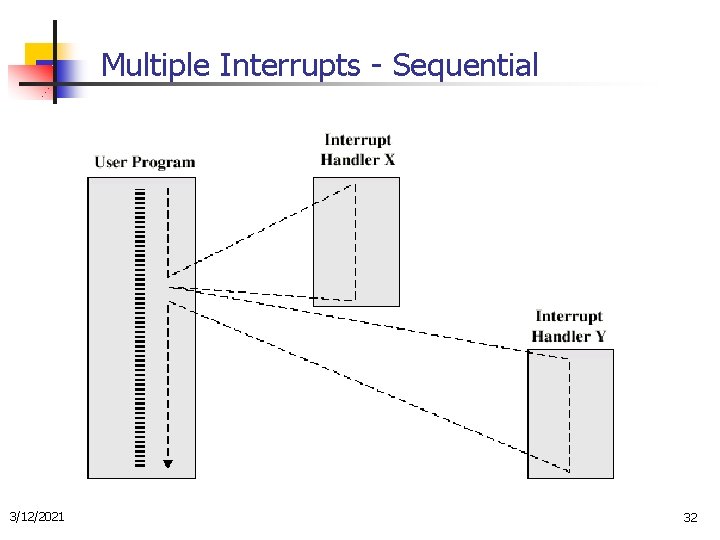

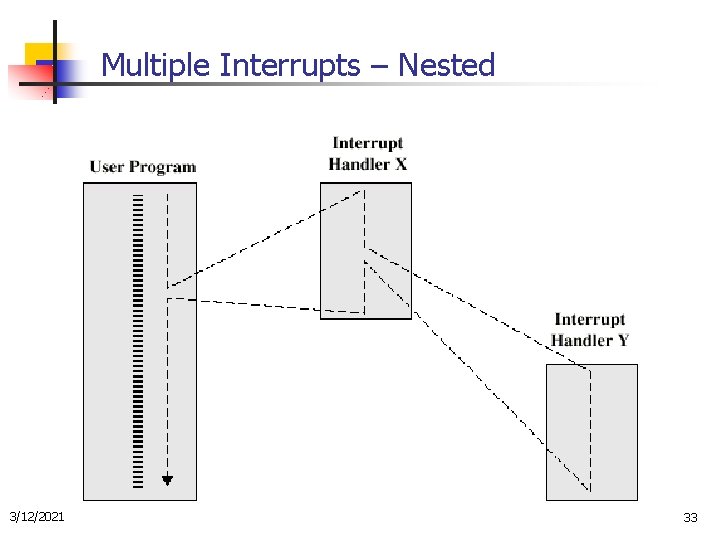

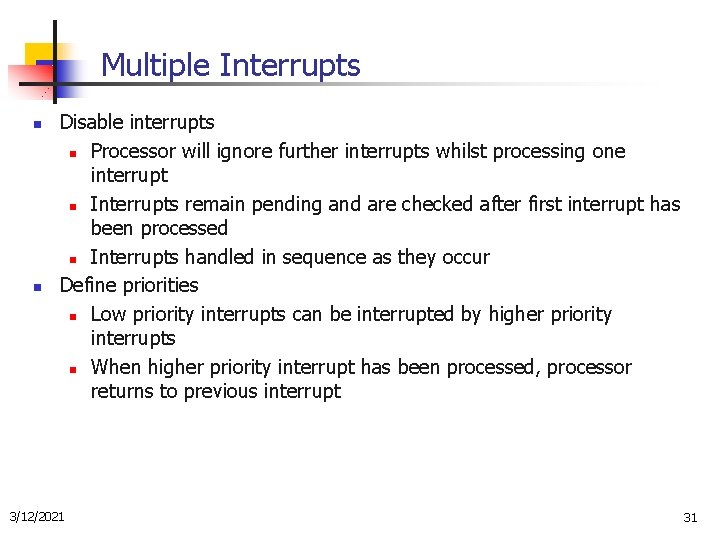

Multiple Interrupts n n Disable interrupts n Processor will ignore further interrupts whilst processing one interrupt n Interrupts remain pending and are checked after first interrupt has been processed n Interrupts handled in sequence as they occur Define priorities n Low priority interrupts can be interrupted by higher priority interrupts n When higher priority interrupt has been processed, processor returns to previous interrupt 3/12/2021 31

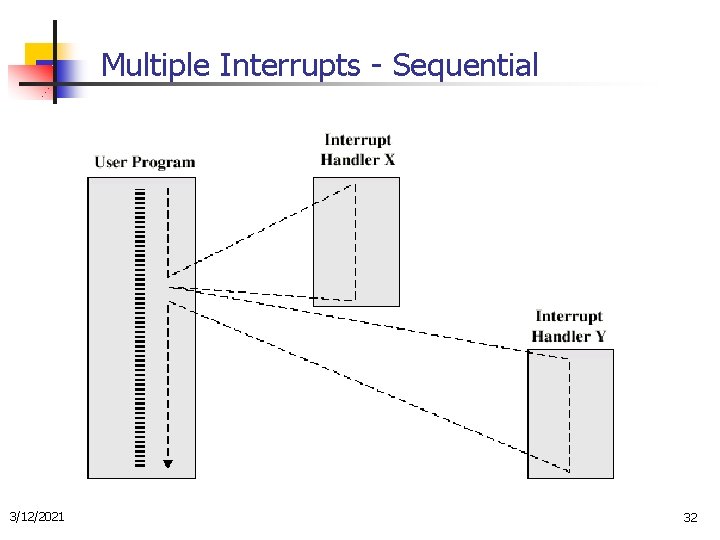

Multiple Interrupts - Sequential 3/12/2021 32

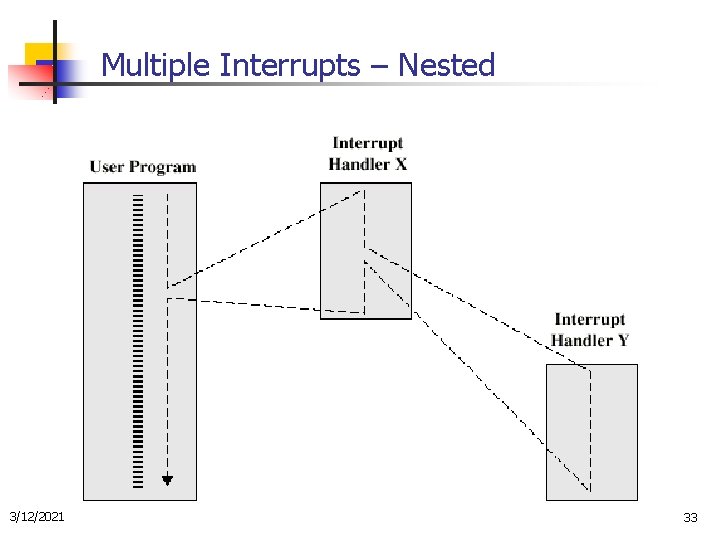

Multiple Interrupts – Nested 3/12/2021 33

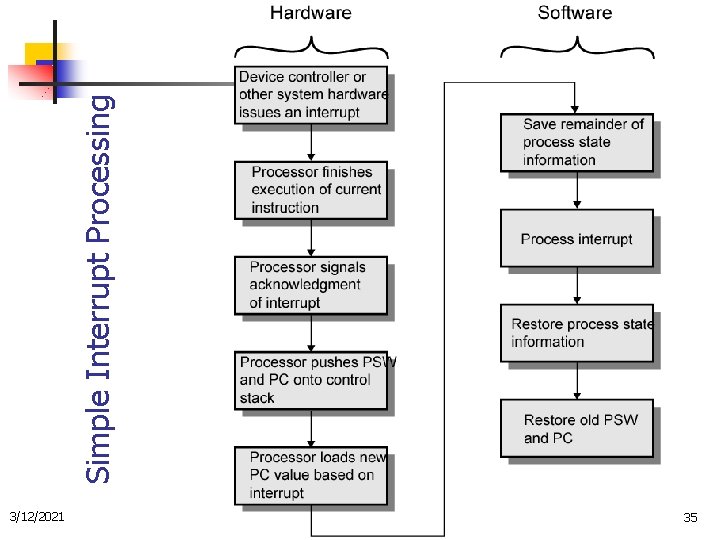

Interrupt Driven I/O: Basic Operation n n CPU issues read command I/O module gets data from peripheral whilst CPU does other work I/O module interrupts CPU requests data I/O module transfers data 3/12/2021 34

3/12/2021 35 Simple Interrupt Processing

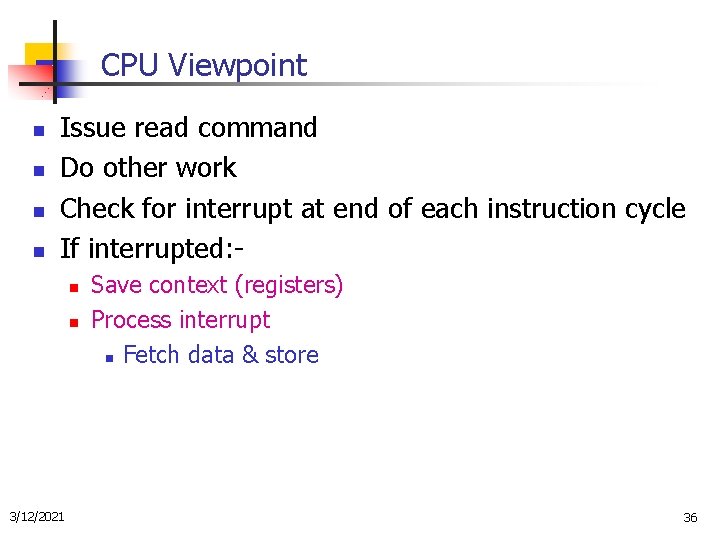

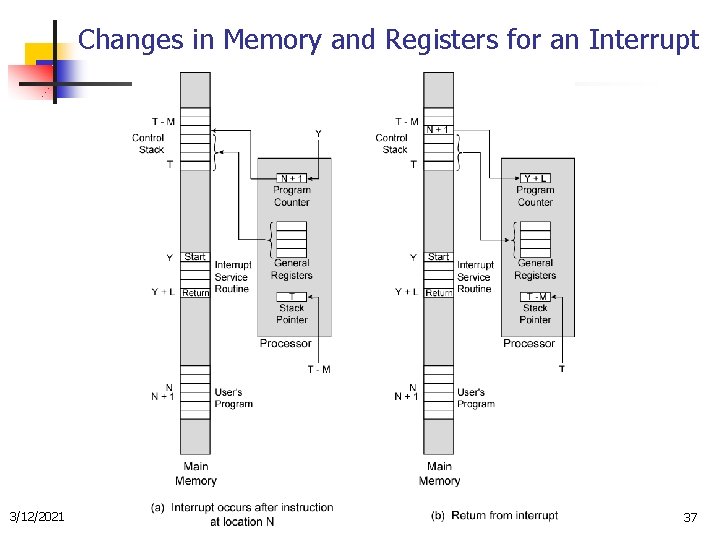

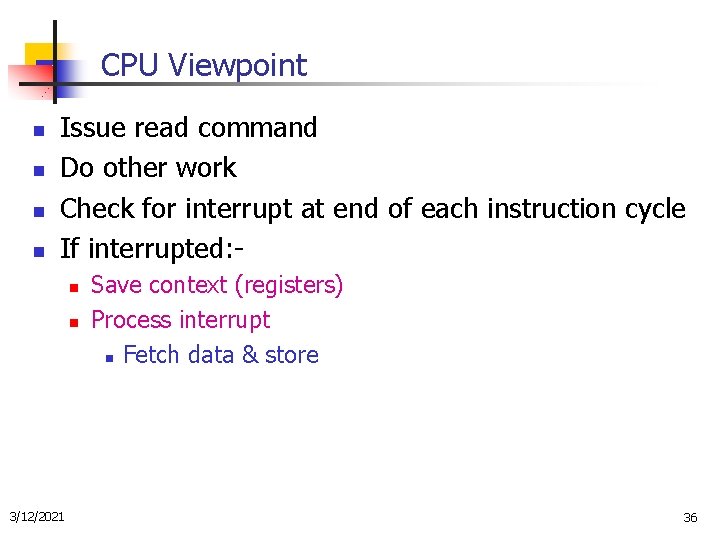

CPU Viewpoint n n Issue read command Do other work Check for interrupt at end of each instruction cycle If interrupted: n n 3/12/2021 Save context (registers) Process interrupt n Fetch data & store 36

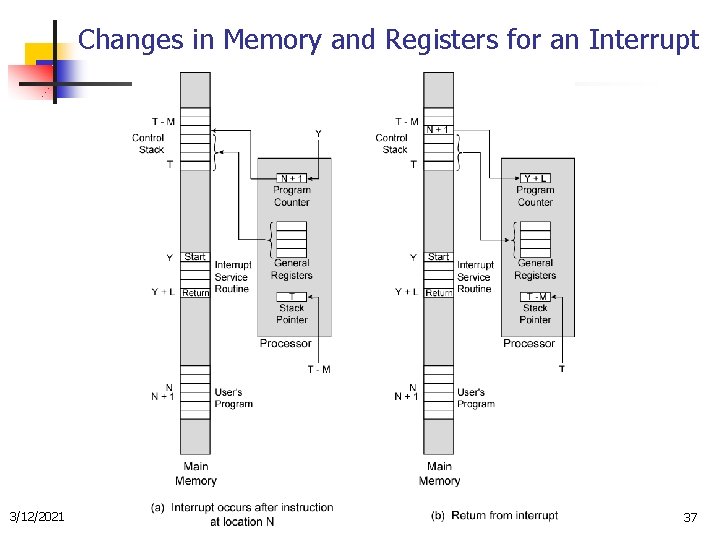

Changes in Memory and Registers for an Interrupt 3/12/2021 37

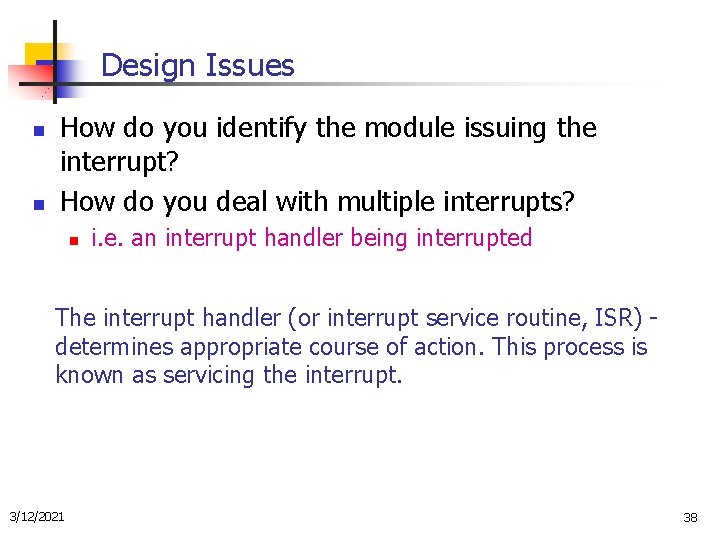

Design Issues n n How do you identify the module issuing the interrupt? How do you deal with multiple interrupts? n i. e. an interrupt handler being interrupted The interrupt handler (or interrupt service routine, ISR) determines appropriate course of action. This process is known as servicing the interrupt. 3/12/2021 38

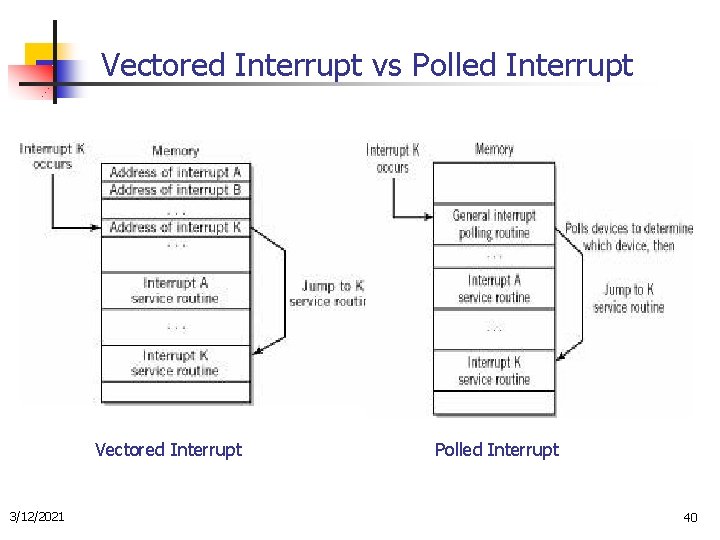

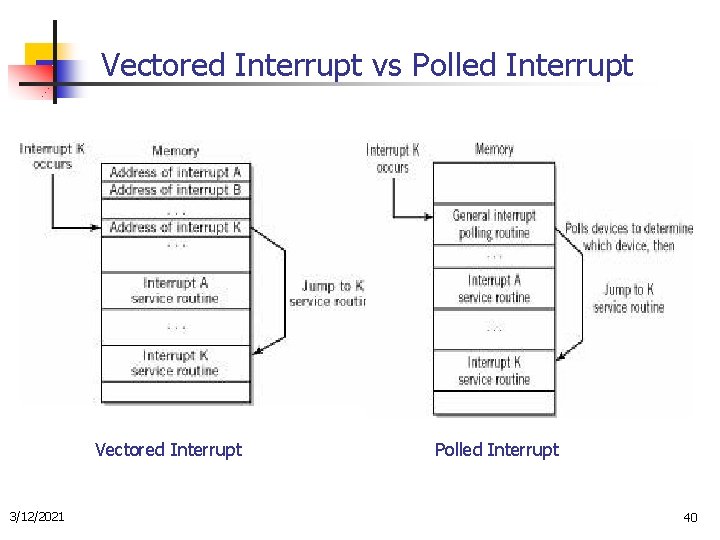

Identifying Interrupting Module (1) n Different line for each module n n Limits number of devices A vectored interrupt is used, in which the address of the interrupting device is included as part of the interrupt. Faster, but requires additional hardware to implement. Software poll n n n 3/12/2021 Use a general interrupt that is shared by all devices. CPU asks each module in turn Slow 39

Vectored Interrupt vs Polled Interrupt Vectored Interrupt 3/12/2021 Polled Interrupt 40

Identifying Interrupting Module (2) n Daisy Chain or Hardware poll n n Interrupt Acknowledge sent down a chain Module responsible places vector on bus CPU uses vector to identify handler routine Bus Master n 3/12/2021 Module must claim the bus before it can raise interrupt 41

Multiple Interrupts n n n Each interrupt line has a priority Higher priority lines can interrupt lower priority lines If bus mastering, only current master can interrupt 3/12/2021 42

Direct Memory Access n Interrupt driven and programmed I/O require active CPU intervention n Transfer rate is limited CPU is tied up DMA is the answer. n 3/12/2021 DMA is more efficient for transferring large volumes of data. 43

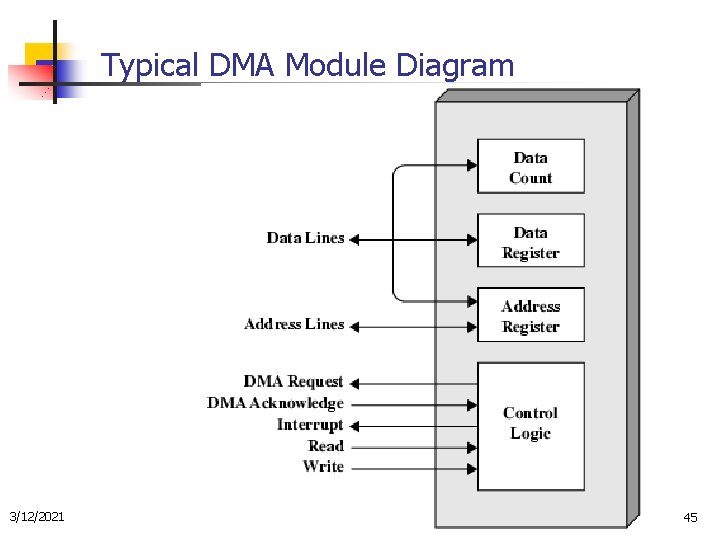

DMA Function n n Additional Module (hardware) on bus DMA controller takes over from CPU for I/O operations. 3/12/2021 44

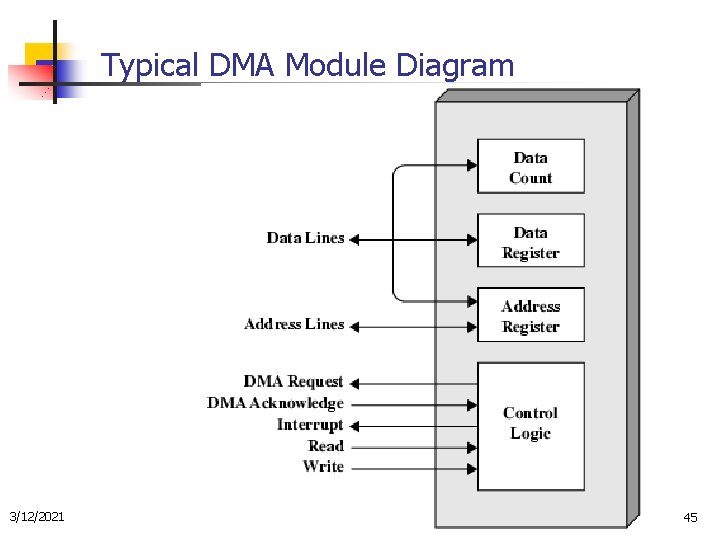

Typical DMA Module Diagram 3/12/2021 45

DMA Operation n CPU tells DMA controller: n n n n Read/Write Device address Starting address of memory block for data Amount of data to be transferred CPU carries on with other work DMA controller deals with transfer DMA controller sends interrupt when finished 3/12/2021 46

DMA Transfer: Cycle Stealing n n n DMA controller takes over bus for a cycle Transfer of one word of data Not an interrupt n n CPU suspended just before it accesses bus n n CPU does not switch context i. e. before an operand or data fetch or a data write Slows down CPU but not as much as CPU doing transfer. 3/12/2021 47

Fly-By n n While DMA using buses processor idle Processor using bus, DMA idle n n Data does not pass through and is not stored in DMA chip n n n Known as fly-by DMA controller DMA only between I/O port and memory Not between two I/O ports or two memory locations Can do memory to memory via register 3/12/2021 48

I/O Channels n n n I/O devices getting more sophisticated e. g. 3 D graphics cards CPU instructs I/O controller to do transfer I/O controller does entire transfer Improves speed n n 3/12/2021 Takes load off CPU Dedicated processor is faster 49

Thank you Q&A 3/12/2021 50