Timing in Sequential circuits Stabilization time of a

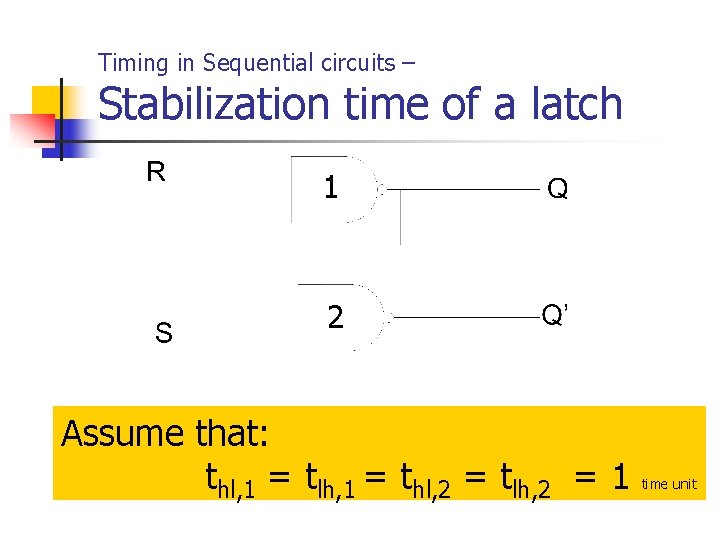

Timing in Sequential circuits – Stabilization time of a latch 1 2 Assume that: thl, 1 = tlh, 1 = thl, 2 = tlh, 2 = 1 time unit

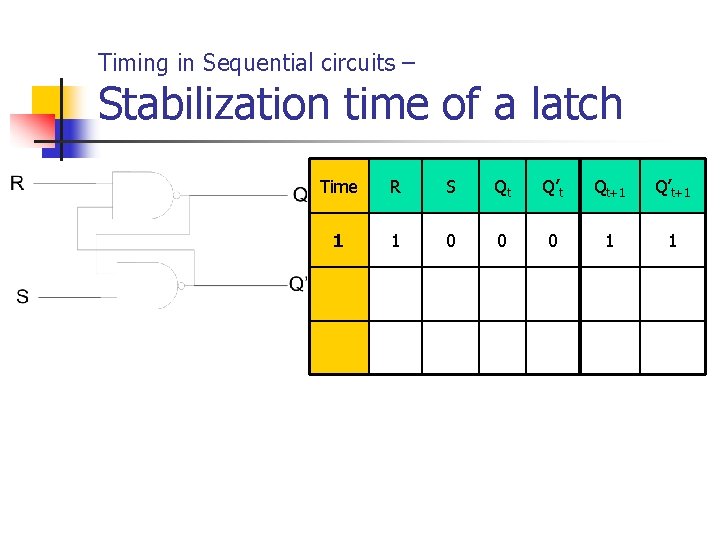

Timing in Sequential circuits – Stabilization time of a latch Time R S Qt Q’t Qt+1 Q’t+1 1 1 0 0 0 1 1

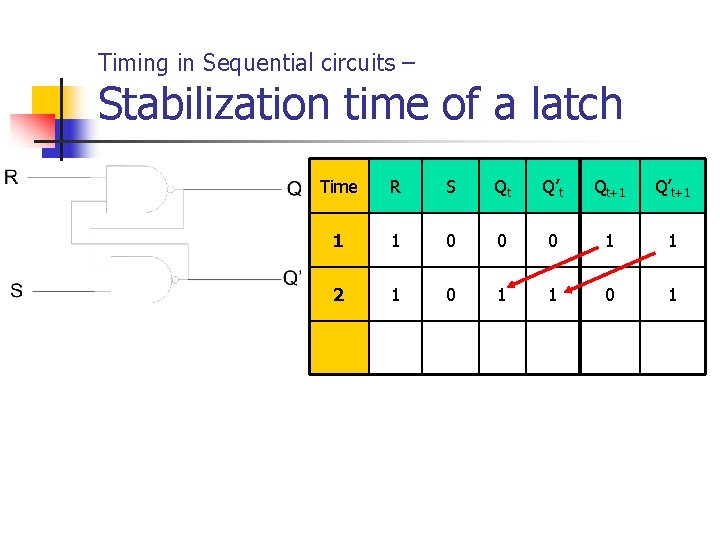

Timing in Sequential circuits – Stabilization time of a latch Time R S Qt Q’t Qt+1 Q’t+1 1 1 0 0 0 1 1 2 1 0 1

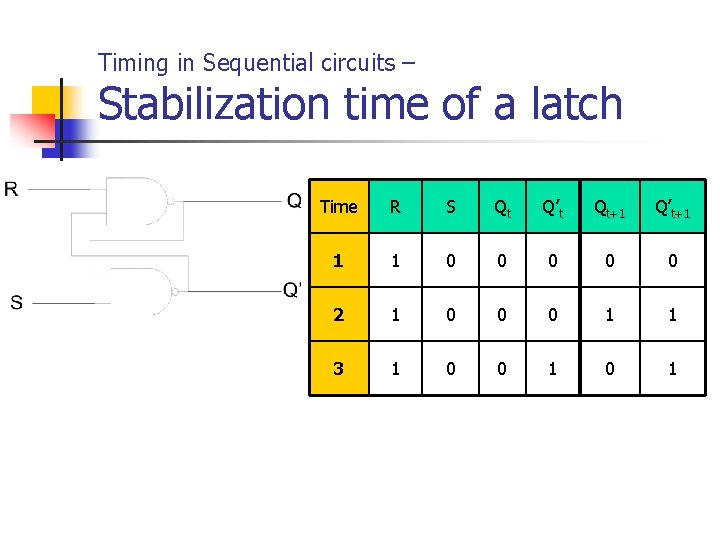

Timing in Sequential circuits – Stabilization time of a latch Time R S Qt Q’t Qt+1 Q’t+1 1 1 0 0 0 2 1 0 0 0 1 1 3 1 0 0 1

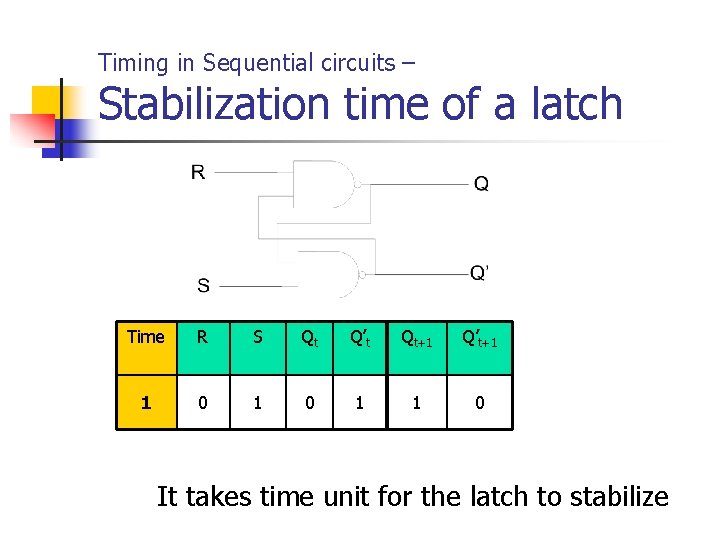

Timing in Sequential circuits – Stabilization time of a latch Time R S Qt Q’t Qt+1 Q’t+1 1 0 It takes time unit for the latch to stabilize

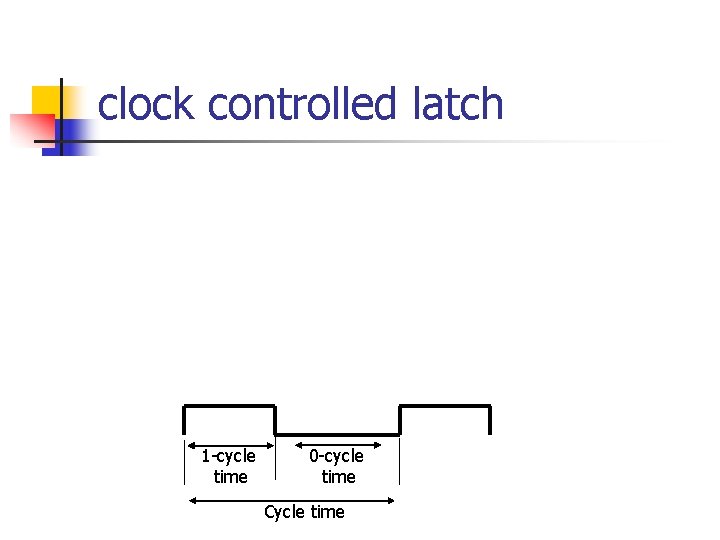

clock controlled latch 1 -cycle time 0 -cycle time Cycle time

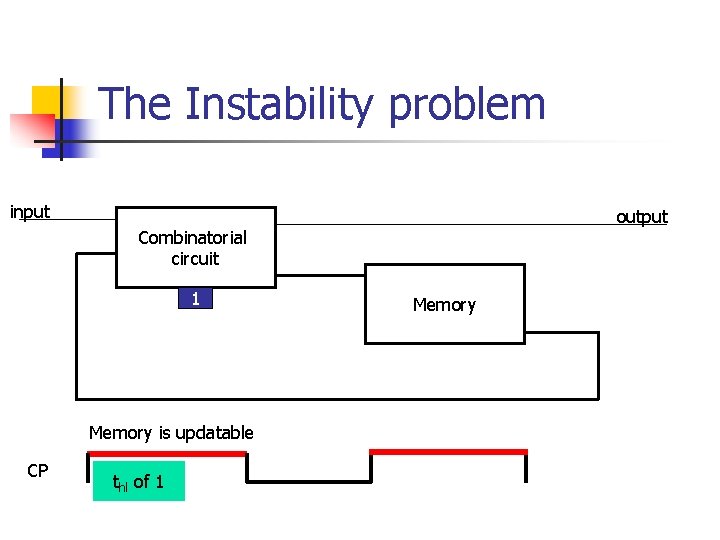

The Instability problem input output Combinatorial circuit 1 Memory is updatable CP thl of 1 Memory

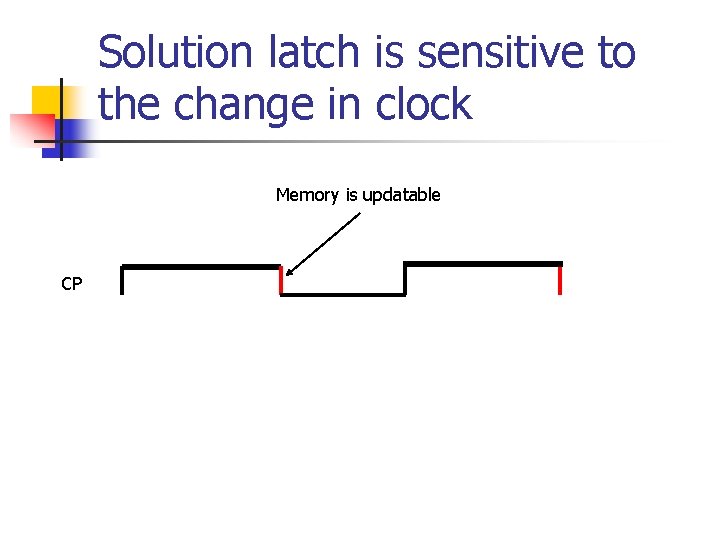

Solution latch is sensitive to the change in clock Memory is updatable CP

Timing in Sequential circuits – Master-Slave Flip Flop 1 2

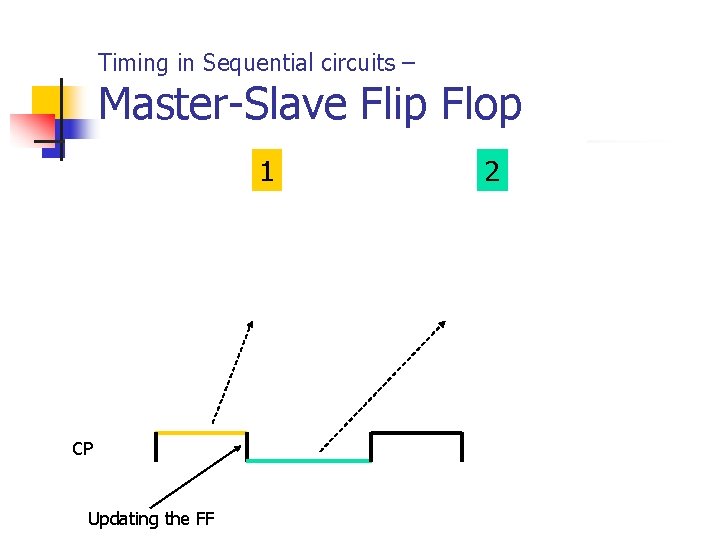

Timing in Sequential circuits – Master-Slave Flip Flop 1 CP Updating the FF 2

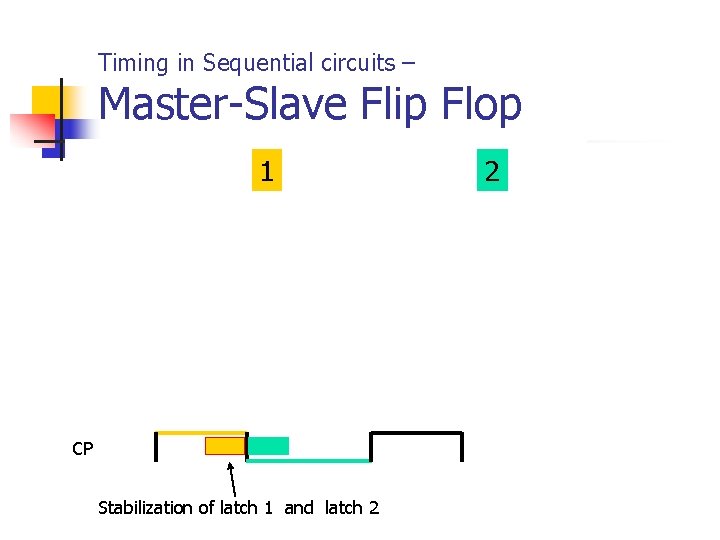

Timing in Sequential circuits – Master-Slave Flip Flop 1 CP Stabilization of latch 1 and latch 2 2

Timing in Sequential circuits – Edge triggered D-Flip Flop

Timing in Sequential circuits – Edge triggered D-Flip Flop

Timing in Sequential circuits – Edge triggered D-Flip Flop

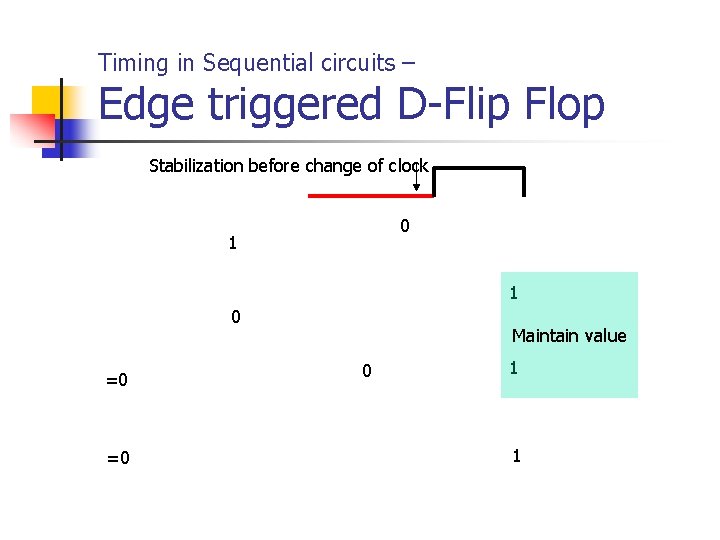

Timing in Sequential circuits – Edge triggered D-Flip Flop Stabilization before change of clock 0 1 1 0 =0 =0 Maintain value 0 1 1

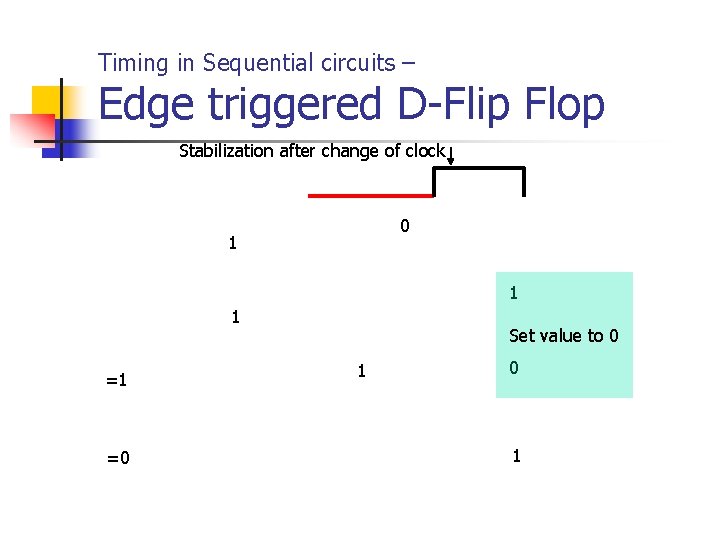

Timing in Sequential circuits – Edge triggered D-Flip Flop Stabilization after change of clock 0 1 1 1 =1 =0 Set value to 0 1

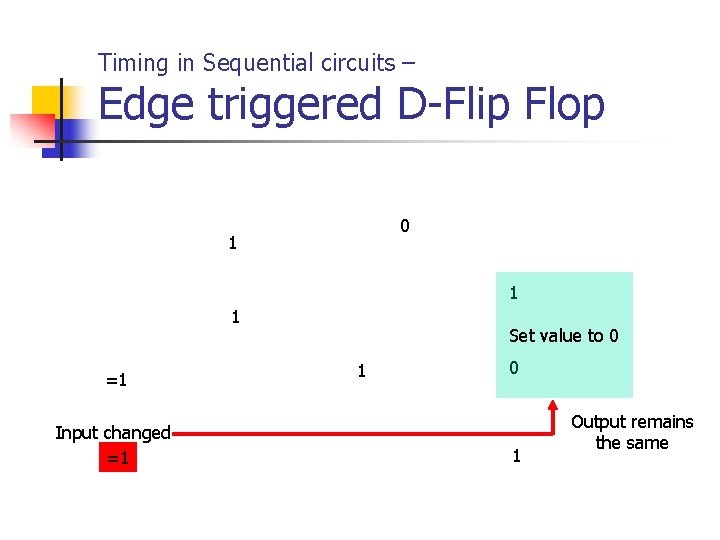

Timing in Sequential circuits – Edge triggered D-Flip Flop 0 1 1 1 =1 Input changed =1 Set value to 0 1 Output remains the same

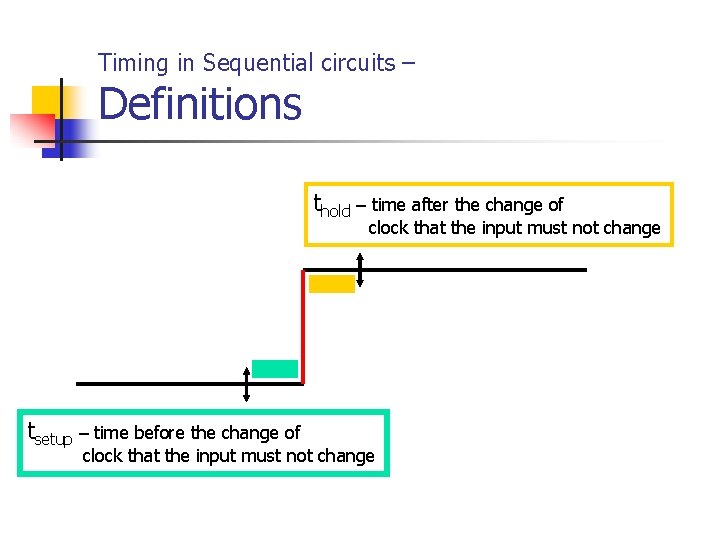

Timing in Sequential circuits – Definitions thold – time after the change of clock that the input must not change tsetup – time before the change of clock that the input must not change

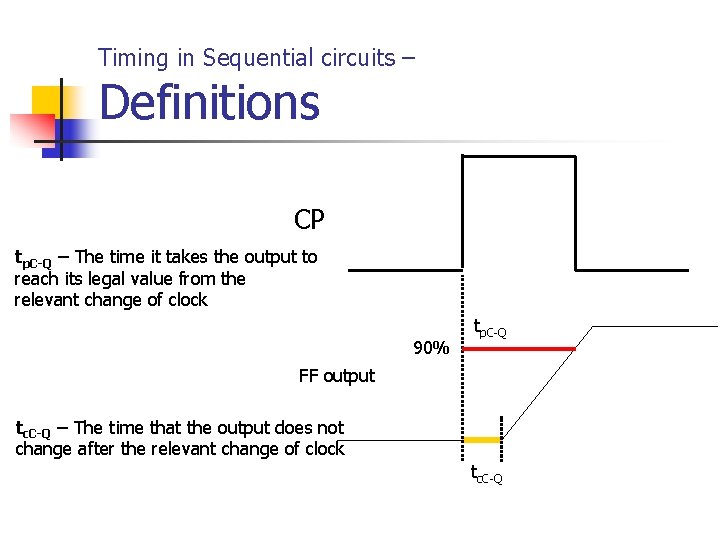

Timing in Sequential circuits – Definitions CP tp. C-Q – The time it takes the output to reach its legal value from the relevant change of clock 90% tp. C-Q FF output tc. C-Q – The time that the output does not change after the relevant change of clock tc. C-Q

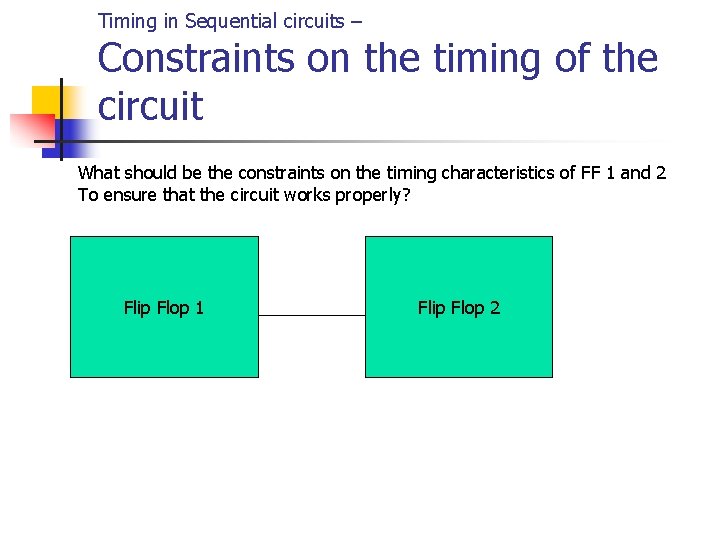

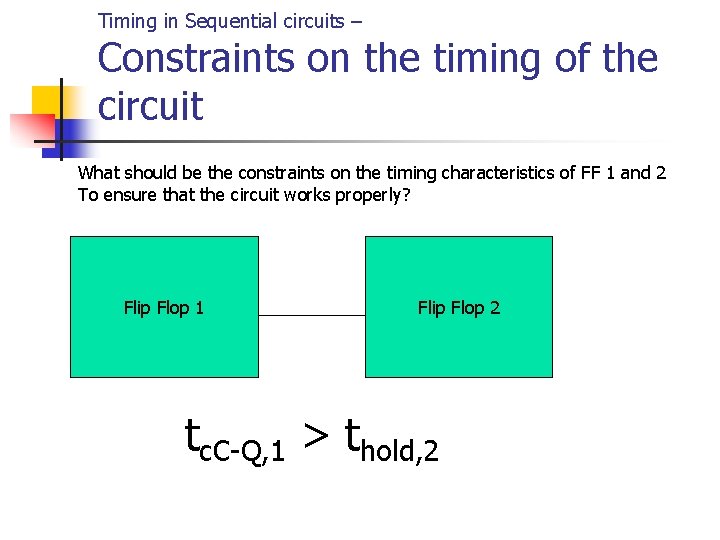

Timing in Sequential circuits – Constraints on the timing of the circuit What should be the constraints on the timing characteristics of FF 1 and 2 To ensure that the circuit works properly? Flip Flop 1 Flip Flop 2

Timing in Sequential circuits – Constraints on the timing of the circuit What should be the constraints on the timing characteristics of FF 1 and 2 To ensure that the circuit works properly? Flip Flop 1 Flip Flop 2 tc. C-Q, 1 > thold, 2

Timing in Sequential circuits – Analyzing a circuit X 1 X 2 2 1 D - FF Updating the variables in the negative edge (decrease from 1 to 0) FF locks in positive edge (increase from 0 to 1). 1. What is the minimal cycle time (what are the durations of each phase)? 2. What is the maximal delay of the circuit output? 3. What are the conditions on the timing properties of the clock such that the circuit will work properly?

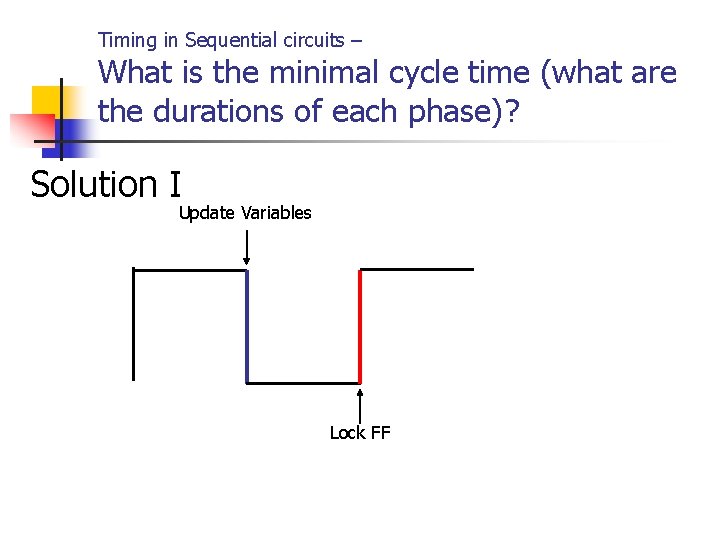

Timing in Sequential circuits – What is the minimal cycle time (what are the durations of each phase)? Solution I Update Variables Lock FF

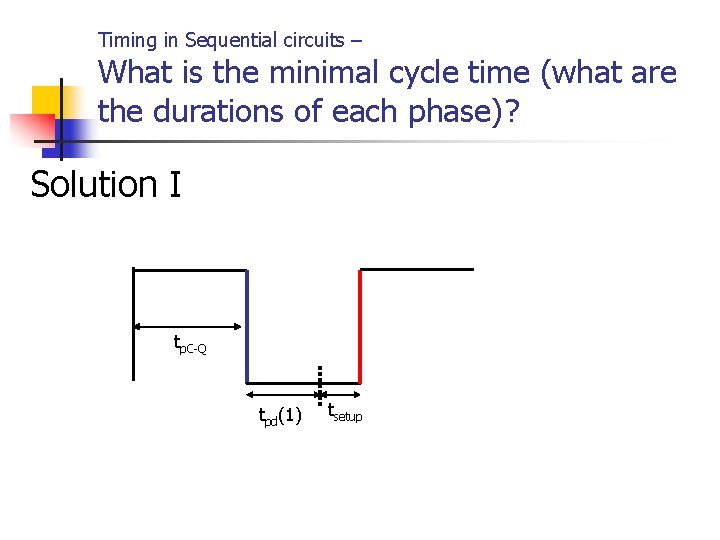

Timing in Sequential circuits – What is the minimal cycle time (what are the durations of each phase)? Solution I tp. C-Q tpd(1) tsetup

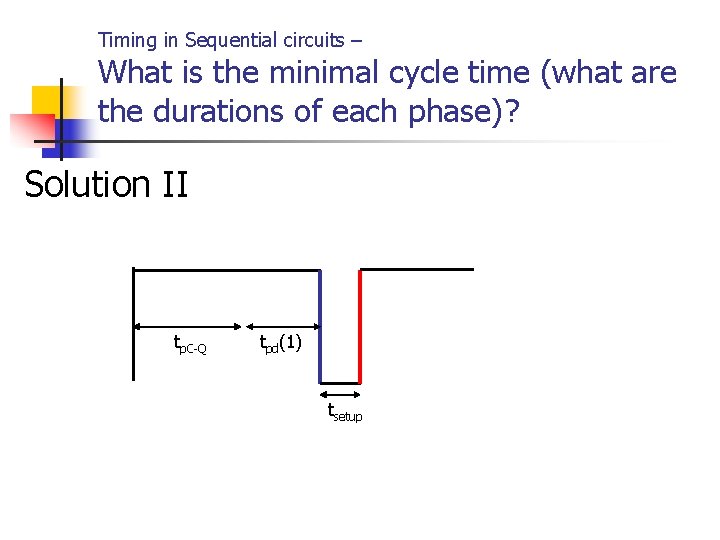

Timing in Sequential circuits – What is the minimal cycle time (what are the durations of each phase)? Solution II tp. C-Q tpd(1) tsetup

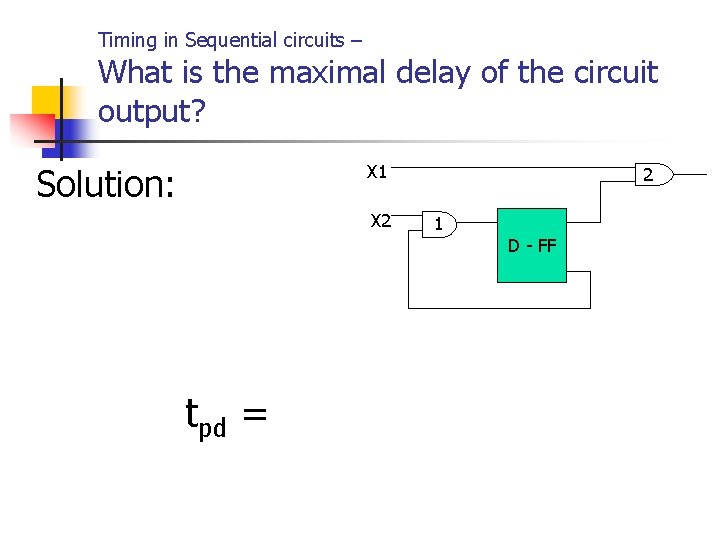

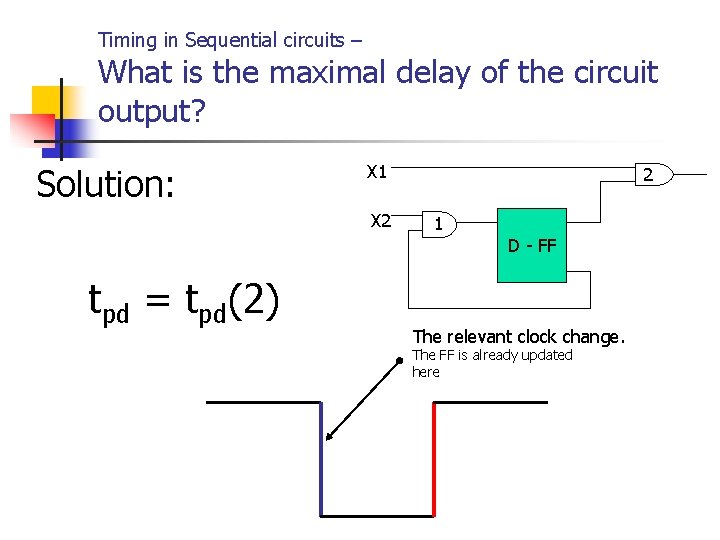

Timing in Sequential circuits – What is the maximal delay of the circuit output? X 1 Solution: X 2 2 1 D - FF tpd =

Timing in Sequential circuits – What is the maximal delay of the circuit output? Solution: X 1 X 2 2 1 D - FF tpd = tpd(2) The relevant clock change. The FF is already updated here

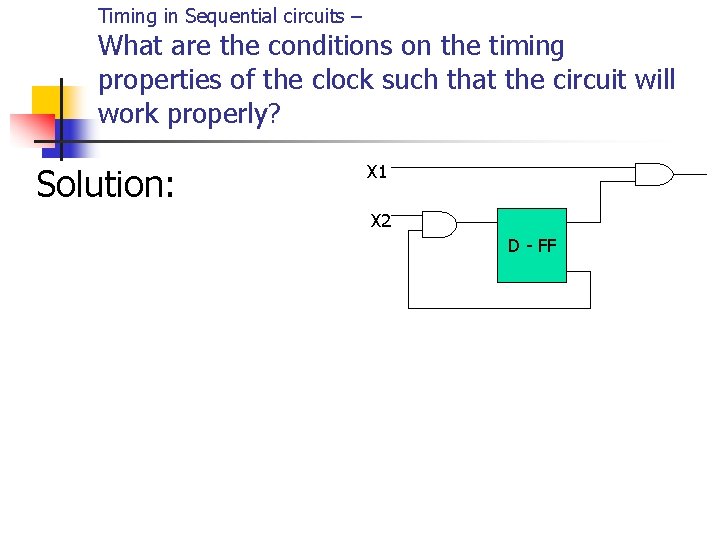

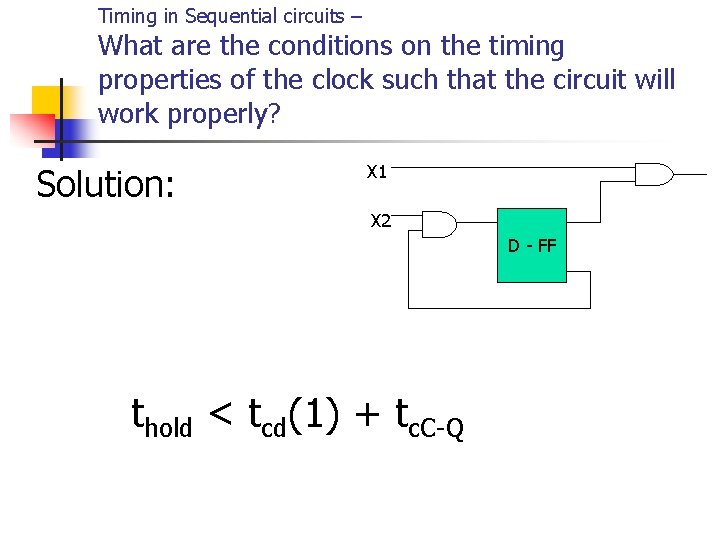

Timing in Sequential circuits – What are the conditions on the timing properties of the clock such that the circuit will work properly? Solution: X 1 X 2 D - FF

Timing in Sequential circuits – What are the conditions on the timing properties of the clock such that the circuit will work properly? Solution: X 1 X 2 D - FF thold < tcd(1) + tc. C-Q

- Slides: 29