Timing Faults in VLSI circuits Elzbieta Piwowarska Institute

Timing Faults in VLSI circuits Elzbieta Piwowarska Institute of Microelectronics and Optoelectronics Warsaw University of Technology Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O

Agenda • Timing analysis of integrated circuits – timing designing – timing spreadsheet – worst-case timing spreadsheet – statistical spreadsheet • Timing faults – propagation effects – interference effects – power noise – clock skew and jitter • conclusions Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 2

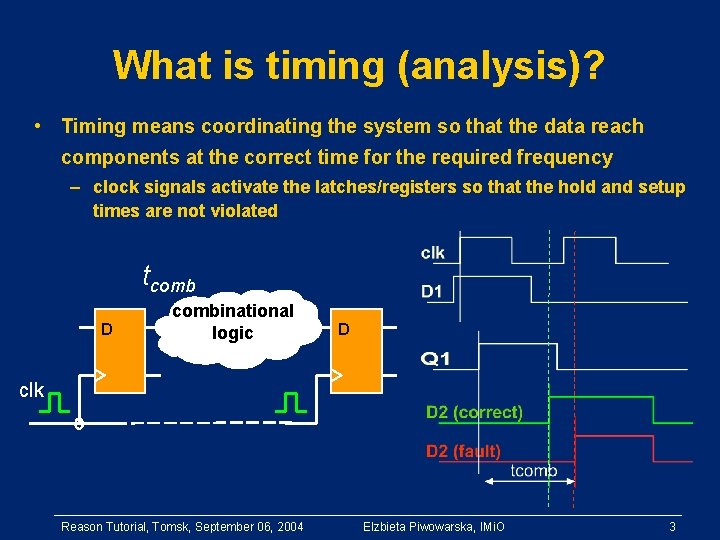

What is timing (analysis)? • Timing means coordinating the system so that the data reach components at the correct time for the required frequency – clock signals activate the latches/registers so that the hold and setup times are not violated tcomb D combinational logic D clk Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 3

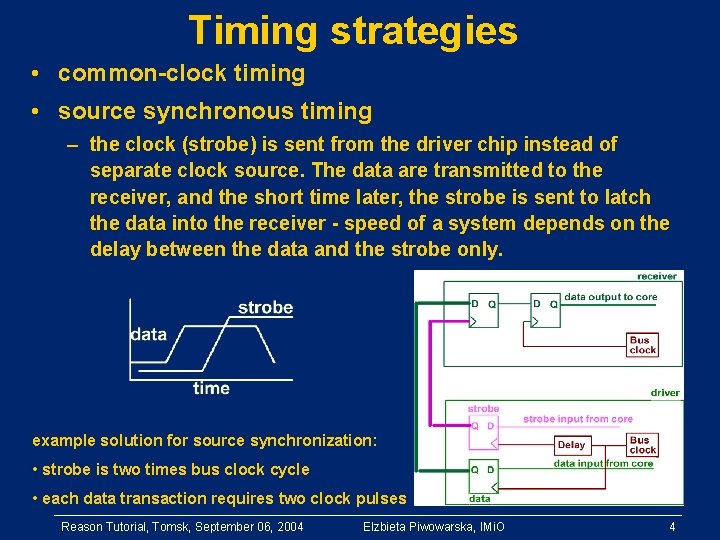

Timing strategies • common-clock timing • source synchronous timing – the clock (strobe) is sent from the driver chip instead of separate clock source. The data are transmitted to the receiver, and the short time later, the strobe is sent to latch the data into the receiver - speed of a system depends on the delay between the data and the strobe only. example solution for source synchronization: • strobe is two times bus clock cycle • each data transaction requires two clock pulses Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 4

Timing designing • define the initial system timings – estimate the values of max and min setup and hold times for each component of the system – estimate the values of max and min skew and jitter – estimate the delays of components and interconnects • use the spreadsheet to implement timing equations and get the starting point for the design – assume the certain amount of margin for interconnect delays • improve the design after post-layout analysis Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 5

Timing spreadsheet • It allows the components designing team (silicon designers) and system design team to coordinate working on a system. • It is updated periodically, it shows the progress of the design, set design targets, perform timing trade-offs. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 6

Worst-case timing spreadsheet • It assumes that all components meet the worst possible performance (the greatest delays, skew, jitter etc. ). • This assumptions guaranties that the product will be reliable and robust. • For systems with very high speed the worst-case assumption might make impossible to design the system - the calculations show the negative margin for the required frequency. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 7

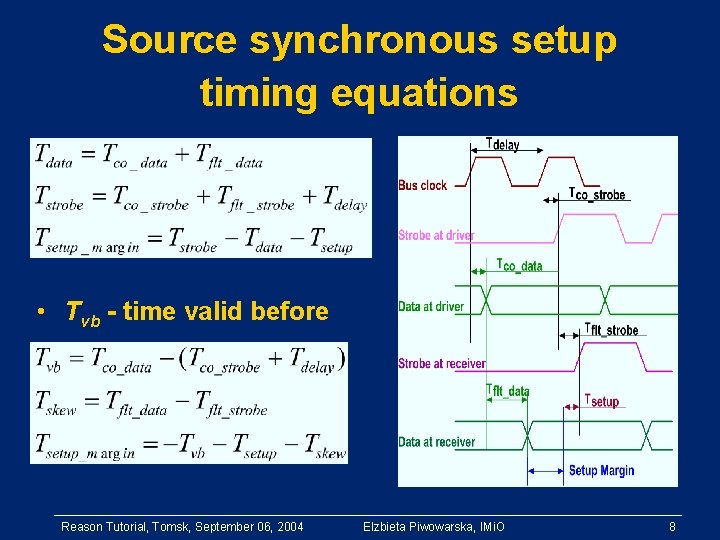

Source synchronous setup timing equations • Tvb - time valid before Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 8

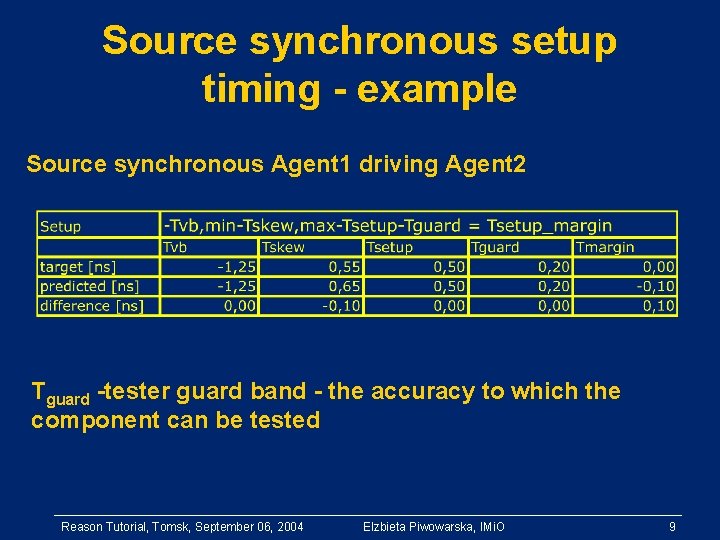

Source synchronous setup timing - example Source synchronous Agent 1 driving Agent 2 Tguard -tester guard band - the accuracy to which the component can be tested Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 9

Statistical spreadsheet • existing in conjunction with the worst-case spreadsheet • the probability of the negative margin is calculated. If it is acceptable small the design will proceed. • the mean and a standard deviation are obtained for each component • It assumes approximately normal (Gaussian) distributions and that the components are completely independent on each other - this works good as a next iteration of the design. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 10

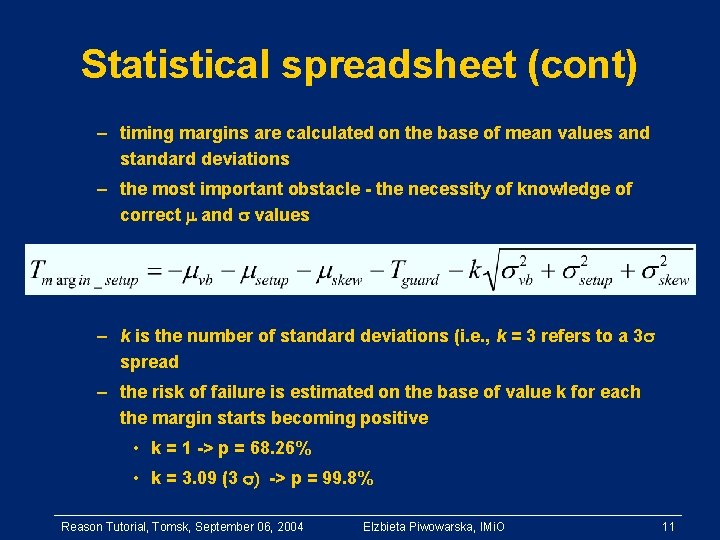

Statistical spreadsheet (cont) – timing margins are calculated on the base of mean values and standard deviations – the most important obstacle - the necessity of knowledge of correct m and s values – k is the number of standard deviations (i. e. , k = 3 refers to a 3 s spread – the risk of failure is estimated on the base of value k for each the margin starts becoming positive • k = 1 -> p = 68. 26% • k = 3. 09 (3 s) -> p = 99. 8% Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 11

• Now the additional effects affecting timing values must be taken into account. • These additional effects are noises caused by the influence of many working components on each other. • The performance metrics should be captured, defined and calculated. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 12

Design optimization • performed after the initial timings and the metrics have been defined • begins with the determination of all the signal categories within the design – common-clock signals – source-synchronous signals – controls – clock – other categories • determination the estimates of all the system variables i. e. : – I/O capacitance – interconnect parameters – buffer strengths and edge rates – termination values Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 13

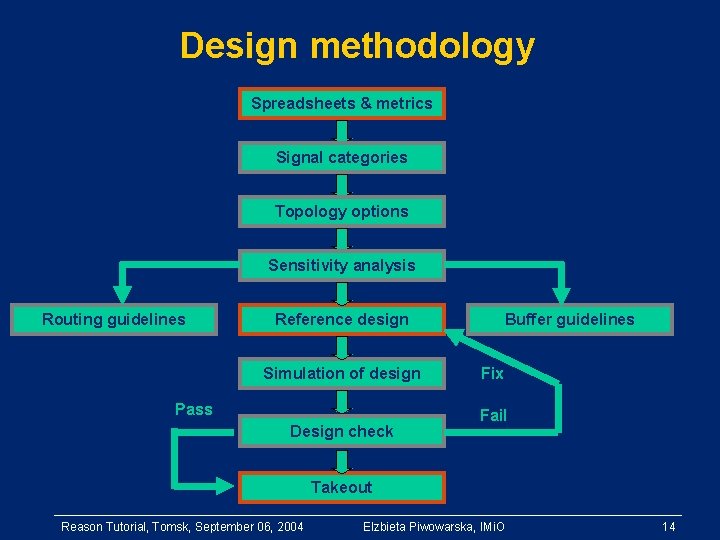

Design methodology Spreadsheets & metrics Signal categories Topology options Sensitivity analysis Routing guidelines Reference design Simulation of design Pass Design check Buffer guidelines Fix Fail Takeout Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 14

Sensitivity analysis • It ranks the variables as to how strongly they affect the system and highlight which variables affect the solution most and in what way they affect the system. • During the sensitivity analysis every variable is varied in simulation and the performance metrics are observed while each variable is swept. • The result is a solution space that will place strict limits on the variables under control of the designer (interconnect lengths, spacing etc. ). • Monte Carlo analysis is still the most common method of the sensitivity analysis. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 15

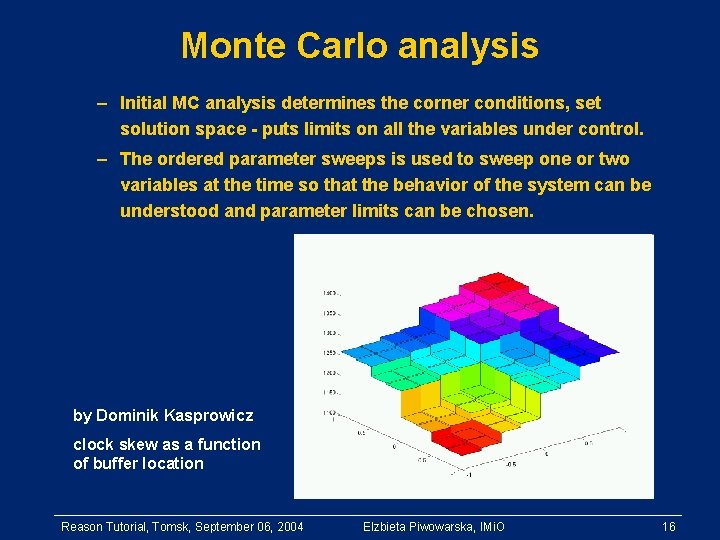

Monte Carlo analysis – Initial MC analysis determines the corner conditions, set solution space - puts limits on all the variables under control. – The ordered parameter sweeps is used to sweep one or two variables at the time so that the behavior of the system can be understood and parameter limits can be chosen. by Dominik Kasprowicz clock skew as a function of buffer location Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 16

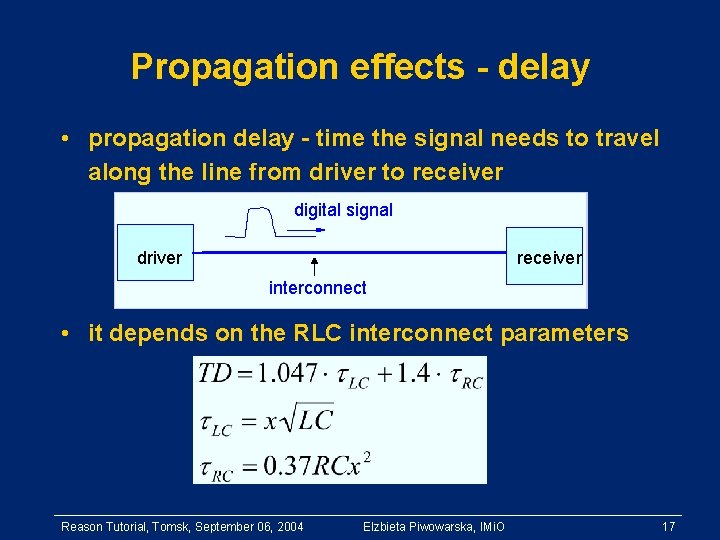

Propagation effects - delay • propagation delay - time the signal needs to travel along the line from driver to receiver digital signal driver receiver interconnect • it depends on the RLC interconnect parameters Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 17

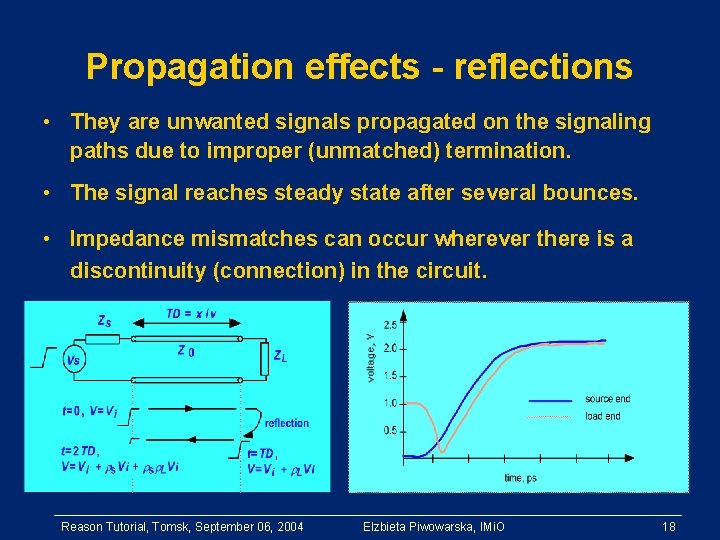

Propagation effects - reflections • They are unwanted signals propagated on the signaling paths due to improper (unmatched) termination. • The signal reaches steady state after several bounces. • Impedance mismatches can occur wherever there is a discontinuity (connection) in the circuit. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 18

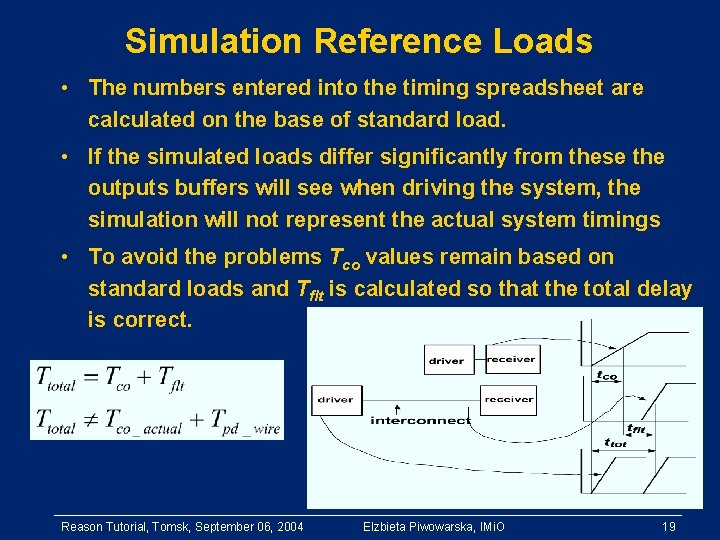

Simulation Reference Loads • The numbers entered into the timing spreadsheet are calculated on the base of standard load. • If the simulated loads differ significantly from these the outputs buffers will see when driving the system, the simulation will not represent the actual system timings • To avoid the problems Tco values remain based on standard loads and Tflt is calculated so that the total delay is correct. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 19

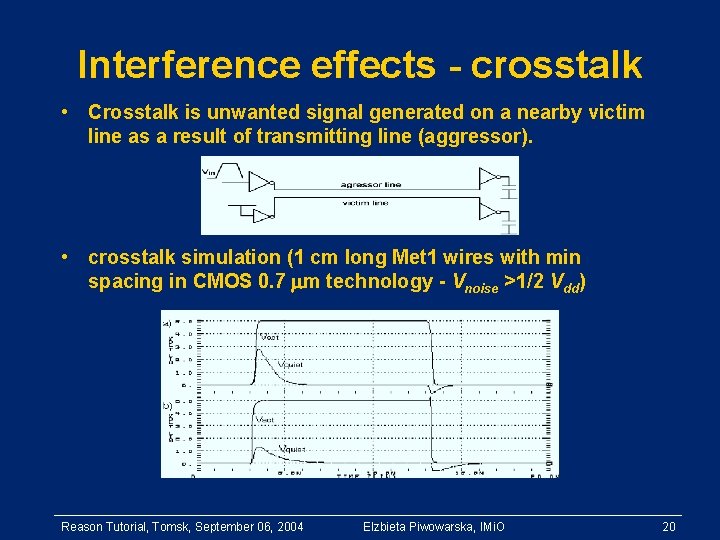

Interference effects - crosstalk • Crosstalk is unwanted signal generated on a nearby victim line as a result of transmitting line (aggressor). • crosstalk simulation (1 cm long Met 1 wires with min spacing in CMOS 0. 7 mm technology - Vnoise >1/2 Vdd) Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 20

Interference effects - crosstalk • caused by electric and magnetic fields, represented by mutual capacitance and inductance respectively odd mode even mode • Crosstalk effects are functions of rise and fall times of the aggressor, distance between the lines and the presence of the reference plane. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 21

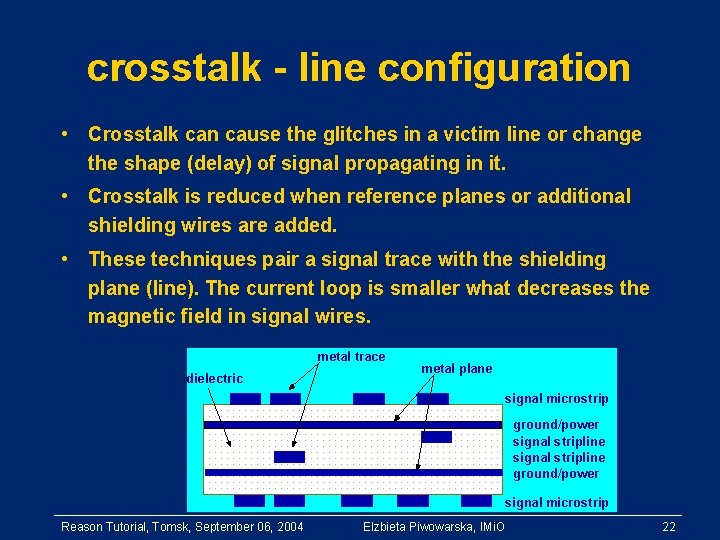

crosstalk - line configuration • Crosstalk can cause the glitches in a victim line or change the shape (delay) of signal propagating in it. • Crosstalk is reduced when reference planes or additional shielding wires are added. • These techniques pair a signal trace with the shielding plane (line). The current loop is smaller what decreases the magnetic field in signal wires. metal trace dielectric metal plane signal microstrip ground/power signal stripline ground/power signal microstrip Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 22

Timing analysis with crosstalk • The crosstalk model considering transition times and driver strength is needed – there are some models (i. e. Chen model) – they need many calculations to find the desired components of timing equations • The simplest gate delay models are not correct in crosstalk existence. • In the combinational logic, existence of crosstalk sites can cause cyclic dependency between the delays of lines. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 23

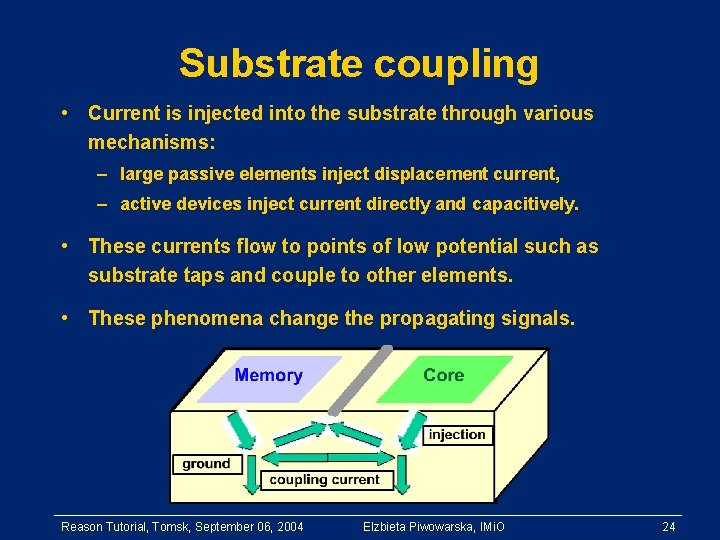

Substrate coupling • Current is injected into the substrate through various mechanisms: – large passive elements inject displacement current, – active devices inject current directly and capacitively. • These currents flow to points of low potential such as substrate taps and couple to other elements. • These phenomena change the propagating signals. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 24

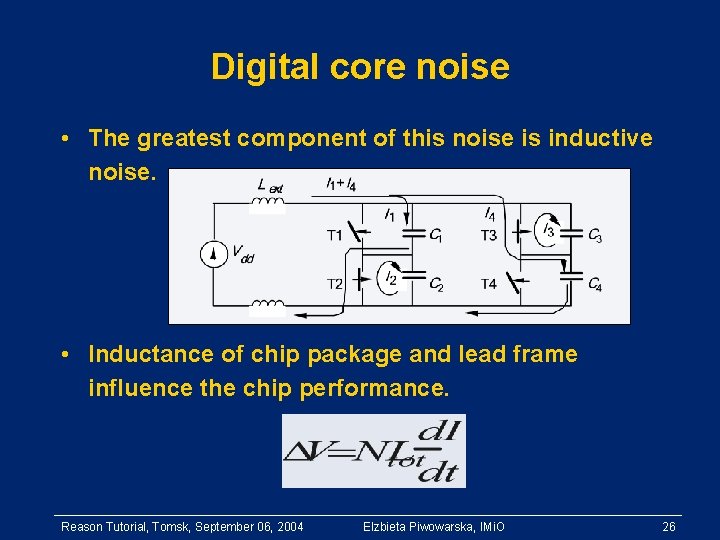

Power noise - digital core noise • called also power supply noise, simultaneous switching noise (SSN), delta I noise • the greatest contributors to this noise are clock trees and memory structures • these elements generate large spikes of current when switching • thousands of flops transitioning through the switching zone simultaneously can draw enough current to momentarily pull the core Vdd significantly down Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 25

Digital core noise • The greatest component of this noise is inductive noise. • Inductance of chip package and lead frame influence the chip performance. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 26

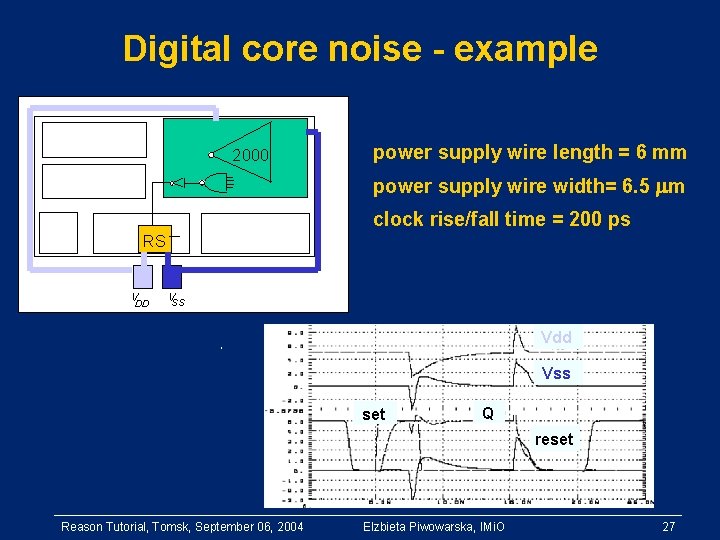

Digital core noise - example 2000 power supply wire length = 6 mm power supply wire width= 6. 5 mm clock rise/fall time = 200 ps RS VDD VSS Vdd Vss set Q reset Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 27

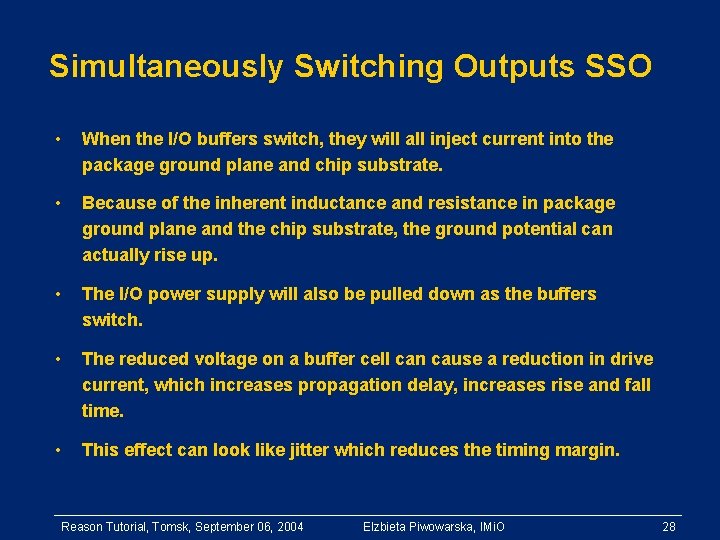

Simultaneously Switching Outputs SSO • When the I/O buffers switch, they will all inject current into the package ground plane and chip substrate. • Because of the inherent inductance and resistance in package ground plane and the chip substrate, the ground potential can actually rise up. • The I/O power supply will also be pulled down as the buffers switch. • The reduced voltage on a buffer cell can cause a reduction in drive current, which increases propagation delay, increases rise and fall time. • This effect can look like jitter which reduces the timing margin. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 28

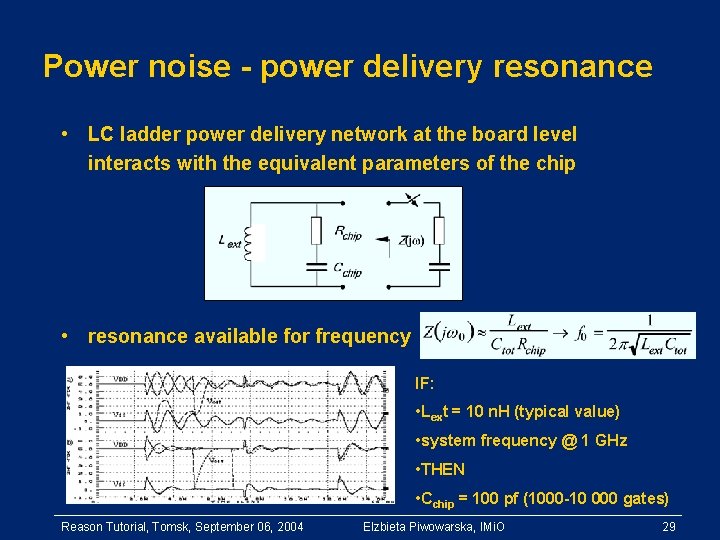

Power noise - power delivery resonance • LC ladder power delivery network at the board level interacts with the equivalent parameters of the chip • resonance available for frequency IF: • Lext = 10 n. H (typical value) • system frequency @ 1 GHz • THEN • Cchip = 100 pf (1000 -10 000 gates) Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 29

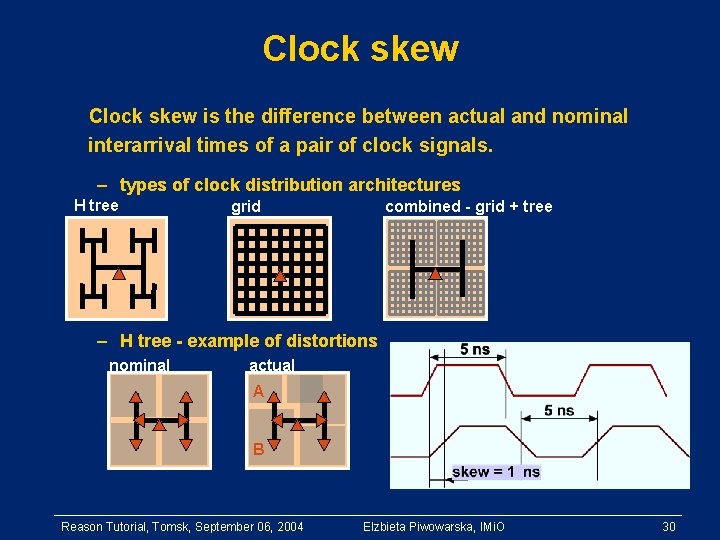

Clock skew is the difference between actual and nominal interarrival times of a pair of clock signals. – types of clock distribution architectures H tree grid combined - grid + tree – H tree - example of distortions nominal actual A B Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 30

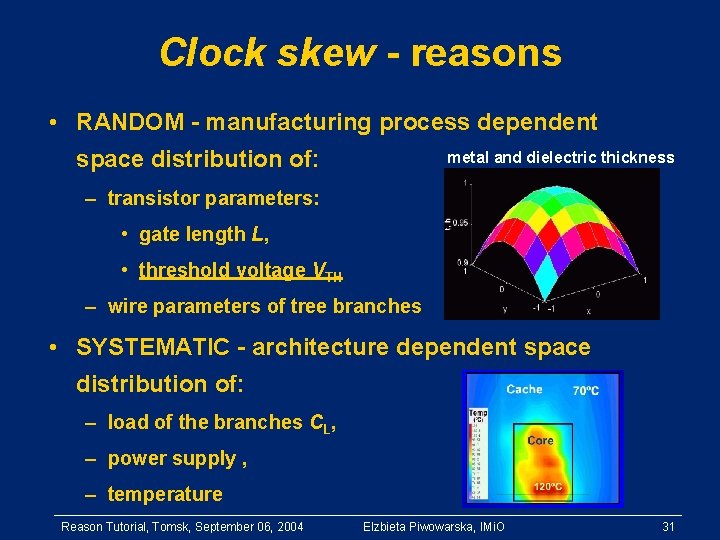

Clock skew - reasons • RANDOM - manufacturing process dependent space distribution of: metal and dielectric thickness – transistor parameters: • gate length L, • threshold voltage VTH – wire parameters of tree branches • SYSTEMATIC - architecture dependent space distribution of: – load of the branches CL, – power supply , – temperature Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 31

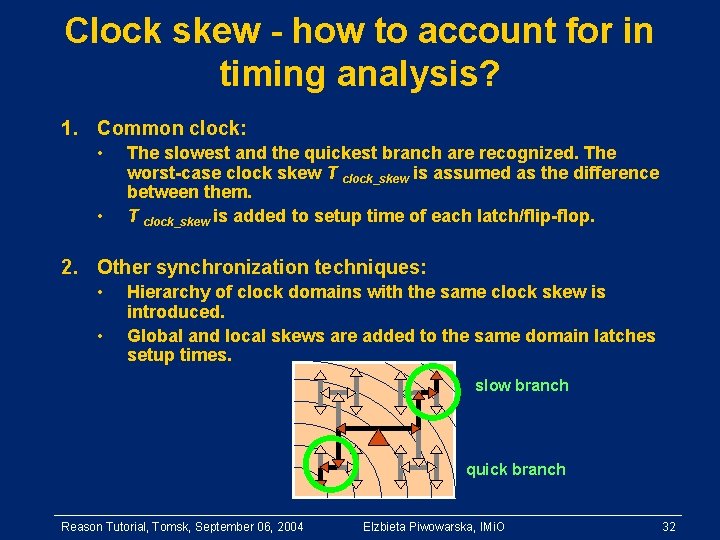

Clock skew - how to account for in timing analysis? 1. Common clock: • • The slowest and the quickest branch are recognized. The worst-case clock skew T clock_skew is assumed as the difference between them. T clock_skew is added to setup time of each latch/flip-flop. 2. Other synchronization techniques: • • Hierarchy of clock domains with the same clock skew is introduced. Global and local skews are added to the same domain latches setup times. slow branch quick branch Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 32

Clock jitter • Jitter means the fluctuations in the clock frequency generated usually by PLL circuits. • The greater jitter the smaller timing margin for data signals. • Jitter is caused by different noises: – – switching (d. I/dt) noise, power supply noises, substrate coupling, random noises. • It can be taken into account in the timing analysis in the similar way as clock skew, but its values are even more difficult to predict. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 33

Conclusions • Manufacturing process, architecture and layout dependent reasons result in differences of nominal and actual values for rising/falling edges and propagation times. • These effects create the loss of timing margin in timing analysis. • Unfortunately not every effect is predictable and countable - these effects must be avoided in design. • Careful timing analysis and design techniques avoiding the timing faults are the best way to ensure better yield. • There are many efforts (publications) related to timing analysis methods. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 34

References • S. H. Hall, G. W. Hall, J. A. Mc. Call, ”High_Speed Digital System Design, ” J. Wiley & Sons, Inc. 2000. • A. M. Niknejad, R. G. Meyer, ”Design, Simulatio and Applications of Inductors and Transformers for Si RF Ics, ” Kluwer Ac. P. 2003. • D. Chase “Achieving signal integrity for ASICs, PCBs and packages, ” Eedesign, Dec. 19, 2003. • D. Harris, M. Horowitz „Timing Analysis Including Clock Skew”, IEEE Trans. on CAD, vol. 18, no. 11, Nov. 1999, pp 1608 -1618 • I-De Huang, S. K. Gupta, M. Breuer, ”Accurate and Efficient Static Timing Analisys with Crosstalk, ” Proc. of ICCD’ 2002. • Dominik Kasprowicz private materials, Ph. D thesis in preparation. • Elzbieta Piwowarska - simulation results and examples - taken from different works. Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 35

Thanks for your attention! Reason Tutorial, Tomsk, September 06, 2004 Elzbieta Piwowarska, IMi. O 36

- Slides: 36