Timers in Coldfire Processor Computer Science Engineering Department

- Slides: 11

Timers in Coldfire Processor Computer Science & Engineering Department Arizona State University Tempe, AZ 85287 Dr. Yann-Hang Lee yhlee@asu. edu (480) 727 -7507 7/23

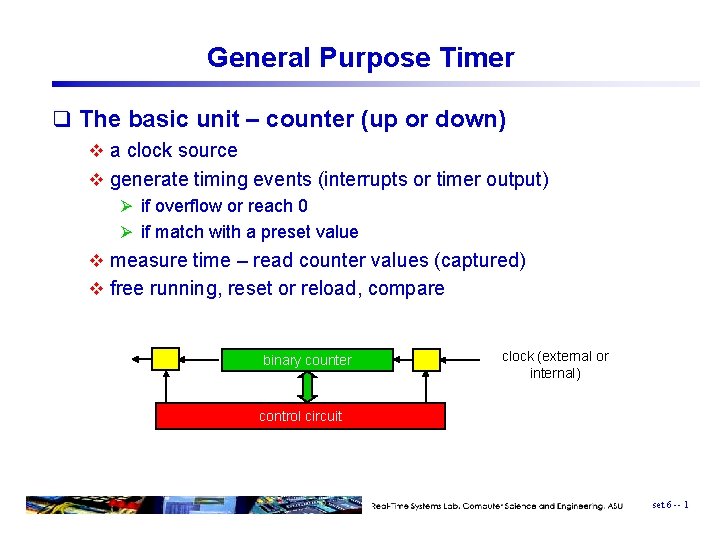

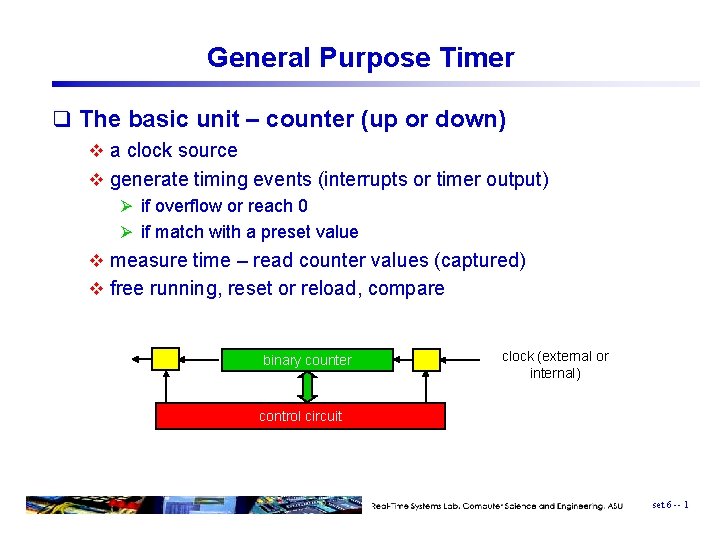

General Purpose Timer q The basic unit – counter (up or down) v a clock source v generate timing events (interrupts or timer output) Ø if overflow or reach 0 Ø if match with a preset value v measure time – read counter values (captured) v free running, reset or reload, compare binary counter clock (external or internal) control circuit set 6 -- 1

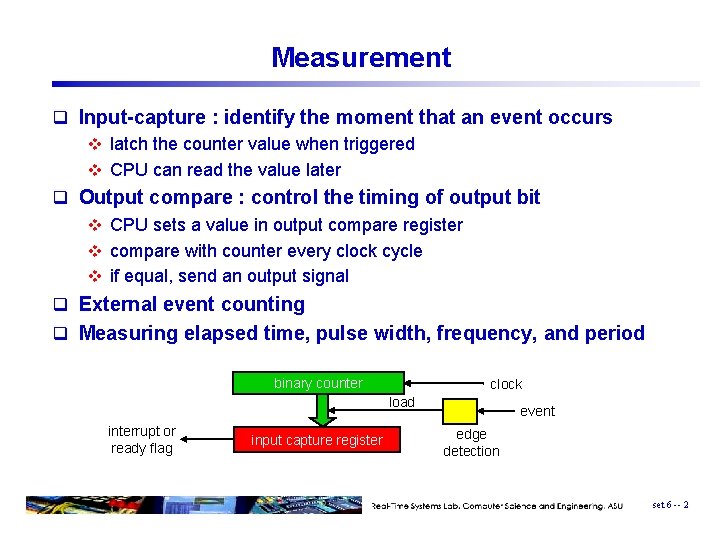

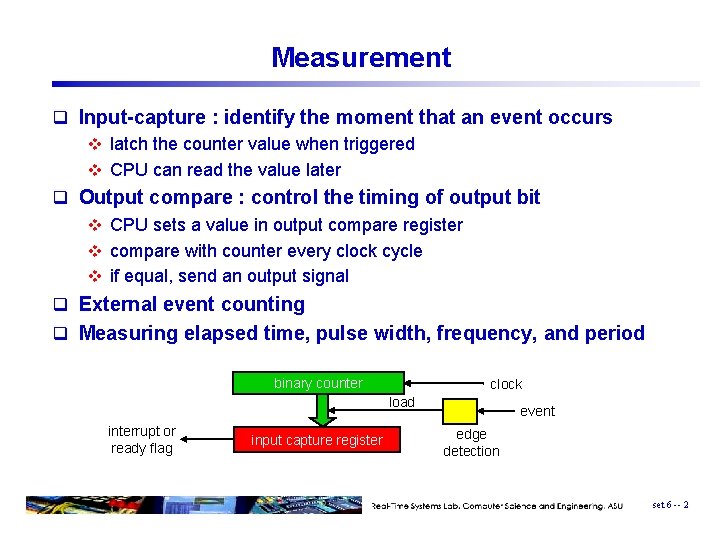

Measurement q Input-capture : identify the moment that an event occurs v latch the counter value when triggered v CPU can read the value later q Output compare : control the timing of output bit v CPU sets a value in output compare register v compare with counter every clock cycle v if equal, send an output signal q External event counting q Measuring elapsed time, pulse width, frequency, and period binary counter clock load interrupt or ready flag input capture register event edge detection set 6 -- 2

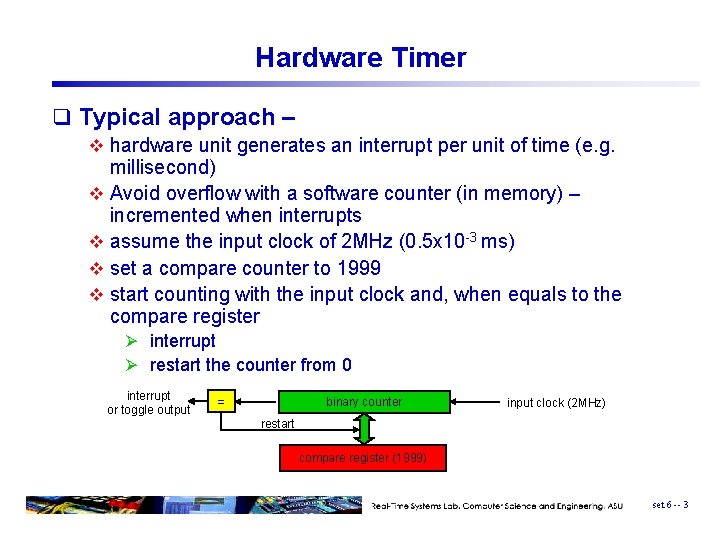

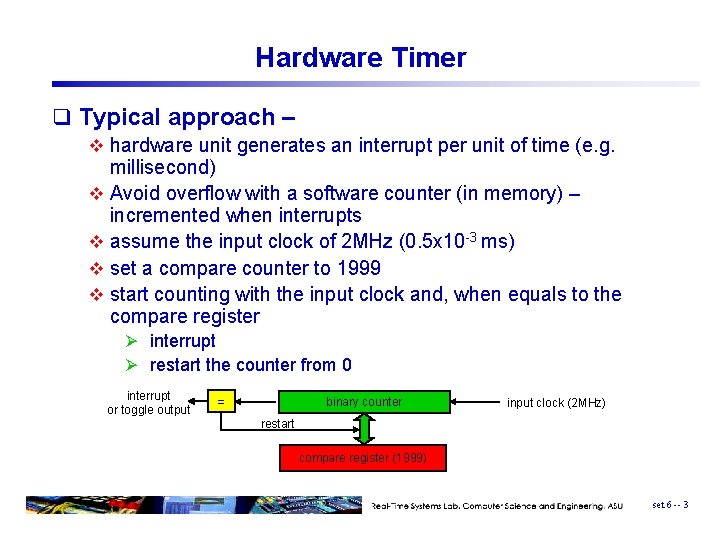

Hardware Timer q Typical approach – v hardware unit generates an interrupt per unit of time (e. g. v v millisecond) Avoid overflow with a software counter (in memory) – incremented when interrupts assume the input clock of 2 MHz (0. 5 x 10 -3 ms) set a compare counter to 1999 start counting with the input clock and, when equals to the compare register Ø interrupt Ø restart the counter from 0 interrupt or toggle output = binary counter input clock (2 MHz) restart compare register (1999) set 6 -- 3

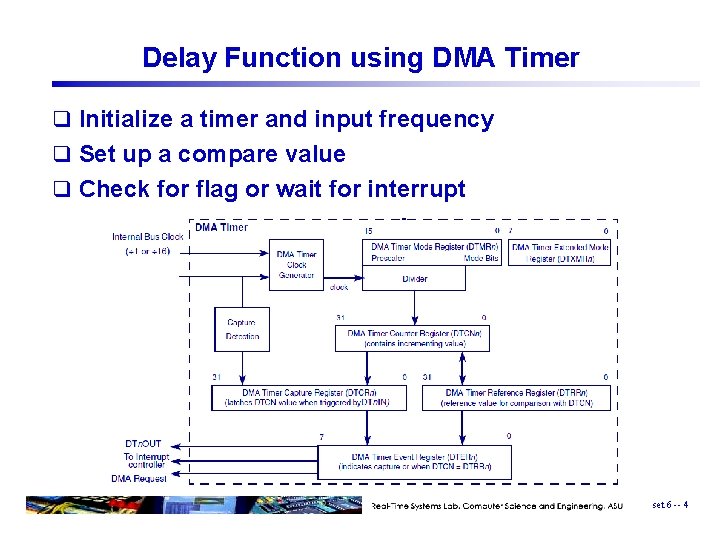

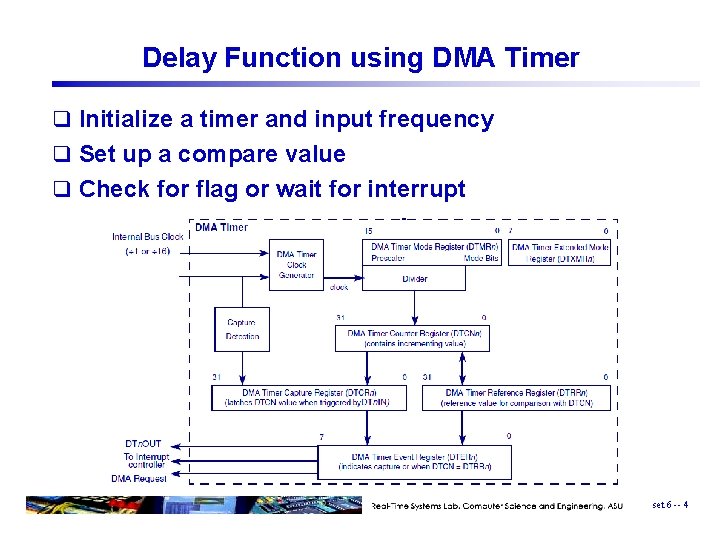

Delay Function using DMA Timer q Initialize a timer and input frequency q Set up a compare value q Check for flag or wait for interrupt set 6 -- 4

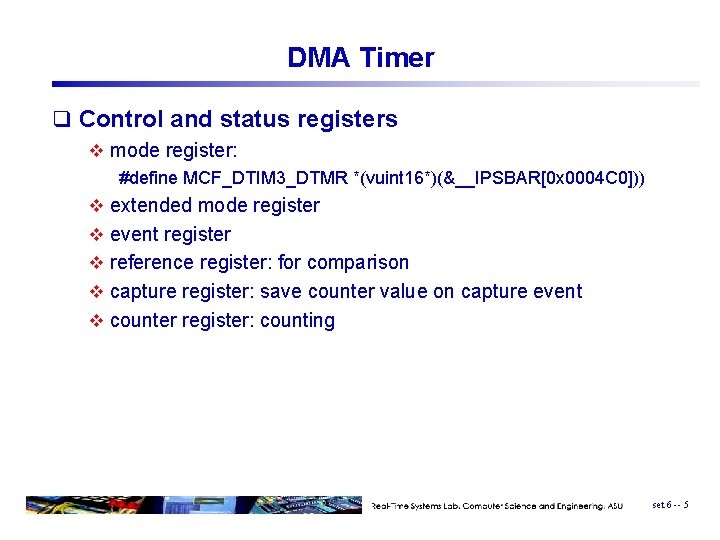

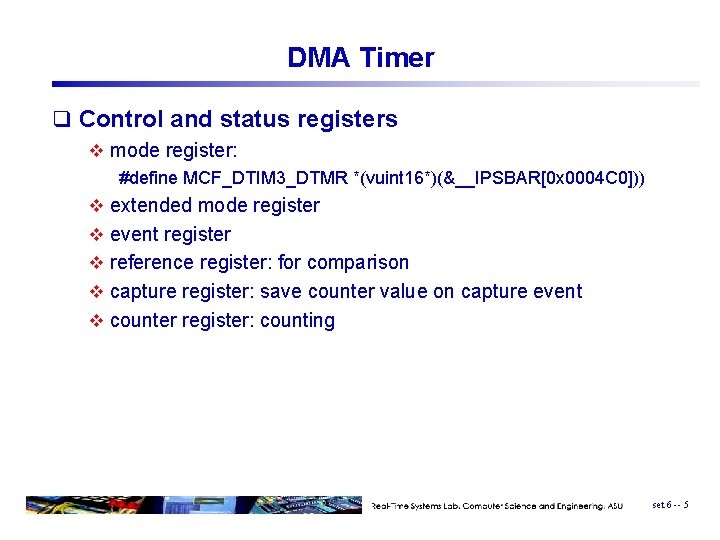

DMA Timer q Control and status registers v mode register: #define MCF_DTIM 3_DTMR *(vuint 16*)(&__IPSBAR[0 x 0004 C 0])) v extended mode register v event register v reference register: for comparison v capture register: save counter value on capture event v counter register: counting set 6 -- 5

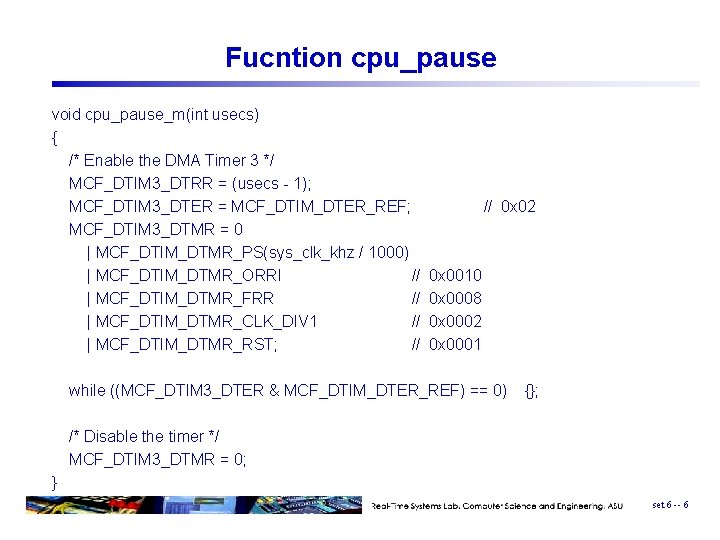

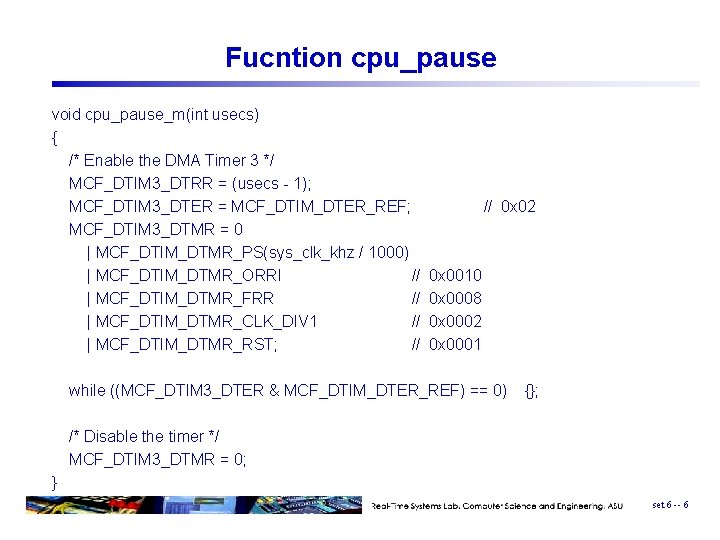

Fucntion cpu_pause void cpu_pause_m(int usecs) { /* Enable the DMA Timer 3 */ MCF_DTIM 3_DTRR = (usecs - 1); MCF_DTIM 3_DTER = MCF_DTIM_DTER_REF; MCF_DTIM 3_DTMR = 0 | MCF_DTIM_DTMR_PS(sys_clk_khz / 1000) | MCF_DTIM_DTMR_ORRI // | MCF_DTIM_DTMR_FRR // | MCF_DTIM_DTMR_CLK_DIV 1 // | MCF_DTIM_DTMR_RST; // // 0 x 02 0 x 0010 0 x 0008 0 x 0002 0 x 0001 while ((MCF_DTIM 3_DTER & MCF_DTIM_DTER_REF) == 0) {}; /* Disable the timer */ MCF_DTIM 3_DTMR = 0; } set 6 -- 6

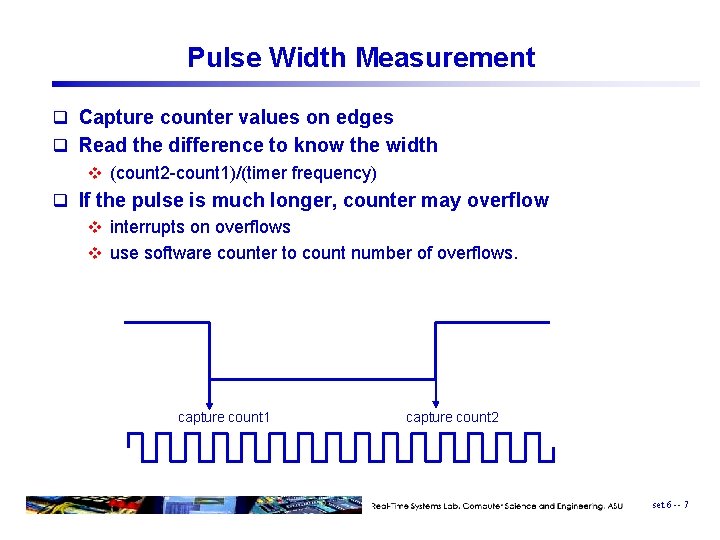

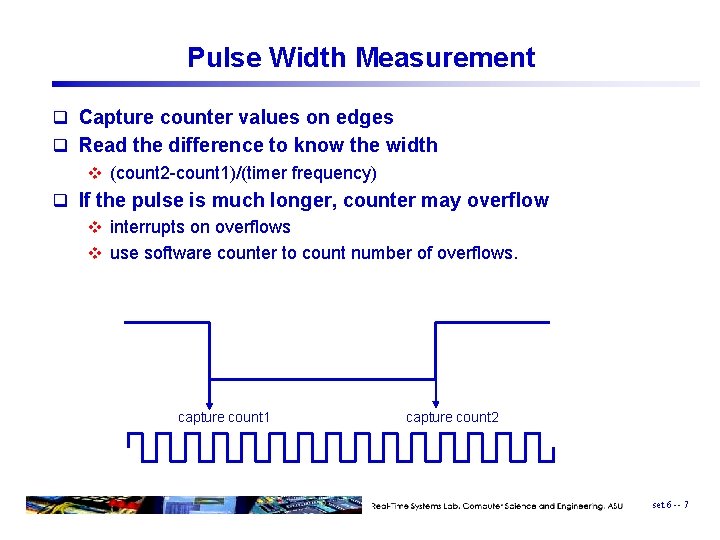

Pulse Width Measurement q Capture counter values on edges q Read the difference to know the width v (count 2 -count 1)/(timer frequency) q If the pulse is much longer, counter may overflow v interrupts on overflows v use software counter to count number of overflows. capture count 1 capture count 2 set 6 -- 7

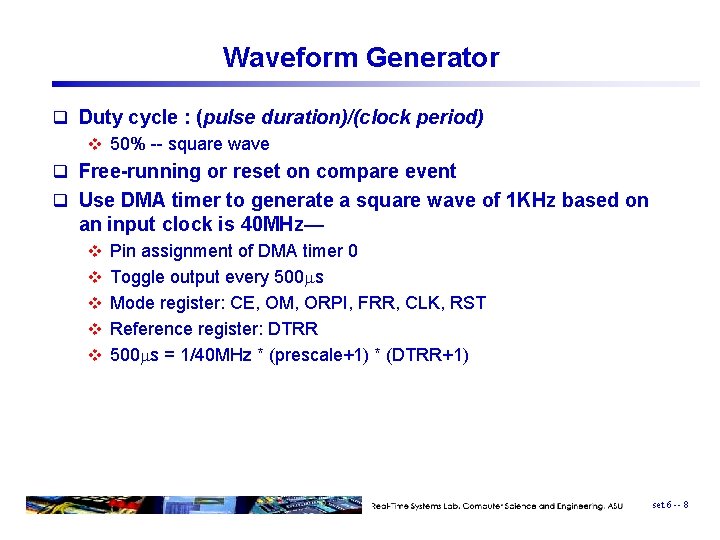

Waveform Generator q Duty cycle : (pulse duration)/(clock period) v 50% -- square wave q Free-running or reset on compare event q Use DMA timer to generate a square wave of 1 KHz based on an input clock is 40 MHz— v Pin assignment of DMA timer 0 v Toggle output every 500 ms v Mode register: CE, OM, ORPI, FRR, CLK, RST v Reference register: DTRR v 500 ms = 1/40 MHz * (prescale+1) * (DTRR+1) set 6 -- 8

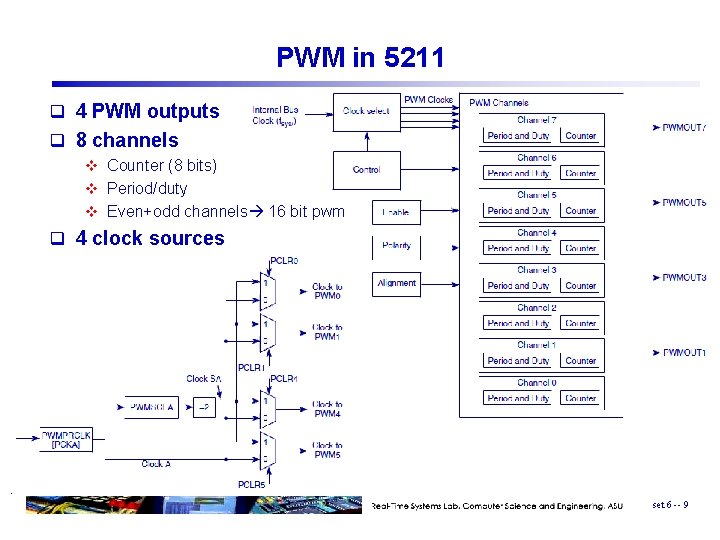

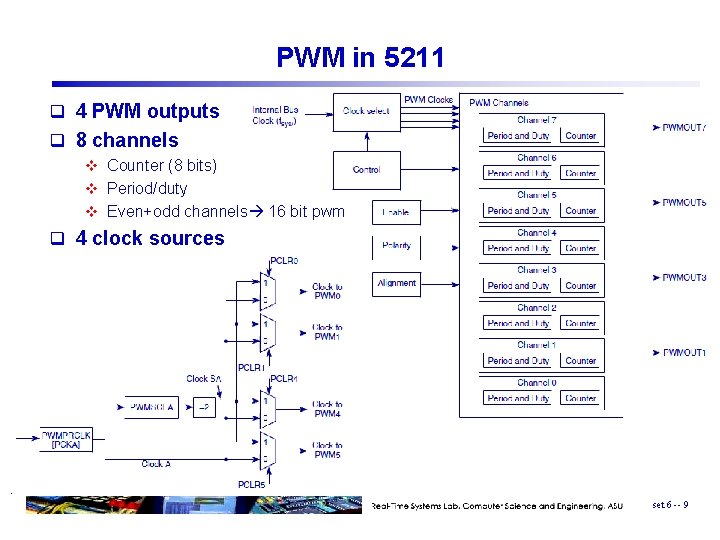

PWM in 5211 q 4 PWM outputs q 8 channels v Counter (8 bits) v Period/duty v Even+odd channels 16 bit pwm q 4 clock sources v A, SA, B, SB set 6 -- 9

PWM in 5211 q Initialization MCF_GPIO_PTAPAR = 0 | MCF_GPIO_PTAPAR 0(3); MCF_PWMPOL = 0 | MCF_PWMPOL_PPOL 1; MCF_PWMCLK = 0|MCF_PWMCLK_PCLK 1; MCF_PWMPRCLK = PRE_SCALE; MCF_PWMSCLA = SCALE; MCF_PWMPER 1 = 255; q Set duty cycle MCF_PWMDTY(channel) = duty_cycle; q Enable pwm MCF_PWME = 0|MCF_PWME_PWME 1 set 6 -- 10