Threshold Voltage Assignment to Supply Voltage Islands in

- Slides: 12

Threshold Voltage Assignment to Supply Voltage Islands in Core-based System-on-a-Chip Designs Project Proposal: Gall Gotfried Steven Beigelmacher 02/09/05

Overview n n Introduction Related Work n n Design Space n n What has already been done What we plan to do Milestones n Deadlines we intend to keep

Introduction n Trends in Design n As process technology improves, more devices will be integrated onto a chip, designs will grow more complex The scope of future designs will increasingly make So. C attractive Importance of Low Power n n Despite what designers previously thought, the power problem has not been solved Need proven techniques that will continue to be effective with future technology nodes n Vdd and Vth assignment

Introduction n n Need low power techniques that work in an So. C framework An So. C design: n n n Hard and soft IP blocks that have been independently characterized The number of blocks may range from a handful up to one hundred There may already be an initial placement of blocks within a defined die size We probably don’t have the freedom to tweak parameters within a core Low power techniques must exist at the intracore level

Introduction n Voltage islands are regions where nearby IP blocks may use a supply voltage different from the full-chip supply We propose taking voltage islands in a corebased So. C design, and adding Vth assignments and latency measures It looks a lot like a placement problem (simulated annealing, quadratic placement, etc)

Related Work n Reduction of power in a system-on-chip n n n Set number of cores Set die size Tool used to move around cores based on common supply voltage n n These common core sections are referred to as voltage islands Cores have several operating supply voltages n Algorithm finds optimal placement of cores

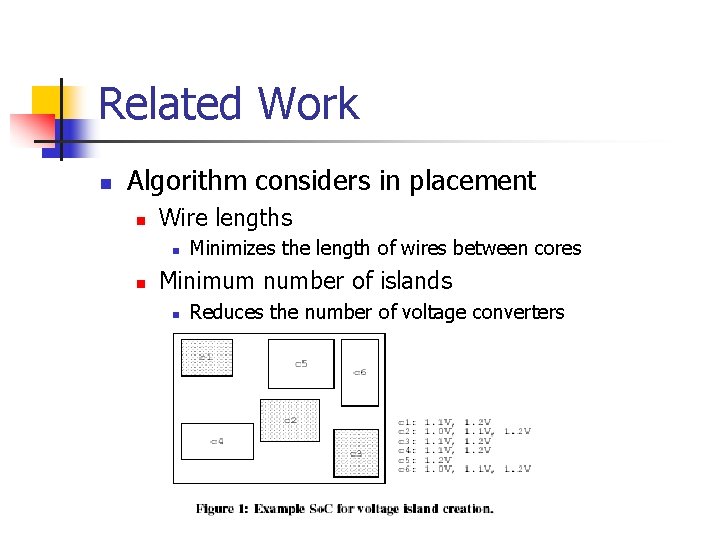

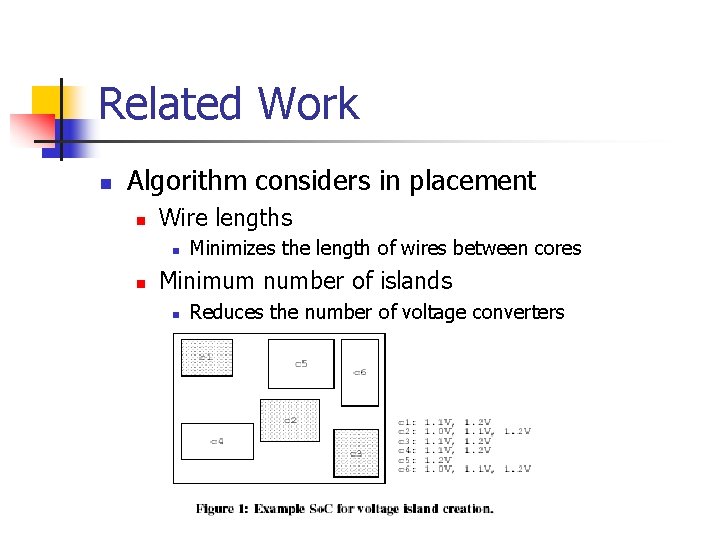

Related Work n Algorithm considers in placement n Wire lengths n n Minimizes the length of wires between cores Minimum number of islands n Reduces the number of voltage converters

More Related Work n Fine grained supply and threshold voltage selection n Gate level partitioning instead of core based Balance between Vdd and Vth is kept to maintain maximum performance Frequency island partitioning n Cores are partitioned based on minimum operating frequency n n Reduces clock skew Communication queues are required for inter-core operations

Design Space n Code exists to take an initial placement and create a placement maximizing the use of voltage islands (Vdd only) n n First step is implement algorithm from previous voltage island paper and attempt to match results n n n But we can’t get access to it Still unsure about implementation approach: Simulated annealing, integer linear programming, topological heuristic, etc Also need to generate comparable benchmarks Then our work really begins

Design Space n n n Need to extend baseline implementation to handle Vth assignment Examining multi-pass solutions (first assign Vdds, then Vth, and so on – or start with Vth) Concern about convergence using a single solution pass via simulated annealing Need to take the latencies of IP blocks into account If time permits, we hope to evaluate a few alternative solutions for comparison

Milestones n Previous work exploration n Extend Algorithm n n Begin implementing algorithm for Vdd island partitioning Deadline 02/23/2005 Test benchmarks on Vdd algorithm to attain similar results as paper suggests Begin extending algorithm to include optimum Vth assignment Deadline 03/21/2005 Achieve Results n n Test algorithm performance on benchmarks used in Vdd only algorithm Deadline 04/11/2005

You Got Questions We Got Answers