THREEDIMENSIONAL INTEGRATED CIRCUITS As Integrated circuits become more

THREE-DIMENSIONAL INTEGRATED CIRCUITS As Integrated circuits become more and more miniaturized, the only direction to go may be … up! Raymond Do Rory Nordeen Ryan Tomita

OVERVIEW Background • Why 3 -D? • Traditional Integrated Circuit methods, Emergence of 3 -D Manufacturing • Major Methods Benefits • What’s so great about 3 -Dimensions? Drawbacks and Challenges • Why don’t we see these everywhere?

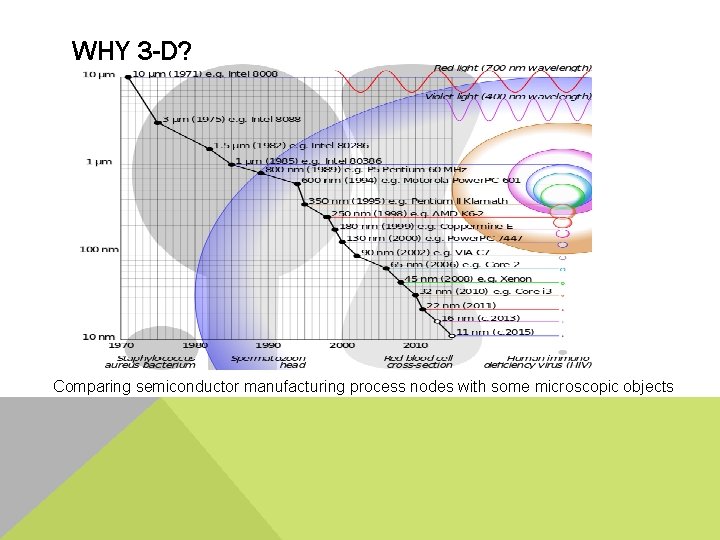

WHY 3 -D? Comparing semiconductor manufacturing process nodes with some microscopic objects

TRADITIONAL METHODS • Highly Pure silicon Wafer substrate • Many individual circuits are laid up on a Silicon wafer substrate • Transistors are formed directly in the substrate, interconnected with wires, and overlaid with dielectric. • Wafer is diced to separate the individual ICs (Dies)

METHODS FOR 3 -D Four Major methods used • Monolithic • Simplest, most limited • Wafer-on-Wafer • More complicated integration using multiple wafers • Die-on-Wafer • Individual dice are stacked on a single wafer • Die-on-Die • Similar to Die-on-Wafer: paired dice are stacked

MONOLITHIC • Method researched at Stanford University • Components and connections are made in layers on a single wafer • Simplicity: no alignment or inter-layer connection issues • Limited complexity! Transistor creation processes damage any existing wiring

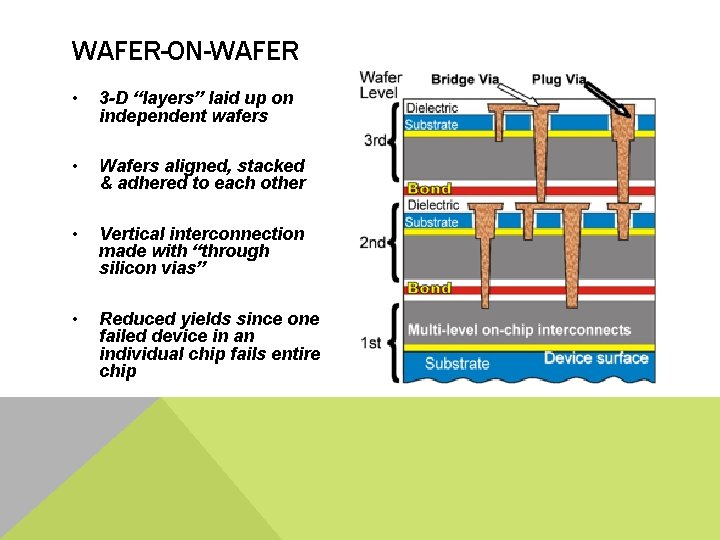

WAFER-ON-WAFER • 3 -D “layers” laid up on independent wafers • Wafers aligned, stacked & adhered to each other • Vertical interconnection made with “through silicon vias” • Reduced yields since one failed device in an individual chip fails entire chip

DIE-ON-WAFER & DIE-ON-DIE Die-on-Wafer Die-on-Die • Same as Wafer-on-Wafer, only one Wafer is diced prior to stacking • Individual Dice are stacked and bonded • Additional dice can be added to the stack • Even more Improved yields since all dice can be tested • Improved yields since individual dies can be tested

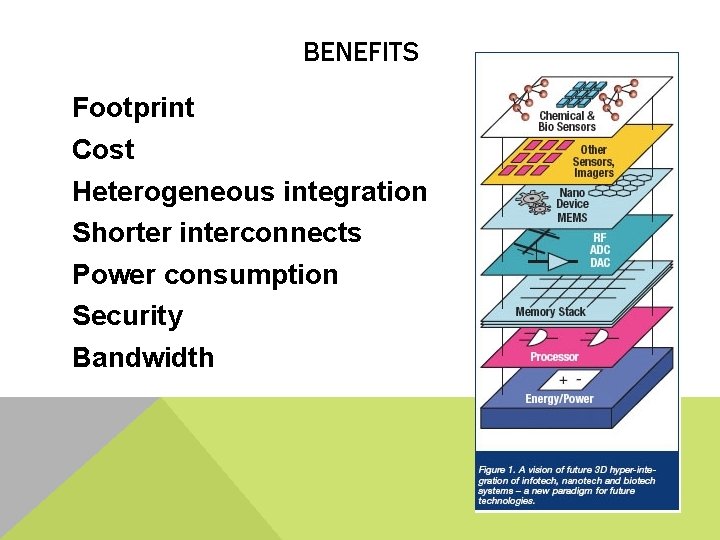

BENEFITS Footprint Cost Heterogeneous integration Shorter interconnects Power consumption Security Bandwidth

Footprint • Stack components in layers on top of each other Cost • Each layer can be designed, tested, and manufactured independently Bandwidth • Interconnects between layers can be wider buses than 2 D interconnects

HETEROGENEOUS INTEGRATION Heterogeneous layers • Layers can have specific functions Package size • Bottom layer keeps original thickness • Layers above bottom can be thinned • Not much thicker than a single wafer

SECURITY Sensitive circuits may be divided among layers Delayering • Circuitry can be hidden between layers • Delayering would destroy circuitry Voltage Imaging • Substrates and bonding material would blur and attenuate image Manufacturing security • Components can be spread across different layers • Layers can be manufactured at different plants

POWER CONSUMPTION Important with devices becoming mobile and distributed Shorter interconnects Potentially keep more signals on-chip • Don’t have to drive I/O

CHALLENGES

YIELD • Manufacturers need to know how 3 D IC will impact yield percentages. • Extra manufacturing step adds risks for defects. • Standard factors that affect yield include: • Die area • Circuit Density • Maturity of Process • Specific factors that affect 3 D yield include: • Extra Processing • Contamination • Alignment • Edge Effects • Design

HEAT • Average distance between system components is reduced: Good for performance but bad for dissipating heat. • Electrical proximity correlates with thermal proximity. • Heat building up within the stack must be dissipated, but how? • A team from IBM, École Polytechnique Fédérale de Lausanne (EPFL) and the Swiss Federal Institute of Technology Zurich (ETH) is working on the issue. • Microchannels with cooling systems using nanosurfaces that pipe coolants

DESIGN COMPLEXITY • 3 D integration requires sophisticated design techniques and new CAD tools. • Full utilization of wafer-thinning and throughsilicon-vias (TSV) cannot be modeled with current 2 D software. • No major companies are offering tools. • Progress is cost-driven.

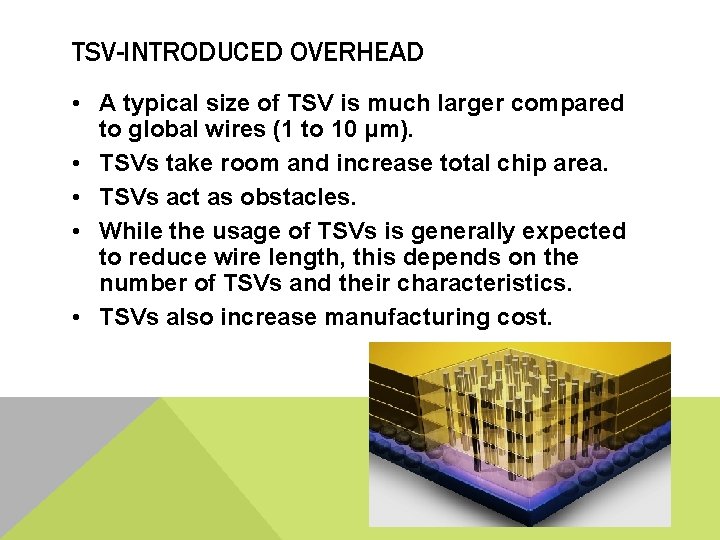

TSV-INTRODUCED OVERHEAD • A typical size of TSV is much larger compared to global wires (1 to 10 μm). • TSVs take room and increase total chip area. • TSVs act as obstacles. • While the usage of TSVs is generally expected to reduce wire length, this depends on the number of TSVs and their characteristics. • TSVs also increase manufacturing cost.

TESTING • Insufficient understanding of 3 D testing issues. • To achieve high overall yield and reduce costs, separate testing of independent dies is essential. • There are serious obstacles to pre-bond testing of wafers in 3 D integration. • Wafer probing is a major limitation for thinned wafers and pre-bond wafers • Any given layer in a stacked 3 D IC does not always include complete functionality. • Methods to test for heat. • Costly test practices.

LACK OF STANDARDS • There are few standards for TSV-based 3 D-IC design, manufacturing, and packaging. • Cost-effective high-volume manufacturing will be difficult to achieve unless manufacturing standards are developed. • SEMI formed a Three-Dimensional Stacked Integrated Circuits Standards Committee. • Bonded Wafer Pair (BWP) Task Force • Inspection and Metrology Task Force • Thin Wafer Carrier Task Force

REFERENCES 1. Robert Patti, "Impact of Wafer-Level 3 D Stacking on the Yield of ICs" http: //www. future-fab. com/documents. asp? d_ID=4415 Future Fab Intl. Volume 23, 2007 2. "EDA's big three unready for 3 D chip packaging" http: //www. eetasia. com/ART_8800485666_480300_NT_fcb 98510. HTM EE Times Asia October 25, 2007 3. D. H. Kim, S. Mukhopadhyay, S. K. Lim, “Through-silicon-via aware interconnect prediction and optimization for 3 D stacked ICs, ” in Proc. of Int. Workshop Sys. -Level Interconn. Pred. , 2009, pp. 85– 92. 4. S. Borkar, “ 3 D integration for energy efficient system design, ” in Proc. Design Autom. Conf. , 2011, pp. 214– 219. 5. H. -H. S. Lee, K. Chakrabarty, “Test challenges for 3 D integrated circuits, ” Des. Test. Comput. , vol. 26, no. 5, pp. 26– 35, Sep 2009 6. 3 -D chip stacks standardized" http: //www. eetimes. com/electronics-news/4077835/3 -D-chip-stacks-standardized EE Times November 7, 2008 7. "SEMI International Standards Program Forms 3 D Stacked IC Standards Committee" http: //www. semi. org/en/press/CTR_042145? id=highlights SEMI press release December 7, 2010 8. Developer, Shed. "3 D Processors, Stacking Core". September 20, 2005. http: //www. devhardware. com/c/a/Computer-Processors/3 D-Processor. Technology/, 9. Developer, Shed. "3 D Processors, Stacking Core". September 20, 2005. http: //www. devhardware. com/c/a/Computer-Processors/3 D-Processor. Technology/1/ 10. Xiangyu Dong and Yuan Xie, "System-level Cost Analysis and Design Exploration for 3 D ICs", Proc. of Asia and South Pacific Design Automation Conference, 2009, http: //www. cse. psu. edu/~yuanxie/3 d. html 11. "3 D IC Technology Delivers The Total Package" http: //electronicdesign. com/article/engineeringessentials/3 d_ic_technology_delivers_the_total_package. aspx Electronic Design July 02, 2010 12. James J-Q Lu, Ken Rose, & Susan Vitkavage “ 3 D Integration: Why, What, Who, When? ” http: //www. future-fab. com/documents. asp? d_ID=4396 Future Fab Intl. Volume 23, 2007 13. William J. Dally, “Future Directions for On-Chip Interconnection Networks” page 17, http: //www. ece. ucdavis. edu/~ocin 06/talks/dally. pdf Computer Systems Laboratory Stanford University, 2006 14. Johnson, R Colin. "3 -D chip stacks standardized". July 10, 2008. http: //www. eetimes. com/electronics-news/4077835/3 -D-chip-stacks-standardized 15. "3 D-ICs and Integrated Circuit Security" http: //www. tezzaron. com/about/papers/3 D-ICs_and_Integrated_Circuit_Security. pdf Tezzaron Semiconductor, 2008 16. Dong Hyuk Woo, Nak Hee Seong, Dean L. Lewis, and Hsien-Hsin S. Lee. "An Optimized 3 D-Stacked Memory Architecture by Exploiting Excessive, High-Density TSV Bandwidth. " In Proceedings of the 16 th International Symposium on High-Performance Computer Architecture, pp. 429 -440, Bangalore, India, January, 2010. 17. "Predicting the Performance of a 3 D Processor-Memory Chip Stack" Jacob, P. , Mc. Donald, J. F. et al. Design & Test of Computers, IEEE Volume 22, Issue 6, Nov. –Dec. 2005 Page(s): 540– 547

- Slides: 21