Ther MOS A Thermal Model for Selfheating in

![Why Ther. MOS? [1] L. T. Clark, et al. , Microelec. Journal 2016 [2] Why Ther. MOS? [1] L. T. Clark, et al. , Microelec. Journal 2016 [2]](https://slidetodoc.com/presentation_image_h/01f9ff2f60dc67f562e44a39e3dca9f0/image-12.jpg)

- Slides: 37

Ther. MOS: A Thermal Model for Self-heating in Advanced MOSFETs Vidya A. Chhabria, Arvind K. Sharma, Meghna G. Makalale and Sachin S. Sapatnekar University of Minnesota November 2019 1

Outline • • • Introduction Self-heating at the device level Ther. MOS: A self-heating temperature analyzer Ther. MOS: Results and use case Conclusion 2

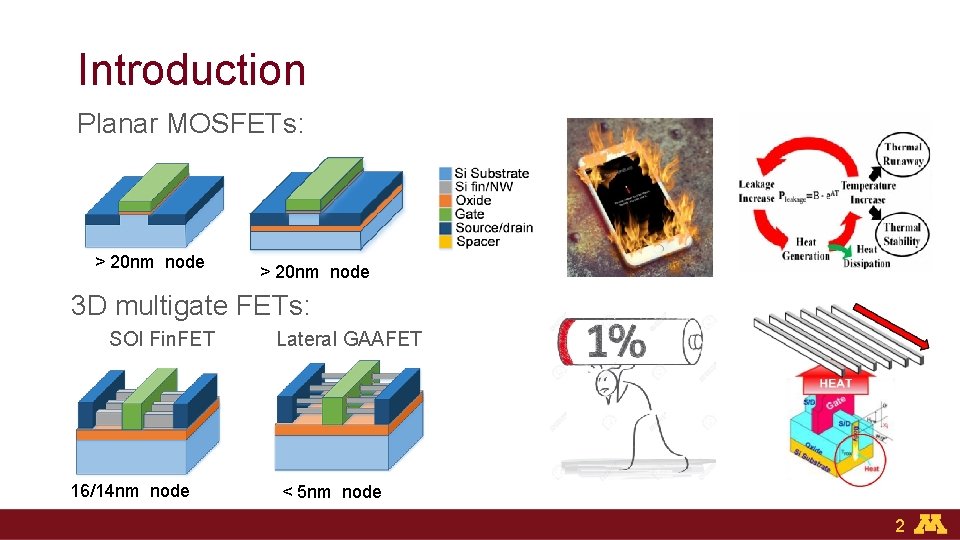

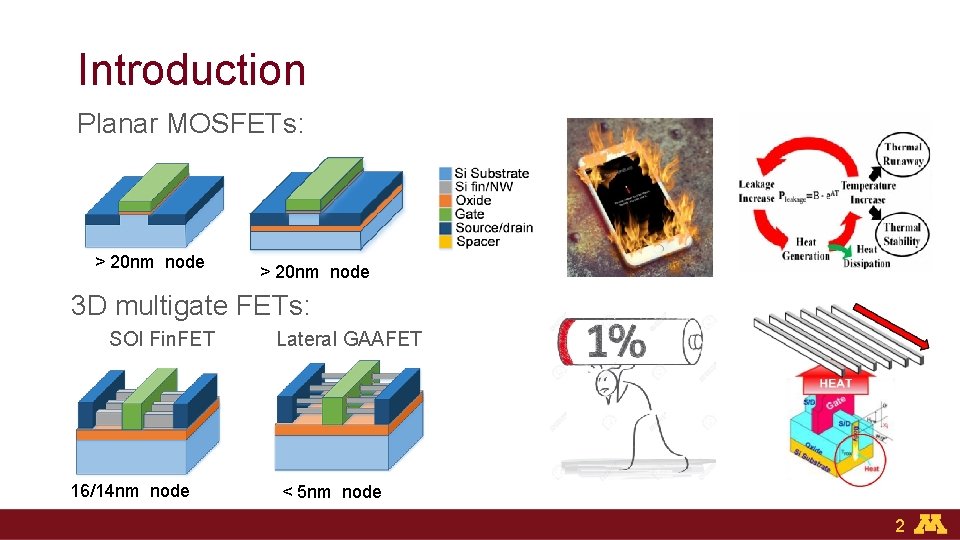

Introduction Planar MOSFETs: > 20 nm node 3 D multigate FETs: SOI Fin. FET 16/14 nm node Lateral GAAFET < 5 nm node 2

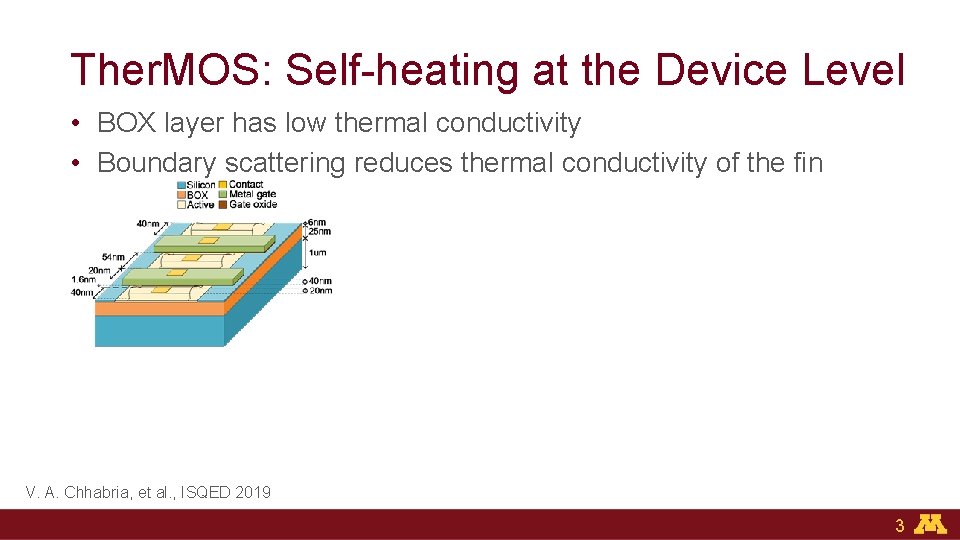

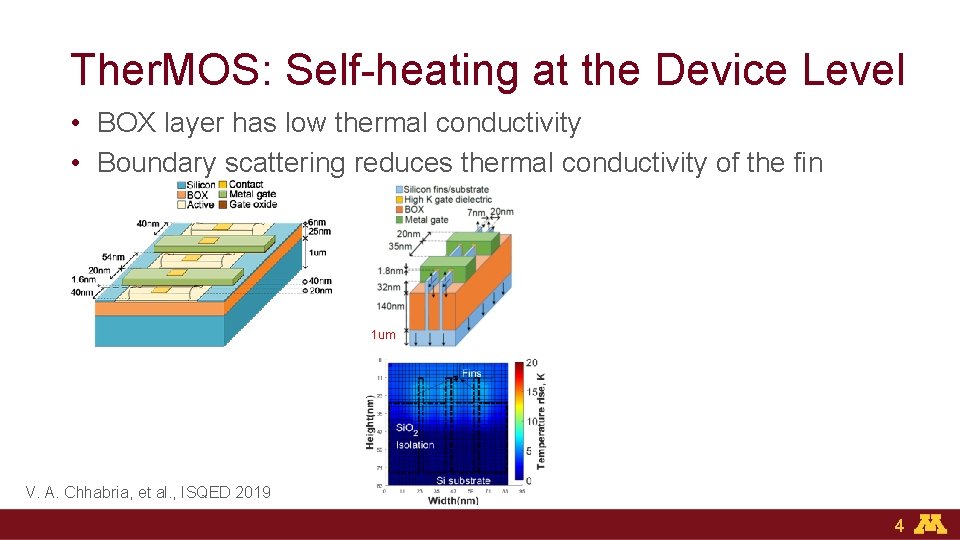

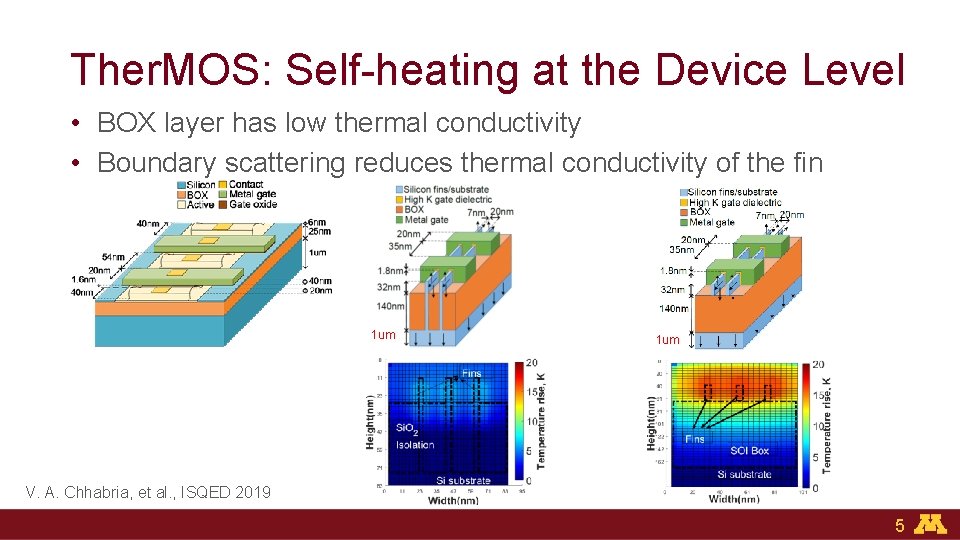

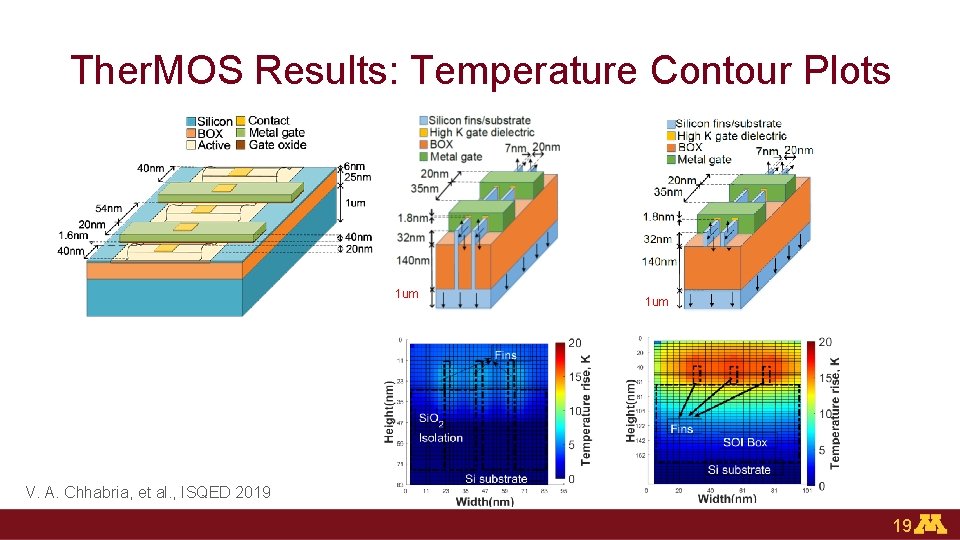

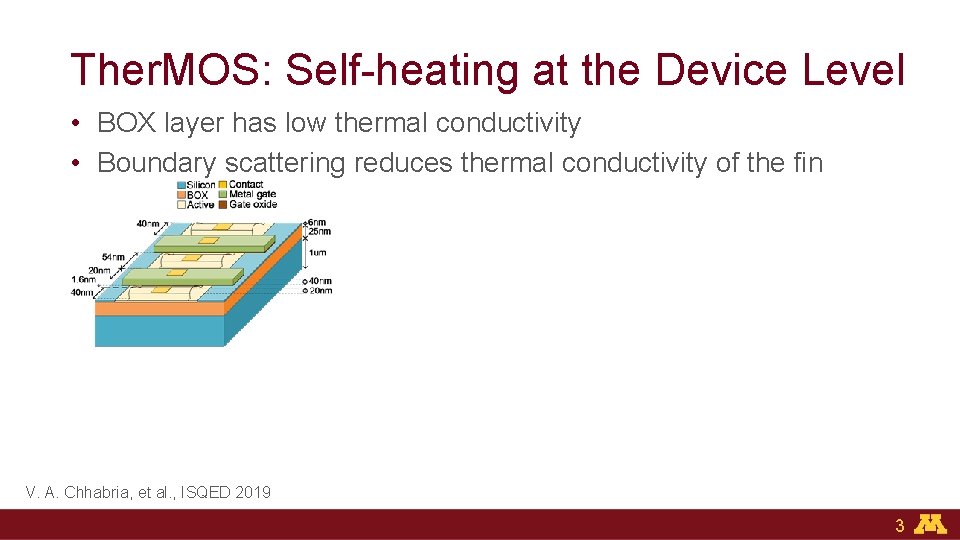

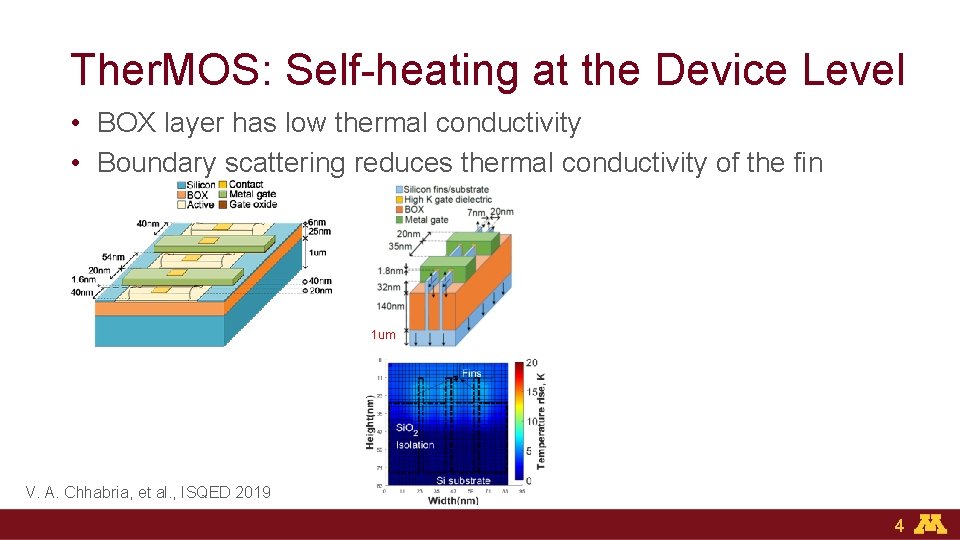

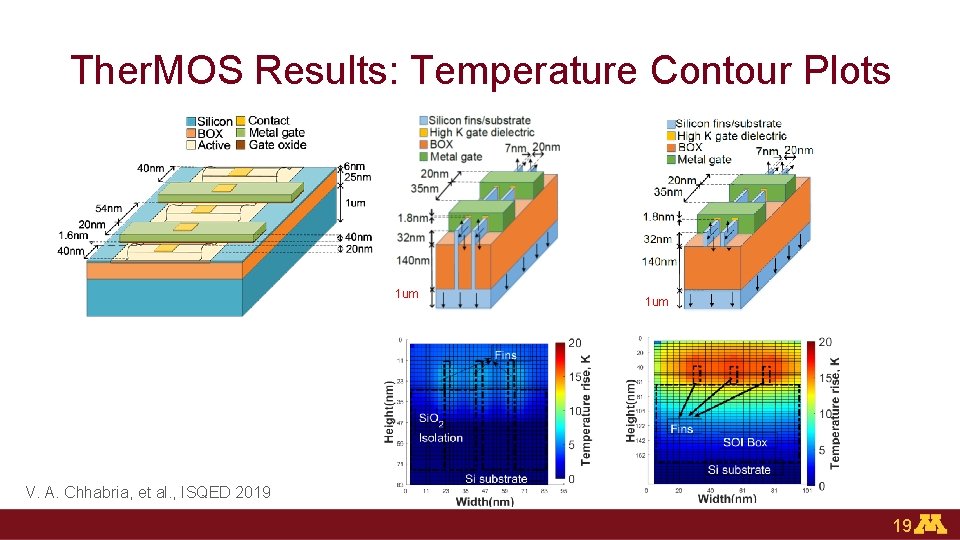

Ther. MOS: Self-heating at the Device Level • BOX layer has low thermal conductivity • Boundary scattering reduces thermal conductivity of the fin 1 um V. A. Chhabria, et al. , ISQED 2019 3

Ther. MOS: Self-heating at the Device Level • BOX layer has low thermal conductivity • Boundary scattering reduces thermal conductivity of the fin 1 um V. A. Chhabria, et al. , ISQED 2019 4

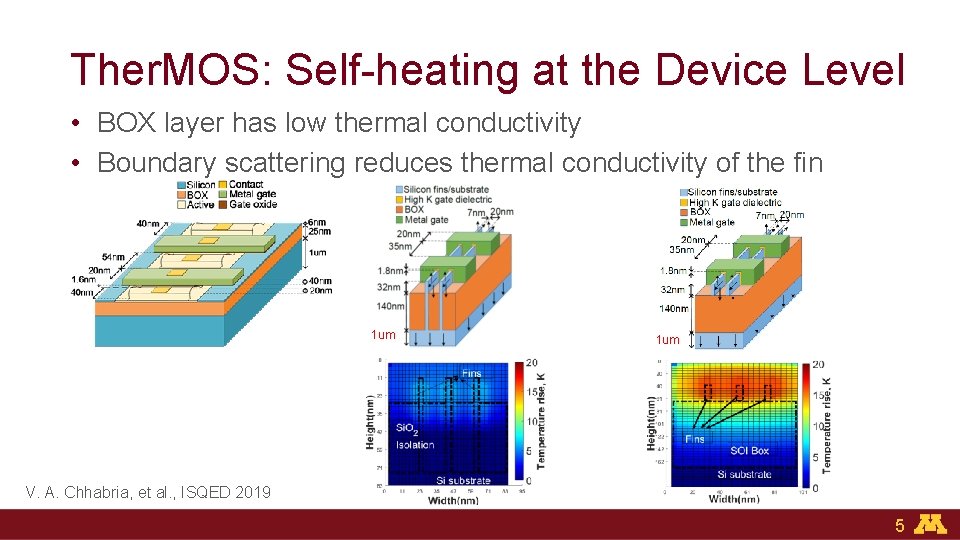

Ther. MOS: Self-heating at the Device Level • BOX layer has low thermal conductivity • Boundary scattering reduces thermal conductivity of the fin 1 um 1 um V. A. Chhabria, et al. , ISQED 2019 5

Outline • • • Introduction Self-heating at the device level Ther. MOS: A self-heating temperature analyzer Ther. MOS: Results and use case Conclusion 6

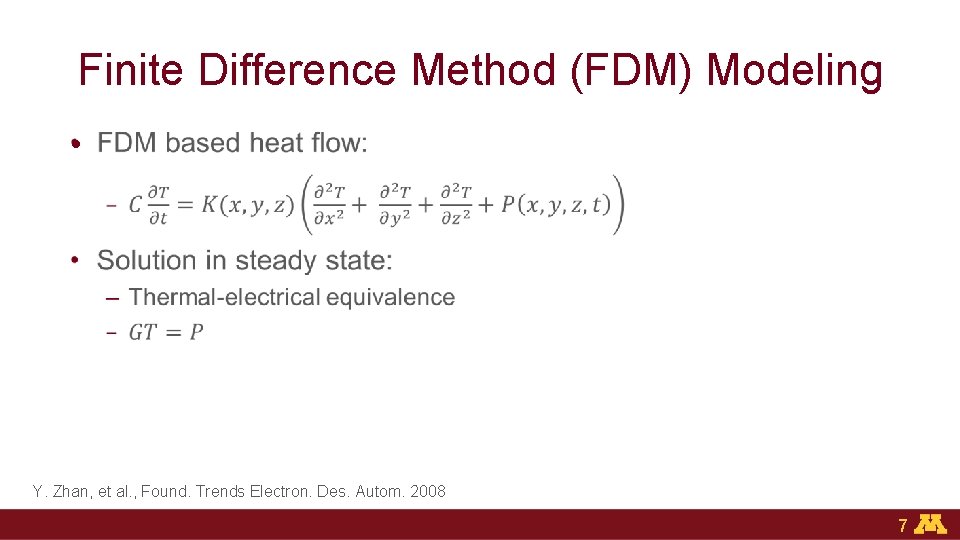

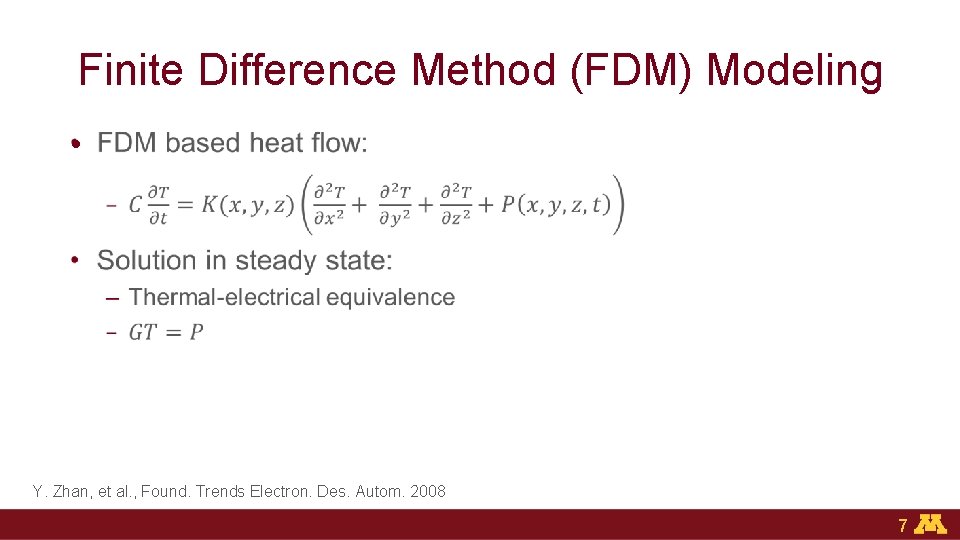

Finite Difference Method (FDM) Modeling • Y. Zhan, et al. , Found. Trends Electron. Des. Autom. 2008 7

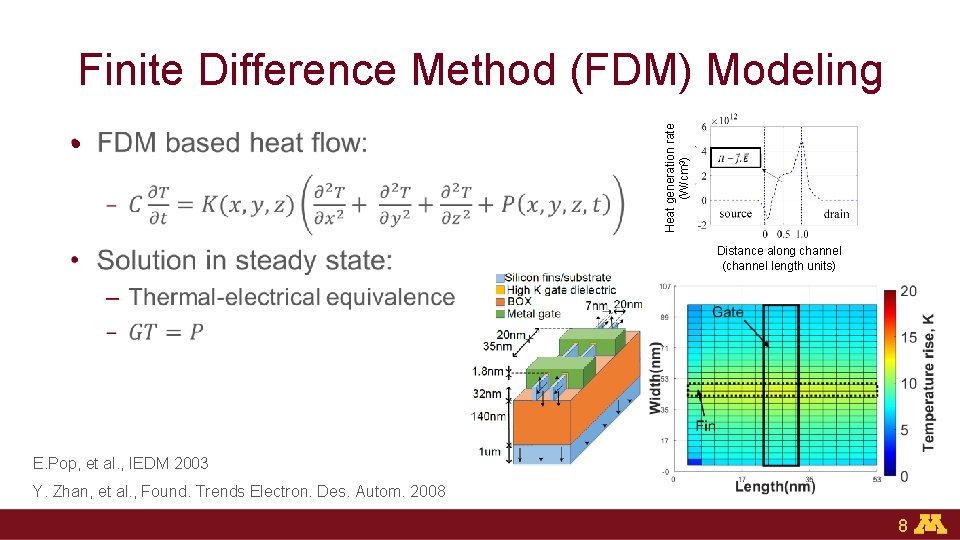

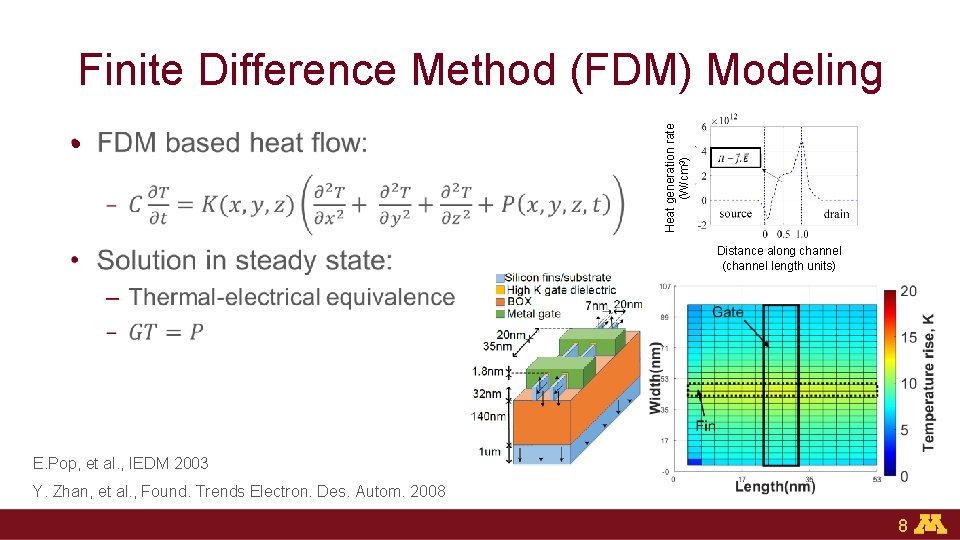

• Heat generation rate (W/cm 3) Finite Difference Method (FDM) Modeling Distance along channel (channel length units) E. Pop, et al. , IEDM 2003 Y. Zhan, et al. , Found. Trends Electron. Des. Autom. 2008 8

WAIT BUT WHY Ther. MOS? ? 9

Why Ther. MOS? • Easy to use • Fast multifin and multigate simulation 10

![Why Ther MOS 1 L T Clark et al Microelec Journal 2016 2 Why Ther. MOS? [1] L. T. Clark, et al. , Microelec. Journal 2016 [2]](https://slidetodoc.com/presentation_image_h/01f9ff2f60dc67f562e44a39e3dca9f0/image-12.jpg)

Why Ther. MOS? [1] L. T. Clark, et al. , Microelec. Journal 2016 [2] V. Vashishtha, et al. , ICCAD Embedded Tutorial, 2017 [3] M. Shrivastava, et al. , IEEE Trans. Elec. Devices, 2012 [4] B. Swahn , et al. , IEEE Trans. VLSI Systems, 2008 11

Outline • • • Introduction Self-heating at the device level Ther. MOS: A self-heating temperature analyzer Ther. MOS: Results and use case Conclusion 12

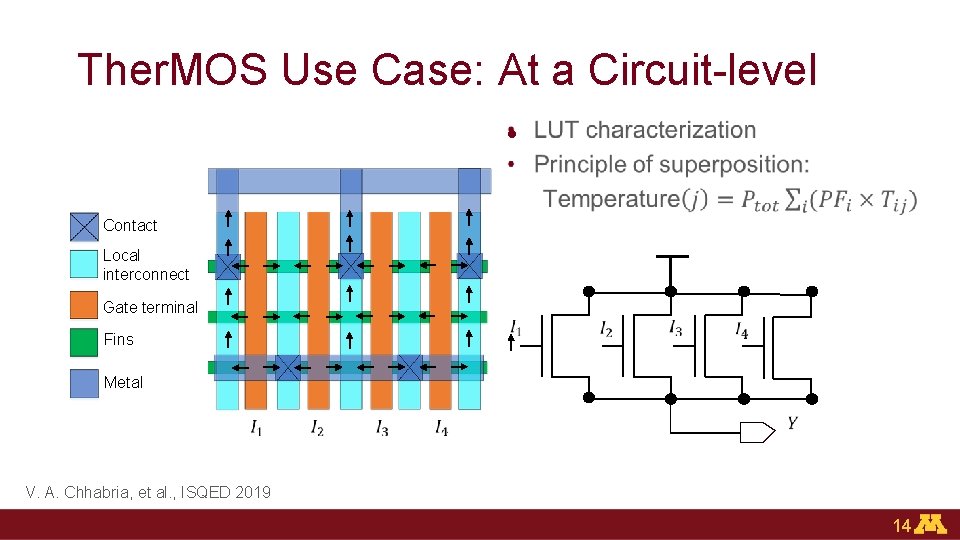

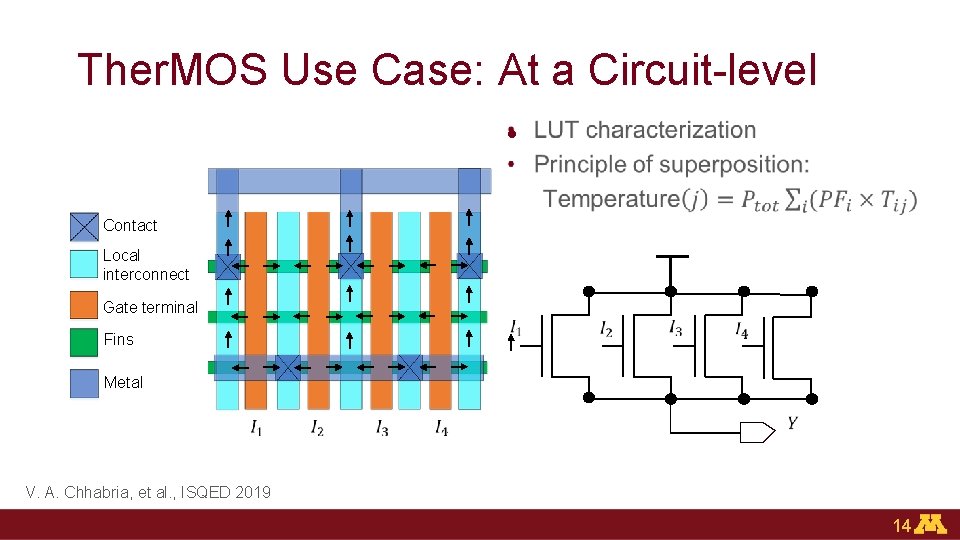

Ther. MOS Use Case: At a Circuit-level • Contact Local interconnect Gate terminal Fins Metal V. A. Chhabria, et al. , ISQED 2019 14

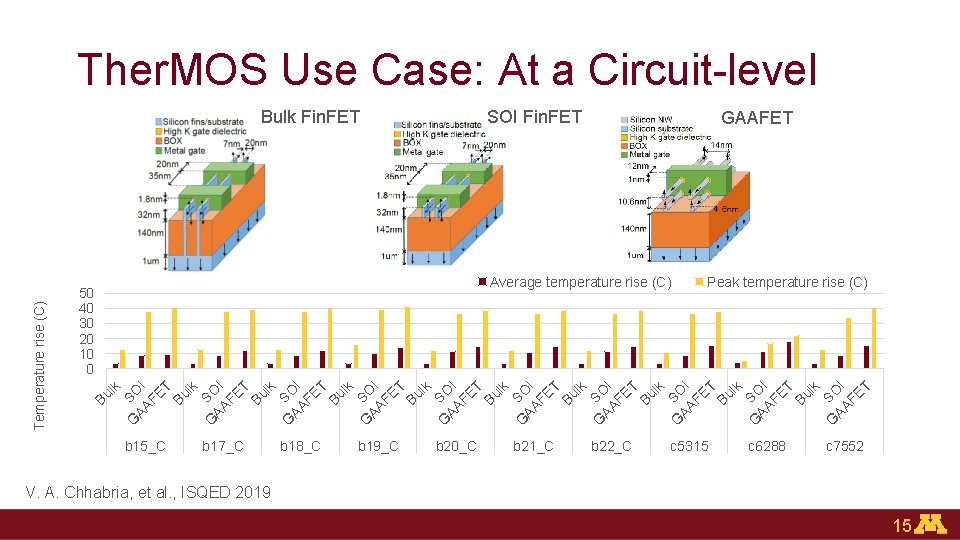

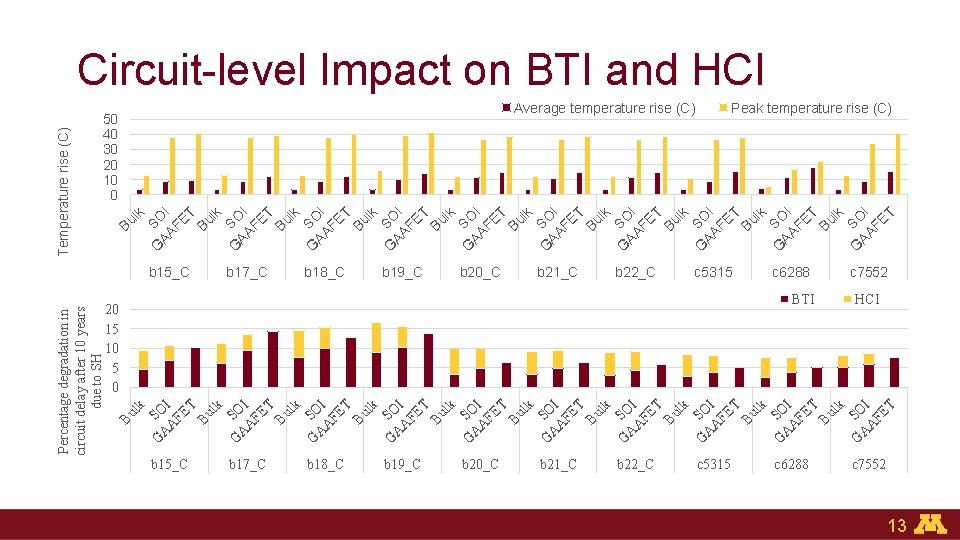

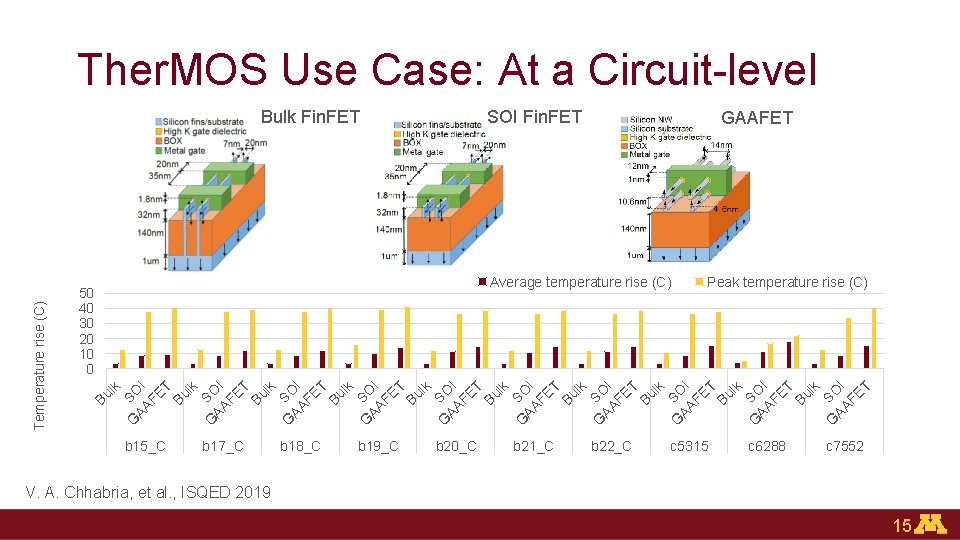

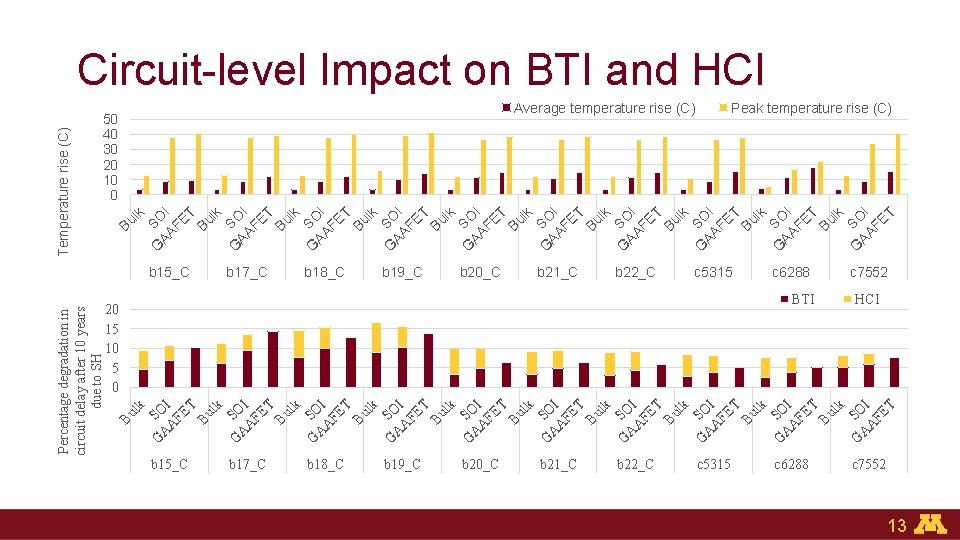

Ther. MOS Use Case: At a Circuit-level SOI Fin. FET GAAFET Average temperature rise (C) Peak temperature rise (C) G lk S AA OI FE T Bu lk G SO AA I FE T Bu lk G SO AA I FE T Bu lk G SO AA I FE T 50 40 30 20 10 0 Bu Temperature rise (C) Bulk Fin. FET b 15_C b 17_C b 18_C b 19_C b 20_C b 21_C b 22_C c 5315 c 6288 c 7552 V. A. Chhabria, et al. , ISQED 2019 15

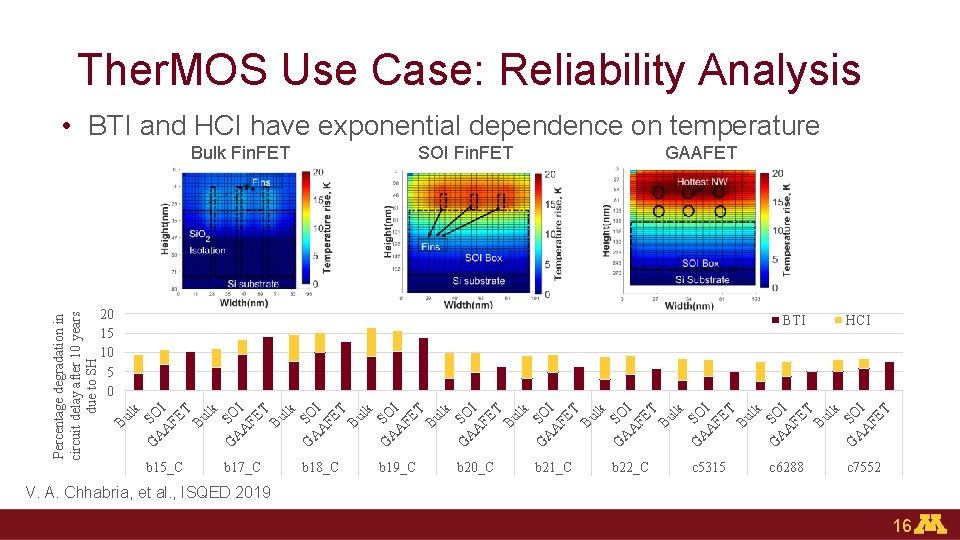

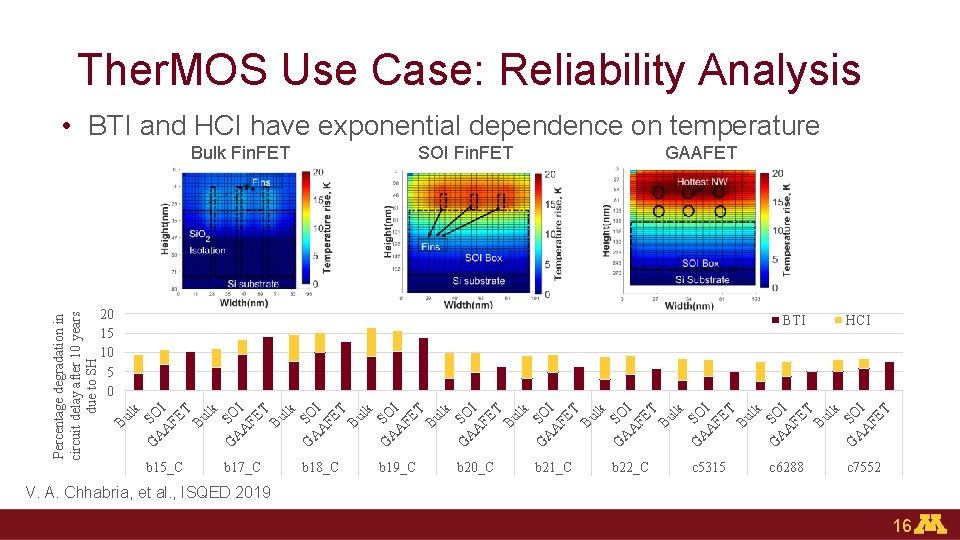

Ther. MOS Use Case: Reliability Analysis • BTI and HCI have exponential dependence on temperature GAAFET SOI Fin. FET 20 15 10 5 0 HCI G A lk SO A I FE T Bu lk G SO A A I FE T Bu lk G SO A A I FE T Bu lk G SO A A I FE T BTI Bu Percentage degradation in circuit delay after 10 years due to SH Bulk Fin. FET b 15_C b 17_C b 18_C b 19_C b 20_C b 21_C b 22_C c 5315 c 6288 c 7552 V. A. Chhabria, et al. , ISQED 2019 16

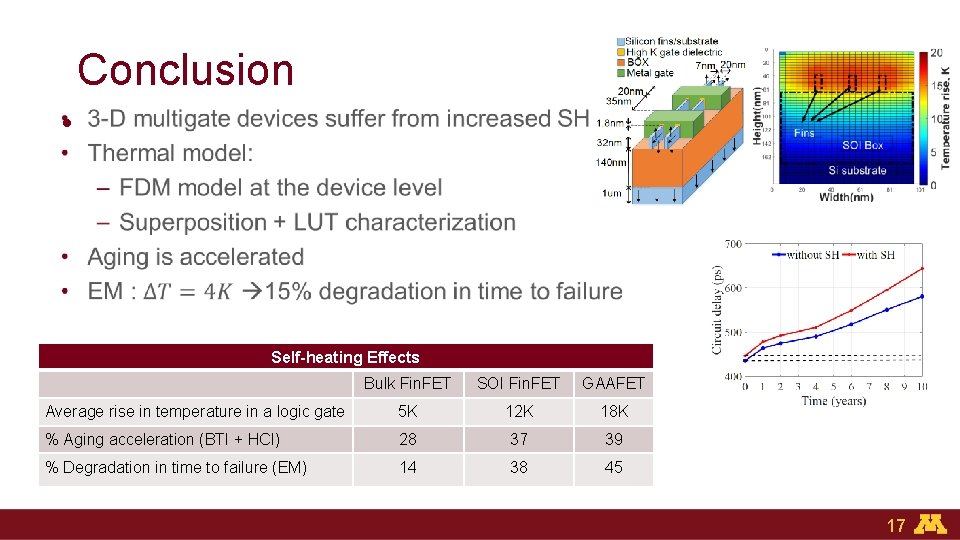

Conclusion • Modern FDSOI and multigate devices suffer from SH • Ther. MOS analyzes the rise in temperature 17

Conclusion • Modern FDSOI and multigate devices suffer from SH • Ther. MOS analyzes the rise in temperature • Give it a whirl: – https: //github. com/Vidya. Chhabria/Ther. MOS – git clone; source install. sh; pytest – python 3 SOI_Fin. FET –device_type NMOS –n_fin 3 –n_gate 1 –power 5 e-6 • Thank you! Questions? 19

BACKUP SLIDES

Ther. MOS Results: Temperature Contour Plots 1 um V. A. Chhabria, et al. , ISQED 2019 19

Why Ther. MOS? • Fast run-times: User-definable resolution and non-uniform meshing 14

Why Ther. MOS? • Fast run-times: User-definable resolution and non-uniform meshing • Device parameters compiled from literature sources for 7 FF and 14 nm FDSOI technologies 15

Why Ther. MOS? • Fast run-times: User-definable resolution and non-uniform meshing • Device parameters compiled from literature sources for 7 FF and 14 nm FDSOI technologies • Multifin and multigate array simulation 16

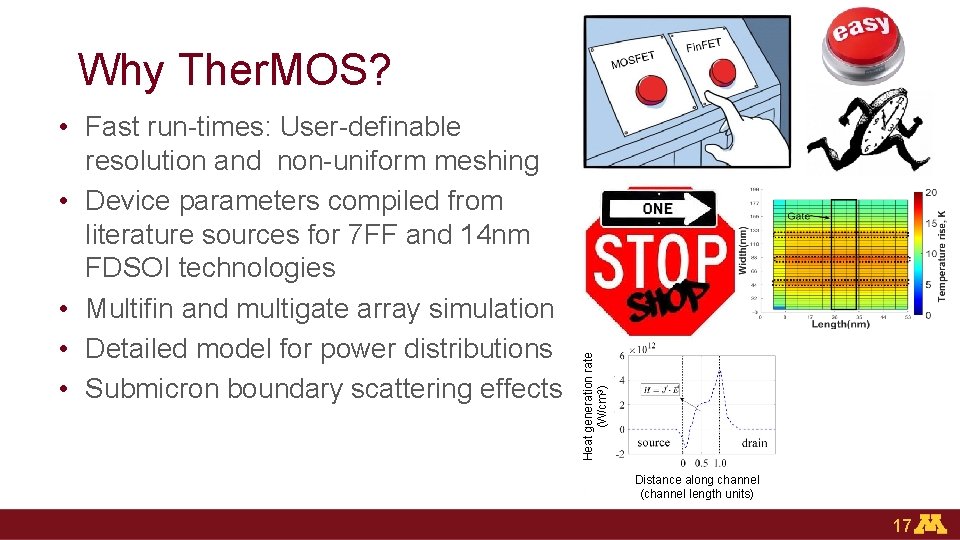

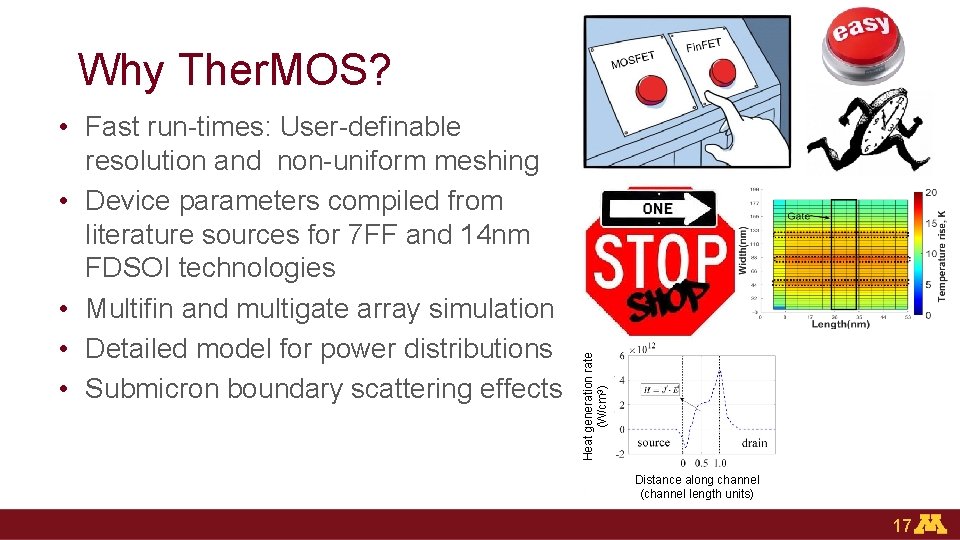

• Fast run-times: User-definable resolution and non-uniform meshing • Device parameters compiled from literature sources for 7 FF and 14 nm FDSOI technologies • Multifin and multigate array simulation • Detailed model for power distributions • Submicron boundary scattering effects Heat generation rate (W/cm 3) Why Ther. MOS? Distance along channel (channel length units) 17

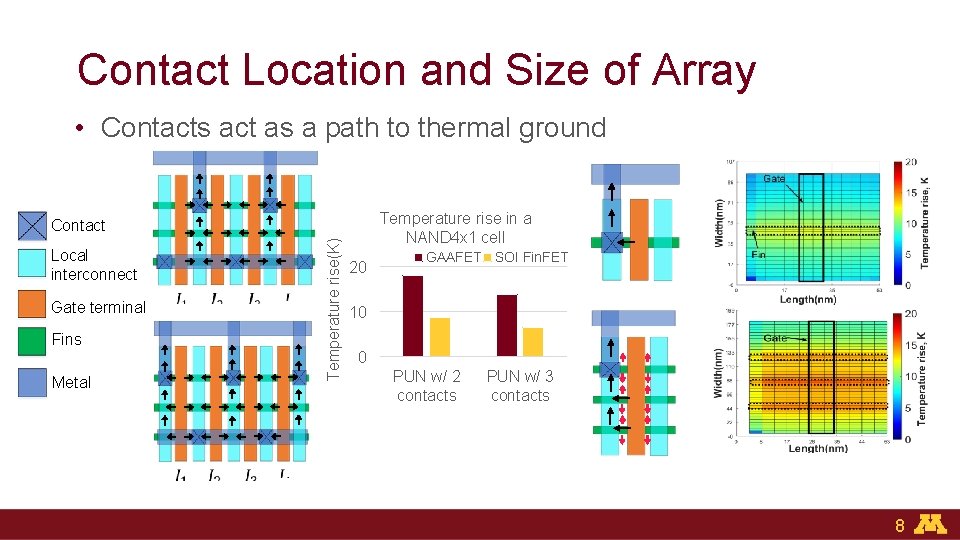

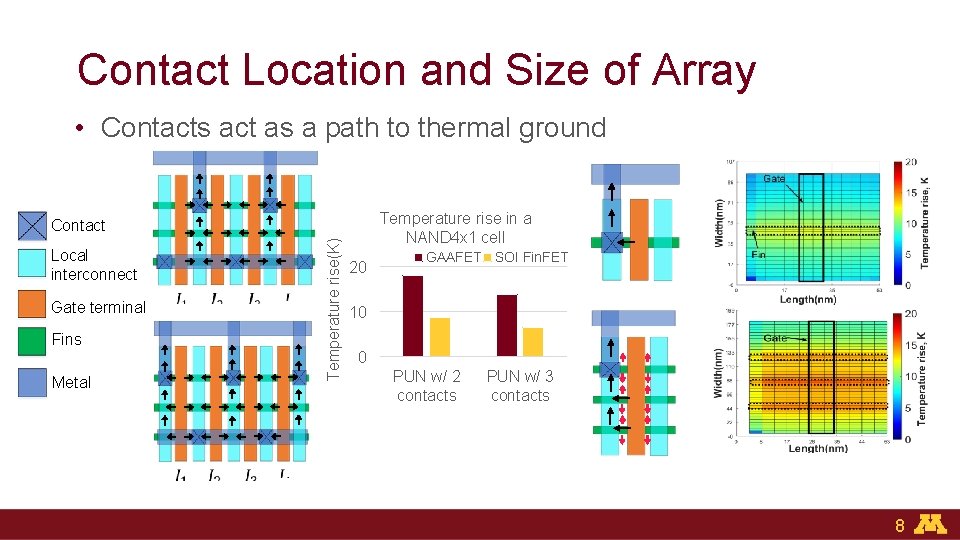

Contact Location and Size of Array • Contacts act as a path to thermal ground Temperature rise in a NAND 4 x 1 cell Local interconnect Gate terminal Fins Metal Temperature rise(K) Contact 20 GAAFET SOI Fin. FET 10 0 PUN w/ 2 contacts PUN w/ 3 contacts 8

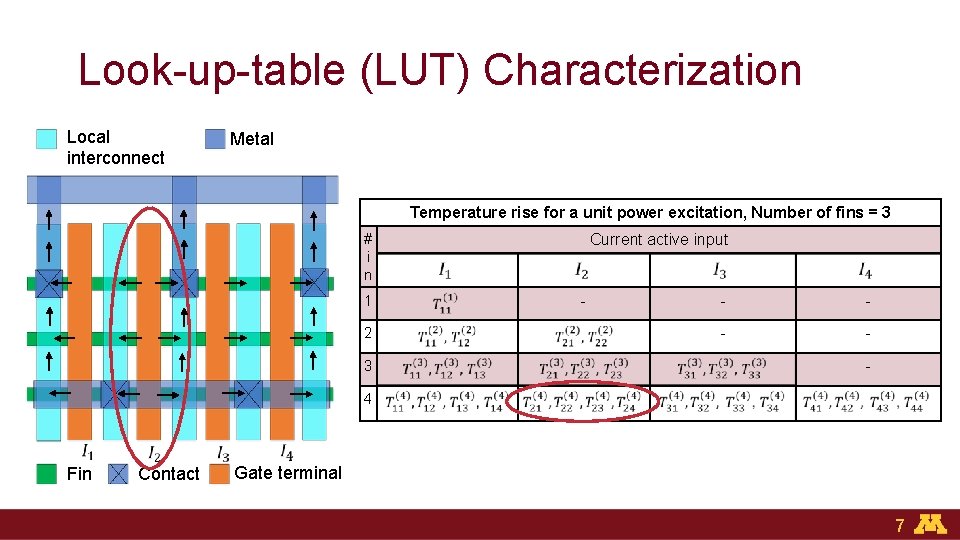

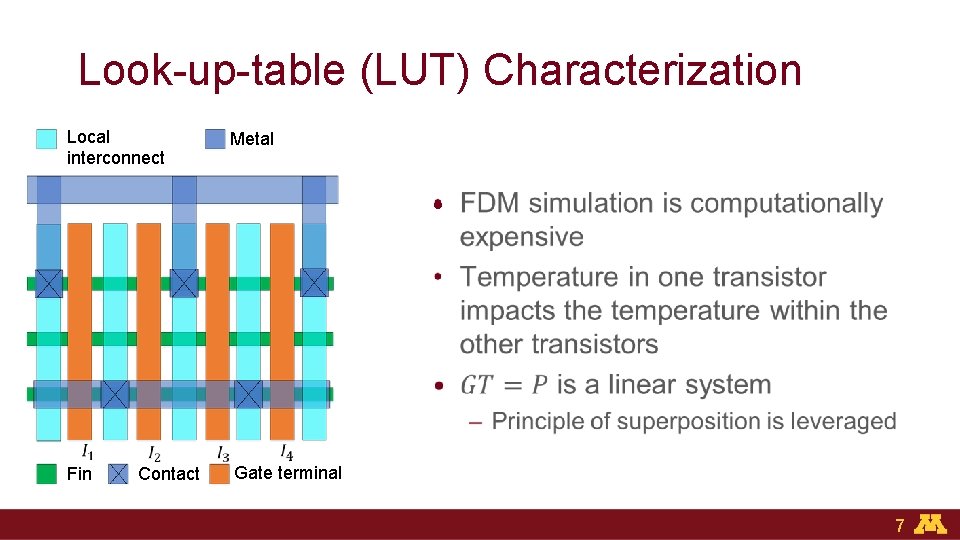

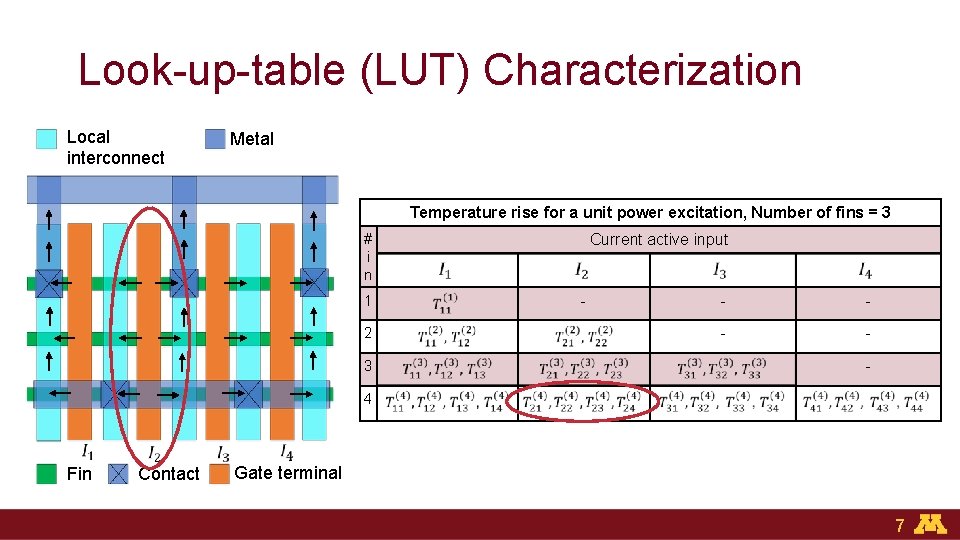

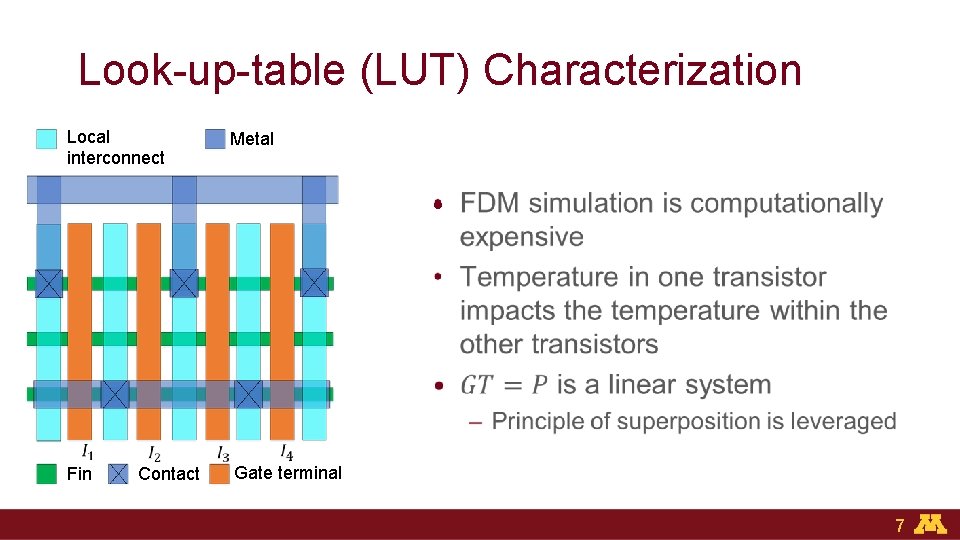

Look-up-table (LUT) Characterization Local interconnect Metal Temperature rise for a unit power excitation, Number of fins = 3 # i n 1 2 3 Current active input - - - 4 Fin Contact Gate terminal 7

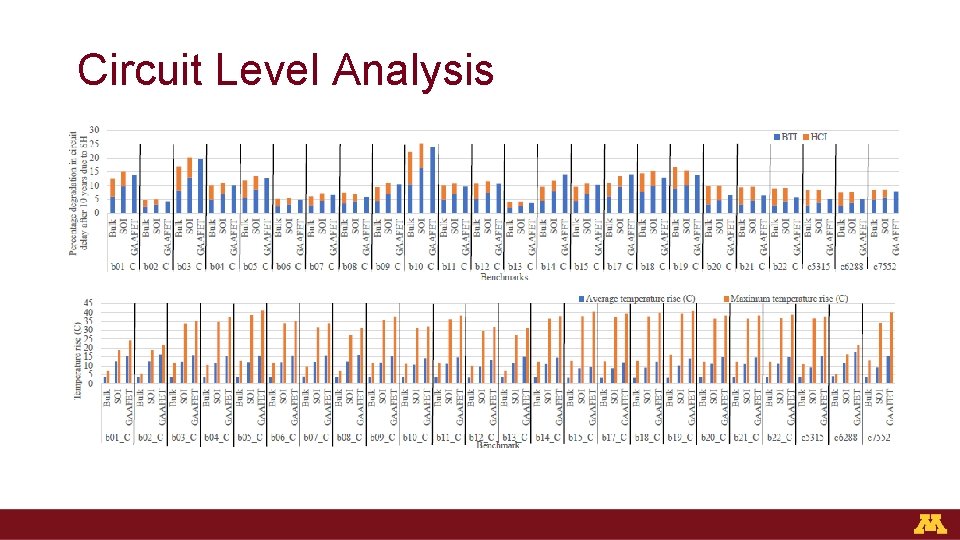

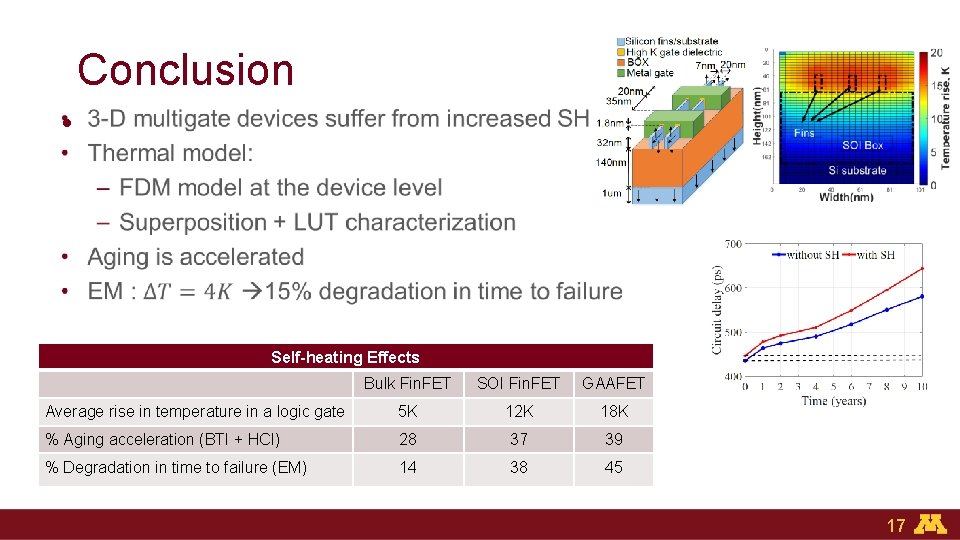

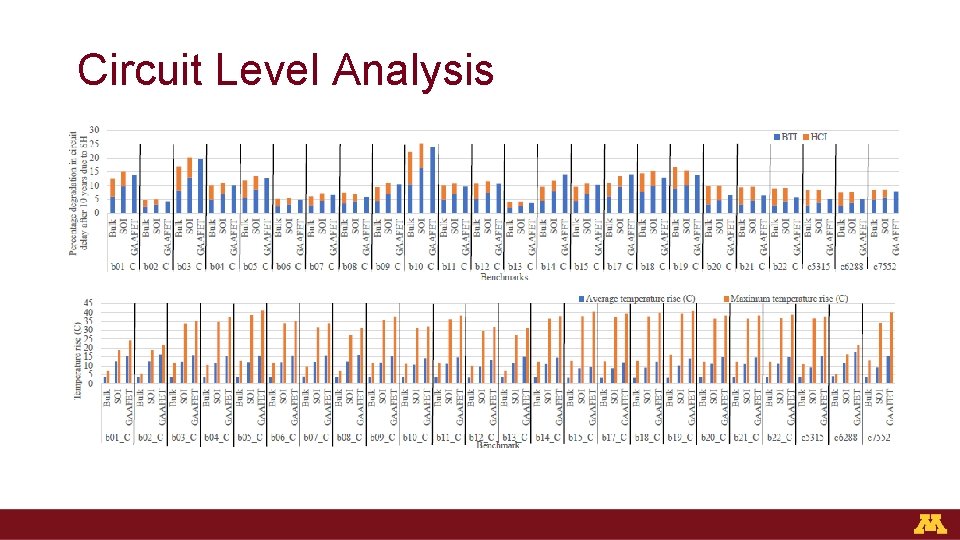

Conclusion • Self-heating Effects Bulk Fin. FET SOI Fin. FET GAAFET Average rise in temperature in a logic gate 5 K 12 K 18 K % Aging acceleration (BTI + HCI) 28 37 39 % Degradation in time to failure (EM) 14 38 45 17

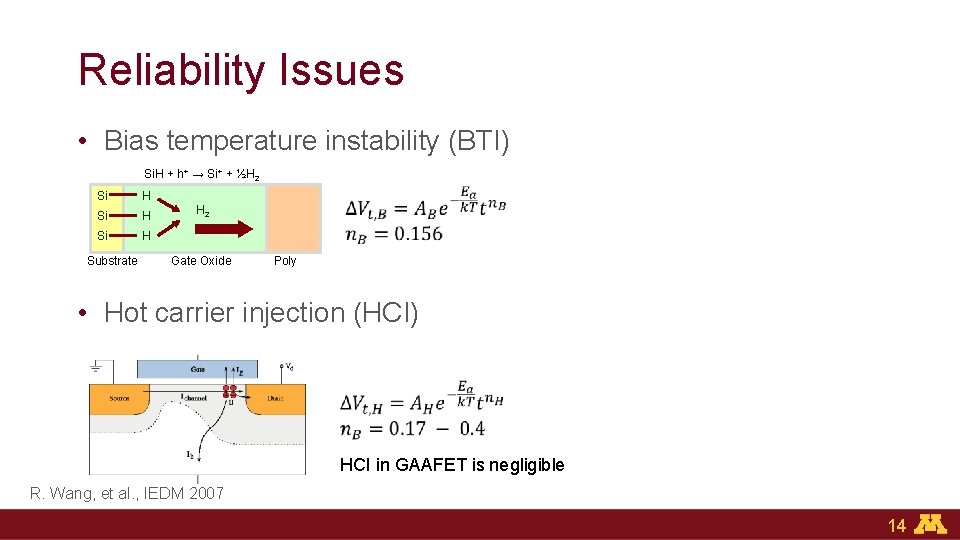

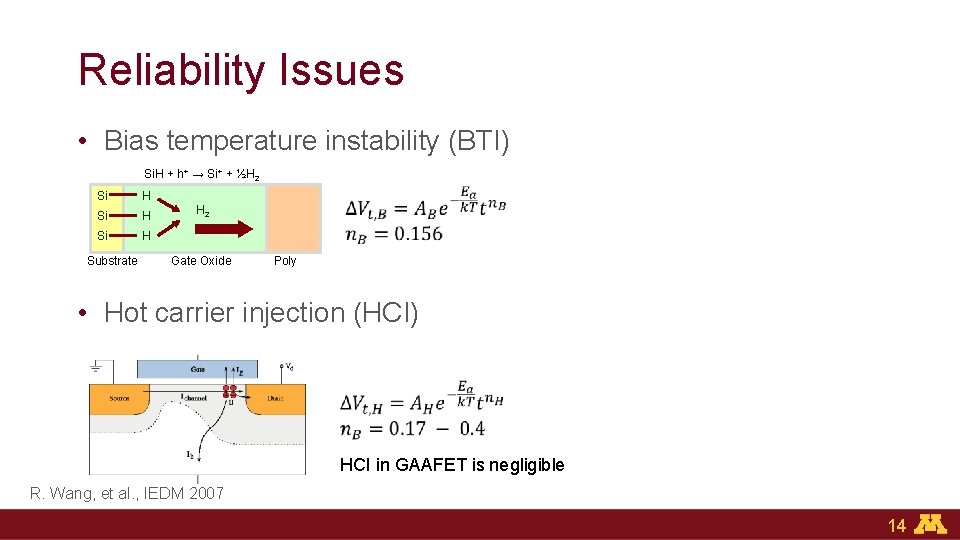

Reliability Issues • Bias temperature instability (BTI) Si. H + h+ → Si+ + ½H 2 Si Si H Substrate H H 2 Gate Oxide Poly • Hot carrier injection (HCI) HCI in GAAFET is negligible R. Wang, et al. , IEDM 2007 14

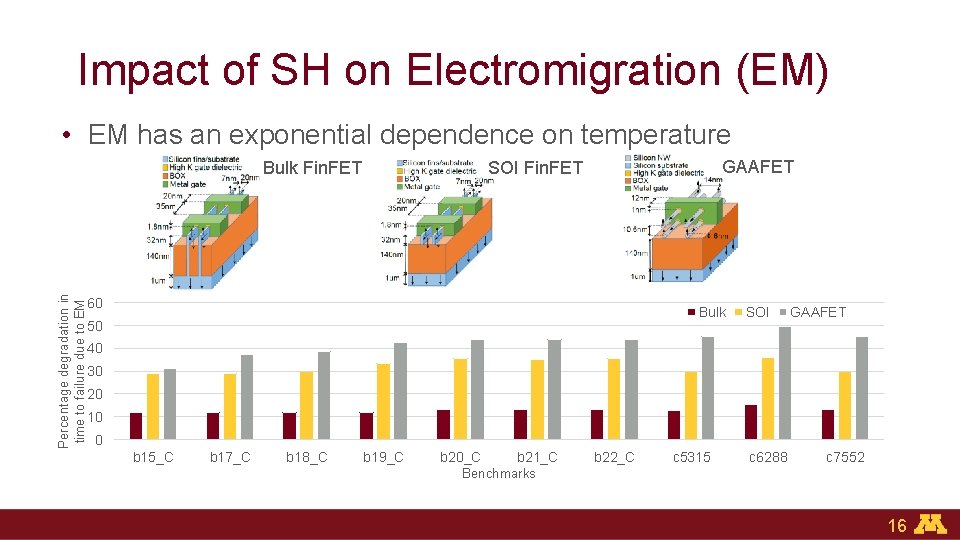

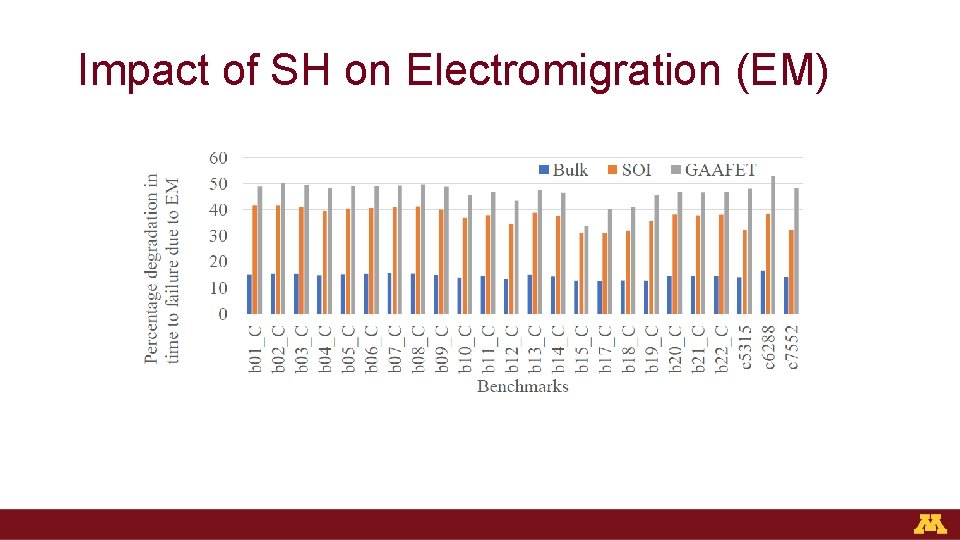

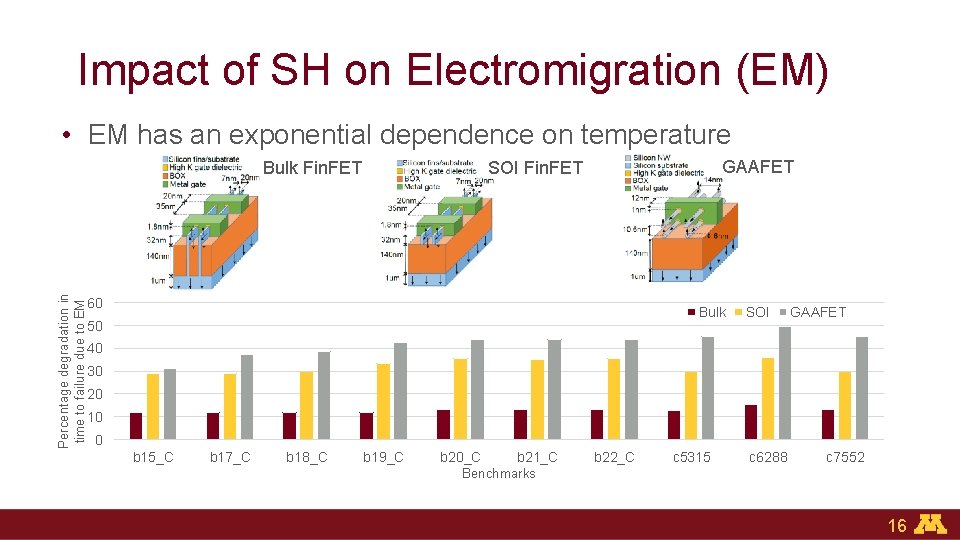

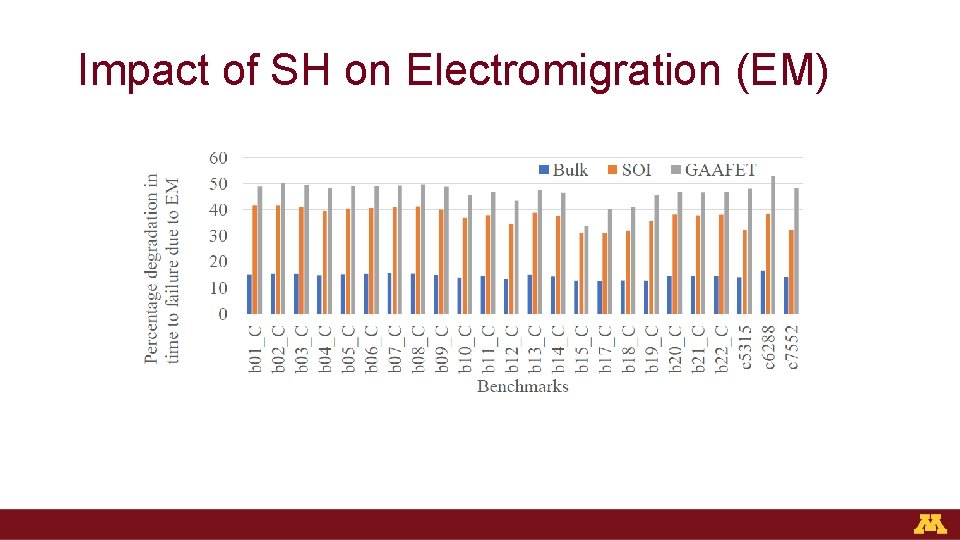

Impact of SH on Electromigration (EM) • EM has an exponential dependence on temperature Percentage degradation in time to failure due to EM Bulk Fin. FET GAAFET SOI Fin. FET 60 Bulk 50 SOI GAAFET 40 30 20 10 0 b 15_C b 17_C b 18_C b 19_C b 20_C b 21_C Benchmarks b 22_C c 5315 c 6288 c 7552 16

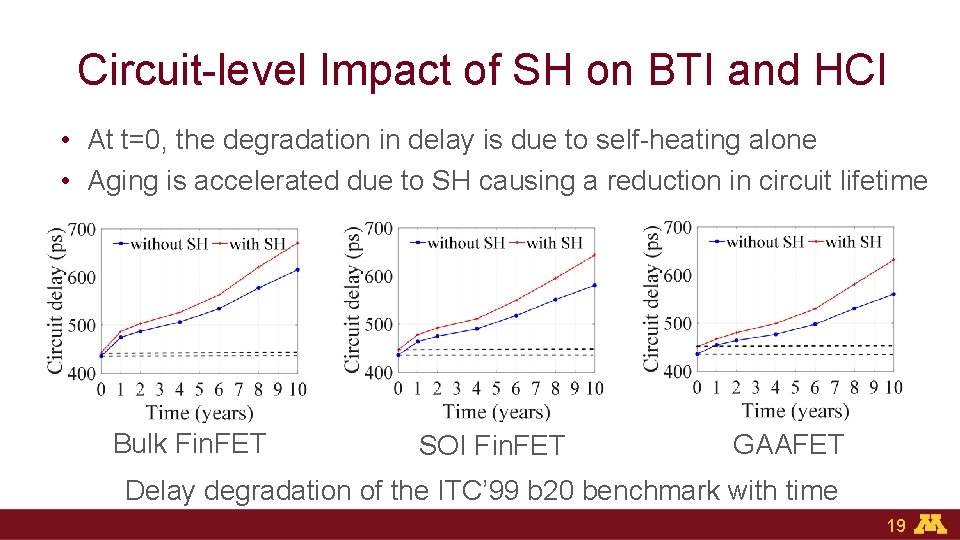

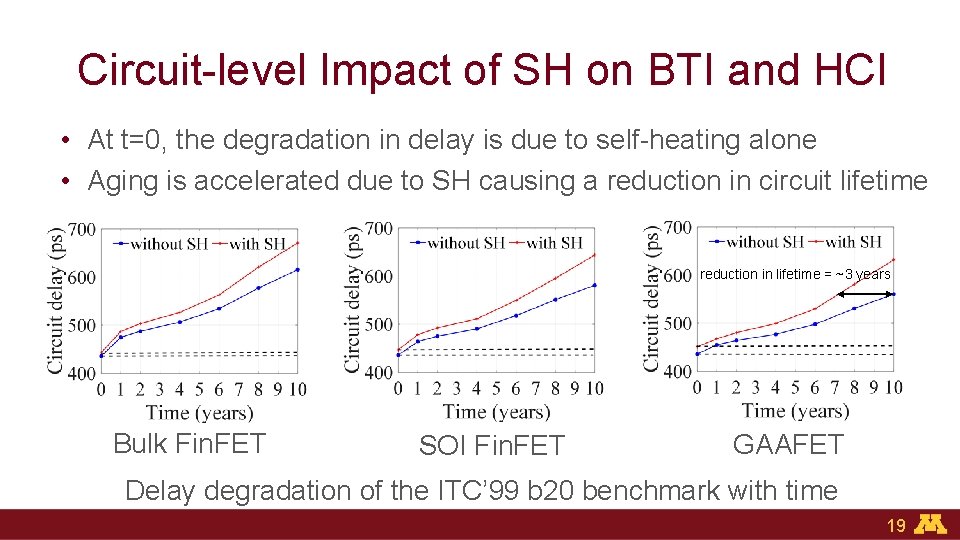

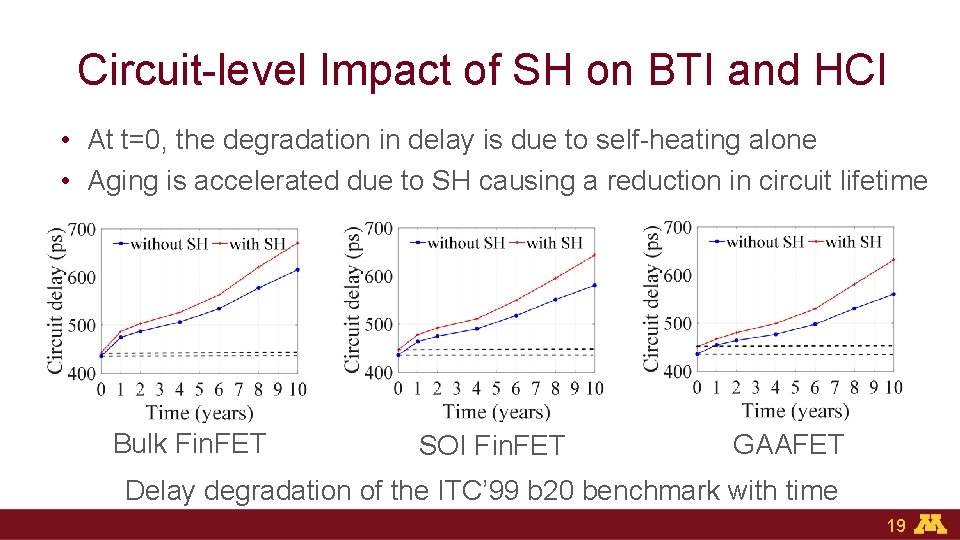

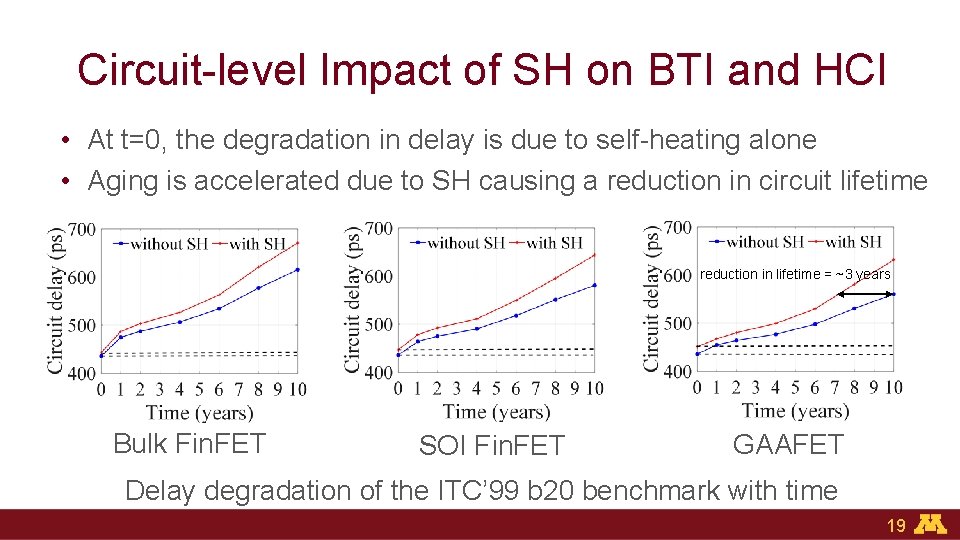

Circuit-level Impact of SH on BTI and HCI • At t=0, the degradation in delay is due to self-heating alone • Aging is accelerated due to SH causing a reduction in circuit lifetime Bulk Fin. FET SOI Fin. FET GAAFET Delay degradation of the ITC’ 99 b 20 benchmark with time 19

Circuit-level Impact of SH on BTI and HCI • At t=0, the degradation in delay is due to self-heating alone • Aging is accelerated due to SH causing a reduction in circuit lifetime reduction in lifetime = ~3 years Bulk Fin. FET SOI Fin. FET GAAFET Delay degradation of the ITC’ 99 b 20 benchmark with time 19

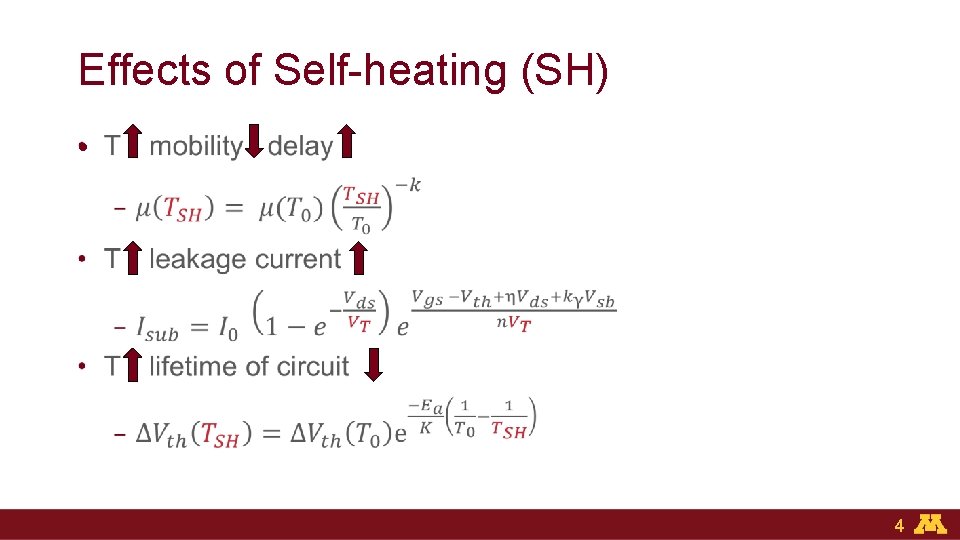

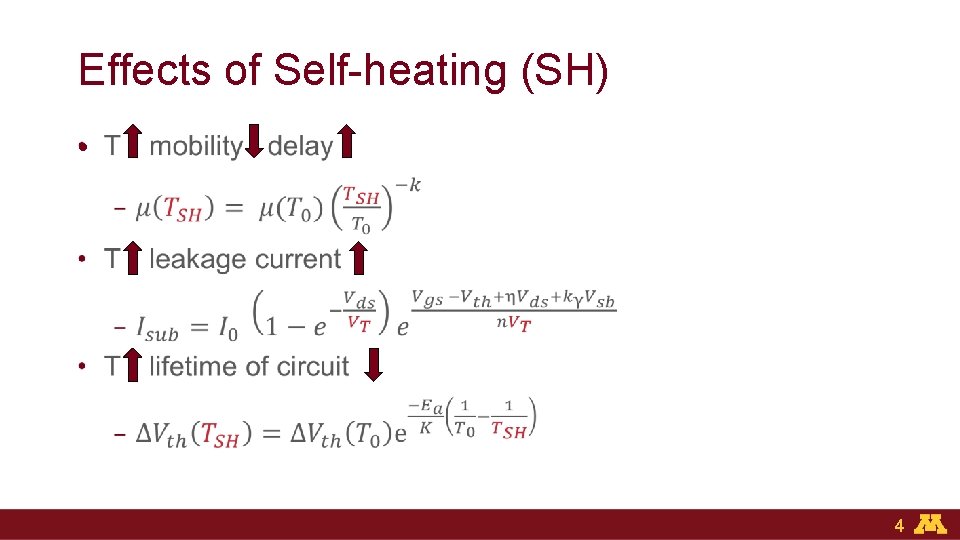

Effects of Self-heating (SH) • 4

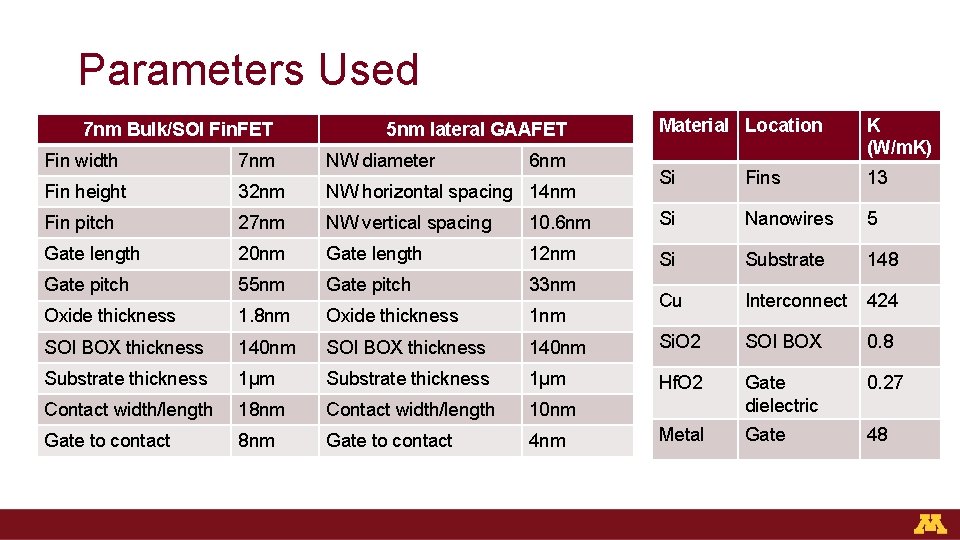

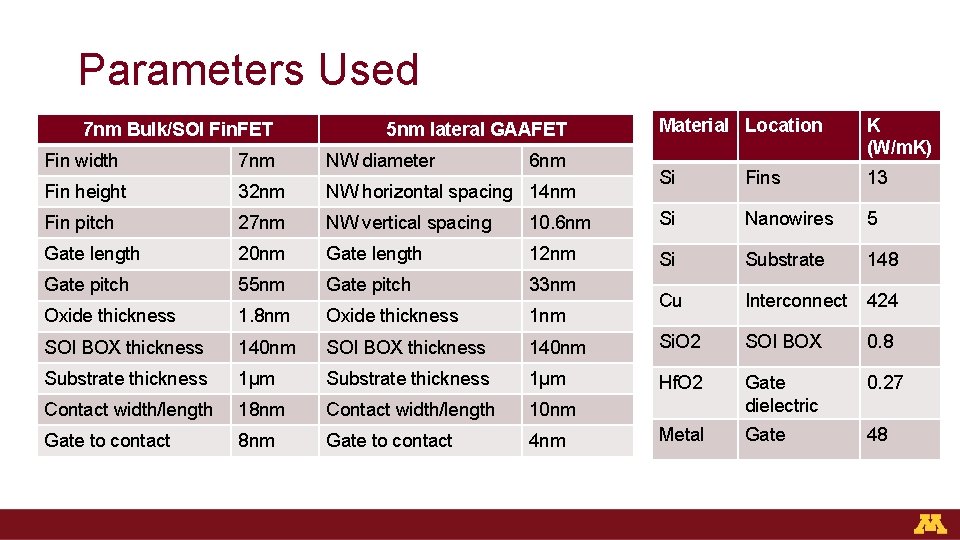

Parameters Used 7 nm Bulk/SOI Fin. FET 5 nm lateral GAAFET 6 nm Material Location K (W/m. K) Si Fins 13 Fin width 7 nm NW diameter Fin height 32 nm NW horizontal spacing 14 nm Fin pitch 27 nm NW vertical spacing 10. 6 nm Si Nanowires 5 Gate length 20 nm Gate length 12 nm Si Substrate 148 Gate pitch 55 nm Gate pitch 33 nm Oxide thickness 1. 8 nm Oxide thickness 1 nm Cu Interconnect 424 SOI BOX thickness 140 nm Si. O 2 SOI BOX 0. 8 Substrate thickness 1µm Hf. O 2 0. 27 Contact width/length 18 nm Contact width/length 10 nm Gate dielectric Gate to contact 8 nm Gate to contact 4 nm Metal Gate 48

Look-up-table (LUT) Characterization Local interconnect Metal • Fin Contact Gate terminal 7

A G SO A I FE T Bu lk G SO A A I FE T Bu lk G SO A A I FE T Bu lk G SO A A I FE T lk Bu Percentage degradation in circuit delay after 10 years due to SH S AA OI FE T Bu lk G SO AA I FE T Bu lk G SO AA I FE T Bu lk G SO AA I FE T G lk Bu Temperature rise (C) Circuit-level Impact on BTI and HCI 50 40 30 20 10 0 Average temperature rise (C) b 15_C b 17_C b 18_C b 19_C b 20_C b 21_C b 22_C Peak temperature rise (C) c 5315 20 15 10 5 0 c 5315 c 6288 BTI c 6288 c 7552 HCI c 7552 13

Circuit Level Analysis

Impact of SH on Electromigration (EM)