The Xilinx Spartan3 E FPGA family Field Programmable

The Xilinx Spartan-3 E FPGA family

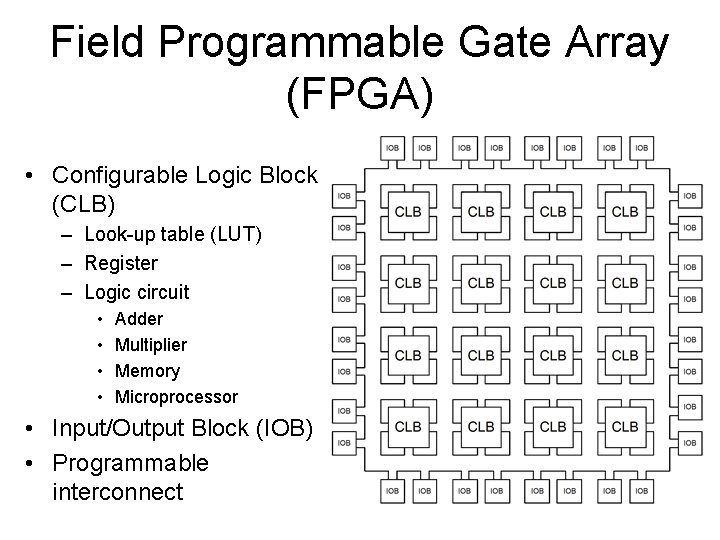

Field Programmable Gate Array (FPGA) • Configurable Logic Block (CLB) – Look-up table (LUT) – Register – Logic circuit • • Adder Multiplier Memory Microprocessor • Input/Output Block (IOB) • Programmable interconnect

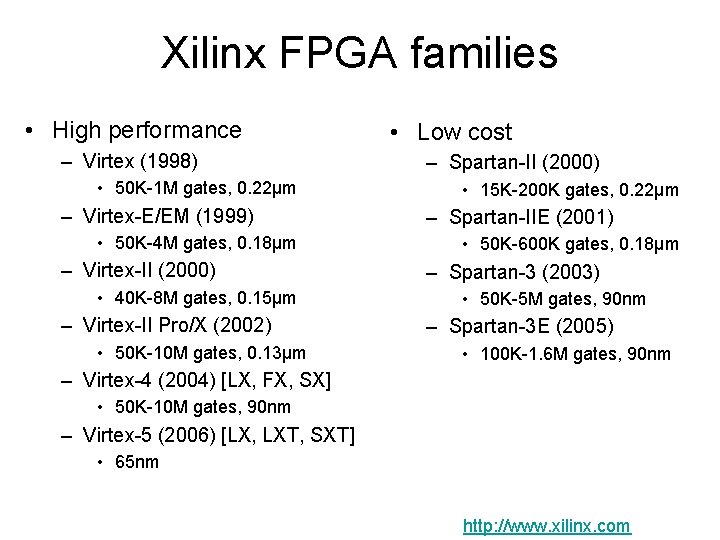

Xilinx FPGA families • High performance – Virtex (1998) • 50 K-1 M gates, 0. 22µm – Virtex-E/EM (1999) • 50 K-4 M gates, 0. 18µm – Virtex-II (2000) • 40 K-8 M gates, 0. 15µm – Virtex-II Pro/X (2002) • 50 K-10 M gates, 0. 13µm • Low cost – Spartan-II (2000) • 15 K-200 K gates, 0. 22µm – Spartan-IIE (2001) • 50 K-600 K gates, 0. 18µm – Spartan-3 (2003) • 50 K-5 M gates, 90 nm – Spartan-3 E (2005) • 100 K-1. 6 M gates, 90 nm – Virtex-4 (2004) [LX, FX, SX] • 50 K-10 M gates, 90 nm – Virtex-5 (2006) [LX, LXT, SXT] • 65 nm http: //www. xilinx. com

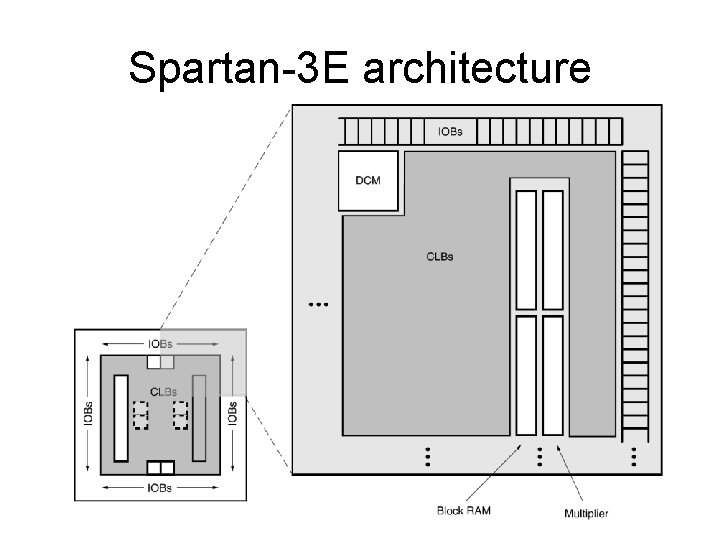

Spartan-3 E architecture

Four Types of Interconnect Tiles

Array of Interconnect Tiles

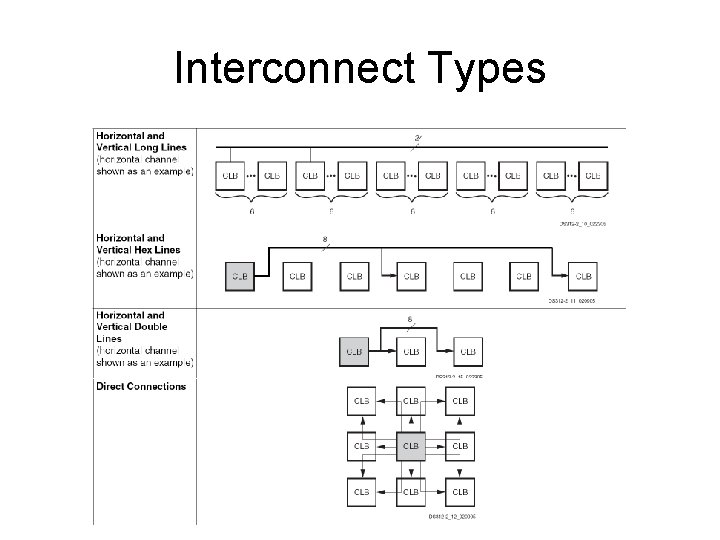

Interconnect Types

Simplified IOB Diagram • 3. 3 V low-voltage TTL (LVTTL) • Low-voltage CMOS (LVCMOS) at 3. 3 V, 2. 5 V, 1. 8 V, 1. 5 V, or 1. 2 V • 3 V PCI at 33 MHz, 66 MHz • HSTL I and III at 1. 8 V • SSTL I at 1. 8 V and 2. 5 V • LVDS, Bus LVDS, mini -LVDS, RSDS • Differential HSTL, SSTL • 2. 5 V LVPECL inputs

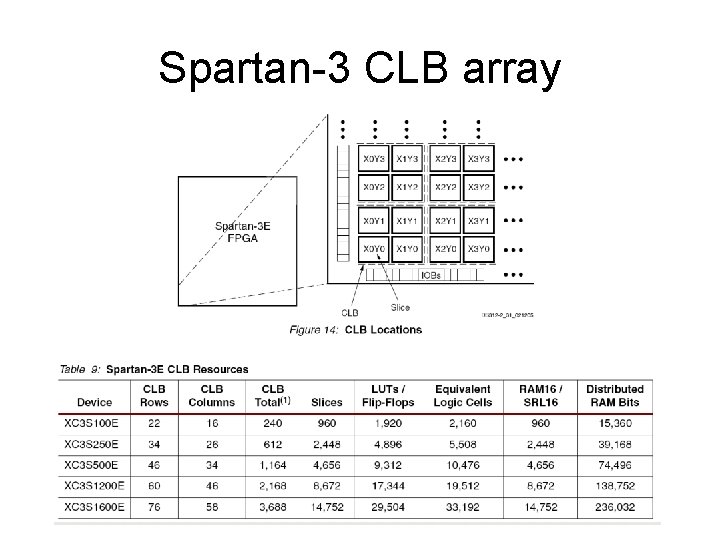

Spartan-3 CLB array

Arrangement of Slices within the CLB

Resources in a Slice

Simplified Diagram of the Left-Hand SLICEM

LUT Resources in a Slice

Dedicated Multiplexers

Carry Logic

Using the Carry Logic

RAM 16 X 1 D Dual-Port Usage

Logic Cell SRL 16 Structure

Block RAM

Dedicated 18 x 18 bit Multiplier

DCM Functional Blocks and Associated Signals • Clock-skew Elimination • Frequency Synthesis • Phase Shifting

Simple DCM usage

Digilent Nexys 2

Digilent Nexys 2

Basic modeling constructs

![Entity Declaration entity identifier is [port (port_interface_list); ] {entity_declarative item} end [entity] [identifier]; interface_list Entity Declaration entity identifier is [port (port_interface_list); ] {entity_declarative item} end [entity] [identifier]; interface_list](http://slidetodoc.com/presentation_image_h2/da20a877fce5336624c681de7ddc79a7/image-26.jpg)

Entity Declaration entity identifier is [port (port_interface_list); ] {entity_declarative item} end [entity] [identifier]; interface_list <= (identifier {, …} : [mode] subtype_indication [: = expression]){; …} mode <= in | out | inout

Entity Declaration entity adder is entity and_or_inv is port ( a : in word; port ( a 1, a 2, b 1, b 2 : in bit : = '1'; b : in word; y : out bit ); sum : out word); end entity and_or_inv; end entity adder; entity top_level is entity adder is port ( a, b : in word; end entity top_level; sum : out word); end entity adder;

Entity Declaration entity program_ROM is port ( address : in std_ulogic_vector(14 downto 0); data : out std_ulogic_vector(7 downto 0); enable : in std_ulogic ); subtype instruction_byte is bit_vector(7 downto 0); type program_array is array (0 to 2**14 - 1) of instruction_byte; constant program : program_array : = ( X"32", X"3 F", X"03", -- LDA $3 F 03 X"71", X"23", -- BLT $23 others => X"00„ --. . . ); end entity program_ROM;

![Architecture Body architecture identifier of entity_name is {block_declarative_item} begin {concurrent_statement} end [architecture][identifier]; Architecture Body architecture identifier of entity_name is {block_declarative_item} begin {concurrent_statement} end [architecture][identifier];](http://slidetodoc.com/presentation_image_h2/da20a877fce5336624c681de7ddc79a7/image-29.jpg)

Architecture Body architecture identifier of entity_name is {block_declarative_item} begin {concurrent_statement} end [architecture][identifier];

Architecture Body entity adder is port ( a : in word; b : in word; sum : out word); end entity adder; architecture abstract of adder is begin add_a_b : process (a, b) is begin sum <= a + b; end process add_a_b; end architecture abstract;

![Signal declaration and assignment signal identifier {, …} : subtype_indication [: =expression]; [label: ] Signal declaration and assignment signal identifier {, …} : subtype_indication [: =expression]; [label: ]](http://slidetodoc.com/presentation_image_h2/da20a877fce5336624c681de7ddc79a7/image-31.jpg)

Signal declaration and assignment signal identifier {, …} : subtype_indication [: =expression]; [label: ] name <= [delay_mechanism] waveform; waveform <= (value_expression [after time_expression]){, …} y <= not or_a_b after 5 ns;

Discrete event simulation • Transaction – After signal assignment, new value at simulaton time T • Active signal – Signal is updated at time T • Event – New value /= old value

Discrete event simulation • Initialization phase – – Each signal is given an initial value Simulation time is set to 0 Each process is activated Signals assigned, transactions scheduled • Simulation cycle – Signal update • Advance time to the next transaction • Perform all scheduled transactions for this time – Process execution • Wake processes which is sensitive to the previous events • New events may occur

Signal assignment entity and_or_inv is port ( a 1, a 2, b 1, b 2 : in bit : = '1'; y : out bit ); end entity and_or_inv; architecture primitive of and_or_inv is signal and_a, and_b : bit; signal or_a_b : bit; begin and_gate_a : process (a 1, a 2) is begin and_a <= a 1 and a 2; end process and_gate_a; and_gate_b : process (b 1, b 2) is begin and_b <= b 1 and b 2; end process and_gate_b; or_gate : process (and_a, and_b) is begin or_a_b <= and_a or and_b; end process or_gate; inv : process (or_a_b) is begin y <= not or_a_b; end process inv; end architecture primitive;

Signal assignment stimulus_05_3_a : process is begin or_a_b <= '1' after 20 ns, '0' after 40 ns; wait; end process stimulus_05_3_a; architecture test of fg_05_04 is constant prop_delay : time : = 5 ns; signal a, b, sel, z : bit; begin mux : process (a, b, sel) is begin case sel is when '0' => z <= a after prop_delay; when '1' => z <= b after prop_delay; end case; end process mux;

Signal assignment clock_gen : process (clk) is begin if clk = '0' then clk <= '1' after T_pw, '0' after 2*T_pw; end if; end process clock_gen; process_05_3_b : process is constant T_pw : delay_length : = 10 ns; begin clk <= '1' after T_pw, '0' after 2*T_pw; wait for 2*T_pw; end process_05_3_b;

Signal attributes S’delayed(T) – A signal that takes on the same value as S but is delayed by time T S’stable(T) – A Boolean signal that is true if there has been no event on S in time T interval T up to the current time, othervise false S’quiet(T) – A Boolean signal that is true if there has been no transaction on S in time T interval T up to the current time, othervise false S’transaction – A signal of type bit that changes value from ‘ 0’ to ‘ 1’ or vice versa each time there is a transaction on S

Signal attributes S’event – True if there is an event on S in the current simulation cycle, false otherwise S’active – True if there is a transaction on S in the current simulation cycle, false otherwise S’last_event – The time interval since the last event on S S’last_active – The time interval since the last transaction on S S’last_value – The value of S just before the last event on S

Examples constant Tpw_clk : delay_length : = 10 ns; constant Tsu : delay_length : = 4 ns; if clk'event and (clk = '1' or clk = 'H') and (clk'last_value = '0' or clk'last_value = 'L') then assert d'last_event >= Tsu report "Timing error: d changed within setup time of clk"; end if; assert (not clk'event) or clk'delayed'last_event >= Tpw_clk report "Clock frequency too high";

![Wait statement [label: ] wait [on signal_name {, …}] [until boolean_expression] [for time_expression]; Wait statement [label: ] wait [on signal_name {, …}] [until boolean_expression] [for time_expression];](http://slidetodoc.com/presentation_image_h2/da20a877fce5336624c681de7ddc79a7/image-40.jpg)

Wait statement [label: ] wait [on signal_name {, …}] [until boolean_expression] [for time_expression];

Examples half_add : process is begin sum <= a xor b after T_pd; carry <= a and b after T_pd; wait on a, b; end process half_add; half_add : process (a, b) is begin sum <= a xor b after T_pd; carry <= a and b after T_pd; end process half_add;

Examples entity mux 2 is port ( a, b, sel : in bit; z : out bit ); end entity mux 2; -------------------------architecture behavioral of mux 2 is constant prop_delay : time : = 2 ns; begin slick_mux : process is begin case sel is when '0' => z <= a after prop_delay; wait on sel, a; when '1' => z <= b after prop_delay; wait on sel, b; end case; end process slick_mux; end architecture behavioral;

Examples wait until clk = '1'; report "clk rising edge detected"; wait on clk until reset = '0'; report "synchronous reset detected"; wait until trigger = '1' for 1 ms; if trigger'event and trigger = '1' then report "trigger rising edge detected"; else report "trigger timeout"; end if;

Examples test_gen : process is begin test 0 <= '0' after 10 ns, '1' after 20 ns, '0' after 30 ns, '1' after 40 ns; test 1 <= '0' after 10 ns, '1' after 30 ns; wait; end process test_gen;

Delta delay • Signal assignment without after equivalent to a delay of 0 fs • BUT the signal value does not change as soon as the signal assignment statement is executed • Assignment schedules a transaction for the signal • The process does NOT see the effect of the assignment until it next time resumes

- Slides: 45