The TILEGx Processor Enabling HPC through MassiveScale Manycore

The TILE-Gx Processor: Enabling HPC through Massive-Scale Manycore Bob Doud Director of Processor Strategy, Tilera Corp. HPEC, September 2011

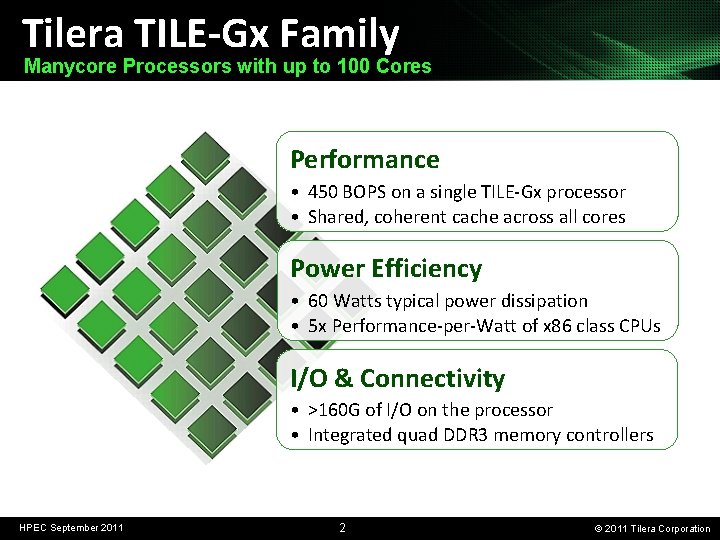

Tilera TILE-Gx Family Manycore Processors with up to 100 Cores Performance • 450 BOPS on a single TILE-Gx processor • Shared, coherent cache across all cores Power Efficiency • 60 Watts typical power dissipation • 5 x Performance-per-Watt of x 86 class CPUs I/O & Connectivity • >160 G of I/O on the processor • Integrated quad DDR 3 memory controllers HPEC September 2011 2 © 2011 Tilera Corporation

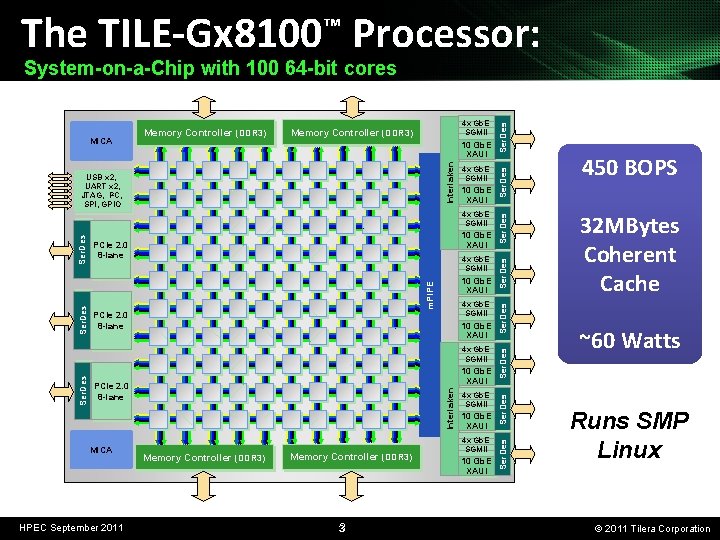

The TILE-Gx 8100™ Processor: 4 x Gb. E SGMII 10 Gb. E XAUI 4 x Gb. E SGMII PCIe 2. 0 8 -lane 10 Gb. E XAUI PCIe 2. 0 8 -lane Mi. CA HPEC September 2011 Interlaken Ser. Des 4 x Gb. E SGMII Memory Controller (DDR 3) 3 4 x Gb. E SGMII 10 Gb. E XAUI Ser. Des 10 Gb. E XAUI PCIe 2. 0 8 -lane m. PIPE Ser. Des 4 x Gb. E SGMII Ser. Des 10 Gb. E XAUI Ser. Des 4 x Gb. E SGMII Ser. Des USB x 2, UART x 2, JTAG, I 2 C, SPI, GPIO Ser. Des 10 Gb. E XAUI Ser. Des 4 x Gb. E SGMII Memory Controller (DDR 3) Interlaken Mi. CA Memory Controller (DDR 3) Ser. Des System-on-a-Chip with 100 64 -bit cores 450 BOPS 32 MBytes Coherent Cache ~60 Watts Runs SMP Linux © 2011 Tilera Corporation

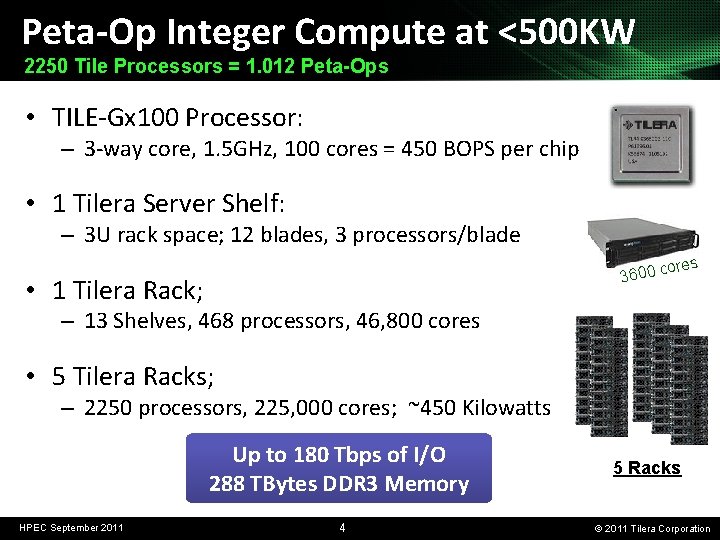

Peta-Op Integer Compute at <500 KW 2250 Tile Processors = 1. 012 Peta-Ops • TILE-Gx 100 Processor: – 3 -way core, 1. 5 GHz, 100 cores = 450 BOPS per chip • 1 Tilera Server Shelf: – 3 U rack space; 12 blades, 3 processors/blade 3600 • 1 Tilera Rack; cores – 13 Shelves, 468 processors, 46, 800 cores • 5 Tilera Racks; – 2250 processors, 225, 000 cores; ~450 Kilowatts Up to 180 Tbps of I/O 288 TBytes DDR 3 Memory HPEC September 2011 4 5 Racks © 2011 Tilera Corporation

TILE-Gx Enables a Range of HPC Applications Real-Time Informatics • Cyber Security Data Harvesting • Threat Analysis / Forensics Video Surveillance & Analysis • Image compression/decompression • Target Tracking / Pattern Recognition Network Security Processing • Intrusion Prevention (IPS/IDS) • Data Leakage Protection (DLP) Integer Compute • Hyper-Scale Integer Computing • Compute-Intensive SIMD & DSP HPEC September 2011 5 © 2011 Tilera Corporation

Thank You • Please stop by our table outside the auditorium • TILE-Gx processor solutions on display • We’ll be happy to discuss your HPC requirements HPEC September 2011 6 © 2011 Tilera Corporation

- Slides: 6