The Threshold Voltage The voltage applied between the

The Threshold Voltage §The voltage applied between the gate and the source which causes the beginning of the channel surface strong inversion. §Threshold voltage Vt is a function of : » Vfb = flatband voltage; depends on difference in work function between gate and substrate and on fixed surface charge. » Fs = surface potential (FD). » Gate oxide thickness. » Charge in the channel area. » Additional ion implantation. n Typical values: 0. 2 V to 1. 0 V for NMOS and -0. 2 to -1. 0 V for PMOS VLSI Design/ RMC Devices-2 © D. Al-Khalili 1

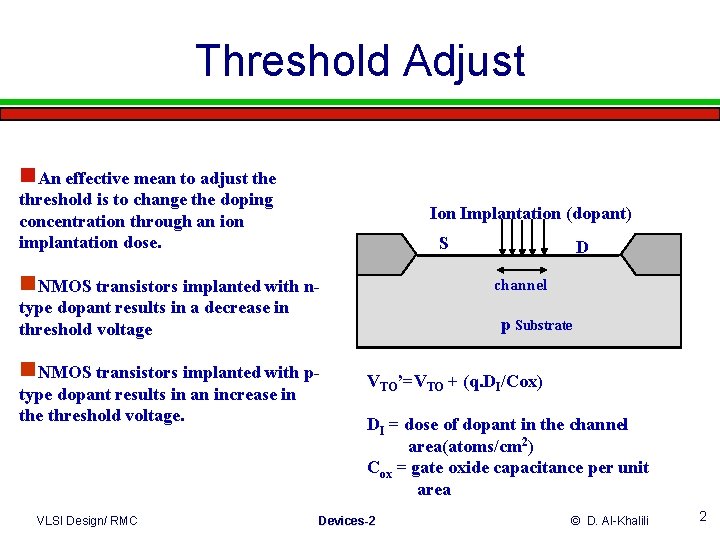

Threshold Adjust g. An effective mean to adjust the threshold is to change the doping concentration through an ion implantation dose. Ion Implantation (dopant) S g. NMOS transistors implanted with ntype dopant results in a decrease in threshold voltage g. NMOS transistors implanted with ptype dopant results in an increase in the threshold voltage. VLSI Design/ RMC D channel p Substrate VTO’=VTO + (q. DI/Cox) DI = dose of dopant in the channel area(atoms/cm 2) Cox = gate oxide capacitance per unit area Devices-2 © D. Al-Khalili 2

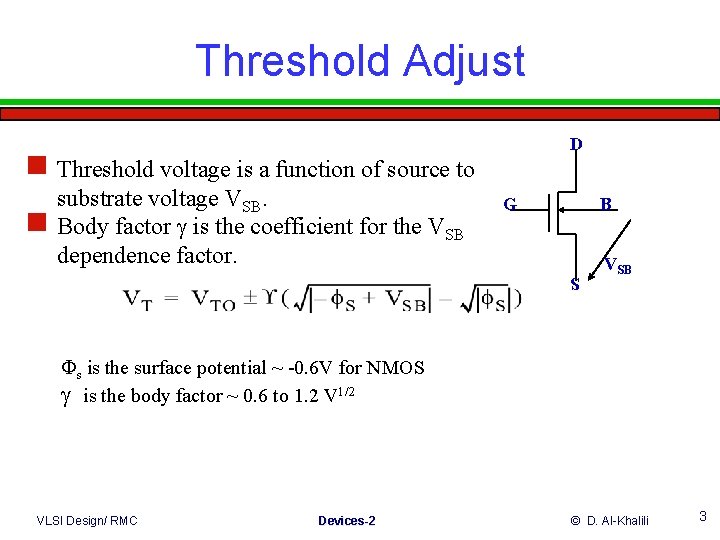

Threshold Adjust g Threshold voltage is a function of source to substrate voltage VSB. g Body factor is the coefficient for the VSB dependence factor. D G B VSB S Fs is the surface potential ~ -0. 6 V for NMOS is the body factor ~ 0. 6 to 1. 2 V 1/2 VLSI Design/ RMC Devices-2 © D. Al-Khalili 3

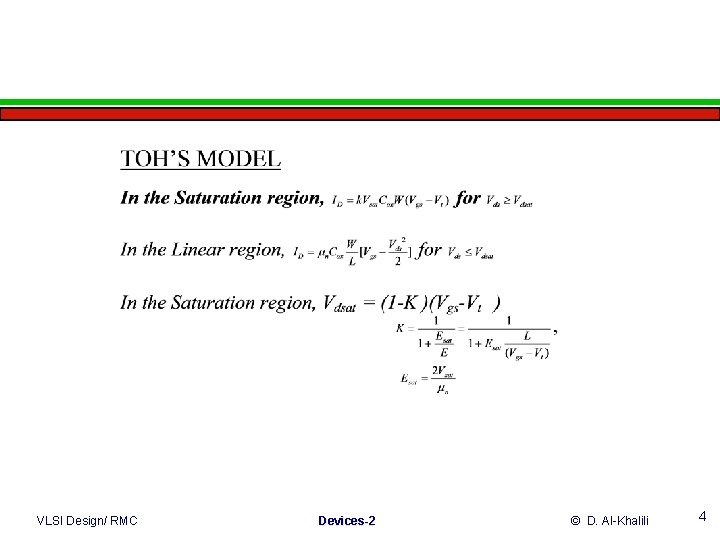

VLSI Design/ RMC Devices-2 © D. Al-Khalili 4

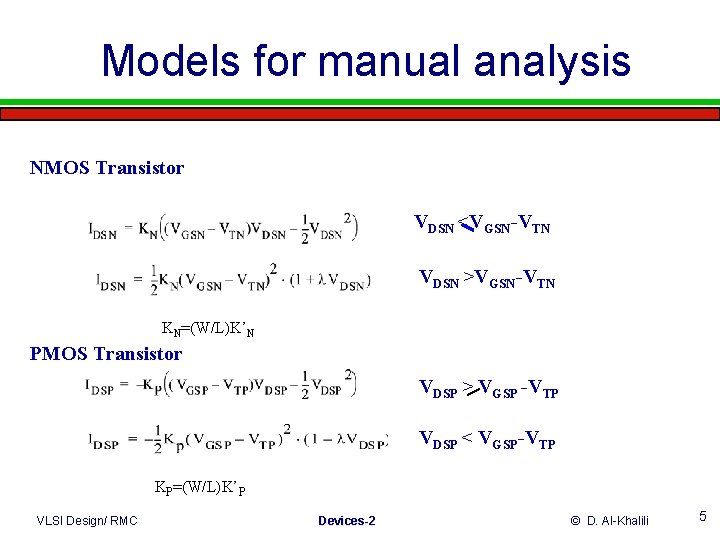

Models for manual analysis NMOS Transistor VDSN <VGSN-VTN VDSN >VGSN-VTN KN=(W/L)K’N PMOS Transistor VDSP > VGSP -VTP VDSP < VGSP-VTP KP=(W/L)K’P VLSI Design/ RMC Devices-2 © D. Al-Khalili 5

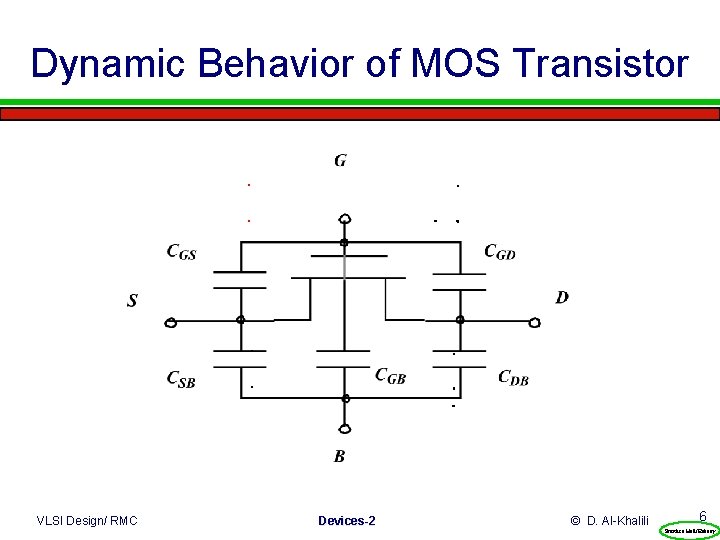

Dynamic Behavior of MOS Transistor VLSI Design/ RMC Devices-2 © D. Al-Khalili 6 Prentice Hall/Rabaey

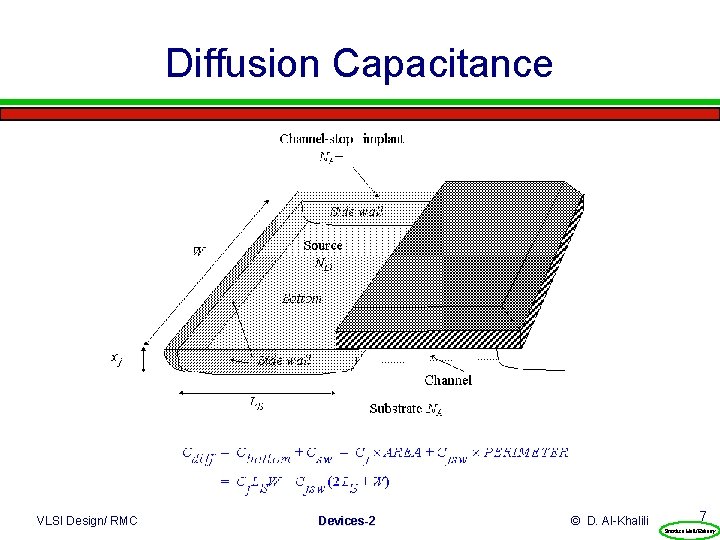

Diffusion Capacitance VLSI Design/ RMC Devices-2 © D. Al-Khalili 7 Prentice Hall/Rabaey

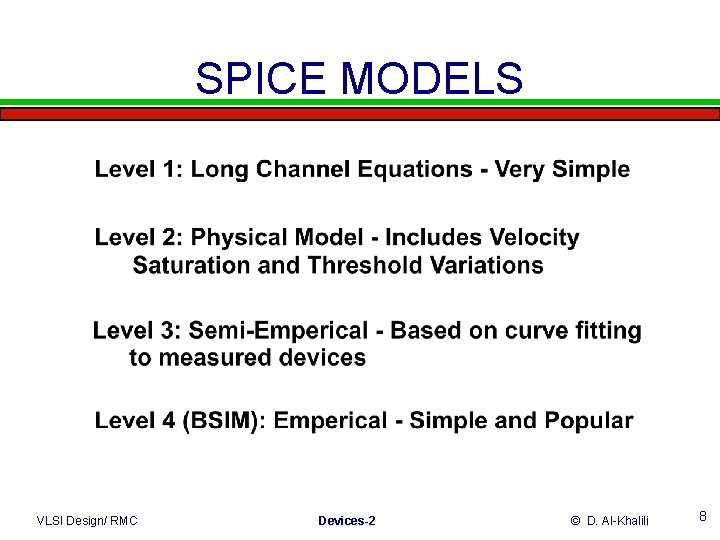

SPICE MODELS VLSI Design/ RMC Devices-2 © D. Al-Khalili 8

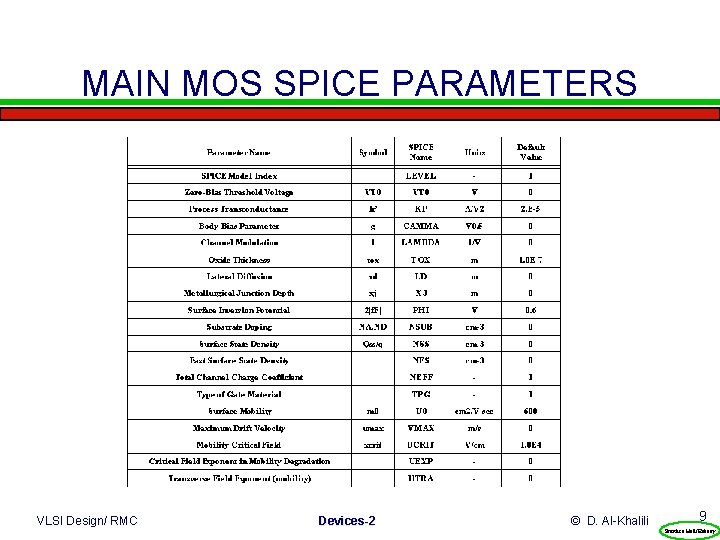

MAIN MOS SPICE PARAMETERS VLSI Design/ RMC Devices-2 © D. Al-Khalili 9 Prentice Hall/Rabaey

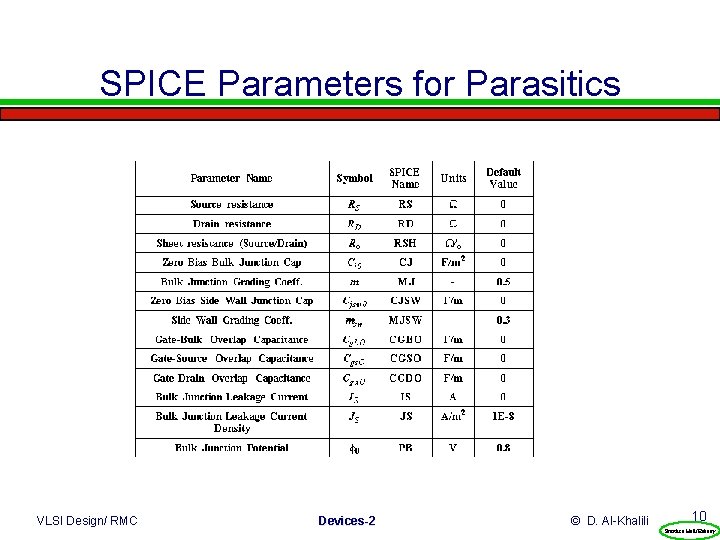

SPICE Parameters for Parasitics VLSI Design/ RMC Devices-2 © D. Al-Khalili 10 Prentice Hall/Rabaey

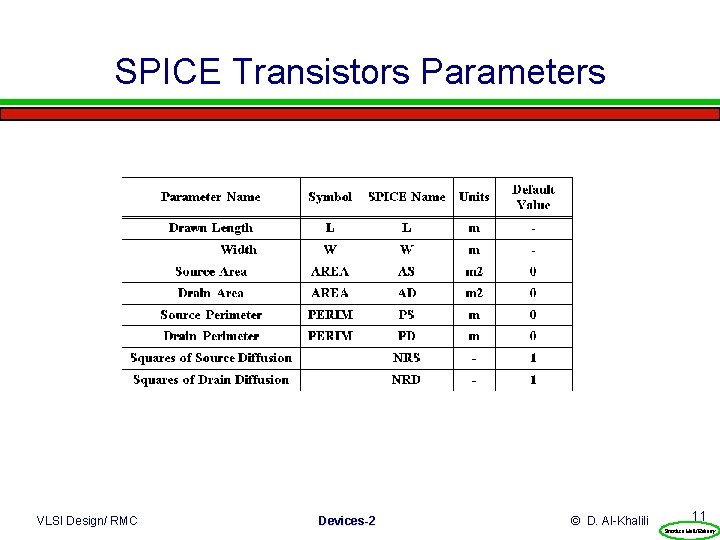

SPICE Transistors Parameters VLSI Design/ RMC Devices-2 © D. Al-Khalili 11 Prentice Hall/Rabaey

- Slides: 11