The Taiwan group Institute of Phys Academia Sinica

- Slides: 37

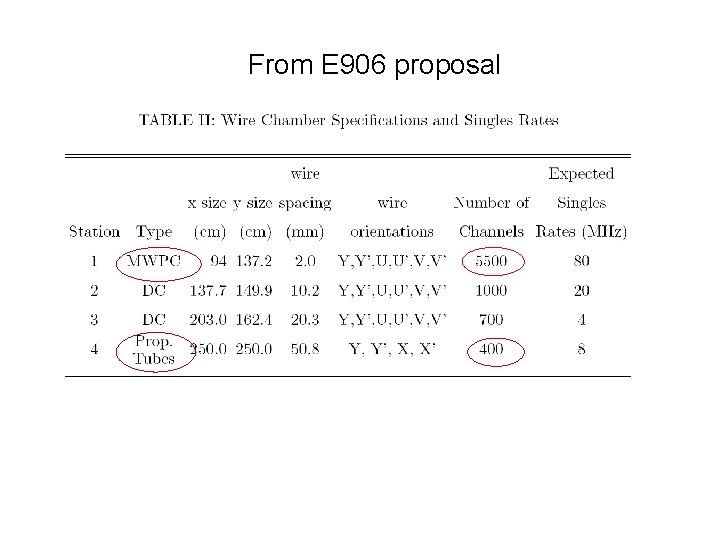

The Taiwan group • • Institute of Phys, Academia Sinica: Wen-Chen Chang, Yen-Chu Chen, Da-Shung Su Ling-Tung U: Ting-Hua Chang Committed responsibility: • • • Build the preamplifier-discriminators cards for 5500 tracking channels in Station 1 MWPC and for 400 channels Proportional tubes in Station 4, Build the readout system for Coincidence Registers (CR), which consists of the CR modules for 5500 tracking channels in Station 1 MWPC, for 400 channels Proportional tubes in Station 4, and for 250 channels of the hodoscope planes in all stations, Participate in the Trigger upgrade project – contribute 2 commercial FPGA logic units and 1 graduate student.

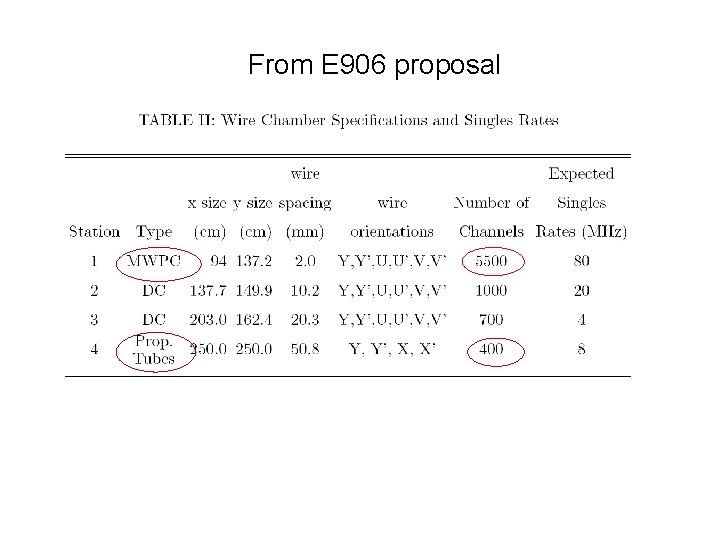

From E 906 proposal

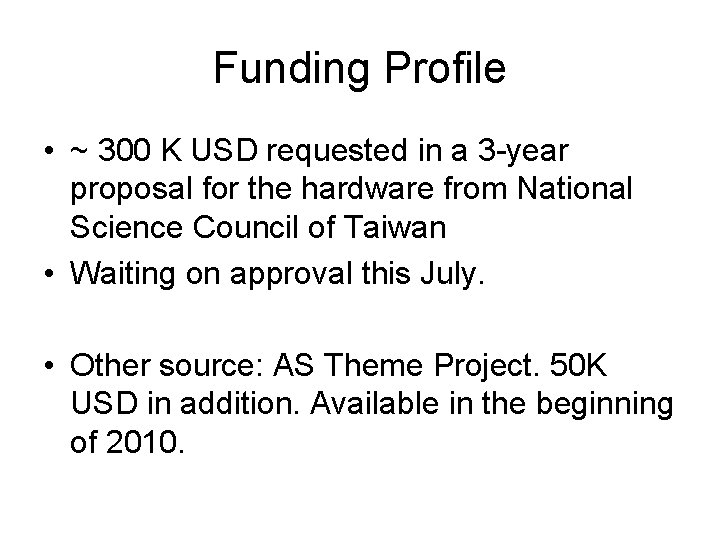

Funding Profile • ~ 300 K USD requested in a 3 -year proposal for the hardware from National Science Council of Taiwan • Waiting on approval this July. • Other source: AS Theme Project. 50 K USD in addition. Available in the beginning of 2010.

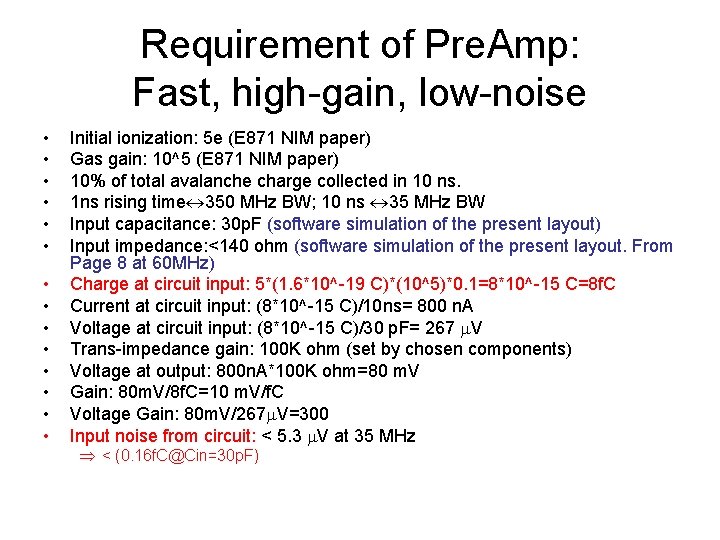

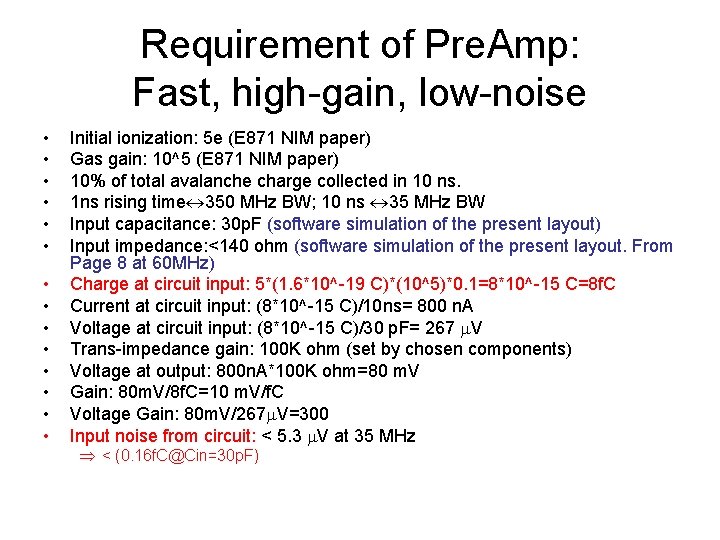

Requirement of Pre. Amp: Fast, high-gain, low-noise • • • • Initial ionization: 5 e (E 871 NIM paper) Gas gain: 10^5 (E 871 NIM paper) 10% of total avalanche charge collected in 10 ns. 1 ns rising time 350 MHz BW; 10 ns 35 MHz BW Input capacitance: 30 p. F (software simulation of the present layout) Input impedance: <140 ohm (software simulation of the present layout. From Page 8 at 60 MHz) Charge at circuit input: 5*(1. 6*10^-19 C)*(10^5)*0. 1=8*10^-15 C=8 f. C Current at circuit input: (8*10^-15 C)/10 ns= 800 n. A Voltage at circuit input: (8*10^-15 C)/30 p. F= 267 V Trans-impedance gain: 100 K ohm (set by chosen components) Voltage at output: 800 n. A*100 K ohm=80 m. V Gain: 80 m. V/8 f. C=10 m. V/f. C Voltage Gain: 80 m. V/267 V=300 Input noise from circuit: < 5. 3 V at 35 MHz Þ < (0. 16 f. C@Cin=30 p. F)

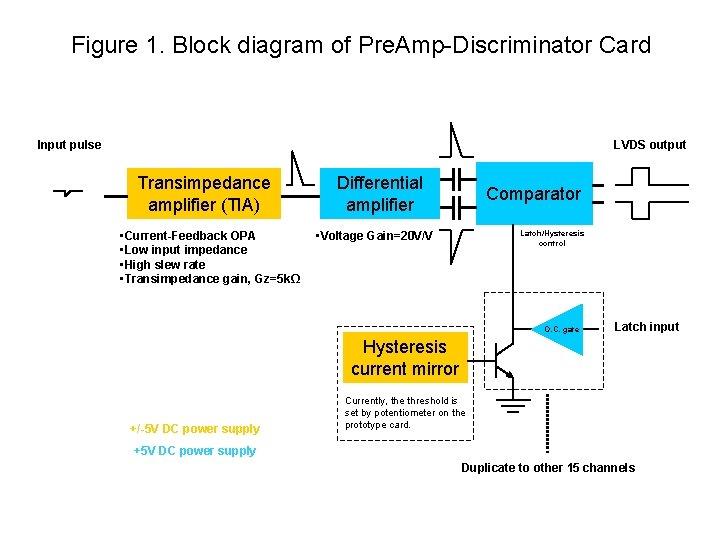

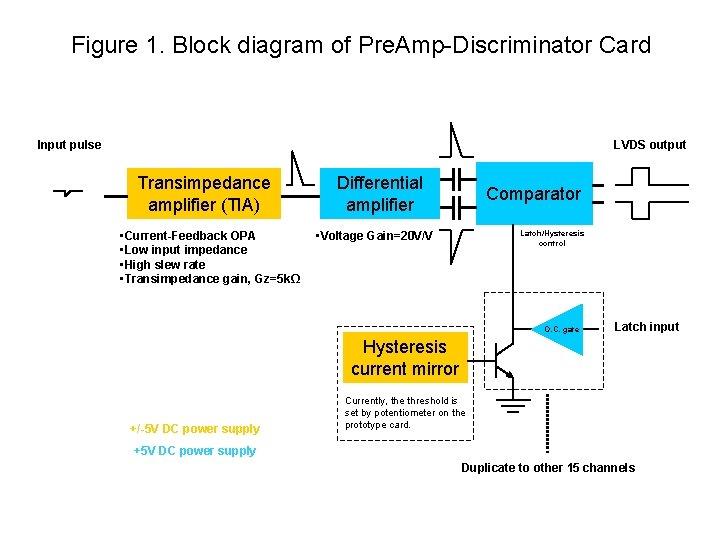

Figure 1. Block diagram of Pre. Amp-Discriminator Card Input pulse LVDS output Transimpedance amplifier (TIA) • Current-Feedback OPA • Low input impedance • High slew rate • Transimpedance gain, Gz=5 kΩ Differential amplifier Comparator • Voltage Gain=20 V/V Latch/Hysteresis control O. C. gate Latch input Hysteresis current mirror +/-5 V DC power supply Currently, the threshold is set by potentiometer on the prototype card. +5 V DC power supply Duplicate to other 15 channels

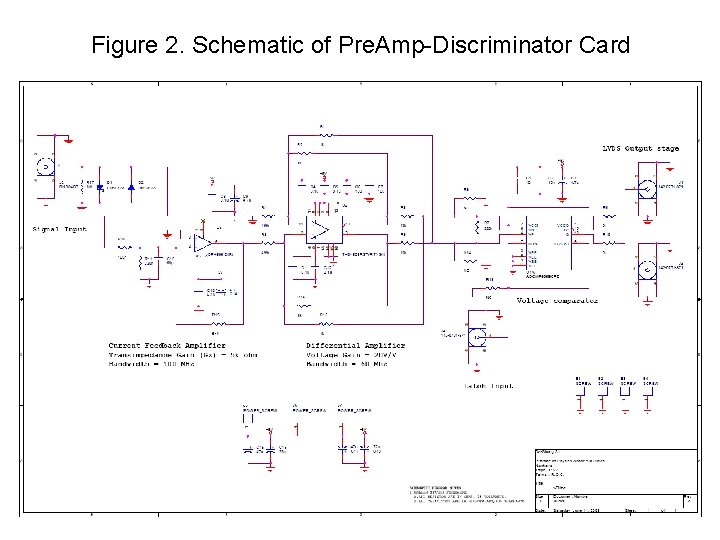

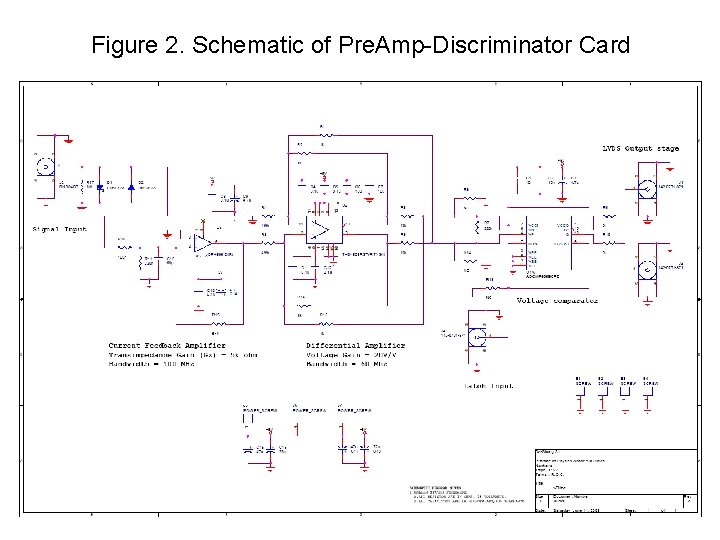

Figure 2. Schematic of Pre. Amp-Discriminator Card

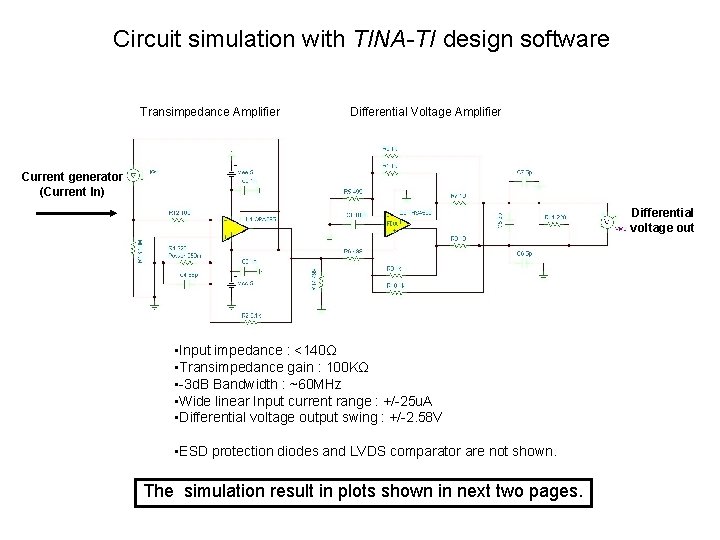

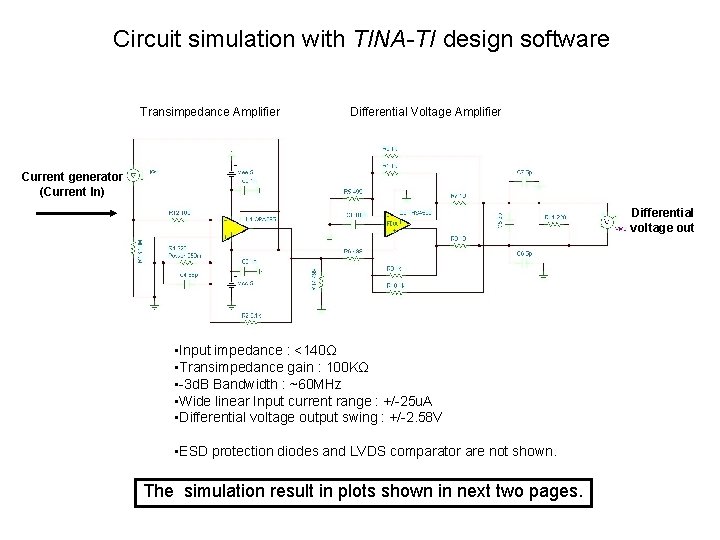

Circuit simulation with TINA-TI design software Transimpedance Amplifier Differential Voltage Amplifier Current generator (Current In) Differential voltage out • Input impedance : <140Ω • Transimpedance gain : 100 KΩ • -3 d. B Bandwidth : ~60 MHz • Wide linear Input current range : +/-25 u. A • Differential voltage output swing : +/-2. 58 V • ESD protection diodes and LVDS comparator are not shown. The simulation result in plots shown in next two pages.

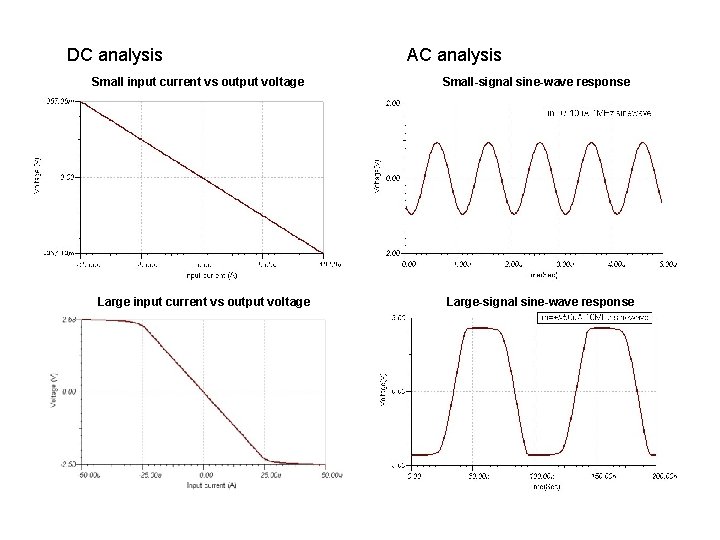

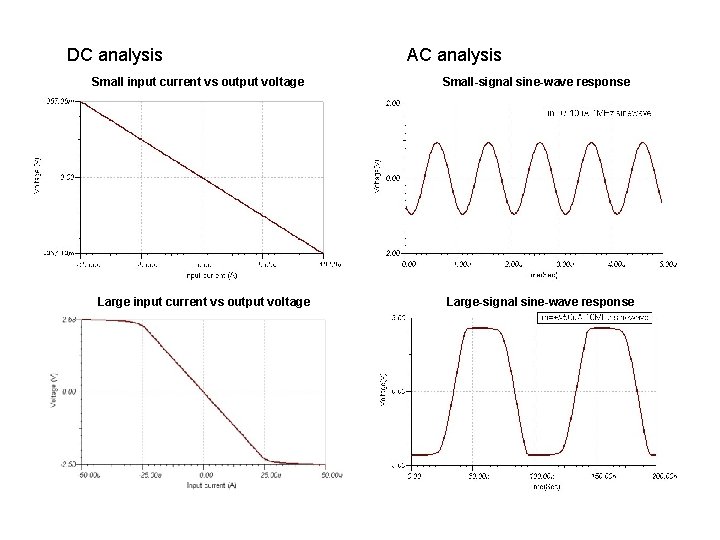

DC analysis Small input current vs output voltage Large input current vs output voltage AC analysis Small-signal sine-wave response Large-signal sine-wave response

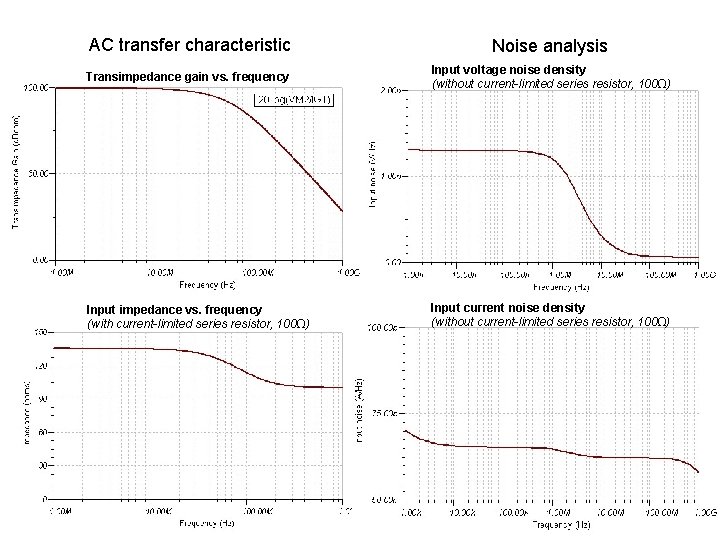

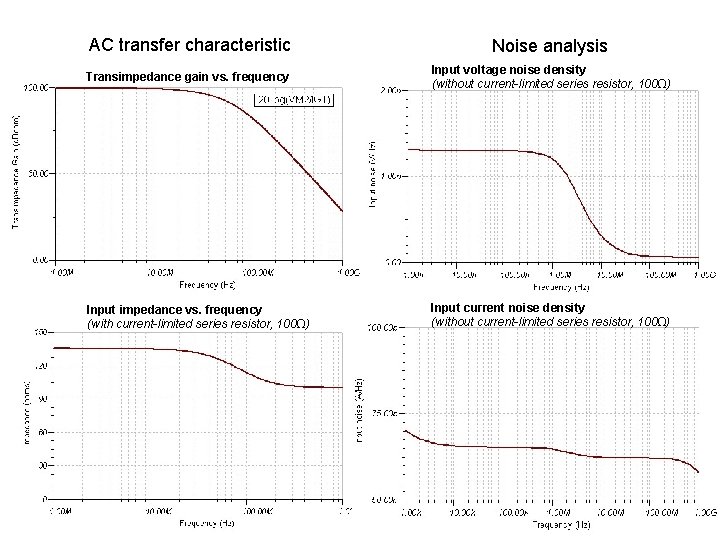

AC transfer characteristic Noise analysis Transimpedance gain vs. frequency Input voltage noise density (without current-limited series resistor, 100Ω) Input impedance vs. frequency (with current-limited series resistor, 100Ω) Input current noise density (without current-limited series resistor, 100Ω)

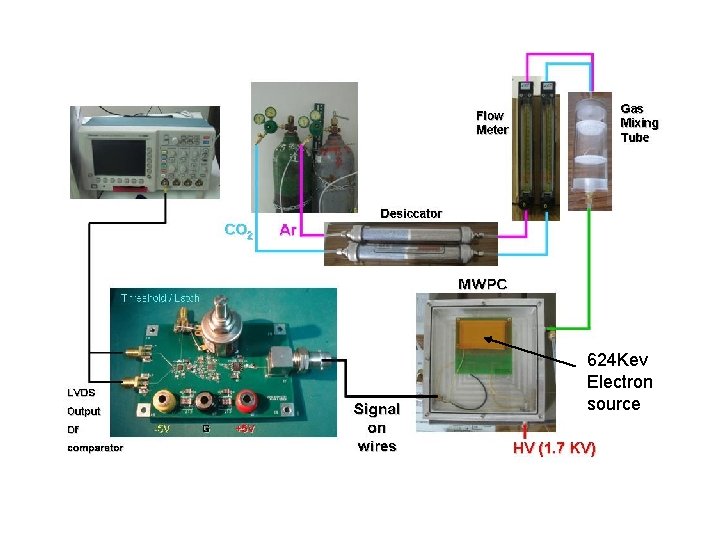

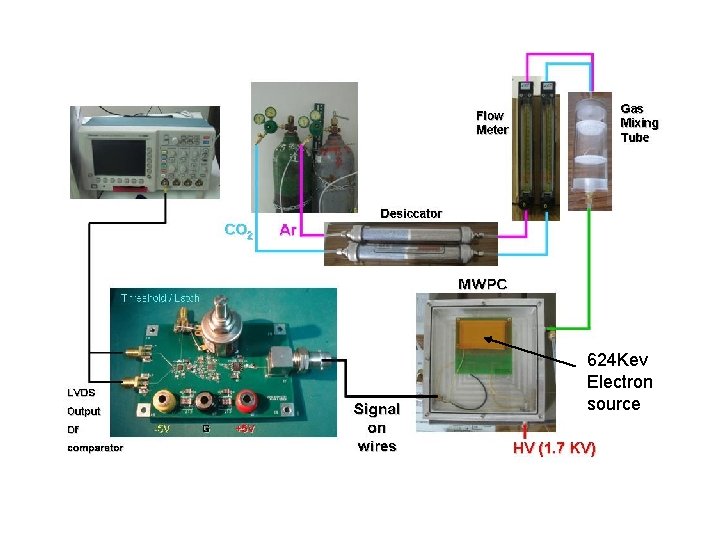

624 Kev Electron source

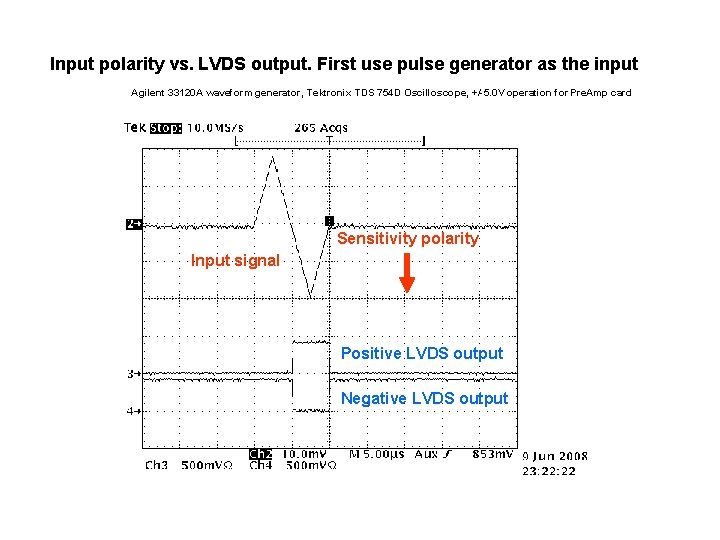

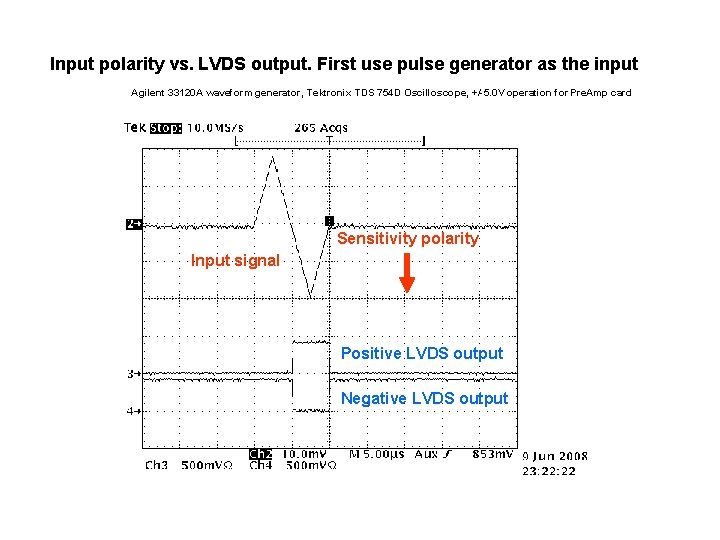

Input polarity vs. LVDS output. First use pulse generator as the input Agilent 33120 A waveform generator, Tektronix TDS 754 D Oscilloscope, +/-5. 0 V operation for Pre. Amp card Sensitivity polarity Input signal Positive LVDS output Negative LVDS output

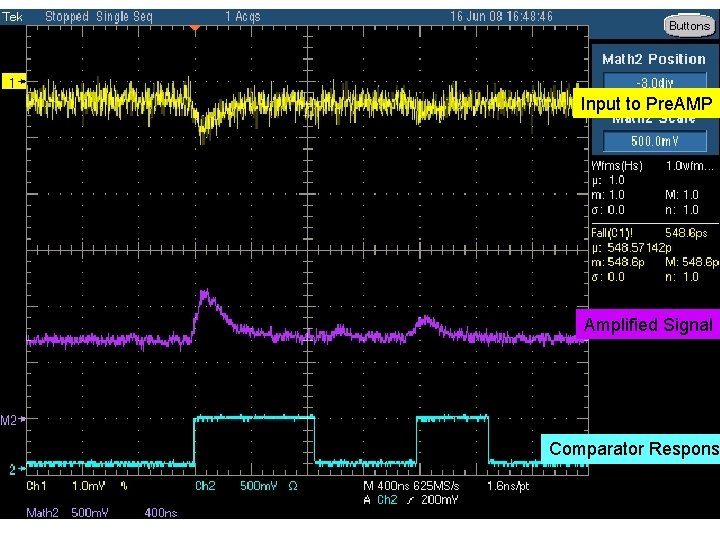

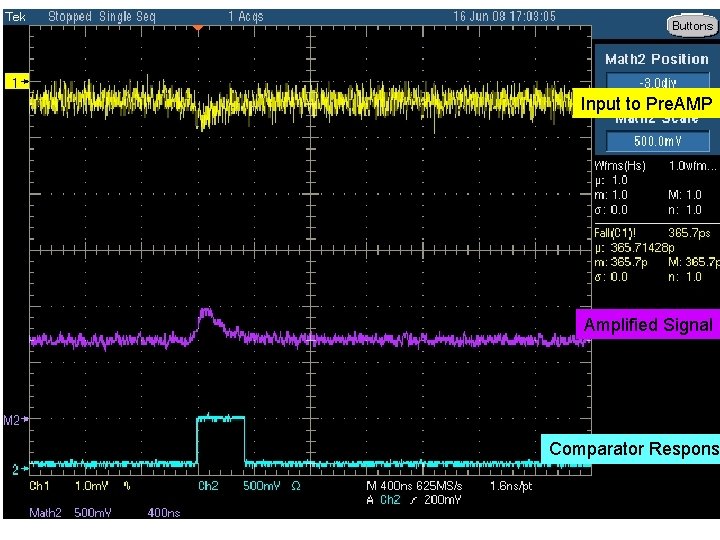

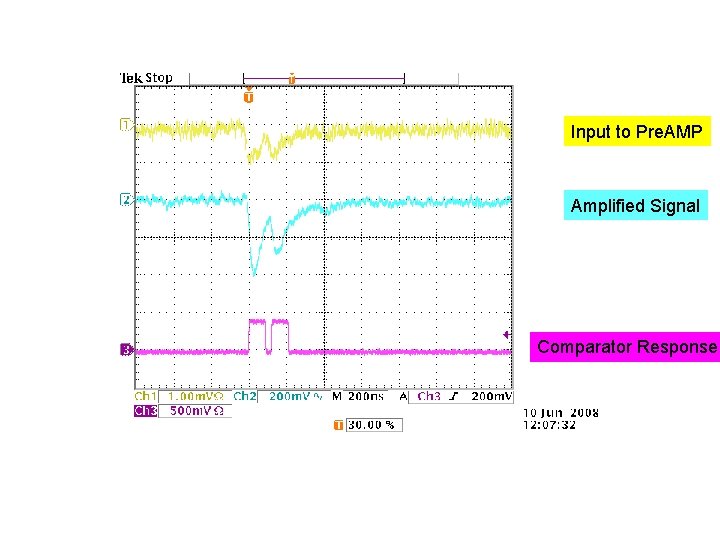

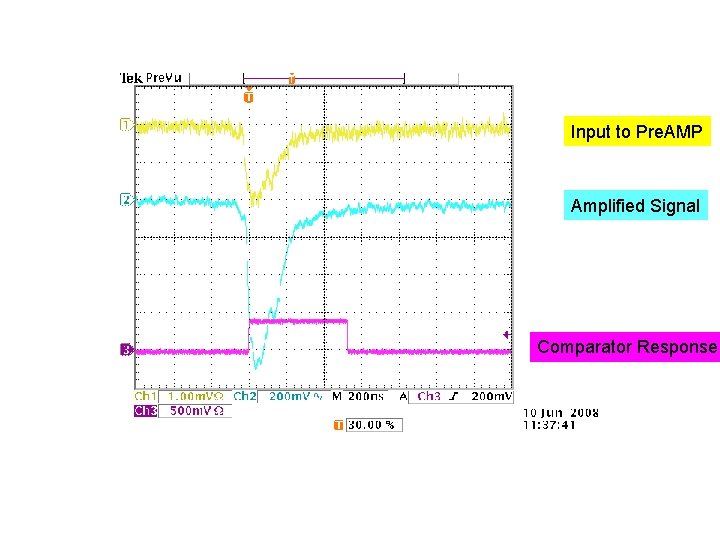

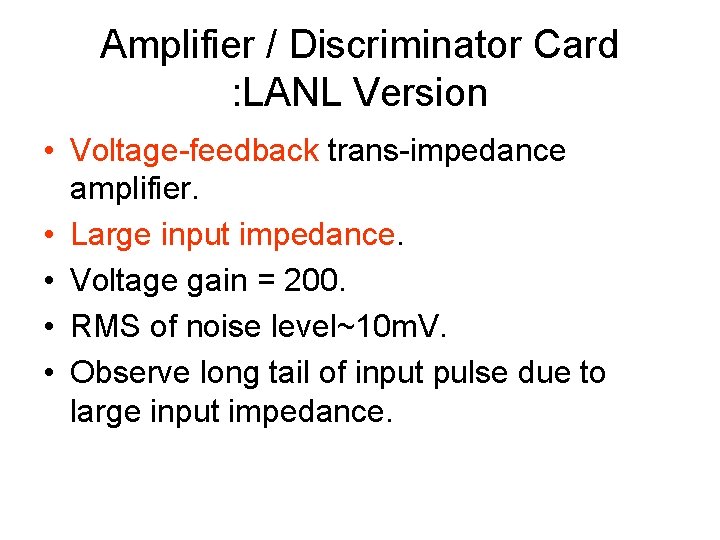

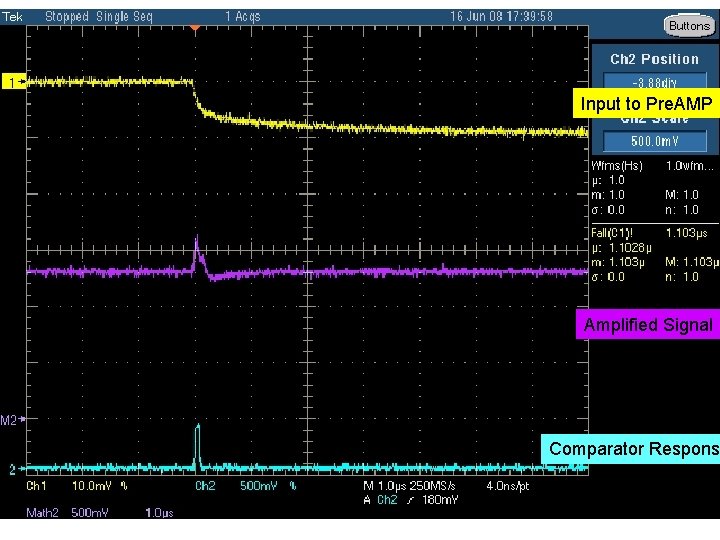

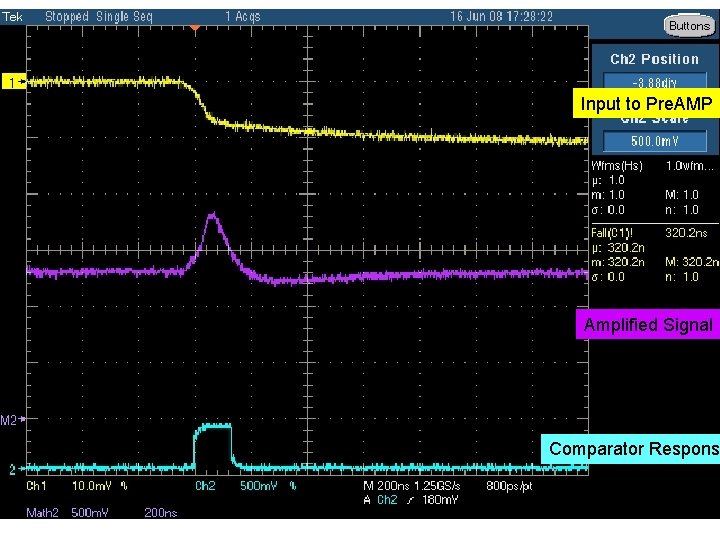

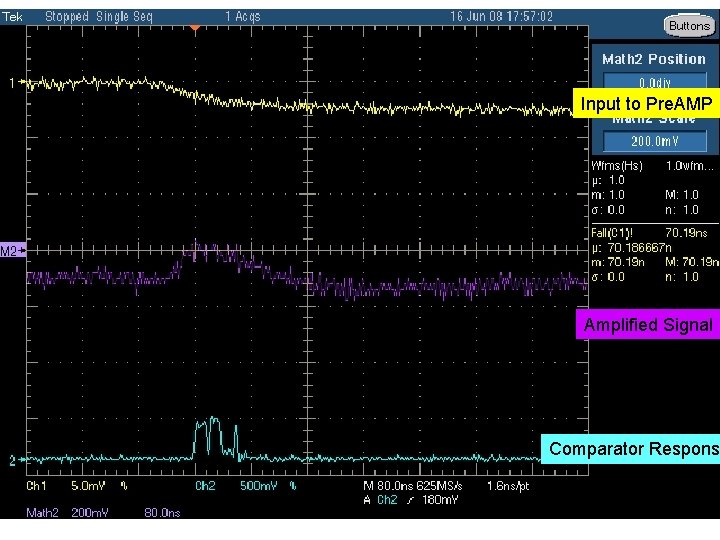

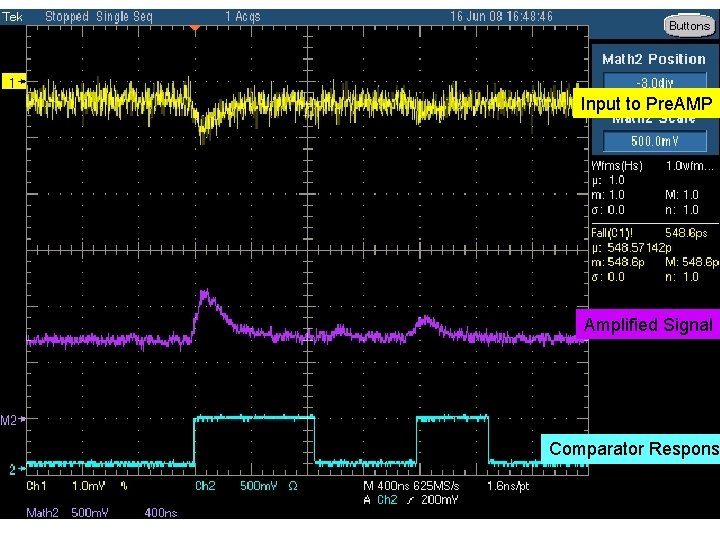

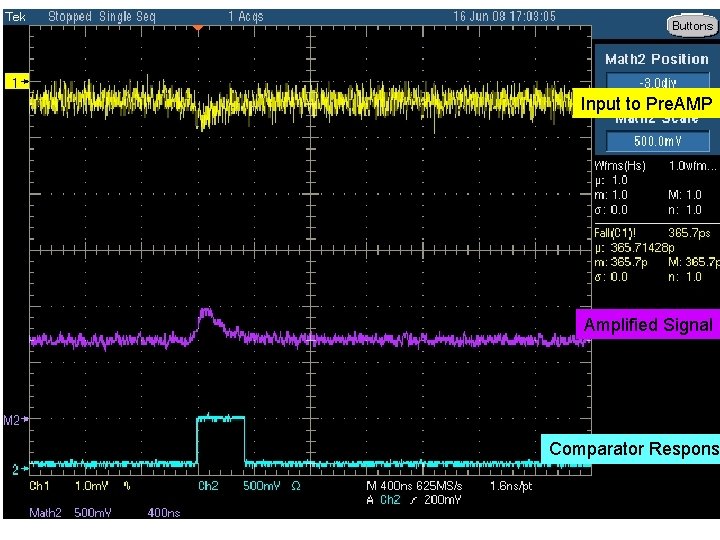

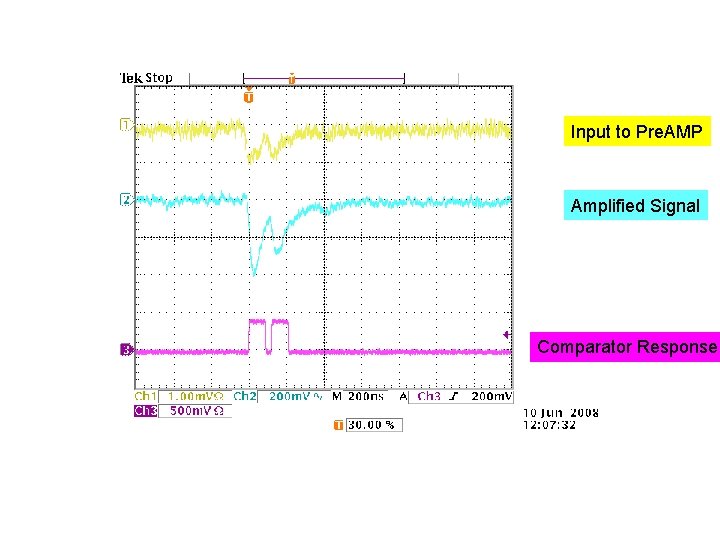

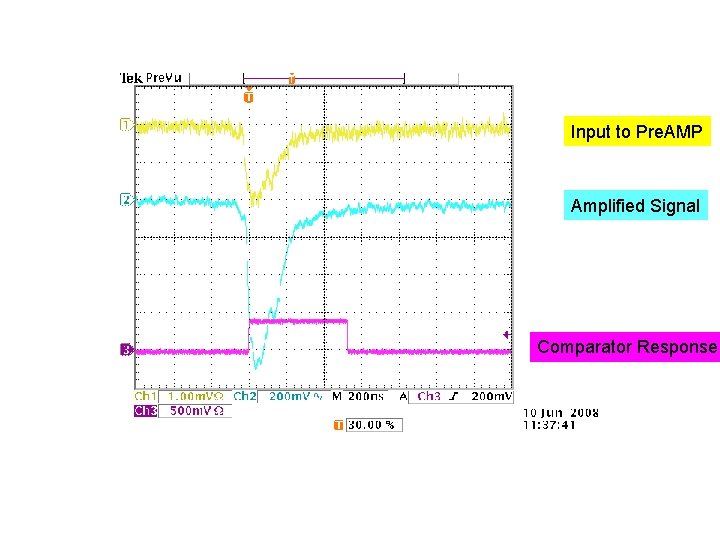

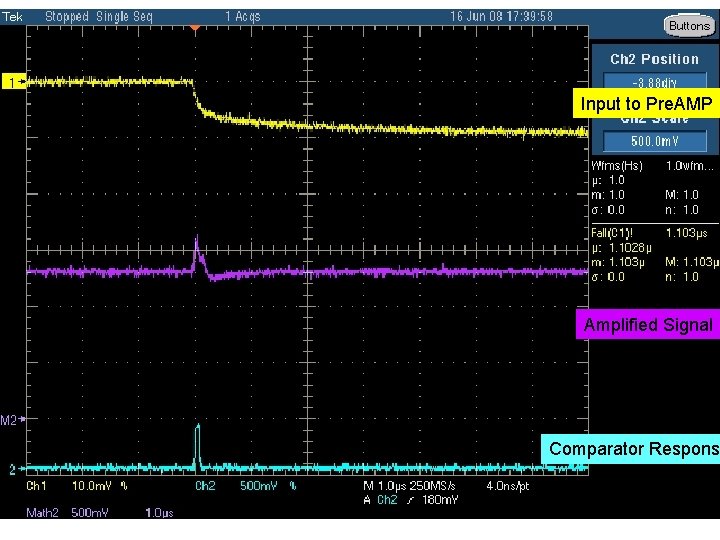

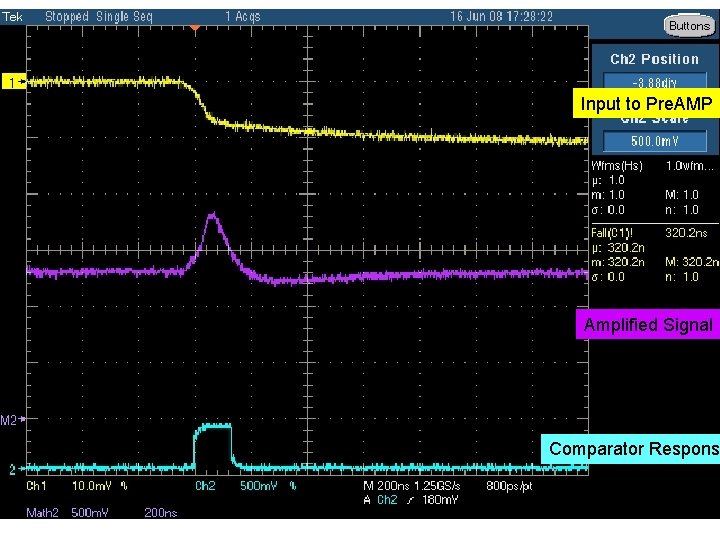

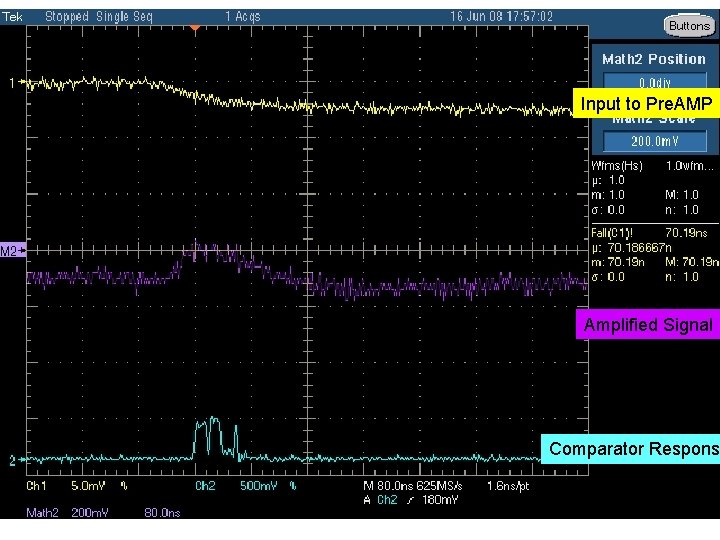

Input to Pre. AMP Amplified Signal Comparator Response

Input to Pre. AMP Amplified Signal Comparator Response

Input to Pre. AMP Amplified Signal Comparator Response

Input to Pre. AMP Amplified Signal Comparator Response

Input to Pre. AMP Amplified Signal Comparator Response

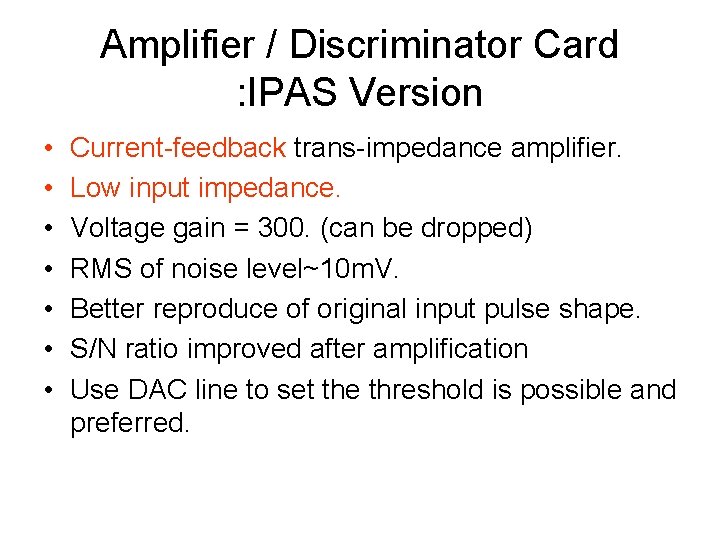

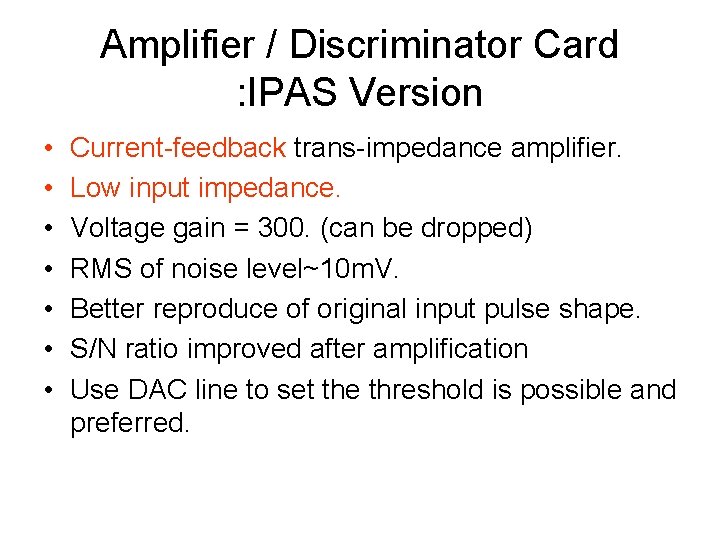

Amplifier / Discriminator Card : IPAS Version • • Current-feedback trans-impedance amplifier. Low input impedance. Voltage gain = 300. (can be dropped) RMS of noise level~10 m. V. Better reproduce of original input pulse shape. S/N ratio improved after amplification Use DAC line to set the threshold is possible and preferred.

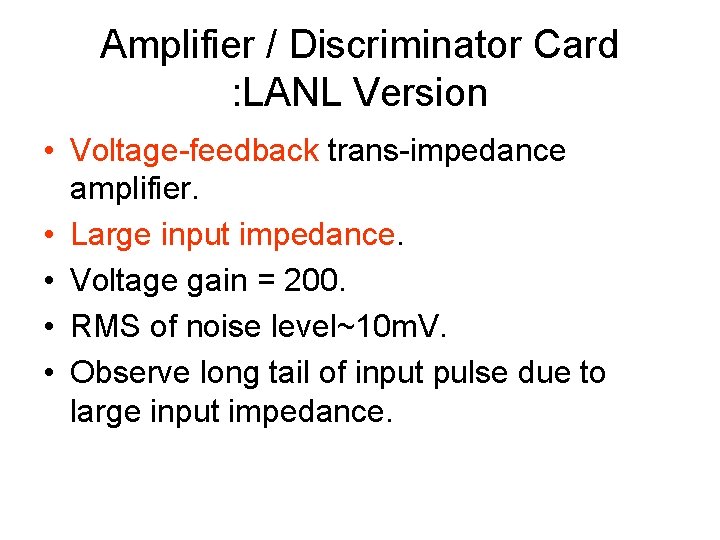

Amplifier / Discriminator Card : LANL Version • Voltage-feedback trans-impedance amplifier. • Large input impedance. • Voltage gain = 200. • RMS of noise level~10 m. V. • Observe long tail of input pulse due to large input impedance.

Input to Pre. AMP Amplified Signal Comparator Response

Input to Pre. AMP Amplified Signal Comparator Response

Input to Pre. AMP Amplified Signal Comparator Response

Questions to be answered • The R-C configuration on the detector side: How to interface between preamp and chamber? • Chamber geometry (pin output arrangement) • Latch frequency: 53 MHz? • Voltage gain appropriate? • Threshold of comparator: 0 -150 m. V (enough? ) • Noise level during the run? • Maximum pulse width from MWPC? (signal tail pile up) • Q: Get power from chamber? Separate power supply?

Two possible schemes of pre. Amp -Latch-CR readout system 1. MWPC— 2 pre. Amp cards— 1 Latch. CR VME module—VME Buffered Encoder—VME Event Buffer Interface 2. MWPC— 4 pre. Amp cards— 1 Latch. CR Card—VME Event Encoder/Buffer

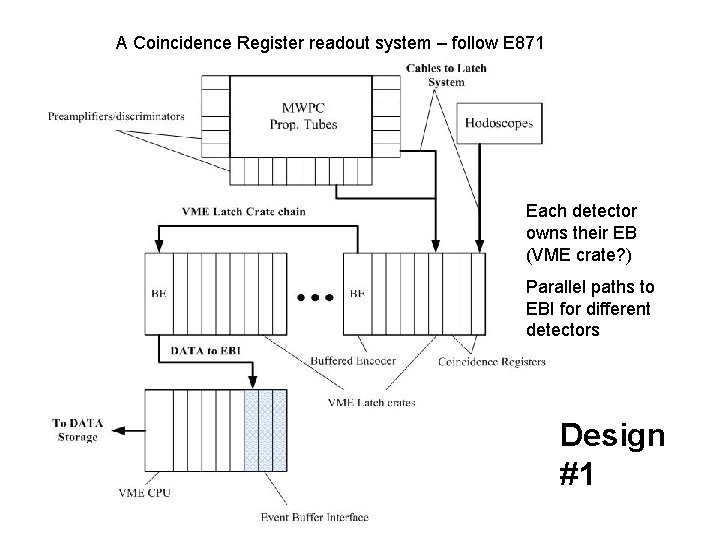

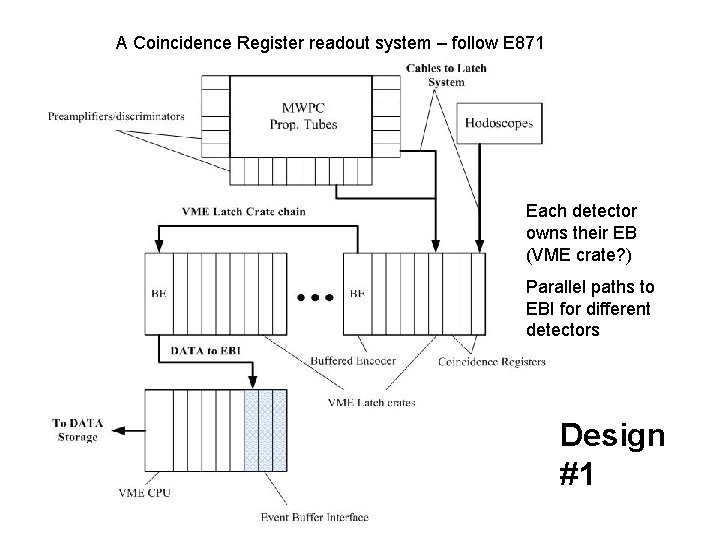

A Coincidence Register readout system – follow E 871 Each detector owns their EB (VME crate? ) Parallel paths to EBI for different detectors Design #1

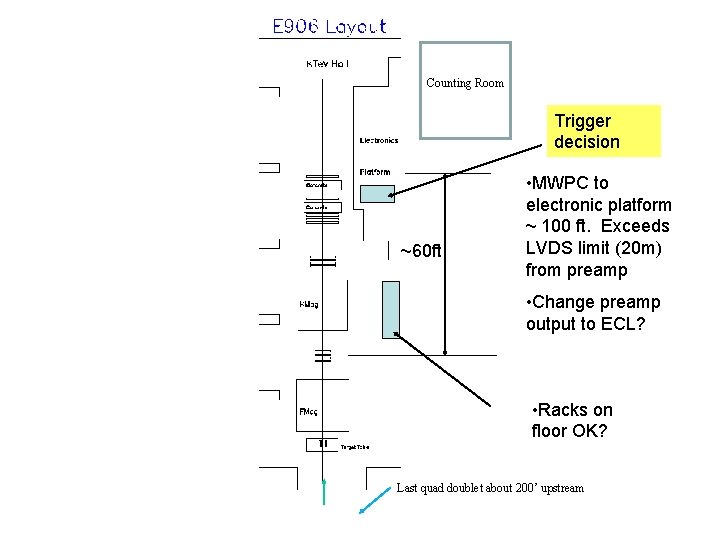

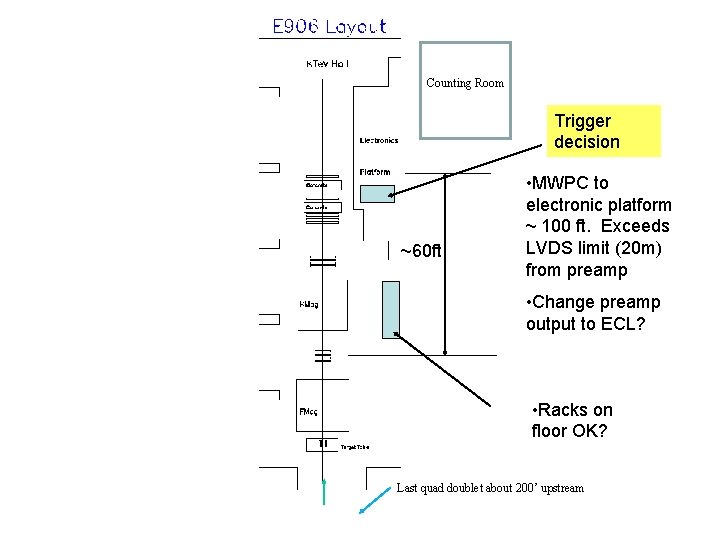

Counting Room Trigger decision ~60 ft • MWPC to electronic platform ~ 100 ft. Exceeds LVDS limit (20 m) from preamp • Change preamp output to ECL? • Racks on floor OK? Last quad doublet about 200’ upstream

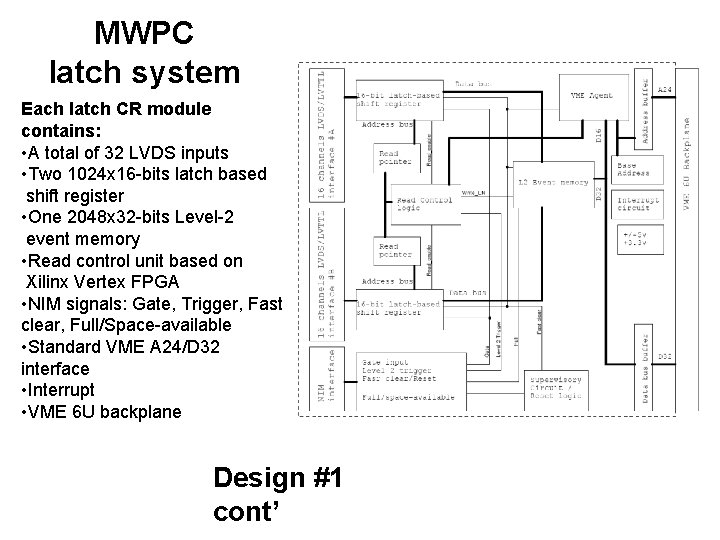

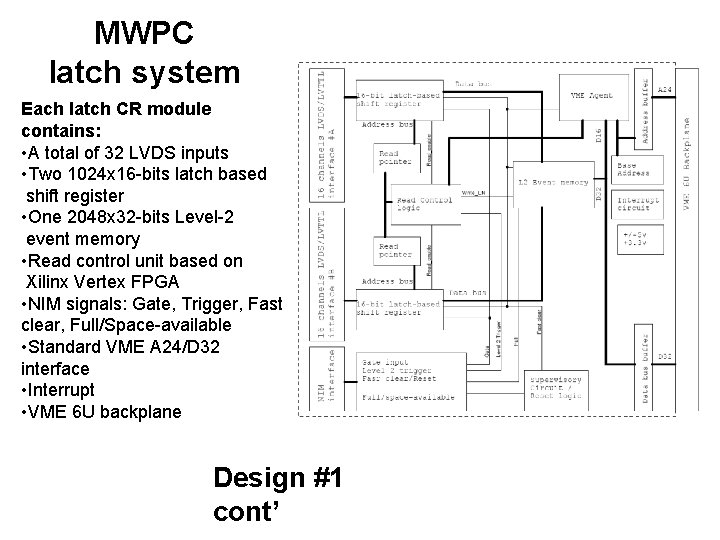

MWPC latch system Each latch CR module contains: • A total of 32 LVDS inputs • Two 1024 x 16 -bits latch based shift register • One 2048 x 32 -bits Level-2 event memory • Read control unit based on Xilinx Vertex FPGA • NIM signals: Gate, Trigger, Fast clear, Full/Space-available • Standard VME A 24/D 32 interface • Interrupt • VME 6 U backplane Design #1 cont’ Figure 1

Design #1 • Data from Pre. Amp sent to Latch-CR where the state of each channel is latched with RF clock. • Data are collected to EB then to EBI at L 1 trigger with data reduction. If L 2 does not occur, clear EBI. • Data in EBI sent out to DAQ at L 2 trigger • Delay of digital signals in FPGA and comparator threshold in Pre. Amp can be remotely adjusted via VME CPU.

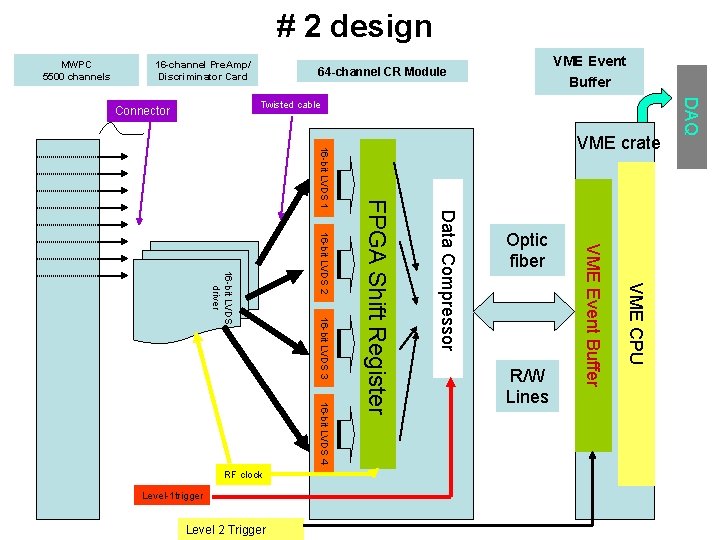

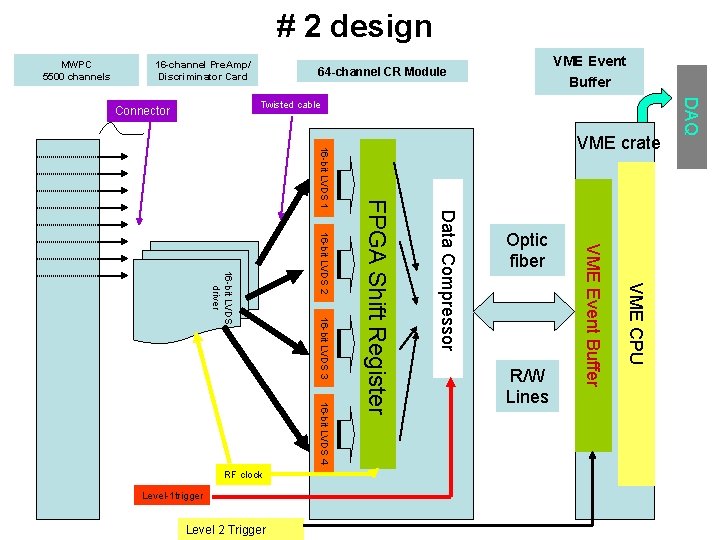

# 2 design MWPC 5500 channels 16 -channel Pre. Amp/ Discriminator Card VME Event Buffer 64 -channel CR Module Optic fiber VME CPU 16 -bit LVDS 4 R/W Lines VME Event Buffer 16 -bit LVDS 3 Level 2 Trigger Data Compressor 16 -bit LVDS 2 Level-1 trigger FPGA Shift Register 16 -bit LVDS 1 16 -bit LVDS driver RF clock VME crate DAQ Twisted cable Connector

Design #2 • CR card: – Sits next to Pre. Amp card and retrieves power from MWPC via LVDS cable connection from Pre. Amp. – Data clocked into shift registers at RF freq. – With L 1 trigger enabled, perform data encoding, and at L 2 trigger send data to VME Event Buffer board. – Uses 1 optic fiber for R/W communication with VME Event Buffer board. – Data transfer rate of optic fiber: 1. 25 Gbps ~ 4. 25 Gbps • Event Buffer board: – Each EB connects with 16 optic fibers. – Data readout from EB to DAQ at L 2 trigger after data is collected from 16 CR cards.

Questions to be answered for #2 • Distance from spectrometer to electronics? • Radiation damage? • L 1 & L 2 trigger rate? (Is 1 optic fiber enough? )

Information & Estimation • Main Injector RF clock frequency: 53 MHz. • Beam structure: 10^13 protons in a 5 s slow extraction spill every minute. Beam intensity: 2*10^12/sec. • 200 triggers/per spill; 1 k. Hz trigger rate aimed for DAQ. (? ? ) • Level-2 trigger latency: Master Trigger OR decision time= 91 ns. • Level-1 trigger rate (X): – MWPC designed Singles rates: 53 MHz. (? ) – The total rate of single muons traversing the detector and passing the trigger matrix tracking will be approximately 100 k. Hz with the LH 2 target and 150 k. Hz with the LD 2 target (both cases include tracks originating in the beam dump). • LVDS clock: minimum 200 MHz. • How many 16 -channel preamp cards which one latched module can deal with: (16 bit*200 MHz)/ (16 bit*53 MHz)~4. • Event size of MWPC W/O data reduction: 5500 bit=0. 8 k. B • Depth of memory buffer: 53 MHz*91 ns~ 5 events. Size of total memory to buffer 5 events=0. 8 k. B*5=4 k. B. • VME transfer throughput: 0. 8 k. B*1 k. Hz=0. 8 MB/per sec << Optic fiber ~100 MB/sec and VME 160 MB/sec. Deadtime-free is possible.

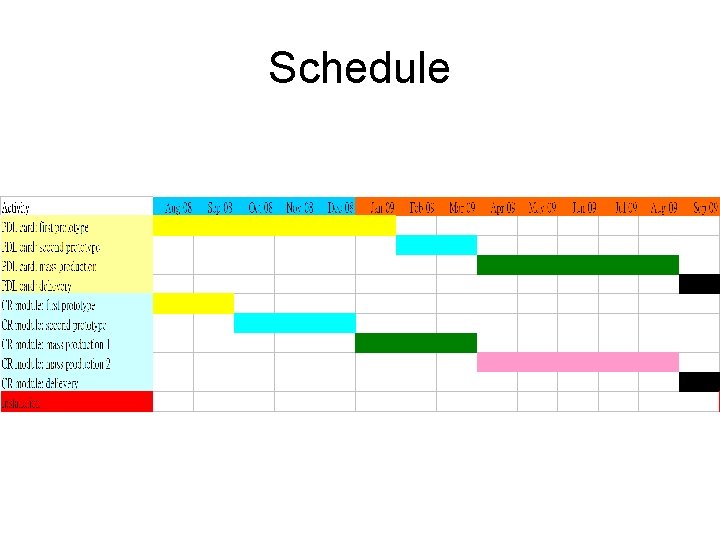

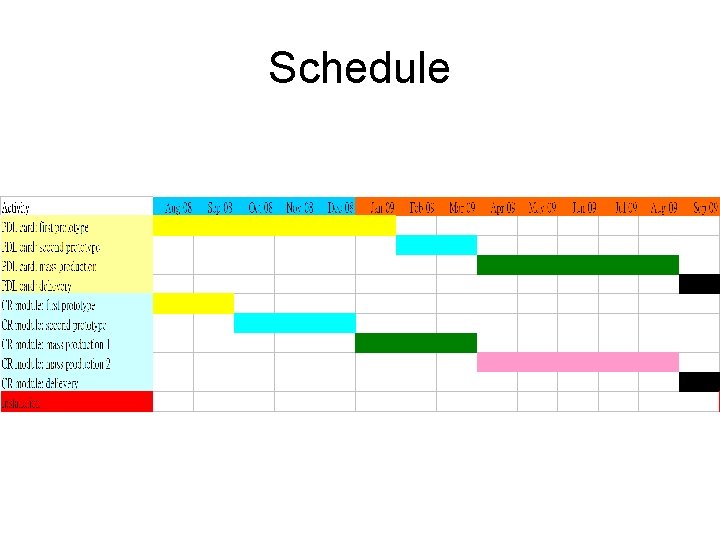

Schedule for building PD cards All R&D and testing work would be done in IPAS electronics lab. • Aug 2008 - Jan 2009 – R&D PD card prototype. First few PD prototype cards produced. Test gain, rising time and invest noise pick up. • Jan 2009 – Mar 2009 – Send prototype cards to US collaborator to test with MWPC chamber. Finalize prototype design. • Mar – Aug 2009 – Mass production. Manufacture the rest (~350) cards. Testing. • Aug – Sept 2009 -- All cards shipped to Fermilab for final integration.

Schedule for building CR modules • Aug - Sept 2008 – R&D CR module prototype. First 2 CR prototype modules produced. Develop readout software for multi-boards. • Sept – Dec 2008 – Set up testing environment with a simple DAQ system. Trigger rate will mimic the running condition. Finish testing first set of prototype boards. Finalize prototype design. • Jan – Mar 2009 – Manufacture first 20 boards, test serial/parallel multicrates readout, test throughputs and event formatting, developing readout software for multi-crates. Set up a DAQ system using JLab CODA in local lab. • Mar – Aug 2009 – Mass production. Manufacture the rest (~ 160) boards. Full system test completed. • Aug – Sept 2009 -- All modules and crates shipped to Fermilab for final integration. • Sept 2009 – Feb 2010 – Crew on site. Install CR modules and PD cards to MWPC. Preparation for the experiment. • Mar 2010 –Scheduled start of E 906 data taking? The Ph. D student and Yen -Chu Chen will stay in Fermilab full time.

Schedule

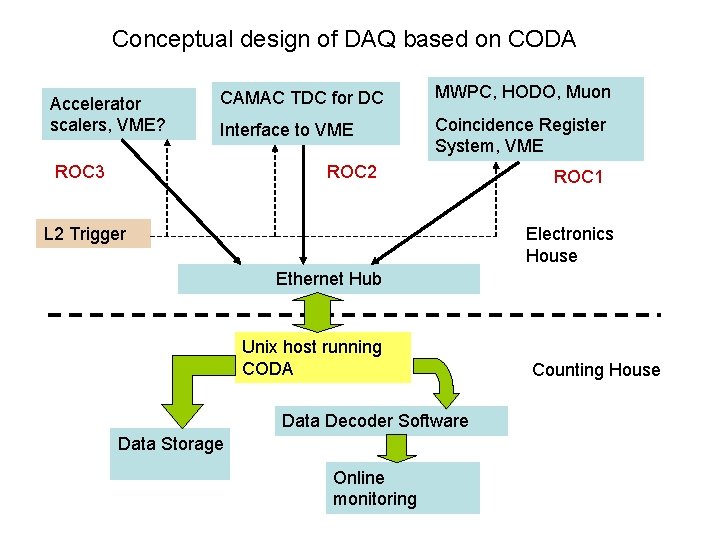

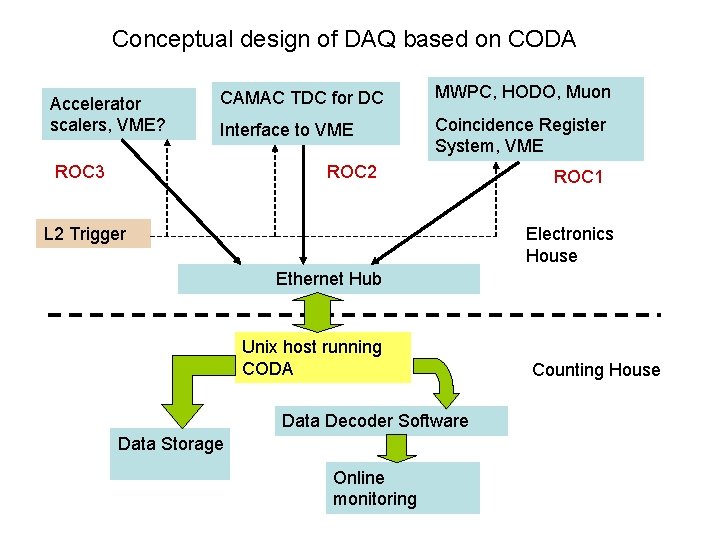

Conceptual design of DAQ based on CODA Accelerator scalers, VME? CAMAC TDC for DC MWPC, HODO, Muon Interface to VME Coincidence Register System, VME ROC 3 ROC 2 L 2 Trigger ROC 1 Electronics House Ethernet Hub Unix host running CODA Data Decoder Software Data Storage Online monitoring Counting House

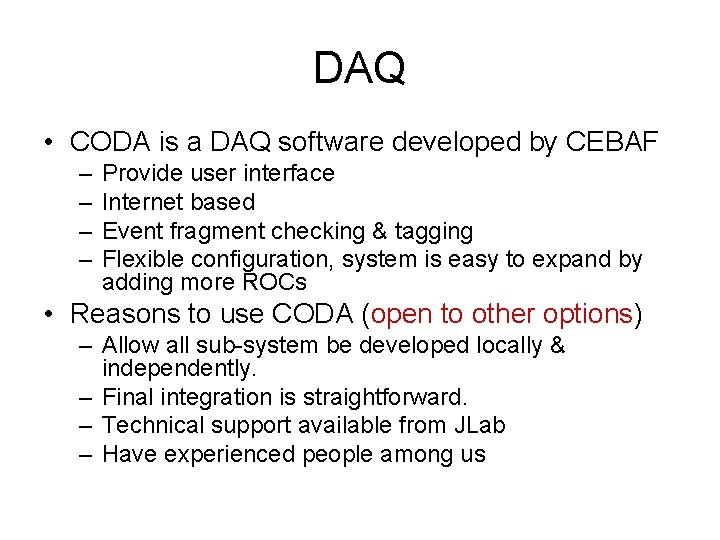

DAQ • CODA is a DAQ software developed by CEBAF – – Provide user interface Internet based Event fragment checking & tagging Flexible configuration, system is easy to expand by adding more ROCs • Reasons to use CODA (open to other options) – Allow all sub-system be developed locally & independently. – Final integration is straightforward. – Technical support available from JLab – Have experienced people among us

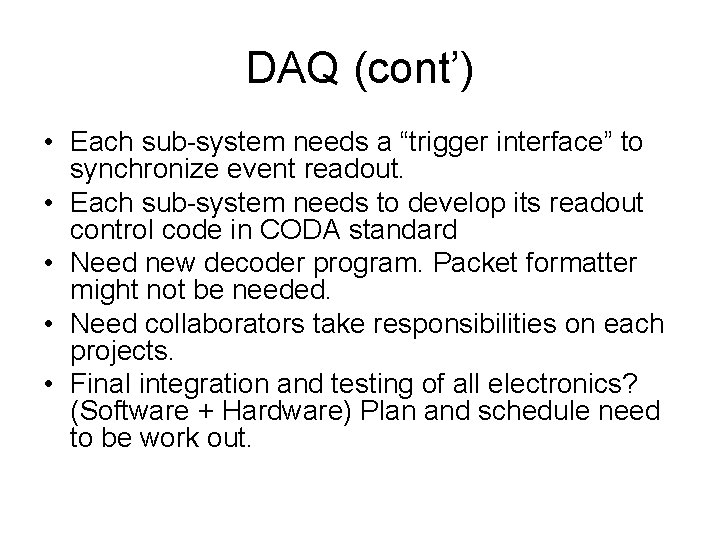

DAQ (cont’) • Each sub-system needs a “trigger interface” to synchronize event readout. • Each sub-system needs to develop its readout control code in CODA standard • Need new decoder program. Packet formatter might not be needed. • Need collaborators take responsibilities on each projects. • Final integration and testing of all electronics? (Software + Hardware) Plan and schedule need to be work out.