The Super B Silicon Vertex Tracker Giuliana Rizzo

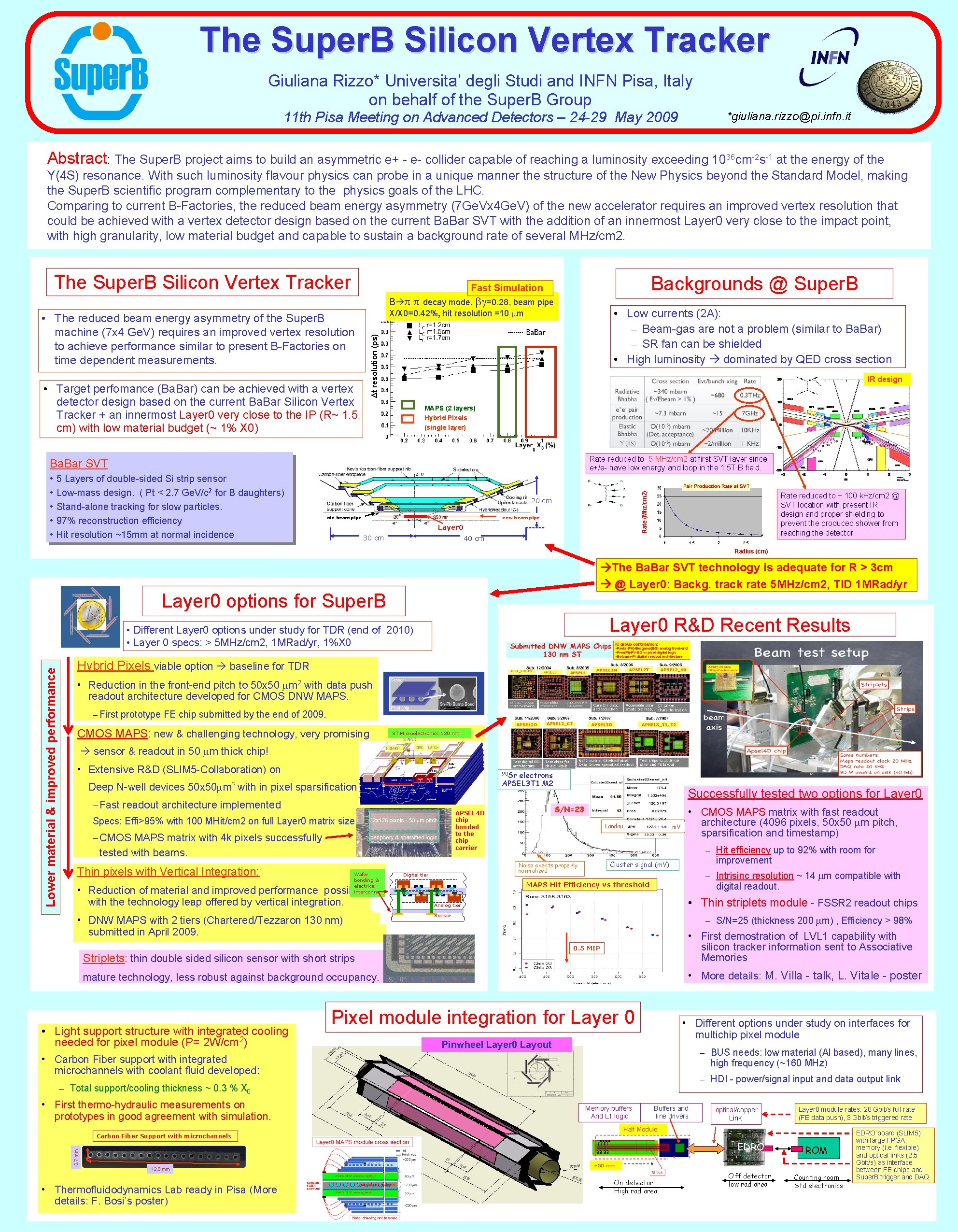

The Super. B Silicon Vertex Tracker Giuliana Rizzo* Universita’ degli Studi and INFN Pisa, Italy on behalf of the Super. B Group 11 th Pisa Meeting on Advanced Detectors – 24 -29 May 2009 *giuliana. rizzo@pi. infn. it . Abstract: The Super. B project aims to build an asymmetric e+ - e- collider capable of reaching a luminosity exceeding 1036 cm-2 s-1 at the energy of the Y(4 S) resonance. With such luminosity flavour physics can probe in a unique manner the structure of the New Physics beyond the Standard Model, making the Super. B scientific program complementary to the physics goals of the LHC. Comparing to current B-Factories, the reduced beam energy asymmetry (7 Ge. Vx 4 Ge. V) of the new accelerator requires an improved vertex resolution that could be achieved with a vertex detector design based on the current Ba. Bar SVT with the addition of an innermost Layer 0 very close to the impact point, with high granularity, low material budget and capable to sustain a background rate of several MHz/cm 2. The Super. B Silicon Vertex Tracker Backgrounds @ Super. B Fast Simulation B p p decay mode, bg=0. 28, beam pipe • Low currents (2 A): – Beam-gas are not a problem (similar to Ba. Bar) – SR fan can be shielded • High luminosity dominated by QED cross section X/X 0=0. 42%, hit resolution =10 mm Dt resolution (ps) • The reduced beam energy asymmetry of the Super. B machine (7 x 4 Ge. V) requires an improved vertex resolution to achieve performance similar to present B-Factories on time dependent measurements. • Target perfomance (Ba. Bar) can be achieved with a vertex detector design based on the current Ba. Bar Silicon Vertex Tracker + an innermost Layer 0 very close to the IP (R~ 1. 5 cm) with low material budget (~ 1% X 0) IR design MAPS (2 layers) Hybrid Pixels (single layer) Rate reduced to 5 MHz/cm 2 at first SVT layer since e+/e- have low energy and loop in the 1. 5 T B field. • • • 5 Layers of double-sided Si strip sensor Low-mass design. ( Pt < 2. 7 Ge. V/c 2 for B daughters) Stand-alone tracking for slow particles. 97% reconstruction efficiency Hit resolution ~15 mm at normal incidence Rate (Mhz/cm 2) Ba. Bar SVT 20 cm old beam pipe new beam pipe Layer 0 30 cm Rate reduced to ~ 100 k. Hz/cm 2 @ SVT location with present IR design and proper shielding to prevent the produced shower from reaching the detector 40 cm Radius (cm) The Ba. Bar SVT technology is adequate for R > 3 cm @ Layer 0: Backg. track rate 5 MHz/cm 2, TID 1 MRad/yr Layer 0 options for Super. B Layer 0 R&D Recent Results Lower material & improved performance • Different Layer 0 options under study for TDR (end of 2010) • Layer 0 specs: > 5 MHz/cm 2, 1 MRad/yr, 1%X 0 Hybrid Pixels viable option baseline for TDR • Reduction in the front-end pitch to 50 x 50 mm 2 with data push readout architecture developed for CMOS DNW MAPS. – First prototype FE chip submitted by the end of 2009. CMOS MAPS: new & challenging technology, very promising ST Microelectronics 130 nm sensor & readout in 50 mm thick chip! • Extensive R&D (SLIM 5 -Collaboration) on 90 Sr electrons APSEL 3 T 1 M 2 Deep N-well devices 50 x 50 mm 2 with in pixel sparsification. – Fast readout architecture implemented – CMOS MAPS matrix with 4 k pixels successfully tested with beams. Thin pixels with Vertical Integration: Wafer bonding & electrical interconn. • Reduction of material and improved performance possible with the technology leap offered by vertical integration. • DNW MAPS with 2 tiers (Chartered/Tezzaron 130 nm) submitted in April 2009. S/N=23 APSEL 4 D chip bonded to the chip carrier Specs: Effi>95% with 100 MHit/cm 2 on full Layer 0 matrix size Successfully tested two options for Layer 0 Landau – Intrisinc resolution ~ 14 mm compatible with digital readout. MAPS Hit Efficiency vs threshold • Thin striplets module - FSSR 2 readout chips Analog tier Sensor – S/N=25 (thickness 200 mm) , Efficiency > 98% • First demostration of LVL 1 capability with silicon tracker information sent to Associative Memories 0. 5 MIP Striplets: thin double sided silicon sensor with short strips • More details: M. Villa - talk, L. Vitale - poster mature technology, less robust against background occupancy. • Light support structure with integrated cooling needed for pixel module (P= 2 W/cm 2) – Hit efficiency up to 92% with room for improvement Cluster signal (m. V) Noise events properly normalized Digital tier m. V • CMOS MAPS matrix with fast readout architecture (4096 pixels, 50 x 50 mm pitch, sparsification and timestamp) Pixel module integration for Layer 0 • Different options under study on interfaces for multichip pixel module Pinwheel Layer 0 Layout – BUS needs: low material (Al based), many lines, high frequency (~160 MHz) • Carbon Fiber support with integrated microchannels with coolant fluid developed: – HDI - power/signal input and data output link – Total support/cooling thickness ~ 0. 3 % X 0 • First thermo-hydraulic measurements on prototypes in good agreement with simulation. Memory buffers And L 1 logic Buffers and line drivers optical/copper Link Half Module Carbon Fiber Support with microchannels 0. 7 mm EDRO 12. 8 mm • Thermofluidodynamics Lab ready in Pisa (More details: F. Bosi’s poster) Layer 0 module rates: 20 Gbit/s full rate (FE data push), 3 Gbit/s triggered rate ROM ~50 mm On detector High rad area Off detector low rad area Counting room Std electronics EDRO board (SLIM 5) with large FPGA, memory (i. e. flexible) and optical links (2. 5 Gbit/s) as interface between FE chips and Super. B trigger and DAQ

- Slides: 1