The R 10000 Microprocessor A Presentation by Dennis

The R 10000 Microprocessor A Presentation by Dennis Konz, Birger Nahs, Klaus Wagner & Sibbi Wormser

Outline • Introduction of the Team Members • Short Historic Treatise • Basic Features of the R 10000 • Registers • Instruction Set • Addressing Modes • Speed • Factors Affecting Performance • Silicon Graphics‘s Onyx 2 • Perspective in the Marketplace

Short Historic Treatise 1981 1984 1996 * College professor James Clark found Silicon Graphics, Incorporated. * MIPS Computer Systems is founded, and begins developing its RISC architecture. * MIPS Technologies announces the R 10000 RISC microprocessor. * Silicon Graphics introduces Infinite. Reality, a workstation based on the MIPS Technologies R 10000 microprocessor. * MIPS Technologies ships the 200 -MHz R 10000 RISC microprocessor

Basic Features of the R 10000 (1) • 64 -bit MIPS IV instruction set architecture (ISA) • it can decode four instructions each pipeline cycle, appending them to one of three instruction queues • five execution pipelines are connected to separate internal integer and floating-point execution (or functional) units • dynamic instruction scheduling and out-of-order execution • RISC

Basic Features of the R 10000 (2) • separate on-chip 32 -Kbyte primary instruction and data caches • individually-optimized secondary cache and System interface ports • an internal controller for the external secondary cache • an internal System interface controller with multiprocessor support

Registers (1) • two 64 -bit-wide register files to store integer and floating-point values • each file contains 64 registers • The integer register file has seven read and three write ports • the floating-point register file has five read and three write ports

Registers (2) • Floating-Point General Registers (contains 64 physical 64 -bit registers) • Floating-Point Control Registers - Floating-Point Implementation and Revision Register - Floating-Point Status Register • Coprocessor Registers - Index Register -Random Register - Wired Register -. . .

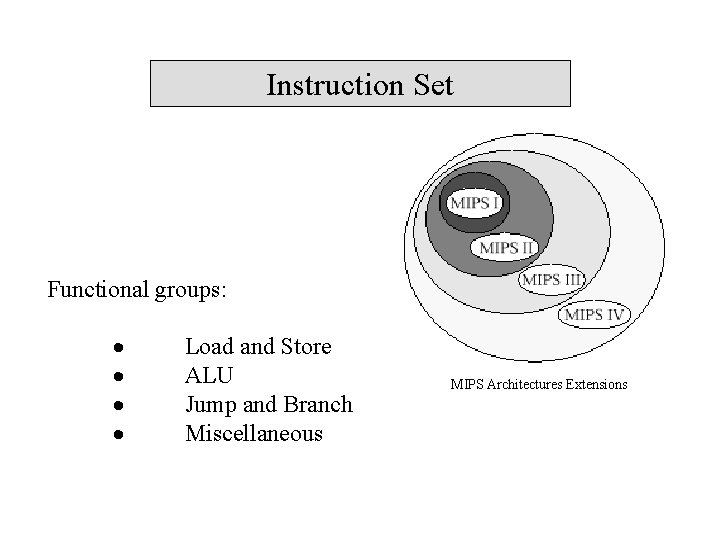

Instruction Set Functional groups: Load and Store ALU Jump and Branch Miscellaneous MIPS Architectures Extensions

Addressing Modes Depending on 3 different operating modes: Kernel mode - allows 64 -bit addressing and all instructions are valid Superwiser mode - allows 64 -bit addressing and MIPS III instructions - MIPS IV ISA is enabled all the time User mode - allows 64 -bit addressing, MIPS III instructions and the new MIPS IV instructions

Speed Internal clock rate of 195 MHz Peak performance of 390 Mflop/s 780 mips

Factors Affecting Performance MIPS ANDES Architecture (Non-sequential Dynamic Execution Scheduling) Most important factors - superscalar instruction issue - speculative execution - non blocking cache

Silicon Graphics‘s Onyx 2 In October 1998 the world's largest Onyx 2 visualization supercomputer has been installed at Argonne National Laboratory Configured with 128 processors and eight graphics pipes Provides up to 190 times the compute performance and 50 times the display capability available from today's highest performance personal computers Enables Scientists to use up to six CAVE virtual reality environments to study such diverse problems as climate modeling, combustion dynamics, and quantum chemistry.

Perspective in the Marketplace good stock market performance of MIPS Technology and Silicon Graphics While in 1996 MIPS already became the fastest growing RISC architecture exceeded Motorola’s 32 -bit 68000 CISC volume in 1997 For 1998 the R 12000 has been announced, but will surely not replace the R 10000 in foreseeable future

END Thanks for your attention!!!!!

- Slides: 14