The Quantum Switch 1 Introduction Preliminaries Switch Architecture

- Slides: 35

The Quantum Switch 1

• • • Introduction Preliminaries Switch Architecture and Control Design The analysis of complexities Future work 2

Introduction • Non-blocking • • ►For an N╳N switch these mappings are the N! permutations of the output address ►If an interconnection network can route all possible one-to-one input-output mappings ►For example, a Banyan network cannot route permutation maps 3

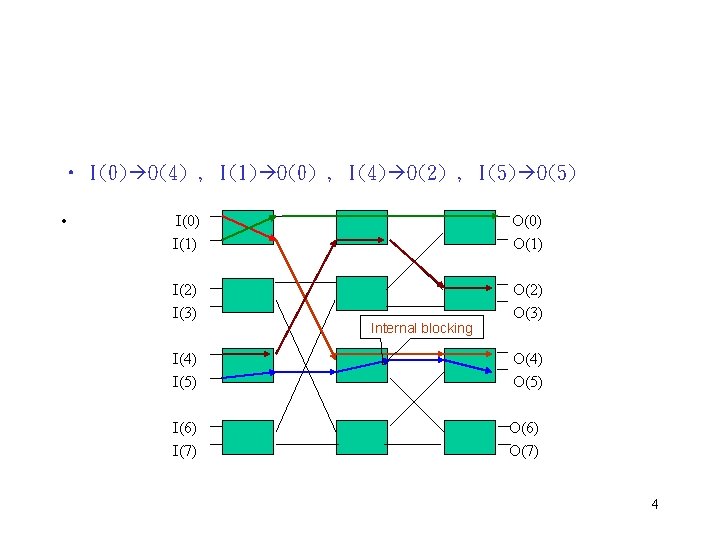

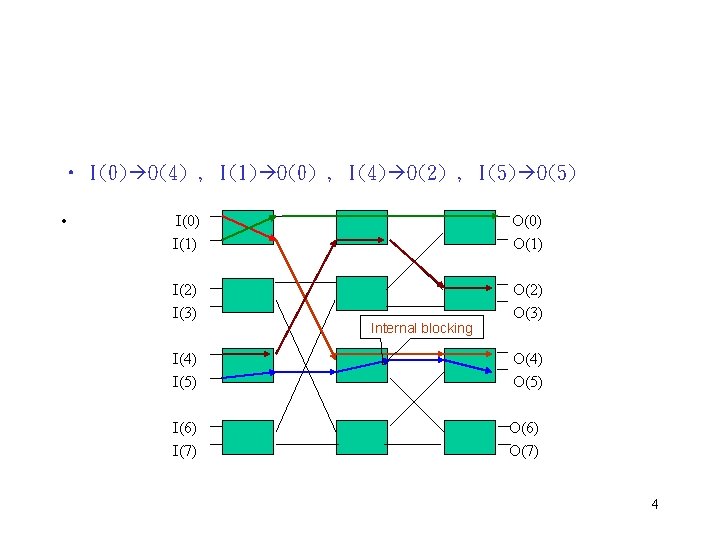

• I(0) O(4) , I(1) O(0) , I(4) O(2) , I(5) O(5) • I(0) I(1) O(0) O(1) I(2) I(3) O(2) O(3) Internal blocking I(4) I(5) O(4) O(5) I(6) I(7) O(6) O(7) 4

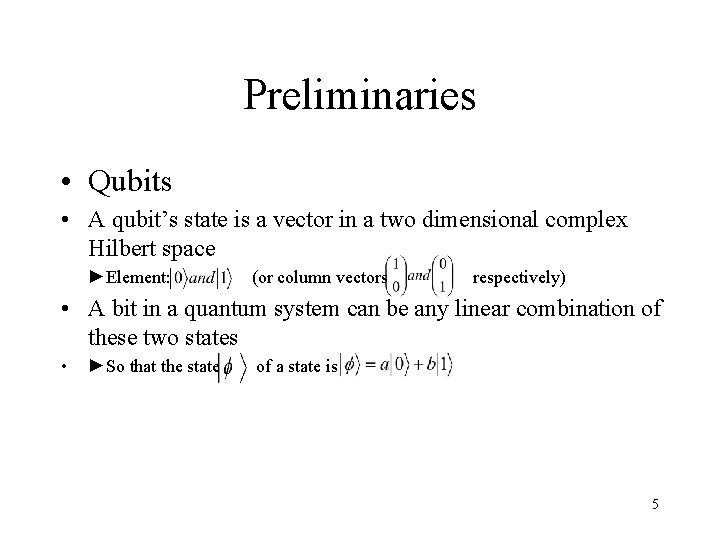

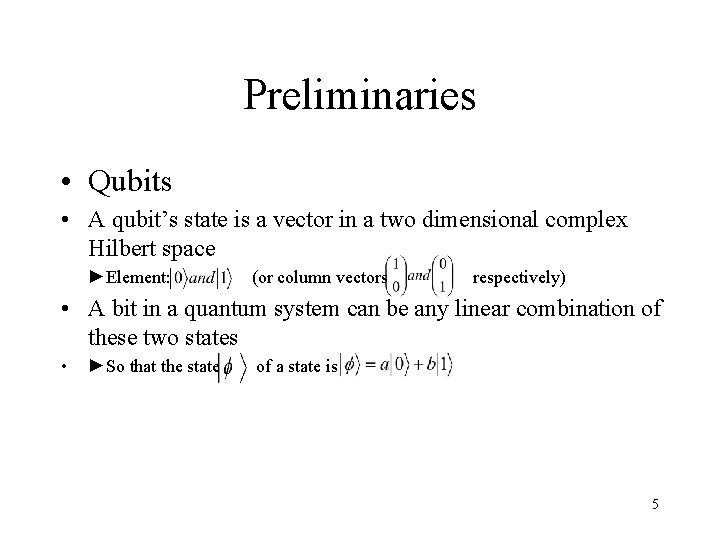

Preliminaries • Qubits • A qubit’s state is a vector in a two dimensional complex Hilbert space ►Element: (or column vectors respectively) • A bit in a quantum system can be any linear combination of these two states • ►So that the state of a state is 5

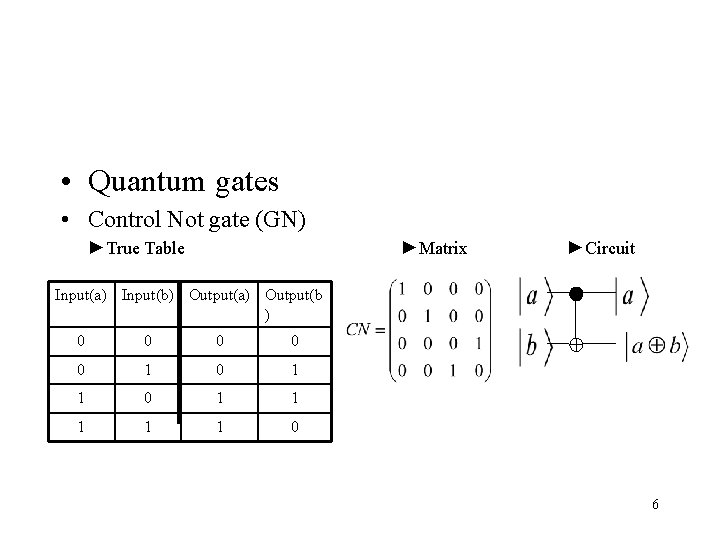

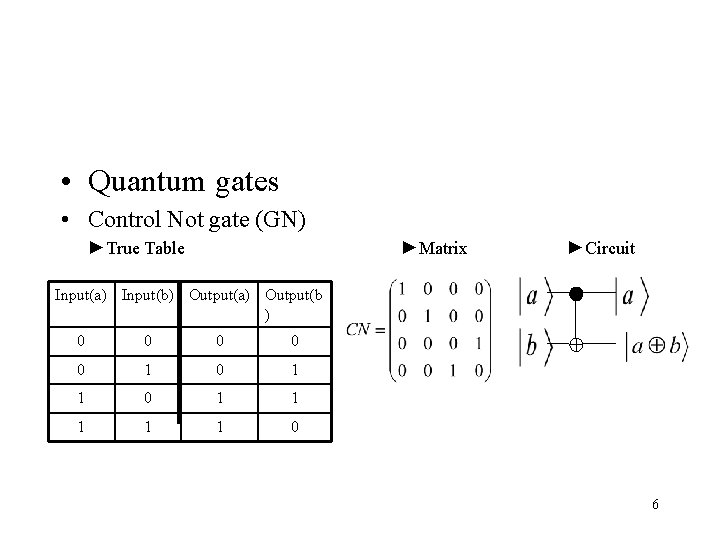

• Quantum gates • Control Not gate (GN) ►True Table ►Matrix ►Circuit Input(a) Input(b) Output(a) Output(b ) 0 0 0 1 1 1 0 6

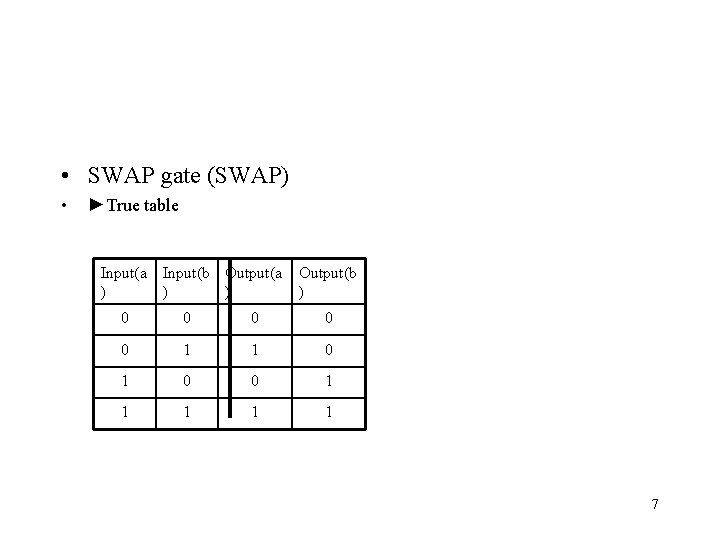

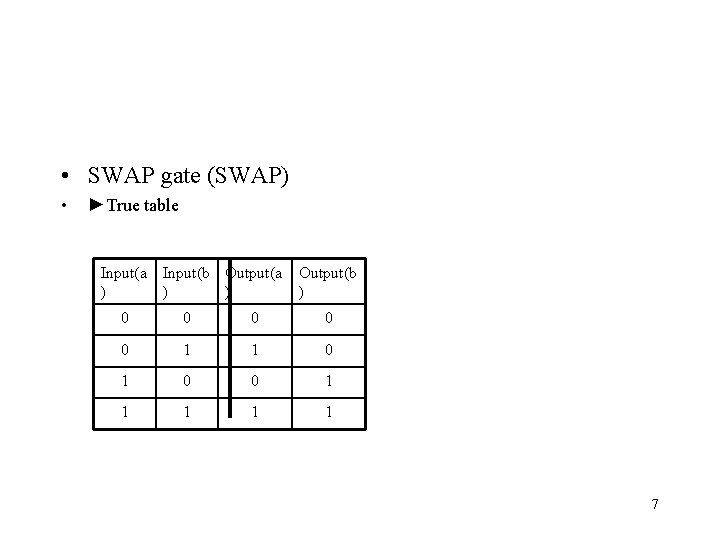

• SWAP gate (SWAP) • ►True table Input(a ) Input(b Output(a ) ) Output(b ) 0 0 0 1 1 1 7

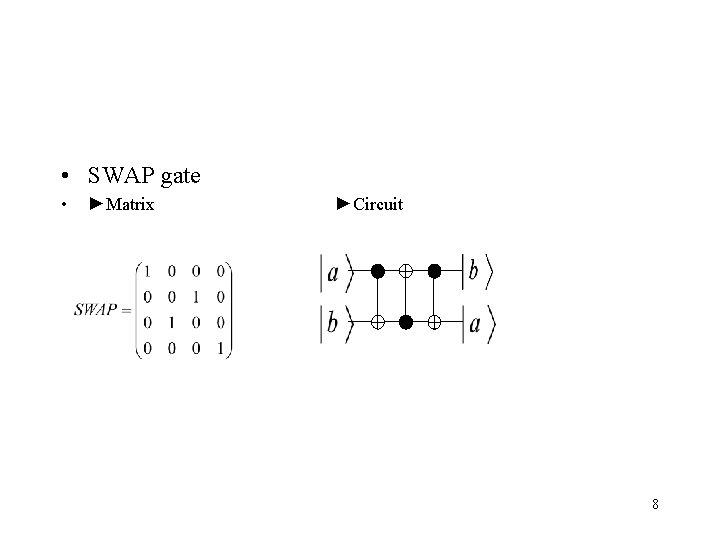

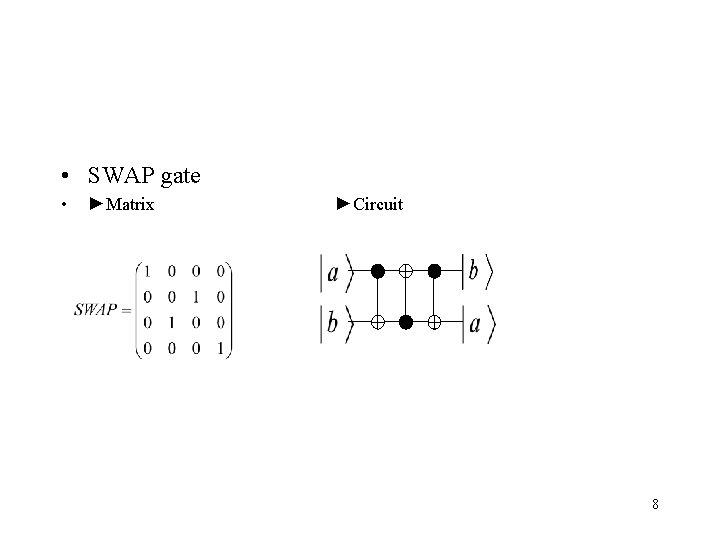

• SWAP gate • ►Matrix ►Circuit 8

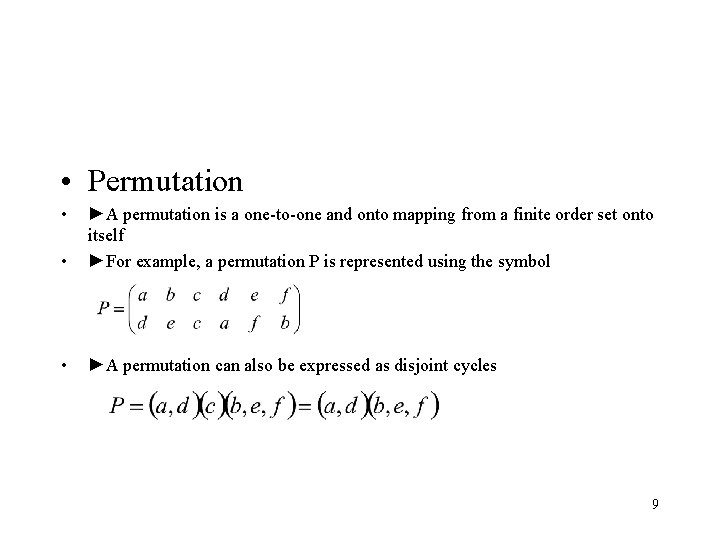

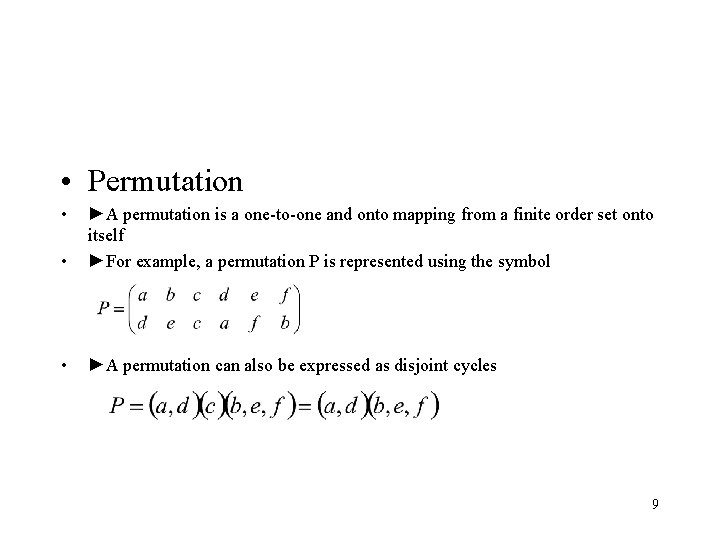

• Permutation • • ►A permutation is a one-to-one and onto mapping from a finite order set onto itself ►For example, a permutation P is represented using the symbol • ►A permutation can also be expressed as disjoint cycles 9

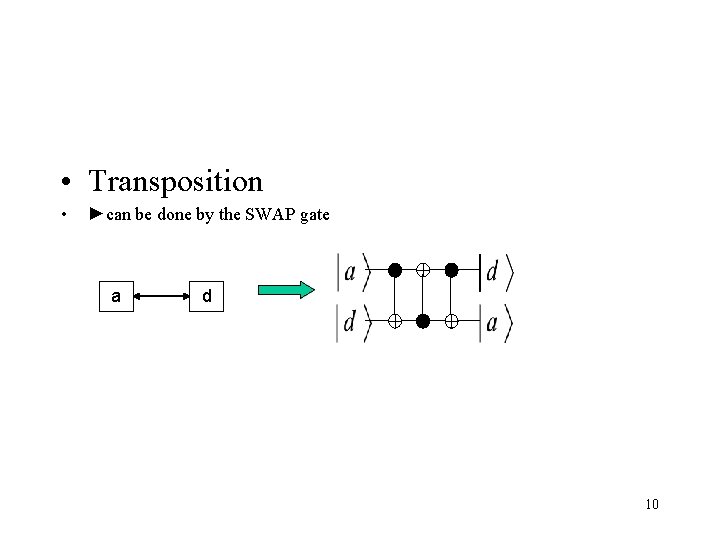

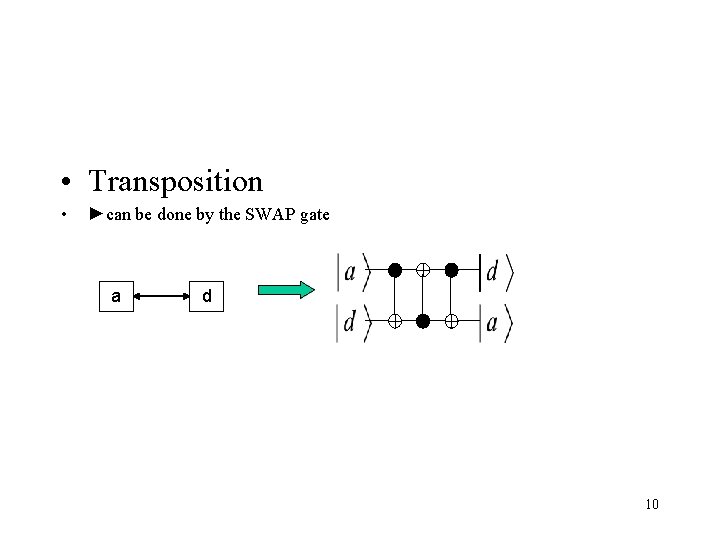

• Transposition • ►can be done by the SWAP gate a d 10

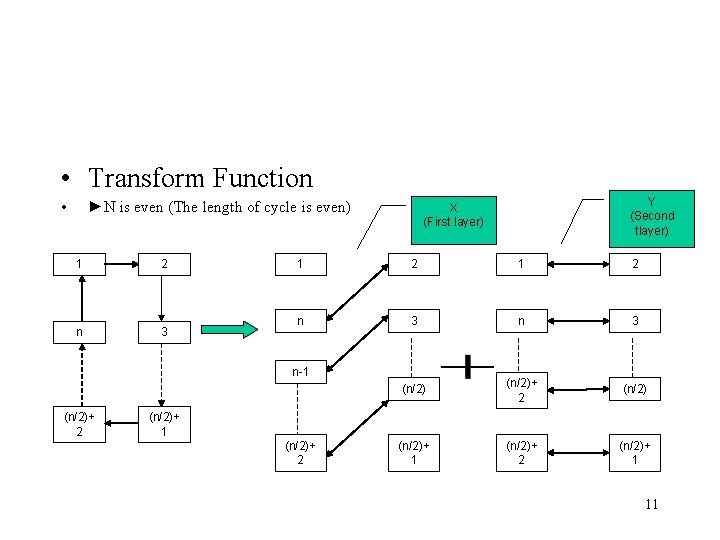

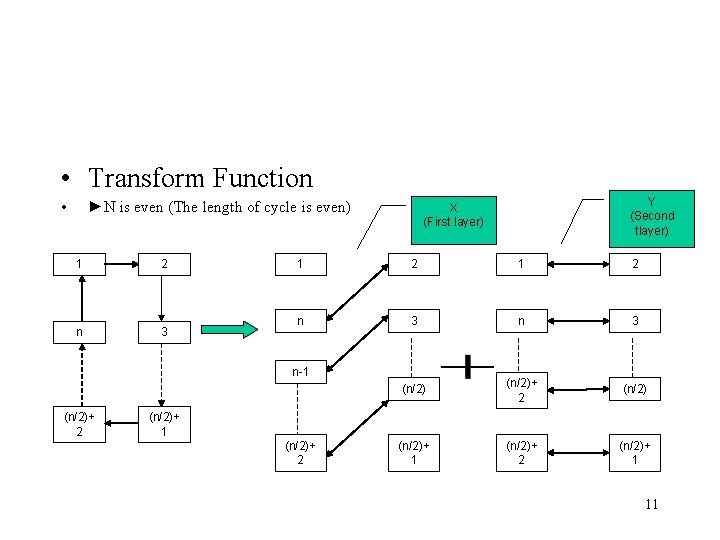

• Transform Function • ►N is even (The length of cycle is even) 1 2 n 3 (n/2)+ 2 (n/2)+ 1 n-1 (n/2)+ 2 Y (Second tlayer) X (First layer) (n/2)+ 1 (n/2)+ 2 11

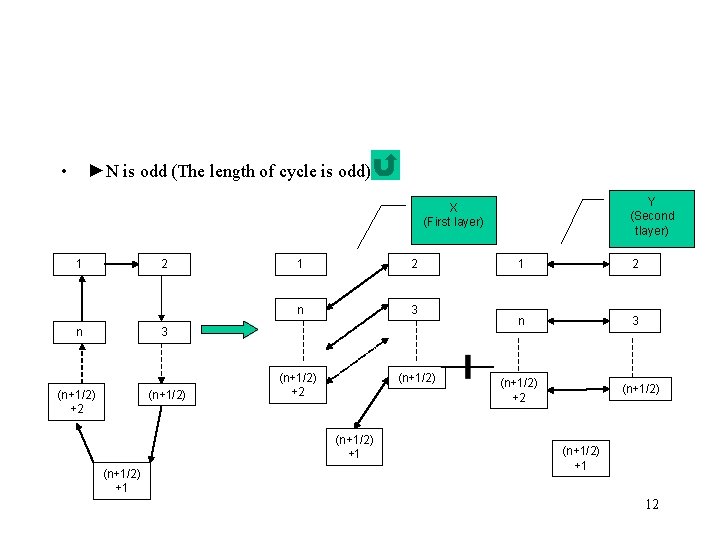

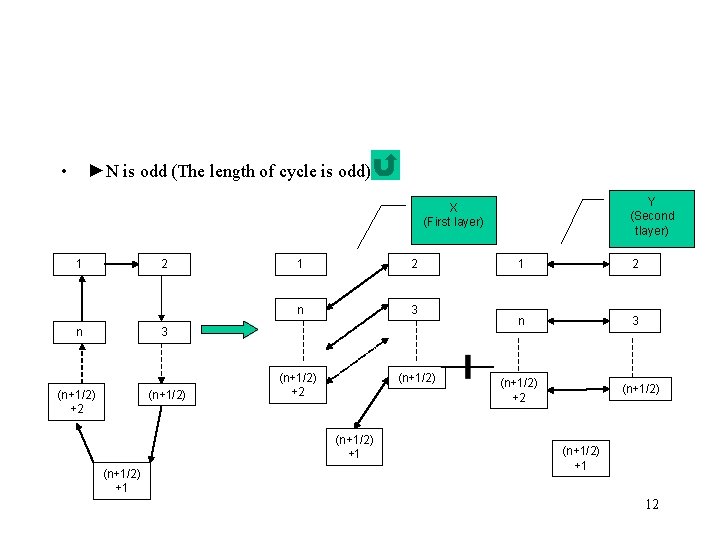

• ►N is odd (The length of cycle is odd) Y (Second tlayer) X (First layer) 1 2 n 3 (n+1/2) +2 (n+1/2) +1 1 2 n 3 (n+1/2) +2 (n+1/2) +1 12

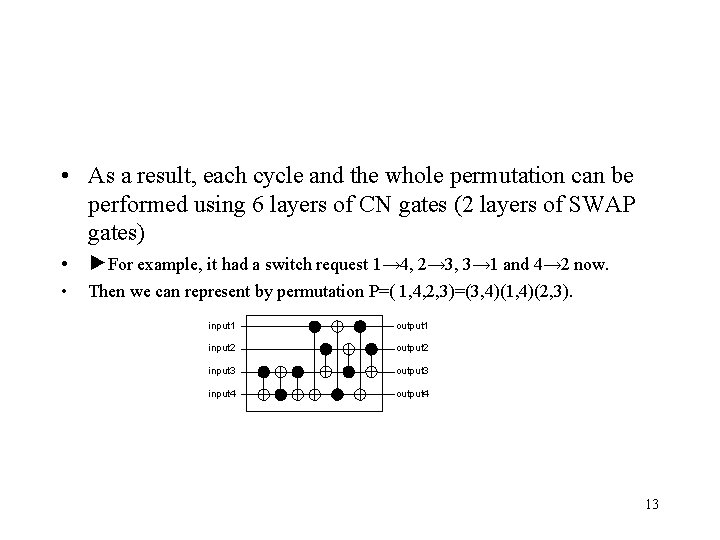

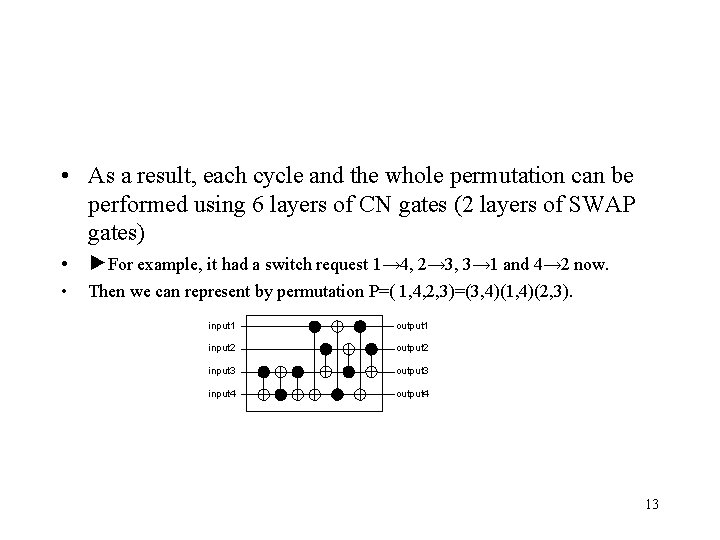

• As a result, each cycle and the whole permutation can be performed using 6 layers of CN gates (2 layers of SWAP gates) • ►For example, it had a switch request 1→ 4, 2→ 3, 3→ 1 and 4→ 2 now. • Then we can represent by permutation P=( 1, 4, 2, 3)=(3, 4)(1, 4)(2, 3). input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 13

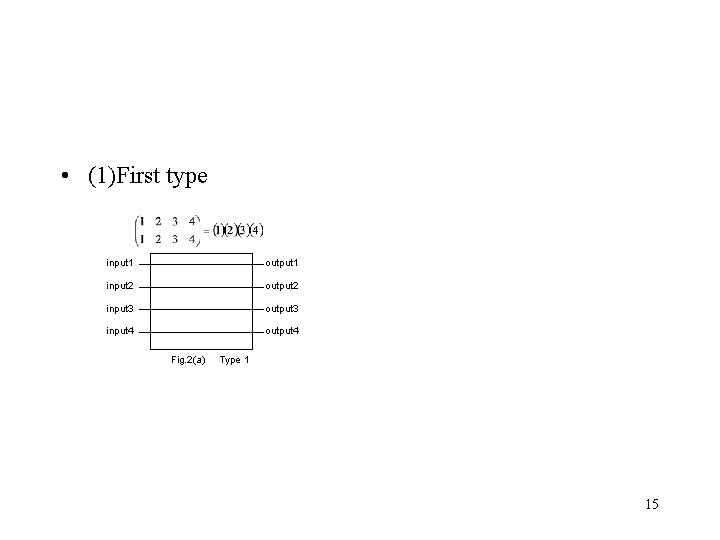

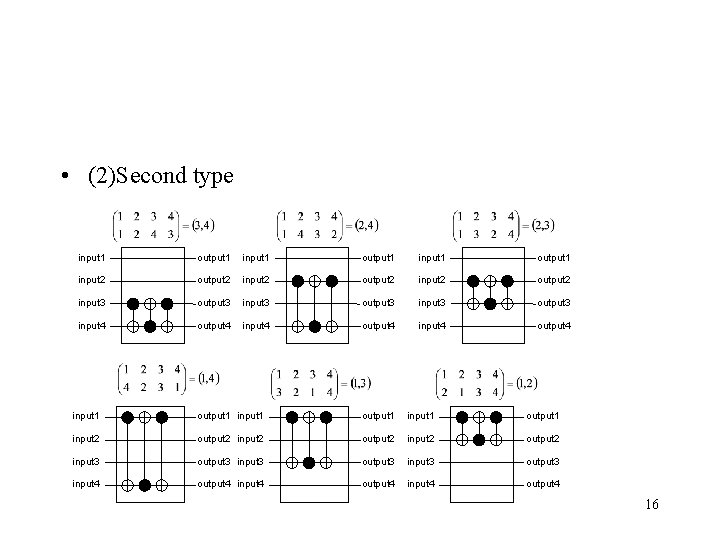

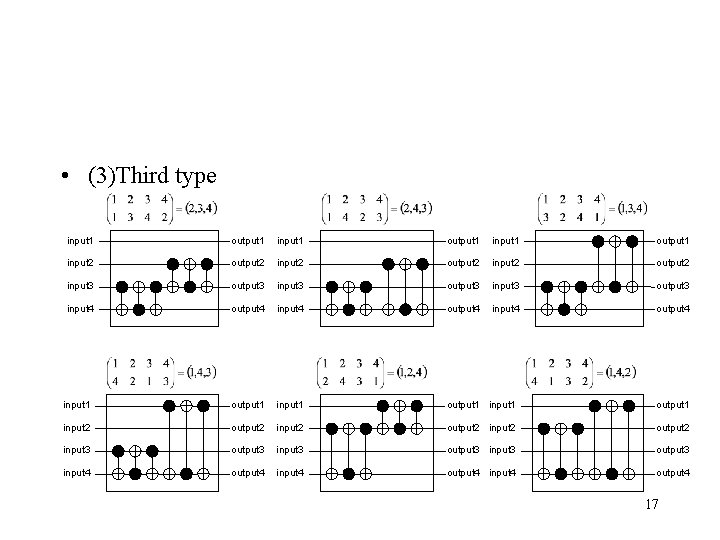

Switch Architecture and Control Design • Switch Architecture • For any input-output pair switch request of one-to-one and onto mapping, we can use quantum circuit to complete. • For design a universal 4× 4 Quantum switch. • • • ►For analyse all 4! Input-output request (1) First type: four input ports does not change to other output port (2)Second type: two of four input ports are change each other (3)Third type: three of four input ports are change each other (4)Fourth type: four input ports are all change 14

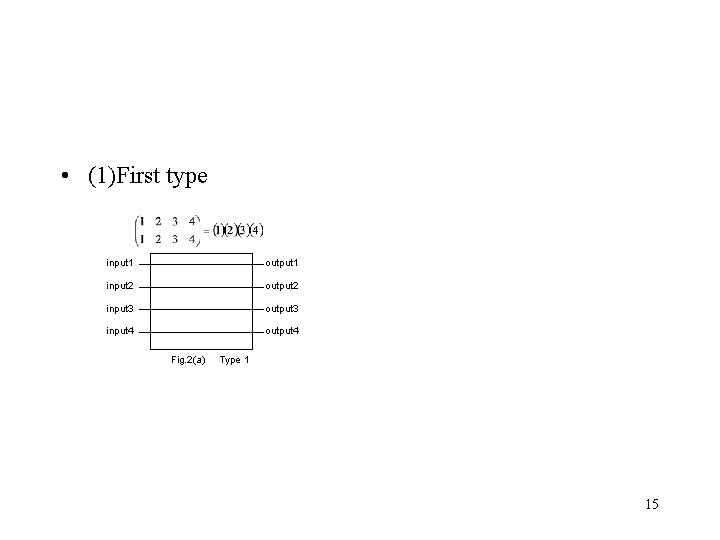

• (1)First type input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 Fig. 2(a) Type 1 15

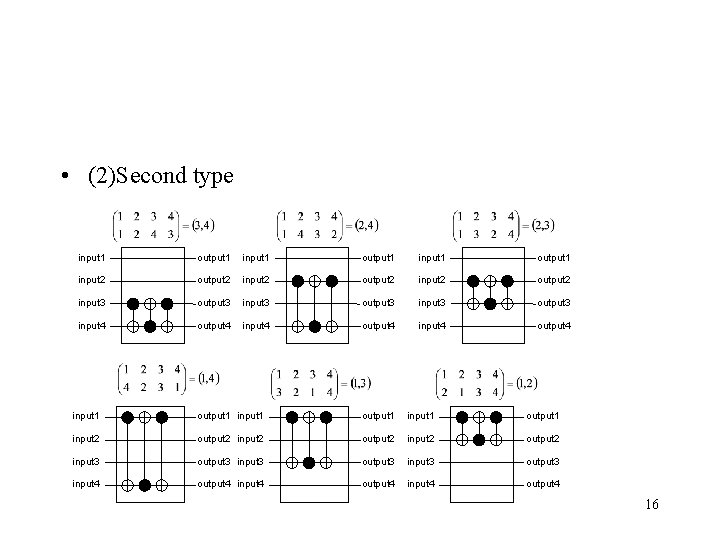

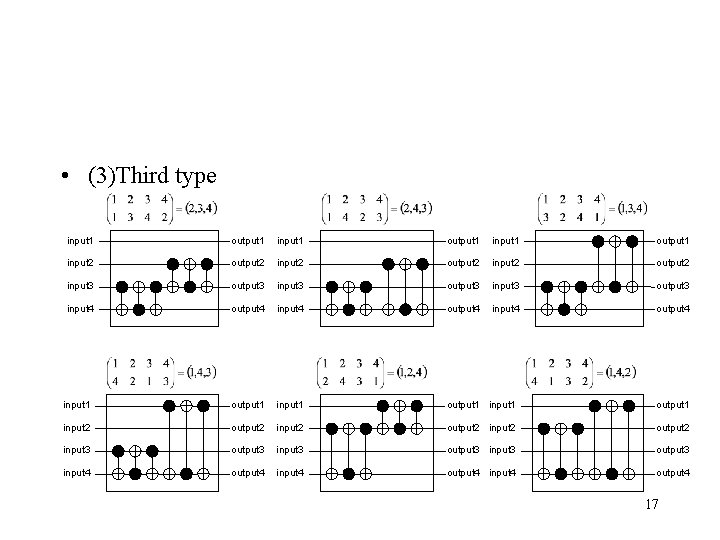

• (2)Second type input 1 output 1 input 1 output 1 input 2 output 2 input 2 output 2 input 3 output 3 input 3 output 3 input 4 output 4 input 4 output 4 16

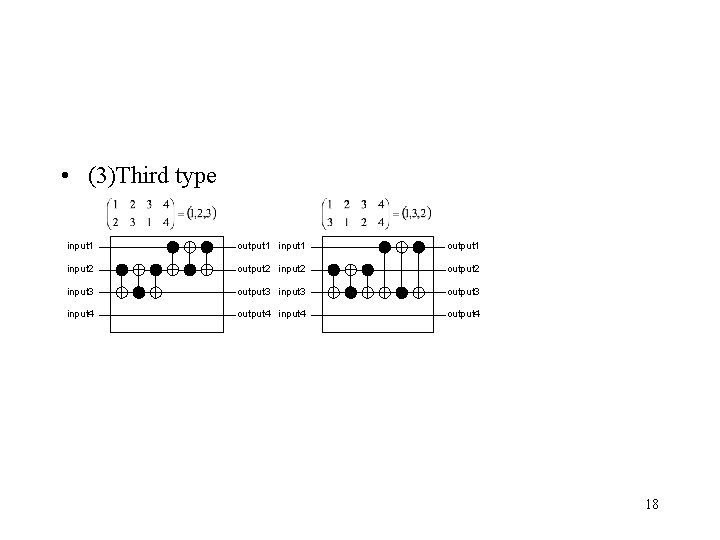

• (3)Third type input 1 output 1 input 1 output 1 input 2 output 2 input 2 output 2 input 3 output 3 input 3 output 3 input 4 output 4 input 4 output 4 17

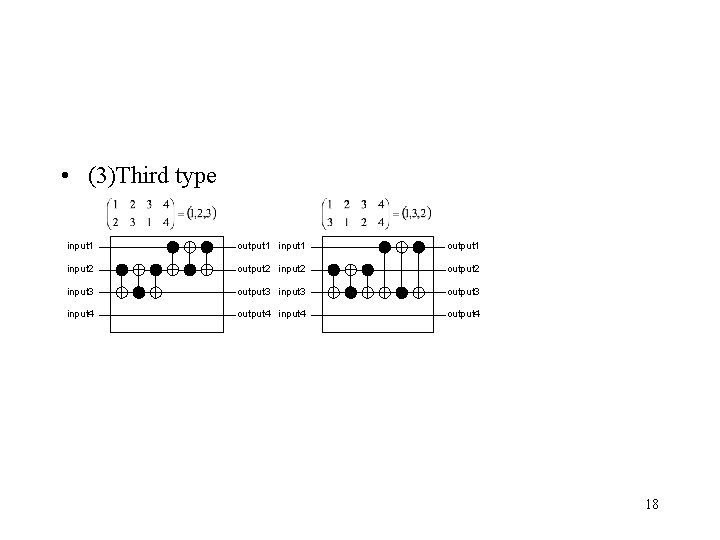

• (3)Third type input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 18

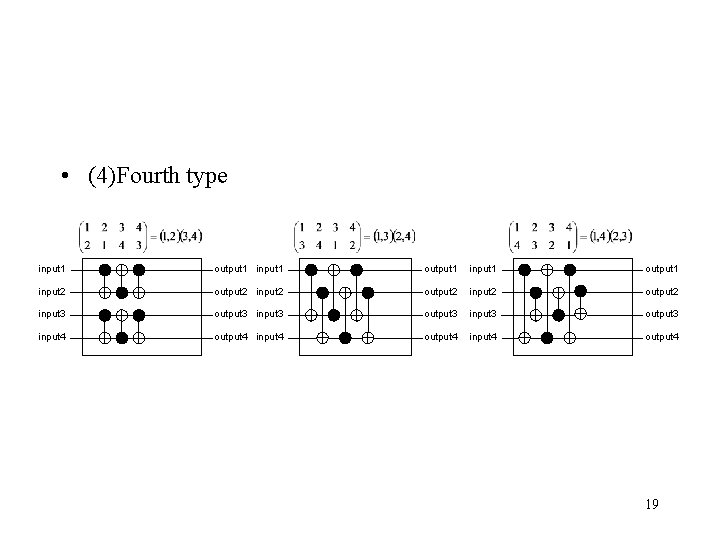

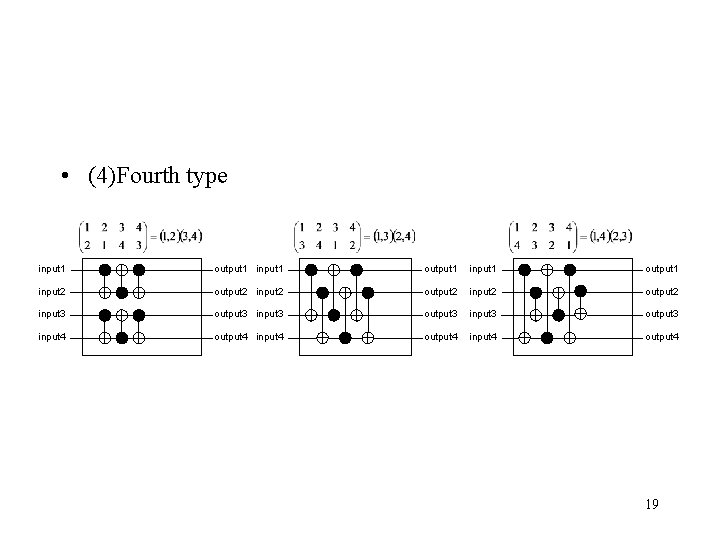

• (4)Fourth type input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 19

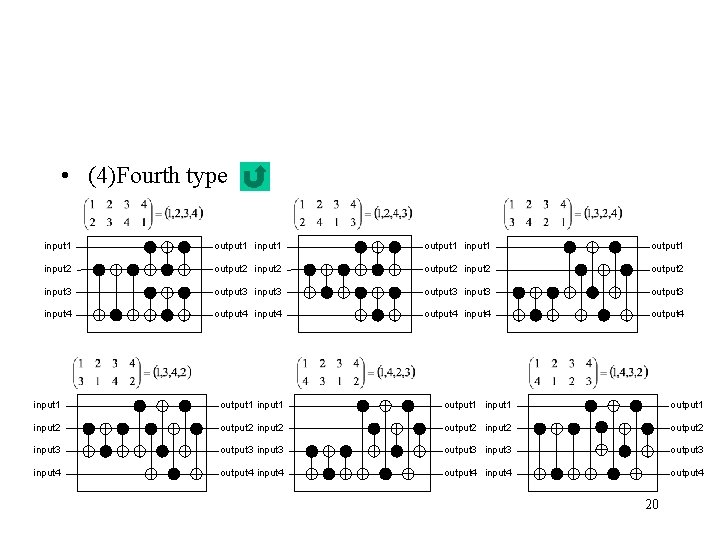

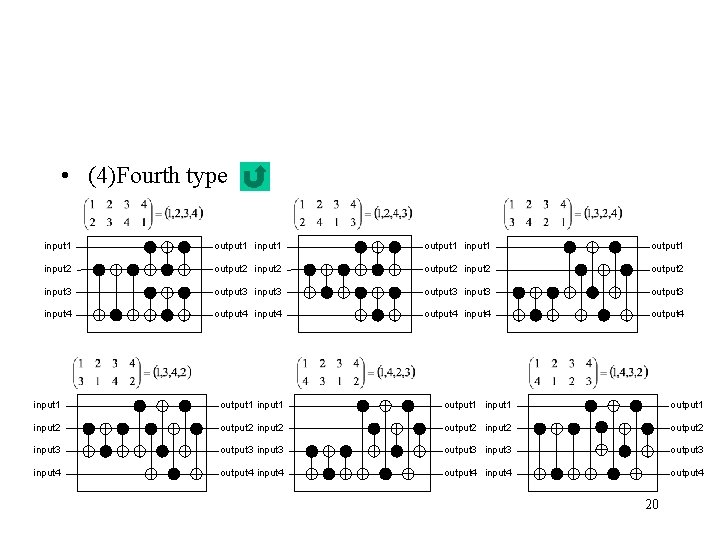

• (4)Fourth type input 1 output 1 input 1 output 1 input 2 output 2 input 2 output 2 input 3 output 3 input 3 output 3 input 4 output 4 input 4 output 4 20

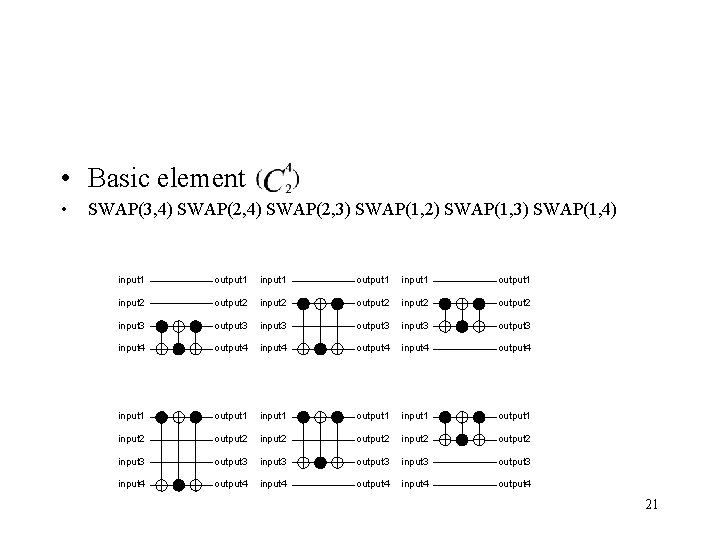

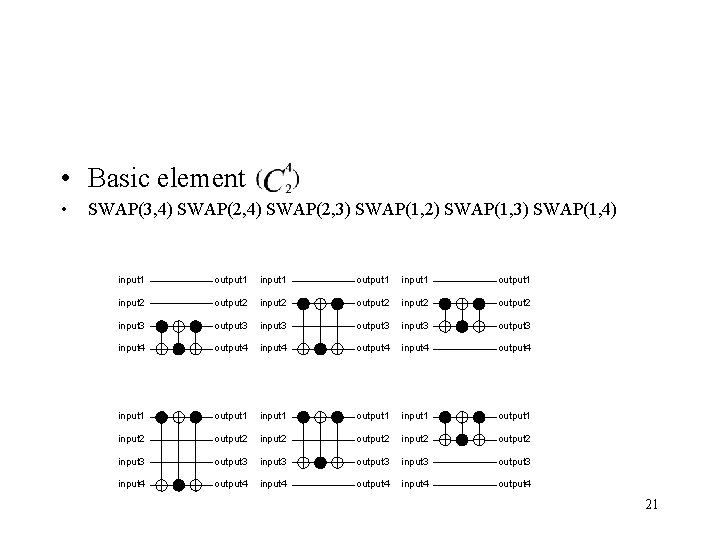

• Basic element • SWAP(3, 4) SWAP(2, 3) SWAP(1, 2) SWAP(1, 3) SWAP(1, 4) input 1 output 1 input 1 output 1 input 2 output 2 input 2 output 2 input 3 output 3 input 3 output 3 input 4 output 4 input 4 output 4 21

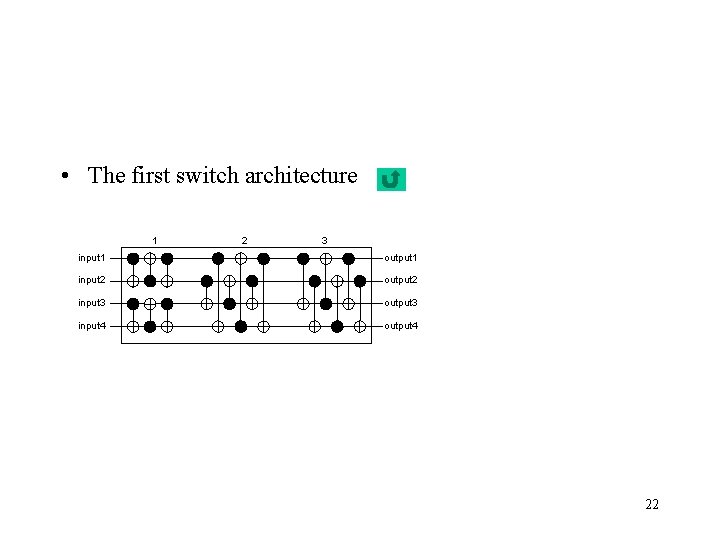

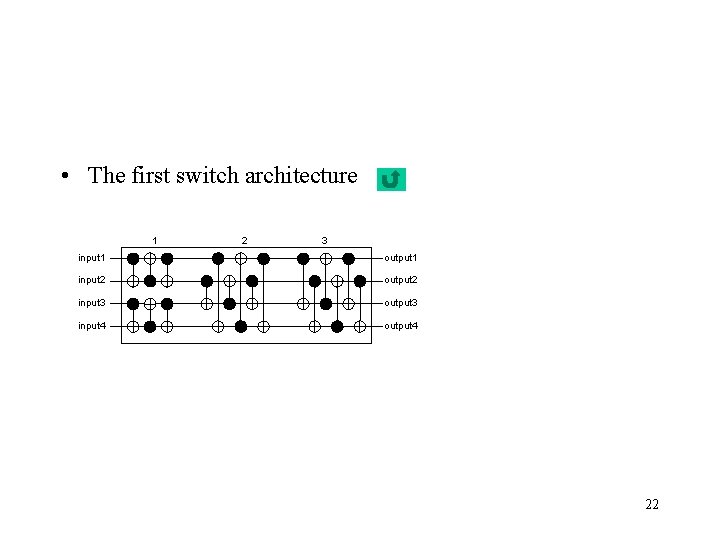

• The first switch architecture 1 2 3 input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 22

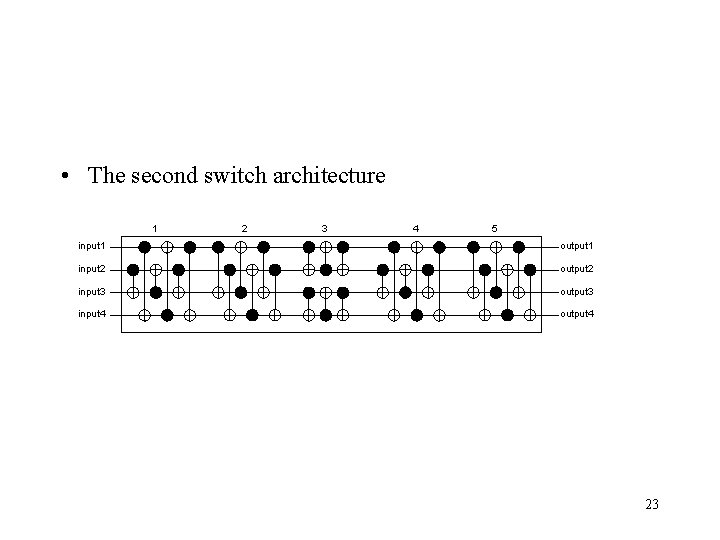

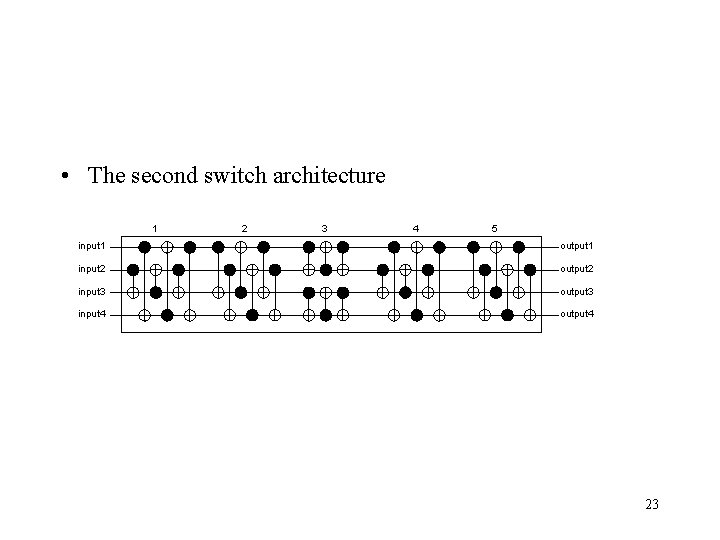

• The second switch architecture 1 2 3 4 5 input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 23

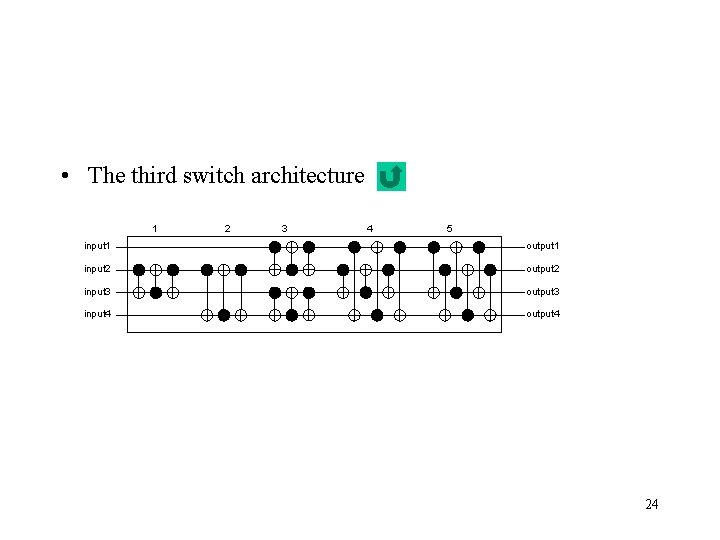

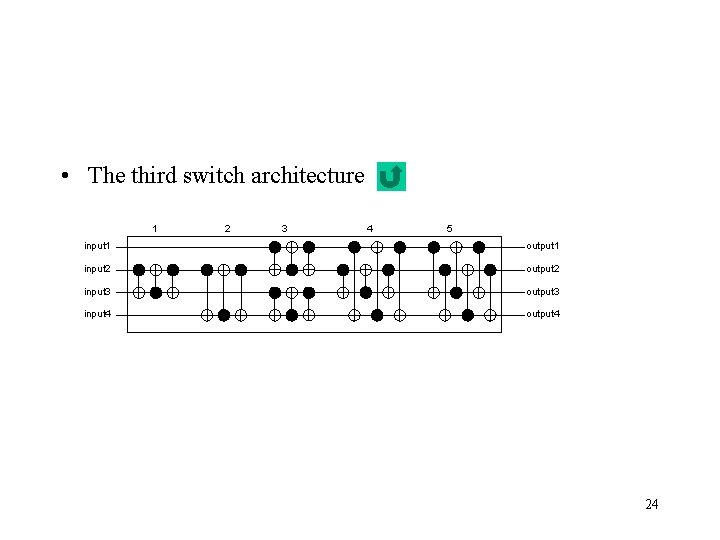

• The third switch architecture 1 2 3 4 5 input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 24

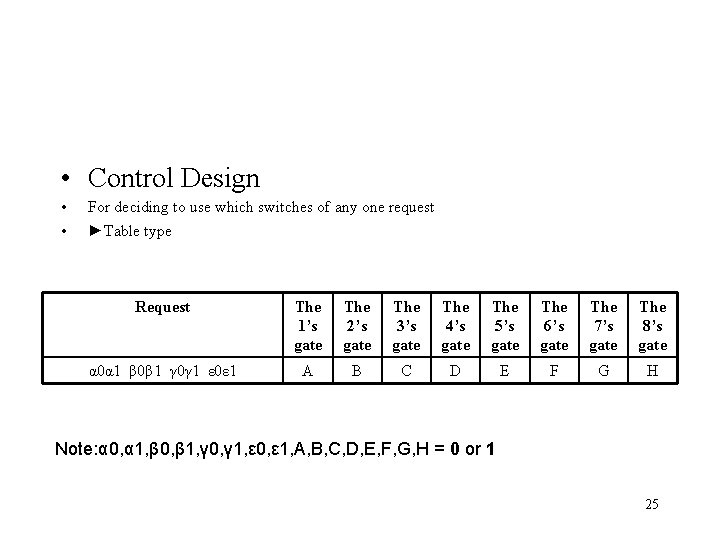

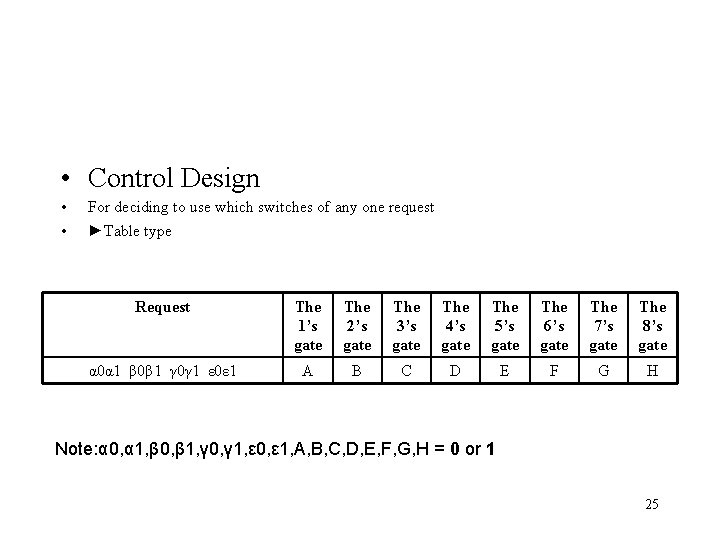

• Control Design • • For deciding to use which switches of any one request ►Table type Request The 1’s gate The 2’s gate The 3’s gate The 4’s gate The 5’s gate The 6’s gate The 7’s gate The 8’s gate α 0α 1 β 0β 1 γ 0γ 1 ε 0ε 1 A B C D E F G H Note: α 0, α 1, β 0, β 1, γ 0, γ 1, ε 0, ε 1, A, B, C, D, E, F, G, H = 0 or 1 25

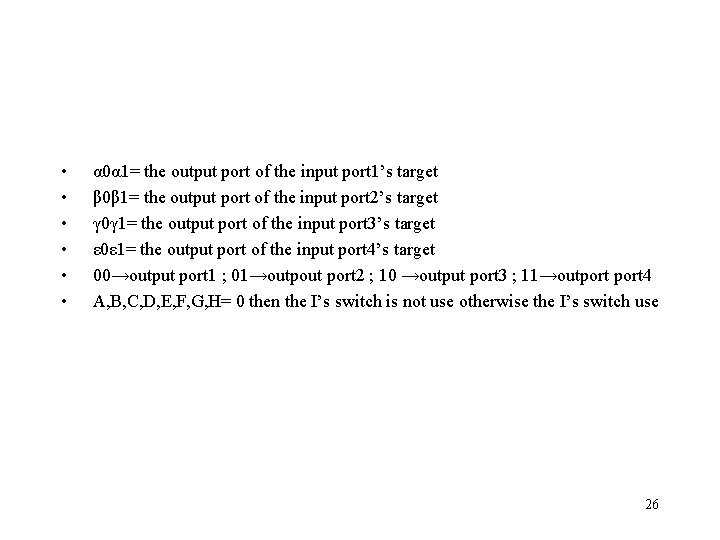

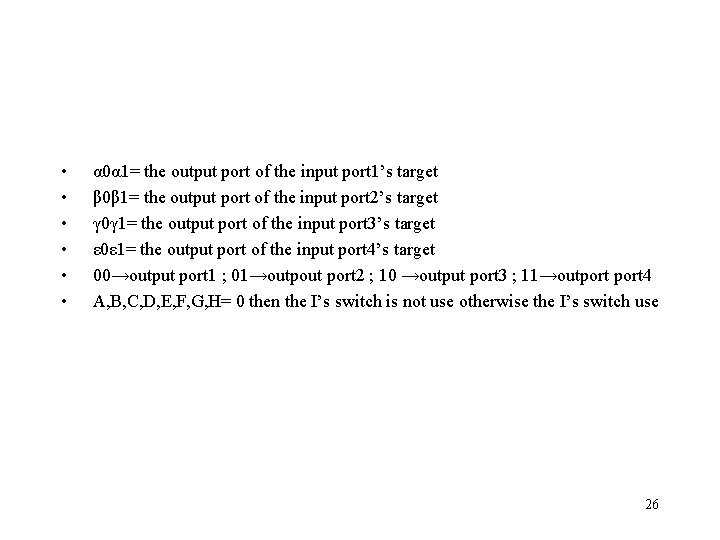

• • • α 0α 1= the output port of the input port 1’s target β 0β 1= the output port of the input port 2’s target γ 0γ 1= the output port of the input port 3’s target ε 0ε 1= the output port of the input port 4’s target 00→output port 1 ; 01→outpout port 2 ; 10 →output port 3 ; 11→outport 4 A, B, C, D, E, F, G, H= 0 then the I’s switch is not use otherwise the I’s switch use 26

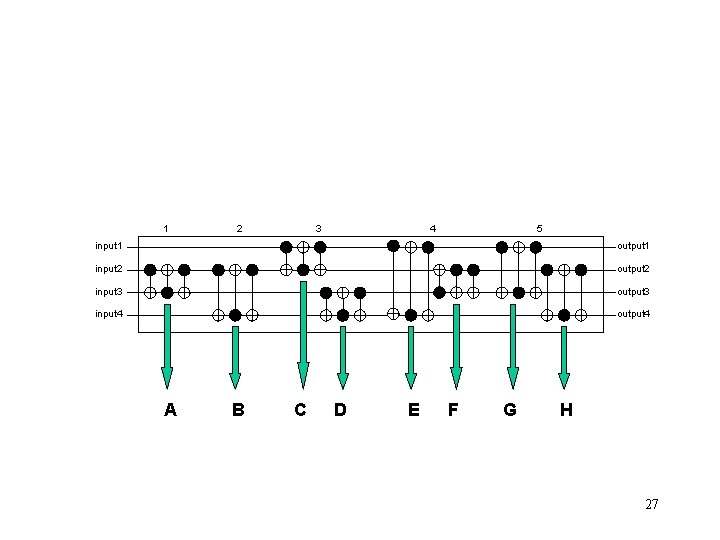

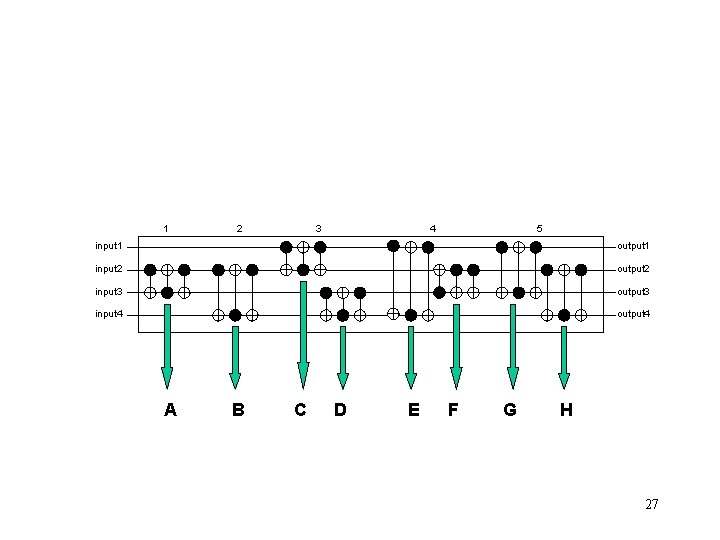

1 2 3 4 5 input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 A B C D E F G H 27

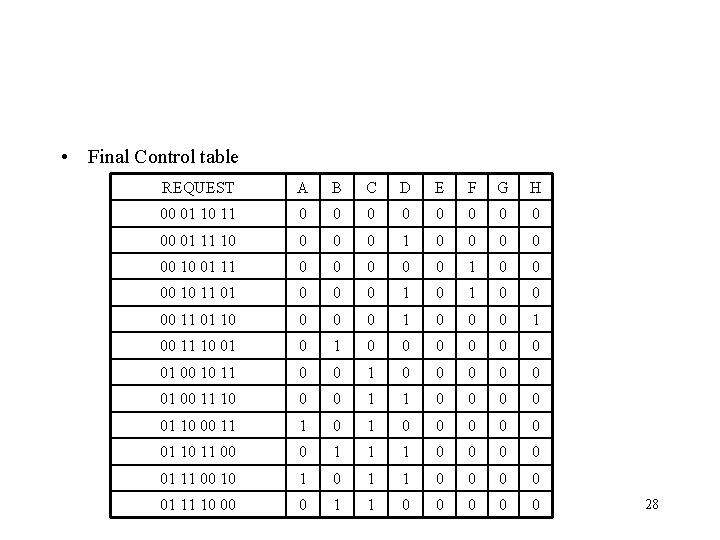

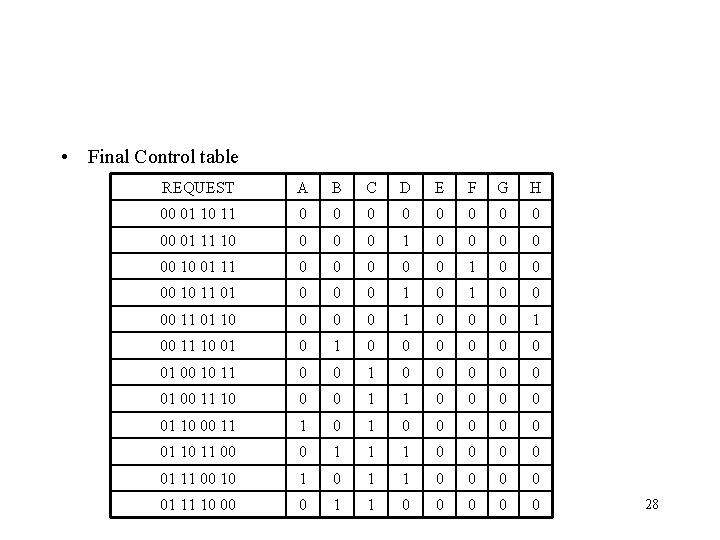

• Final Control table REQUEST A B C D E F G H 00 01 10 11 0 0 0 0 00 01 11 10 0 1 0 0 00 10 01 11 0 0 00 10 11 01 0 0 00 11 01 10 0 1 00 11 10 01 0 0 0 0 01 00 10 11 0 0 01 00 11 10 0 0 1 1 0 0 01 10 00 11 1 0 0 0 01 10 11 00 0 1 1 1 0 0 01 11 00 10 1 1 0 0 01 11 10 00 0 1 1 0 0 0 28

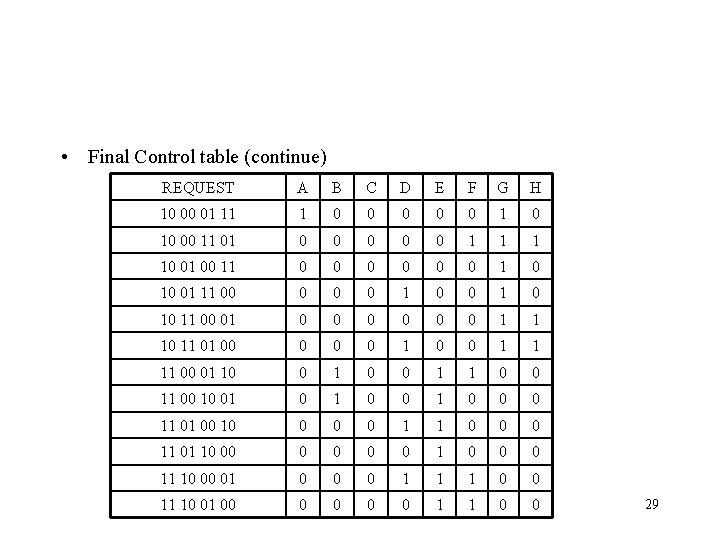

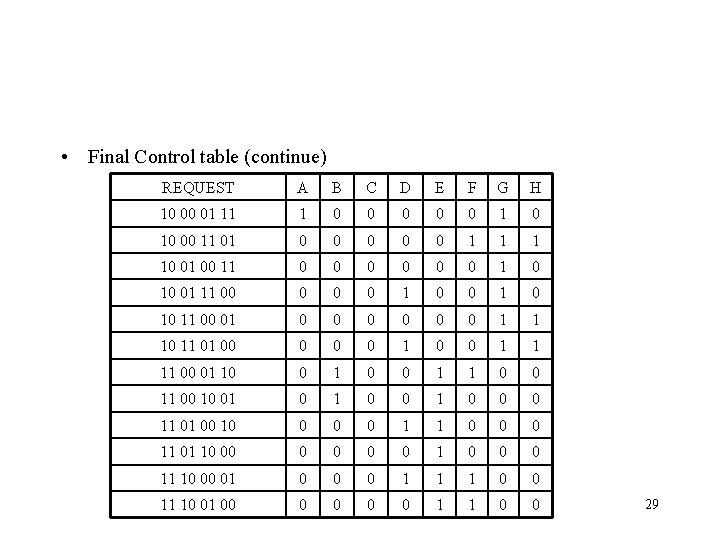

• Final Control table (continue) REQUEST A B C D E F G H 10 00 01 11 1 0 0 0 10 00 11 01 0 0 0 1 10 01 00 11 0 0 0 1 0 10 01 11 00 0 10 11 00 01 0 0 0 1 1 10 11 01 00 0 1 1 11 00 01 10 0 1 1 0 0 11 00 10 01 0 0 0 11 01 00 10 0 1 1 0 0 0 11 01 10 00 0 0 11 10 00 01 0 0 0 1 1 1 0 0 11 10 01 00 0 0 1 1 0 0 29

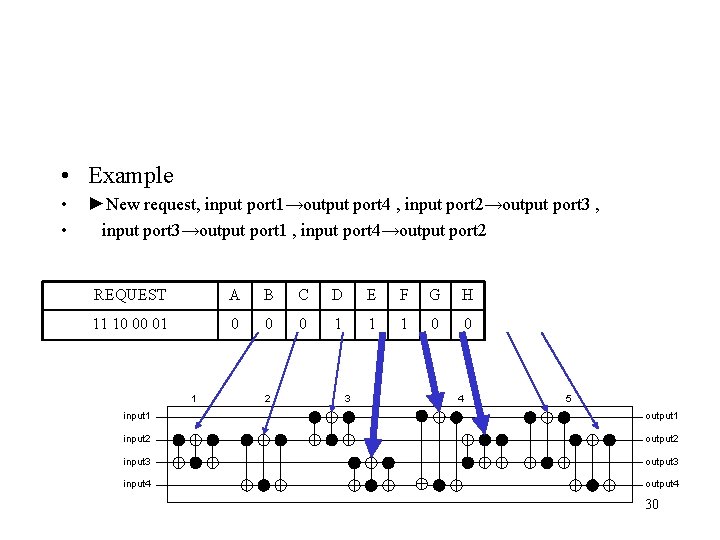

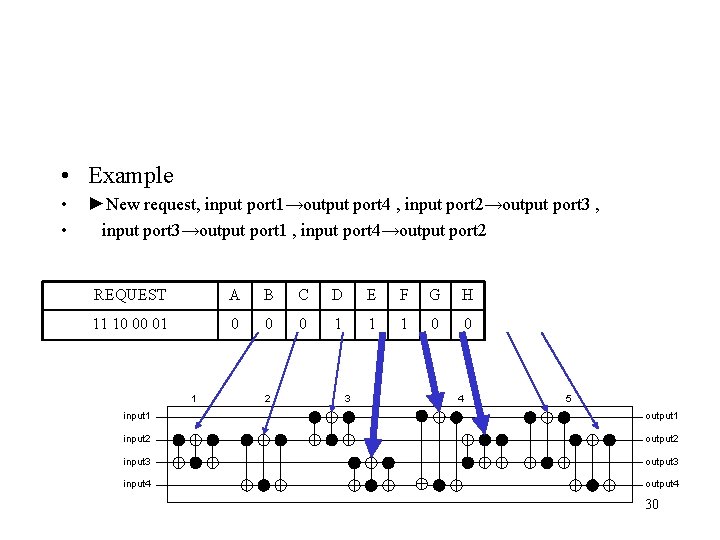

• Example • • ►New request, input port 1→output port 4 , input port 2→output port 3 , input port 3→output port 1 , input port 4→output port 2 REQUEST A B C D E F G H 11 10 00 01 0 0 0 1 1 1 0 0 1 2 3 4 5 input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 30

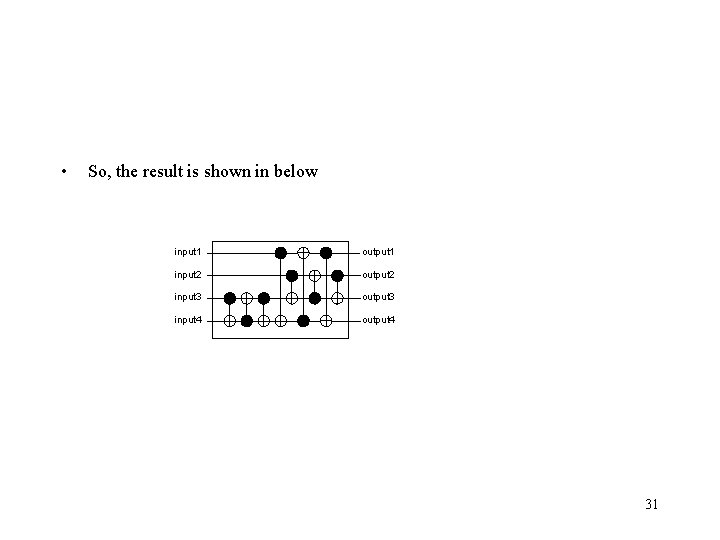

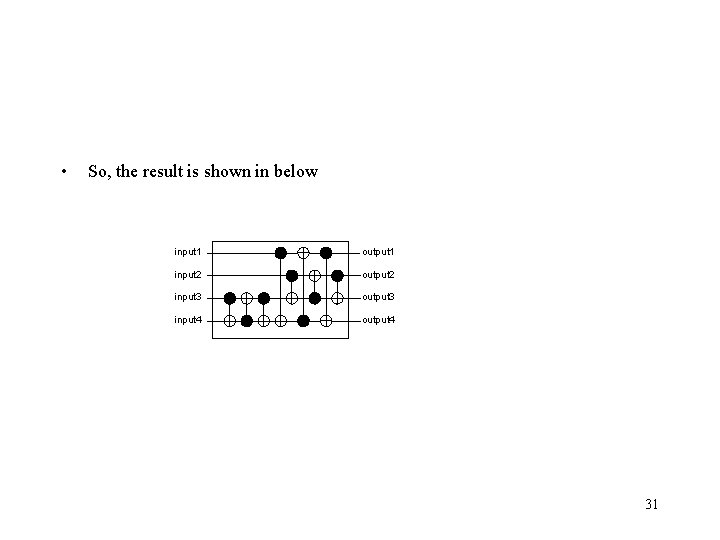

• So, the result is shown in below input 1 output 1 input 2 output 2 input 3 output 3 input 4 output 4 31

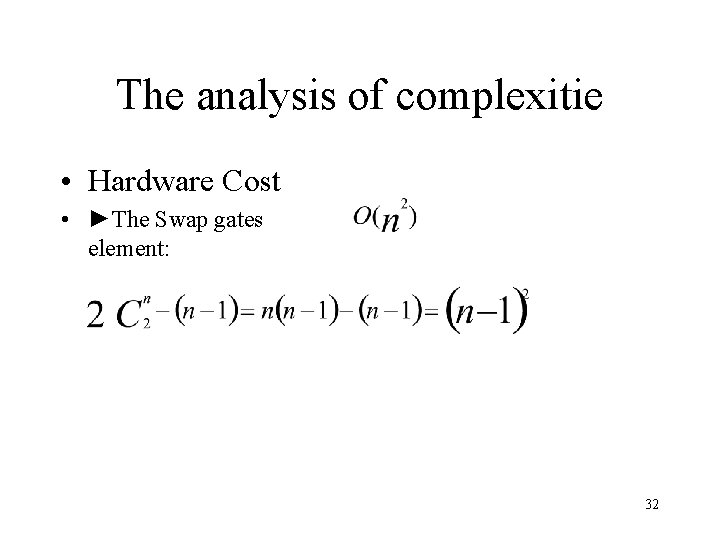

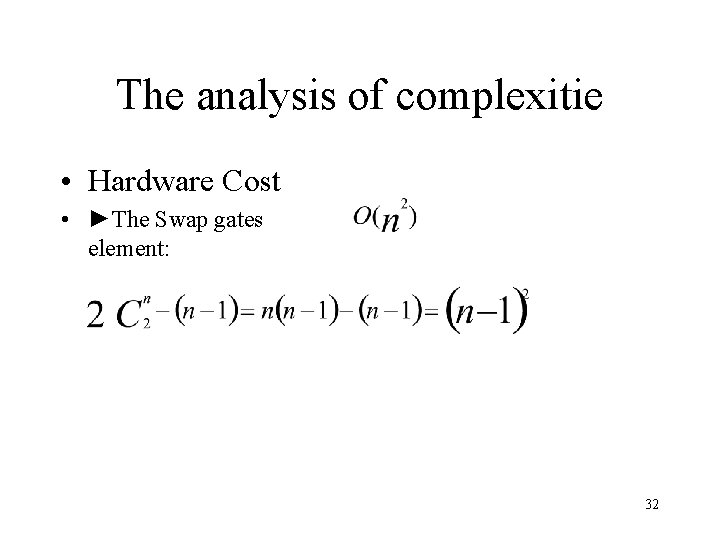

The analysis of complexitie • Hardware Cost • ►The Swap gates element: 32

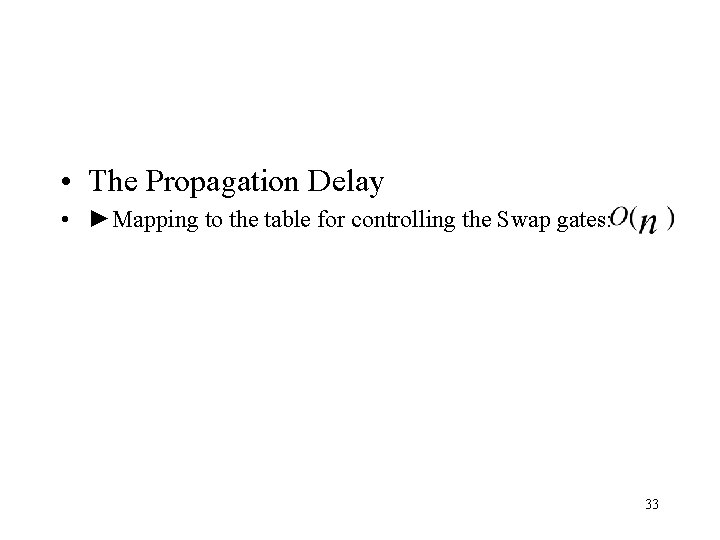

• The Propagation Delay • ►Mapping to the table for controlling the Swap gates: 33

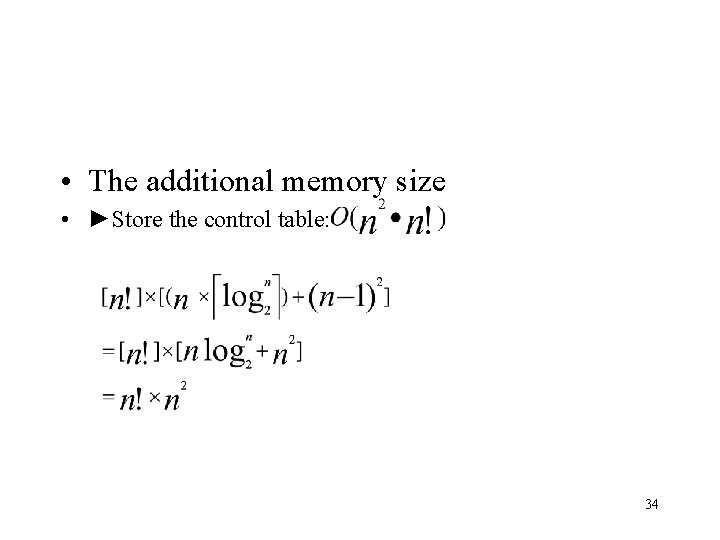

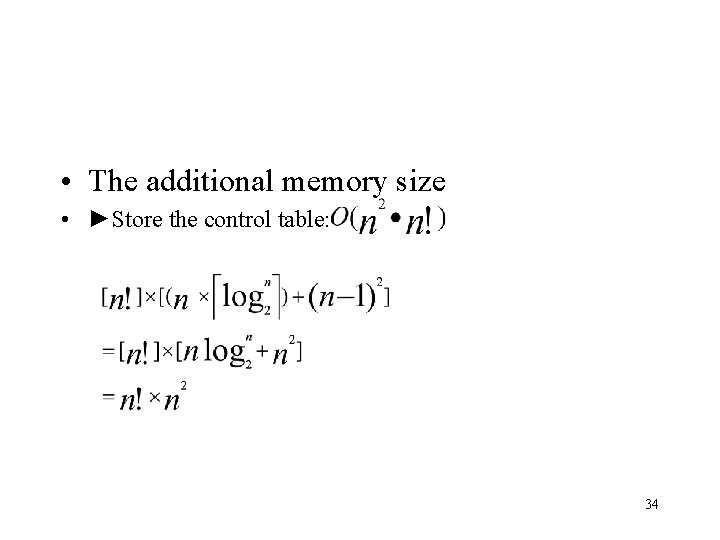

• The additional memory size • ►Store the control table: 34

Future work • Improve Control part • Improve Switch Architecture 35