The program counter There is a special register

- Slides: 24

The program counter There is a special register inside the processor big enough to hold an instruction address called the program counter (PC) Datorteknik Add. Sub bild 1

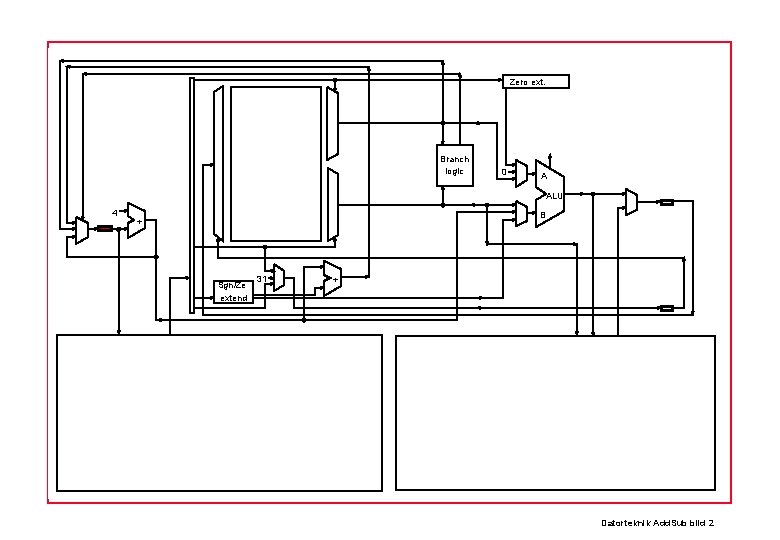

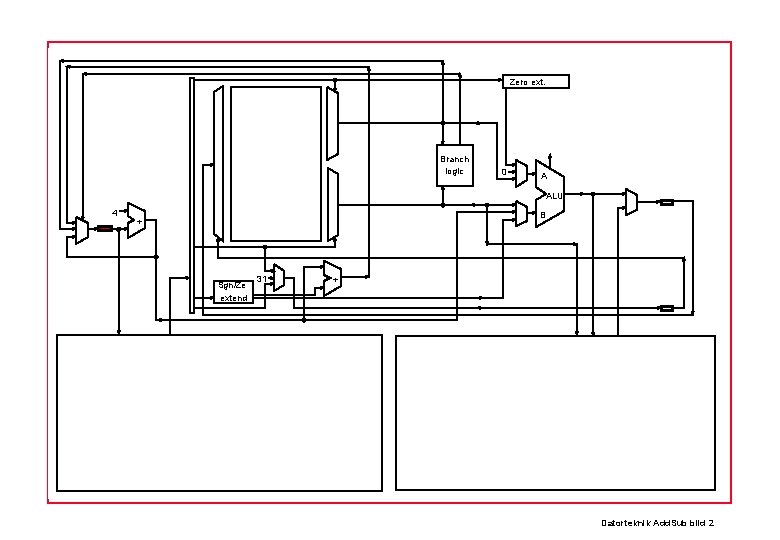

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Datorteknik Add. Sub bild 2

Fetch - execute Fetch: – Send the value in the PC to the instruction memory – The instruction memory gives out one instruction Execute – Carry out the fetched instruction – also: PC : = PC+4; Fetch Execute ≈ 108 times per second Datorteknik Add. Sub bild 3

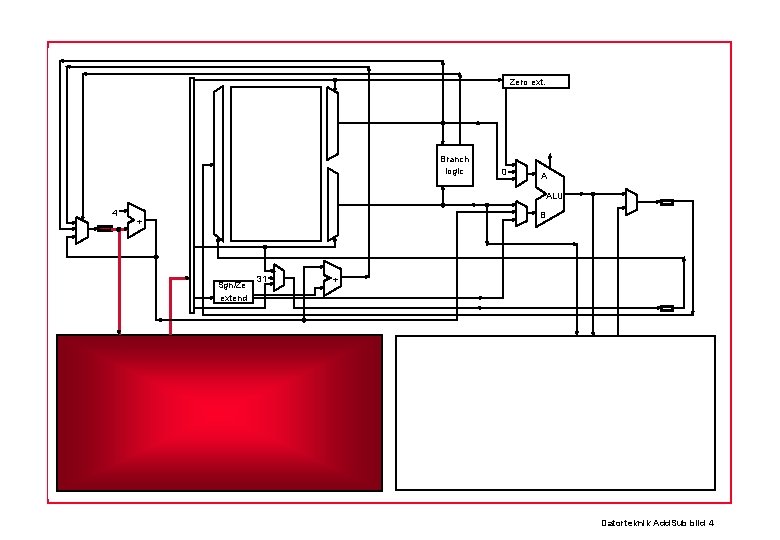

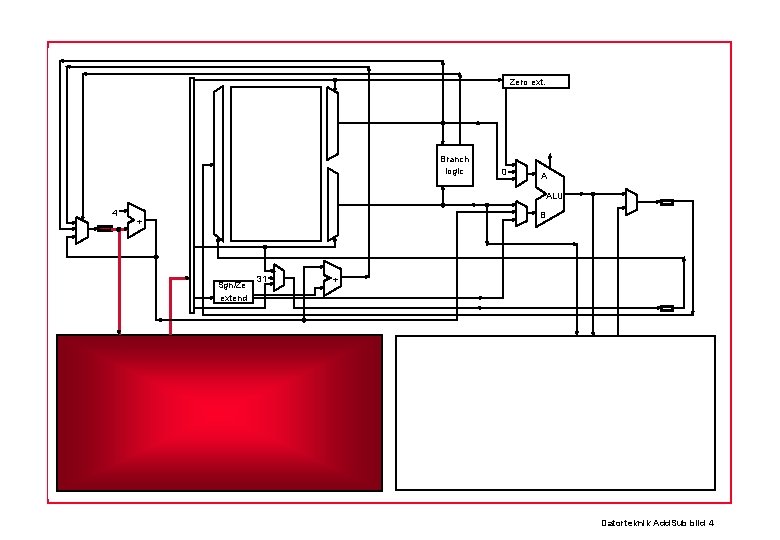

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Datorteknik Add. Sub bild 4

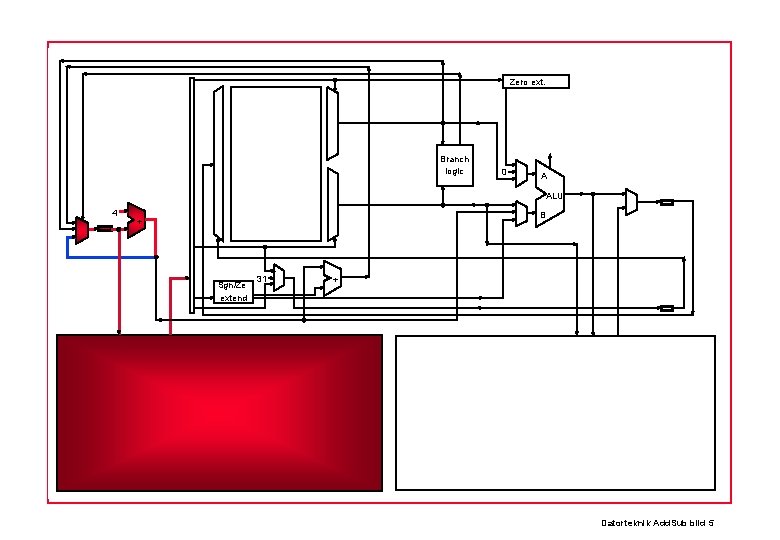

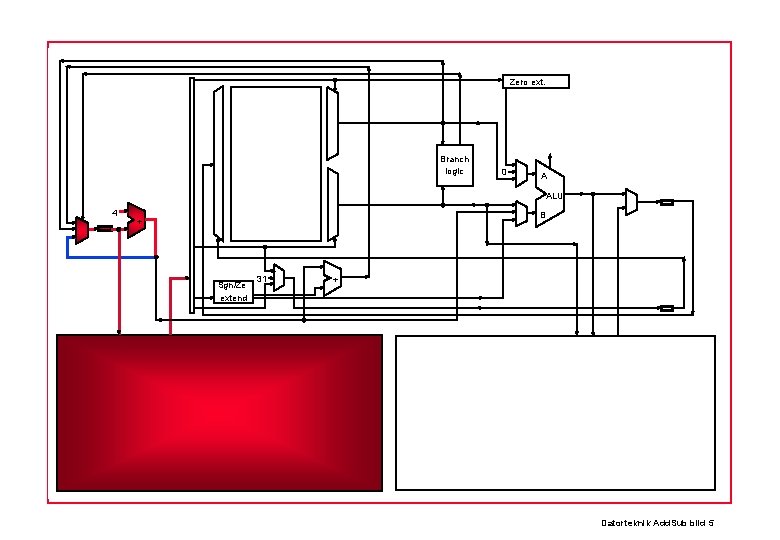

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Datorteknik Add. Sub bild 5

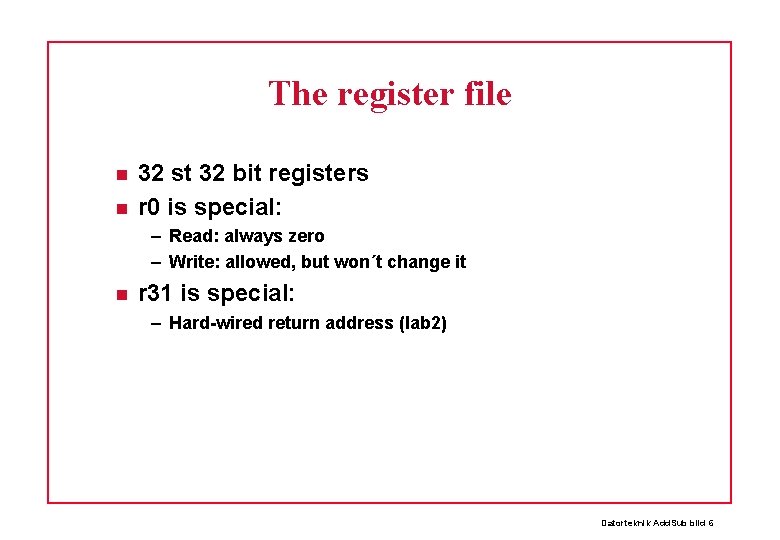

The register file 32 st 32 bit registers r 0 is special: – Read: always zero – Write: allowed, but won´t change it r 31 is special: – Hard-wired return address (lab 2) Datorteknik Add. Sub bild 6

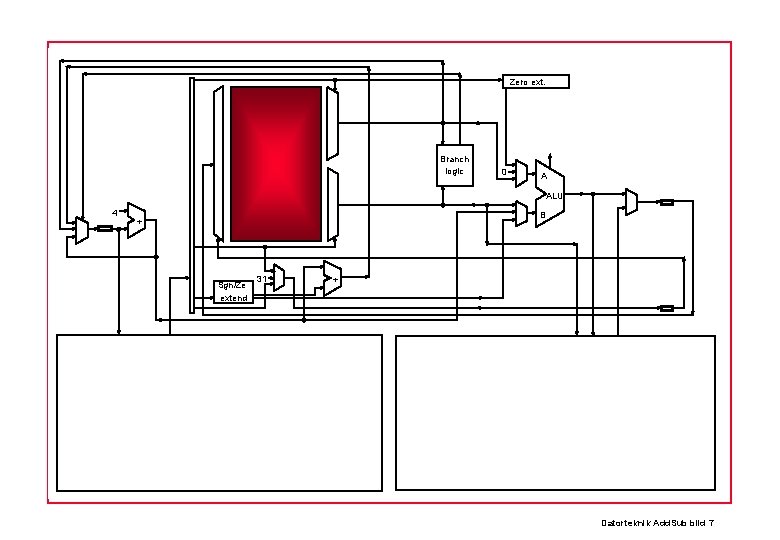

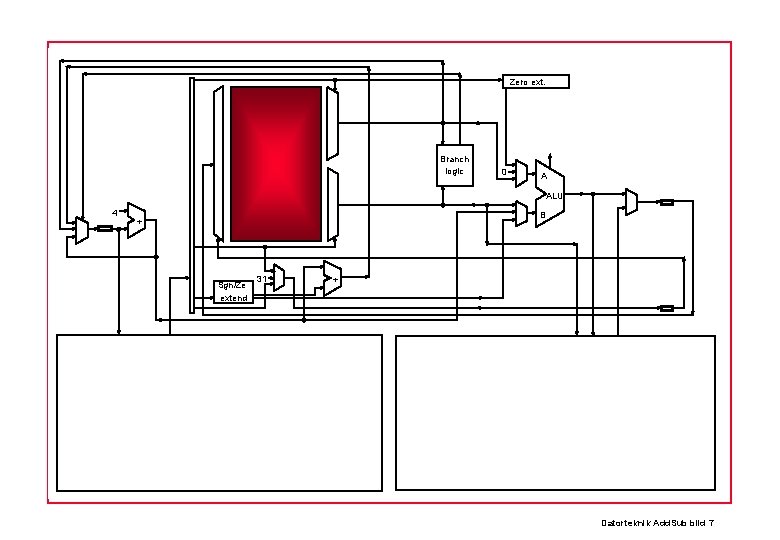

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Datorteknik Add. Sub bild 7

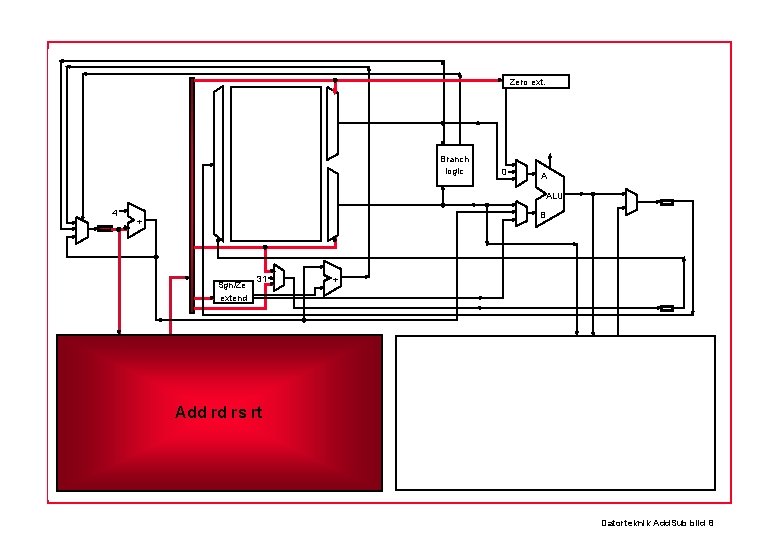

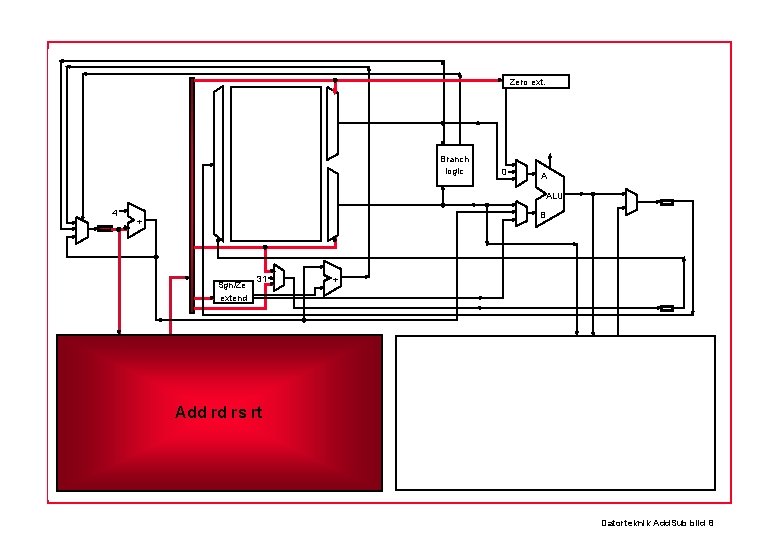

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Add rd rs rt Datorteknik Add. Sub bild 8

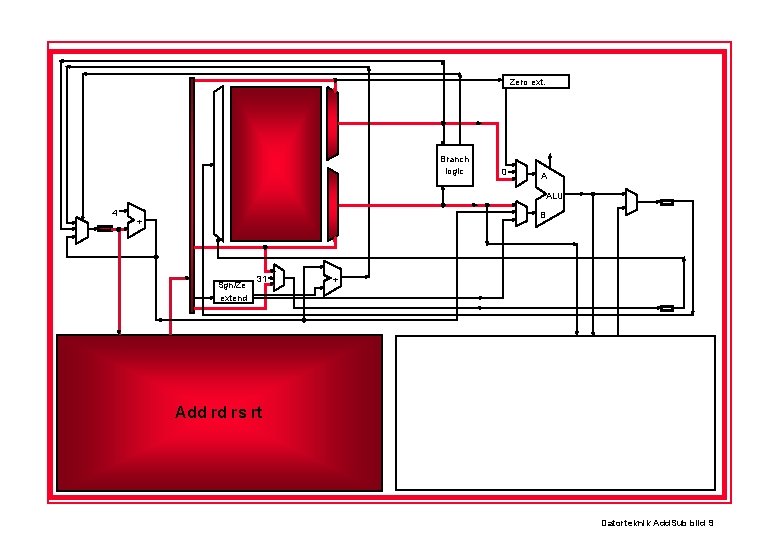

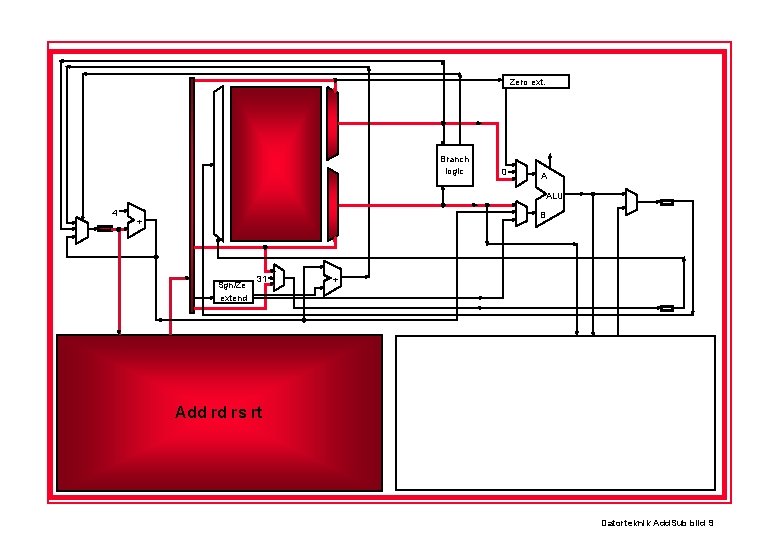

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Add rd rs rt Datorteknik Add. Sub bild 9

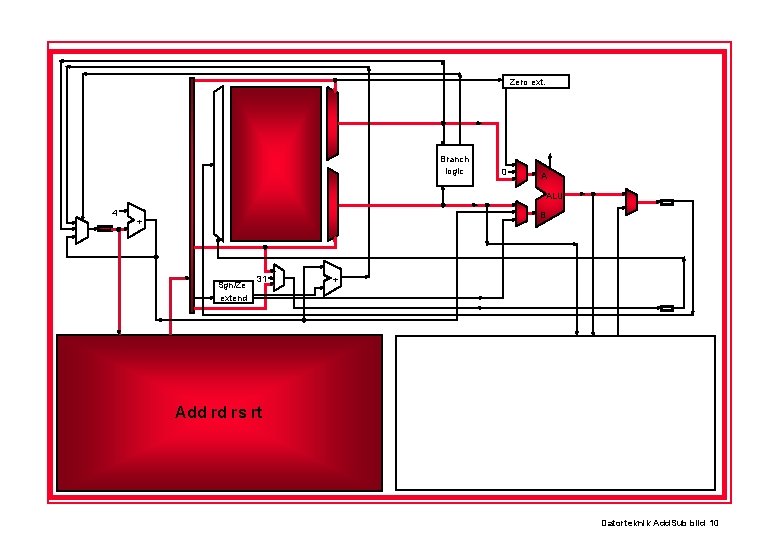

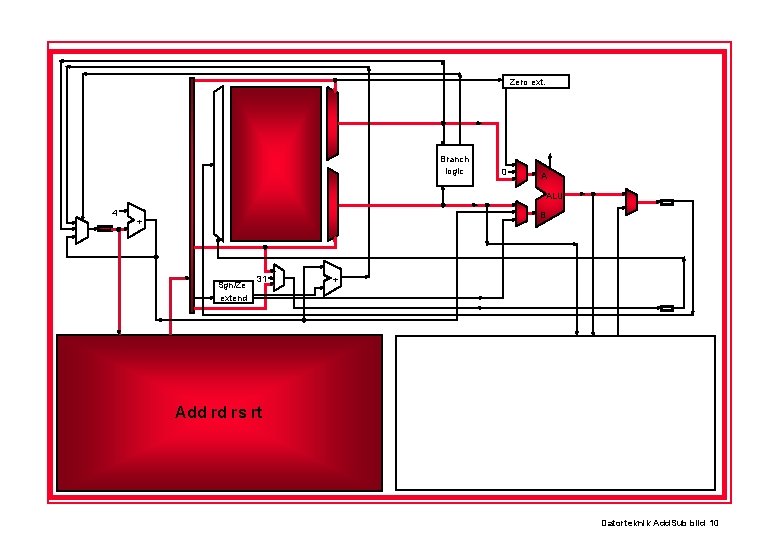

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Add rd rs rt Datorteknik Add. Sub bild 10

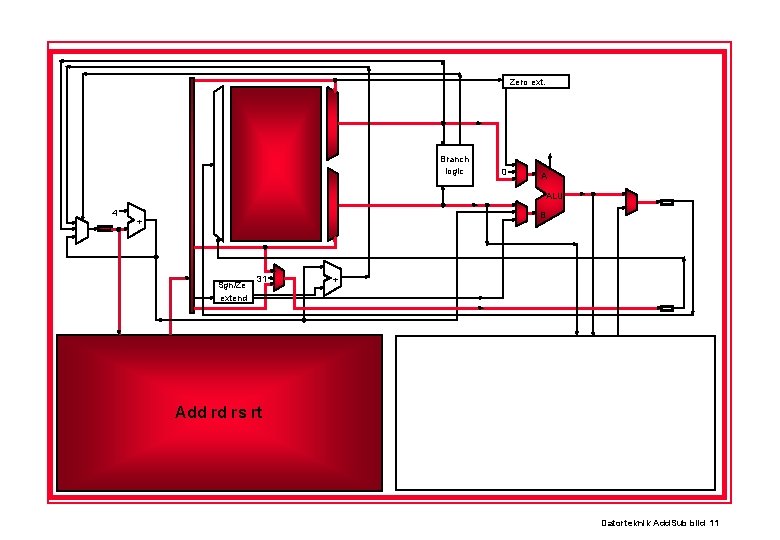

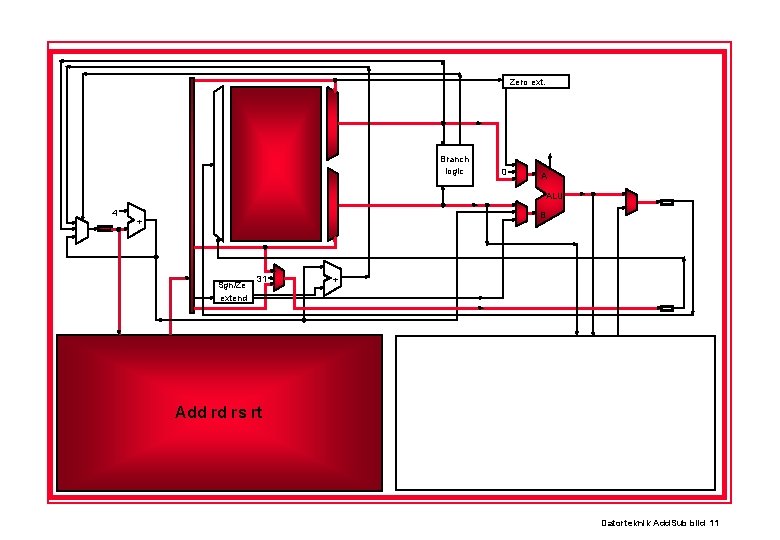

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Add rd rs rt Datorteknik Add. Sub bild 11

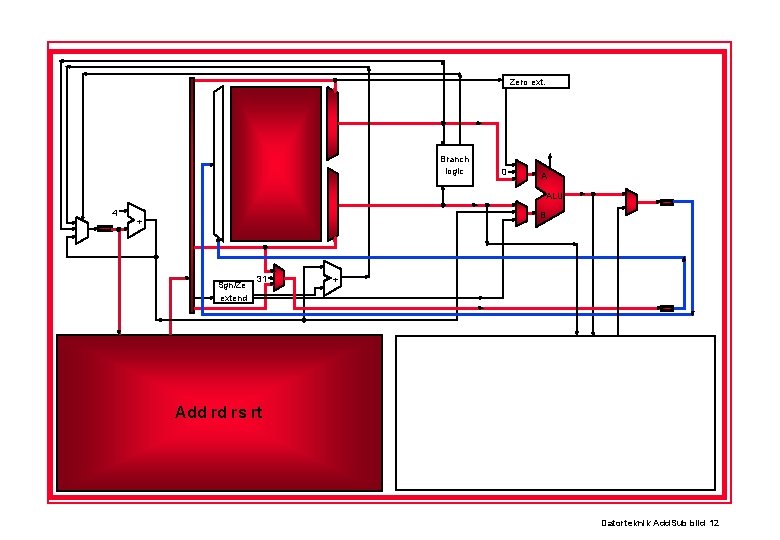

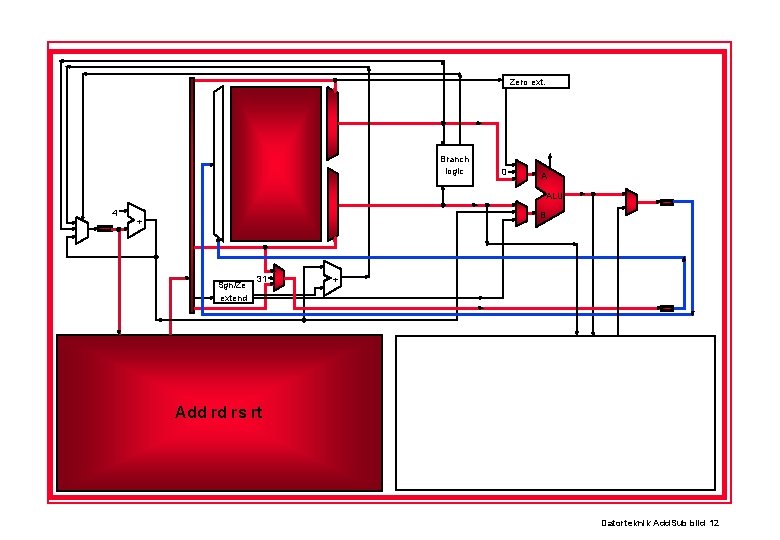

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Add rd rs rt Datorteknik Add. Sub bild 12

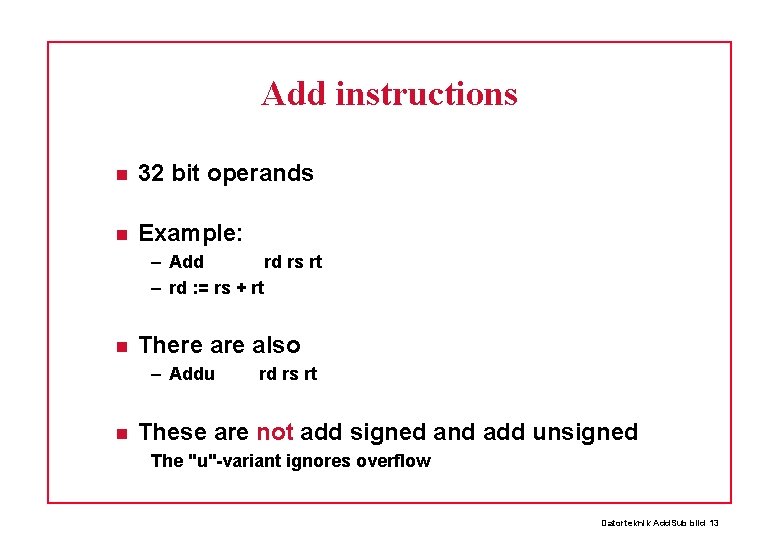

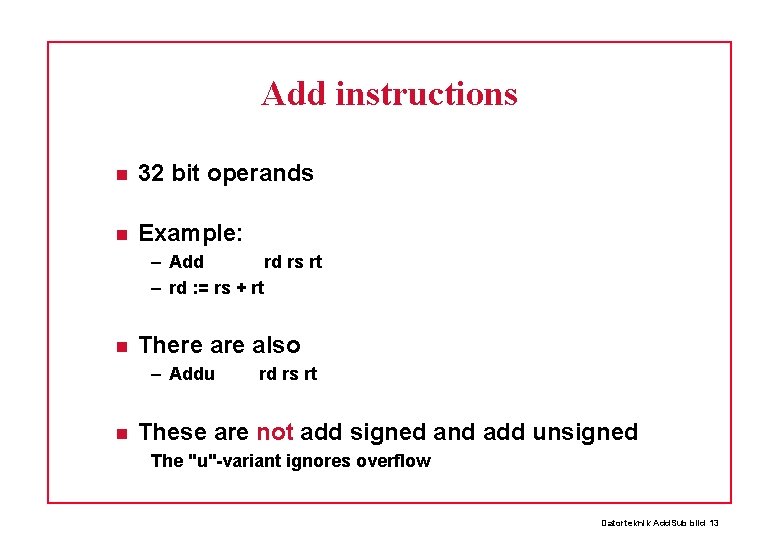

Add instructions 32 bit operands Example: – Add rd rs rt – rd : = rs + rt There also – Addu rd rs rt These are not add signed and add unsigned The "u"-variant ignores overflow Datorteknik Add. Sub bild 13

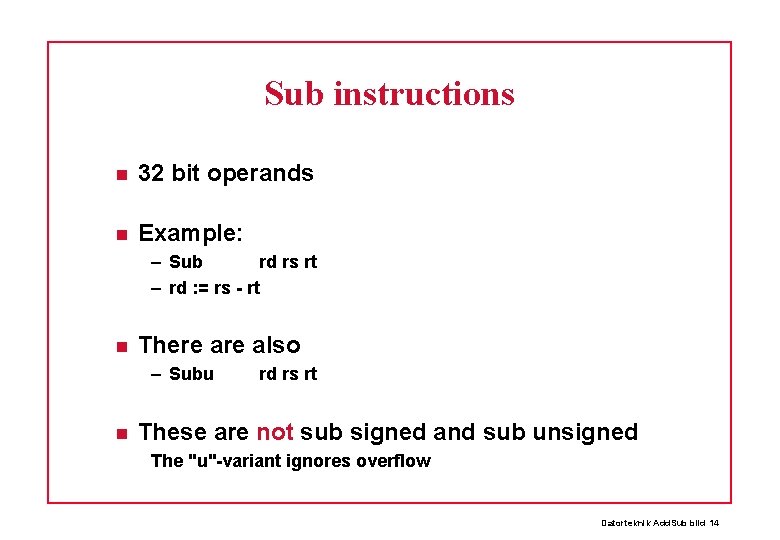

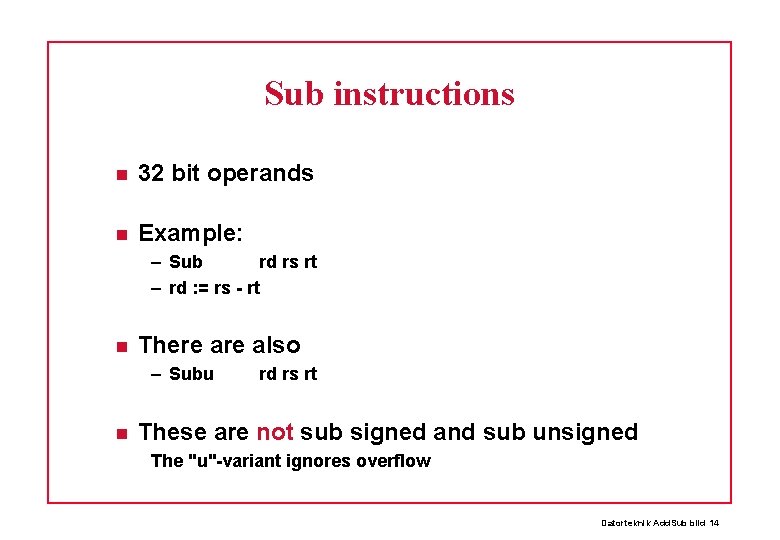

Sub instructions 32 bit operands Example: – Sub rd rs rt – rd : = rs - rt There also – Subu rd rs rt These are not sub signed and sub unsigned The "u"-variant ignores overflow Datorteknik Add. Sub bild 14

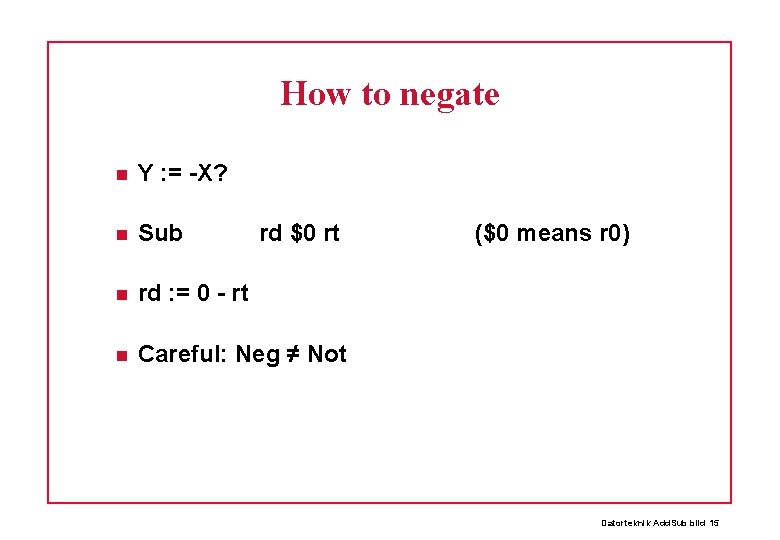

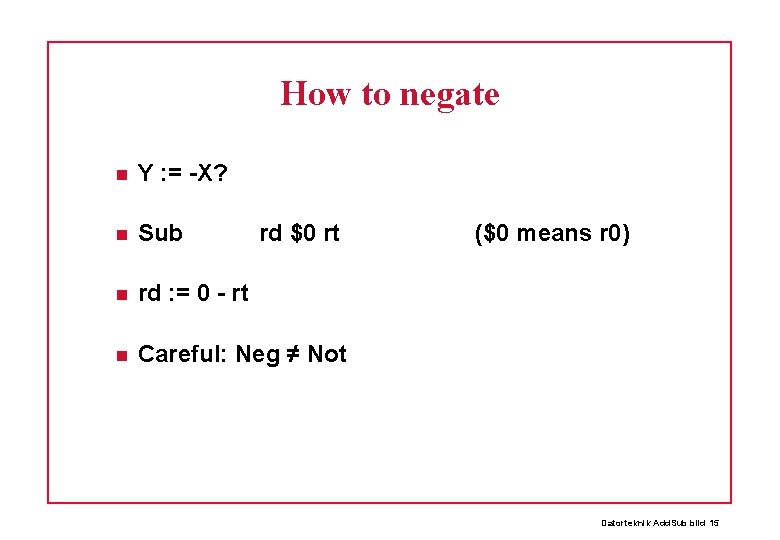

How to negate Y : = -X? Sub rd : = 0 - rt Careful: Neg ≠ Not rd $0 rt ($0 means r 0) Datorteknik Add. Sub bild 15

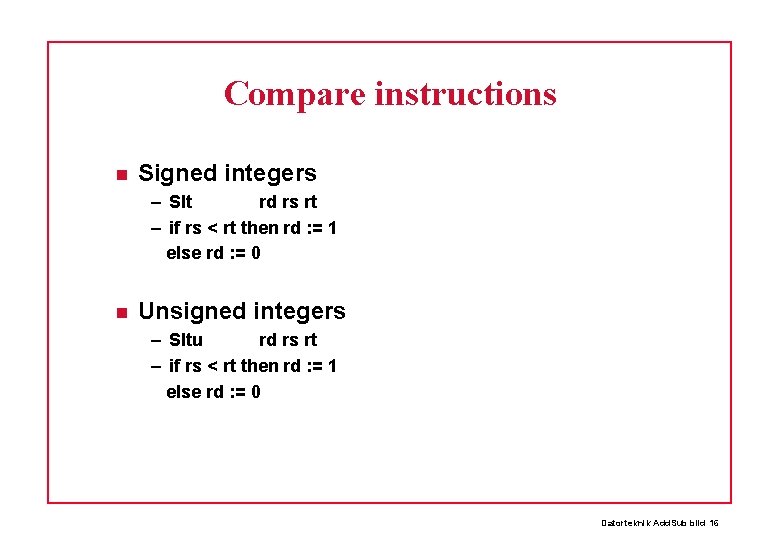

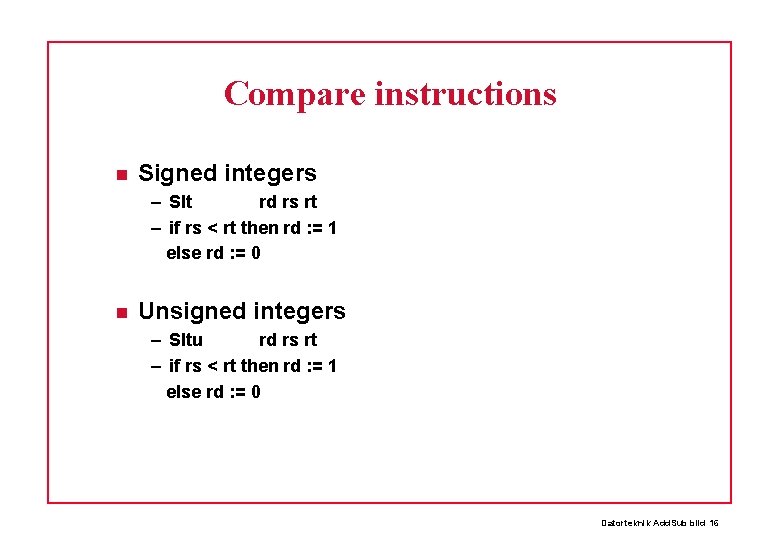

Compare instructions Signed integers – Slt rd rs rt – if rs < rt then rd : = 1 else rd : = 0 Unsigned integers – Sltu rd rs rt – if rs < rt then rd : = 1 else rd : = 0 Datorteknik Add. Sub bild 16

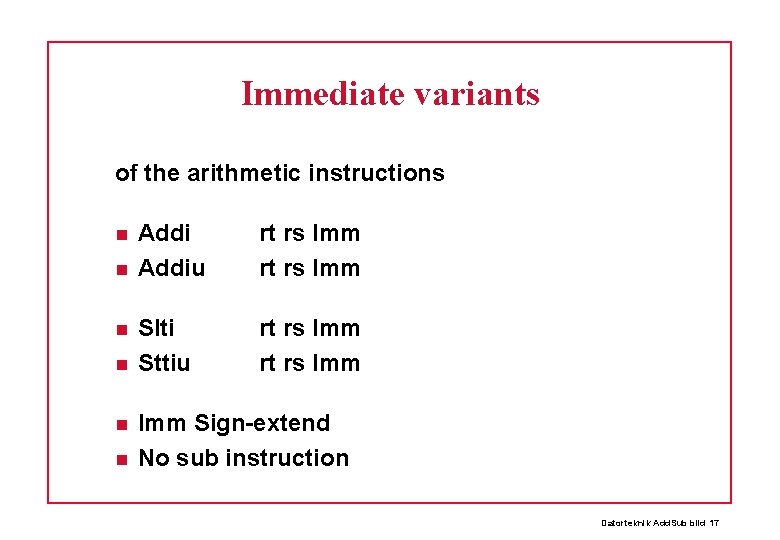

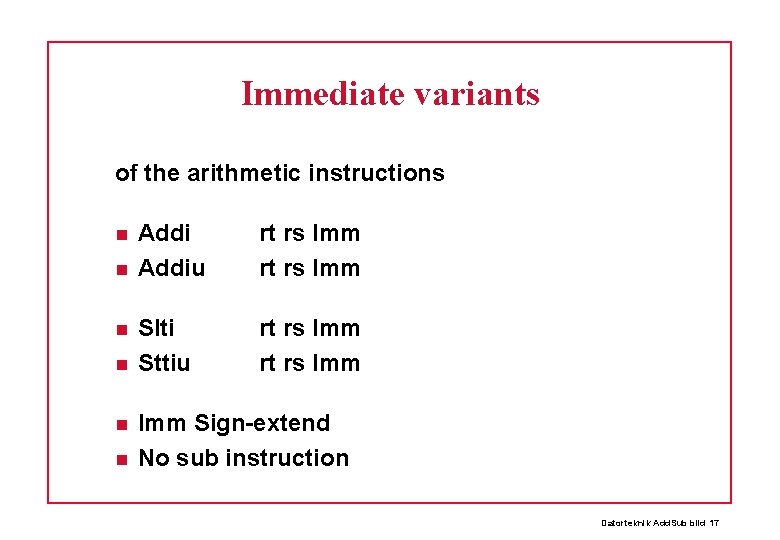

Immediate variants of the arithmetic instructions Addiu rt rs Imm Slti Sttiu rt rs Imm Imm Sign-extend No sub instruction Datorteknik Add. Sub bild 17

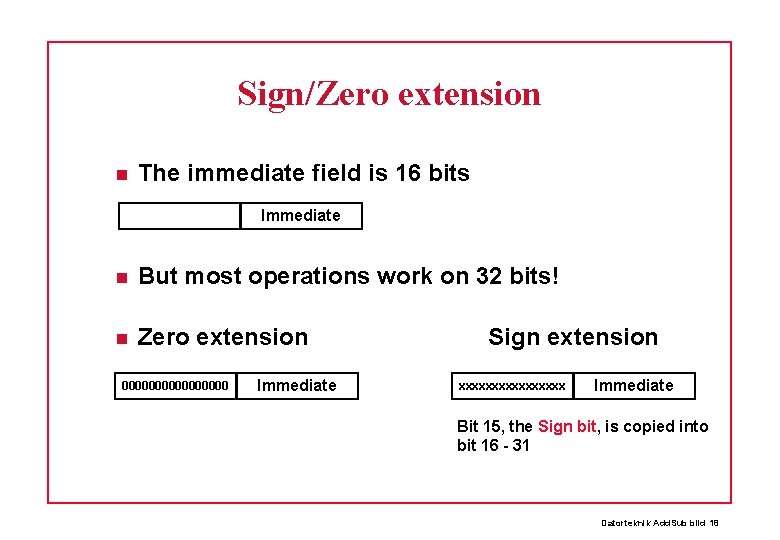

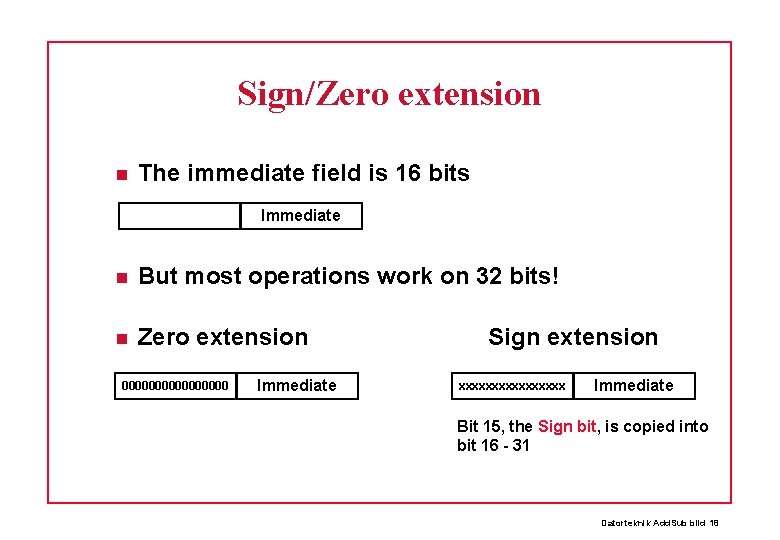

Sign/Zero extension The immediate field is 16 bits Immediate But most operations work on 32 bits! Zero extension 00000000 Immediate Sign extension xxxxxxxx Immediate Bit 15, the Sign bit, is copied into bit 16 - 31 Datorteknik Add. Sub bild 18

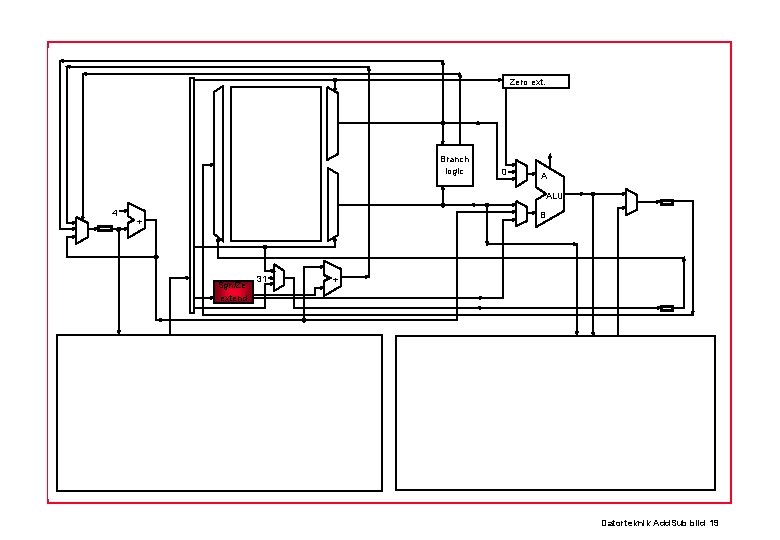

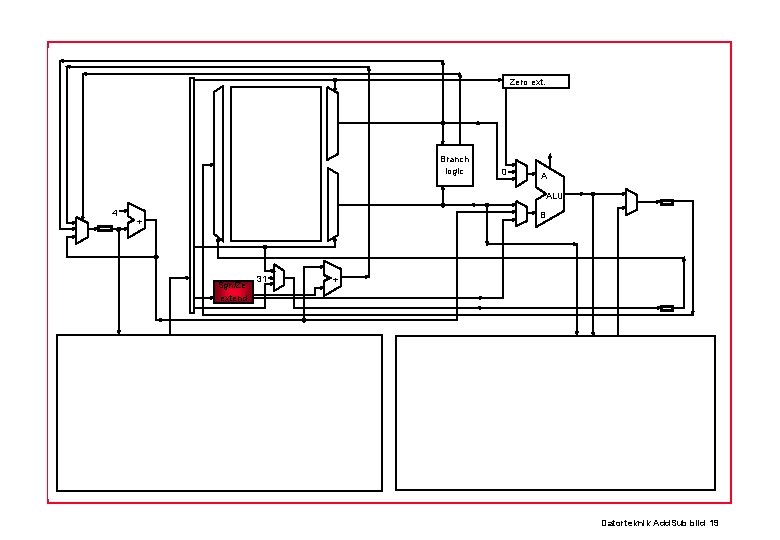

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Datorteknik Add. Sub bild 19

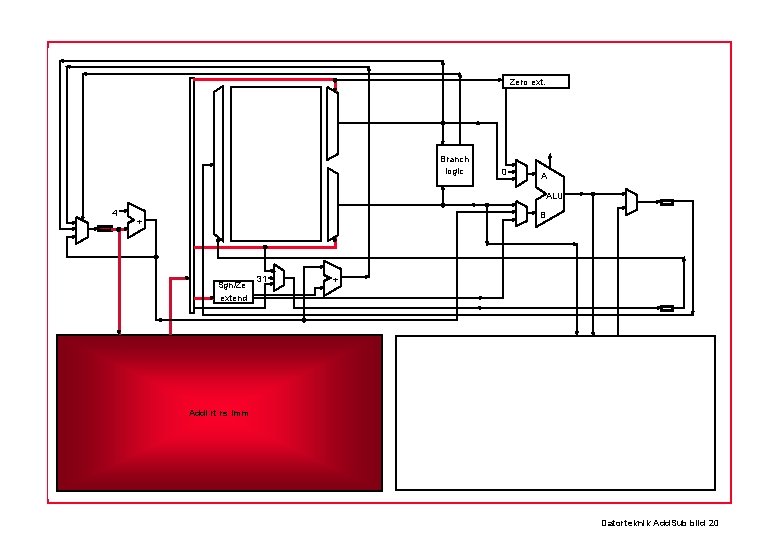

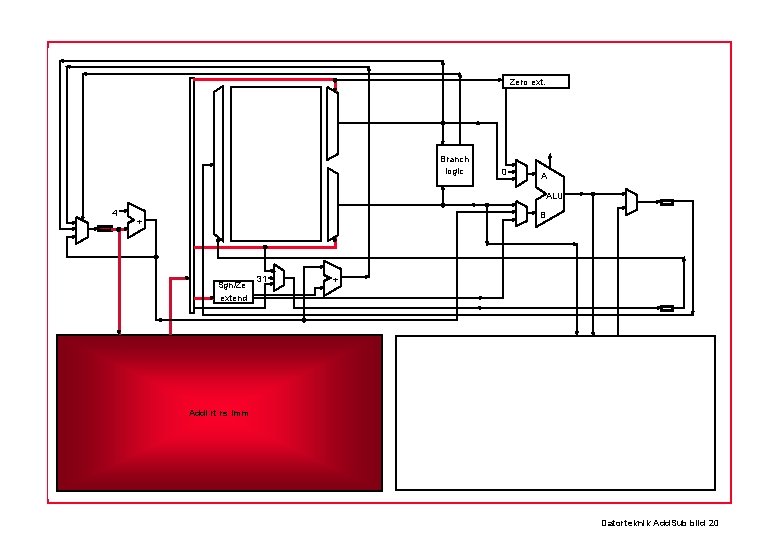

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Addi rt rs Imm Datorteknik Add. Sub bild 20

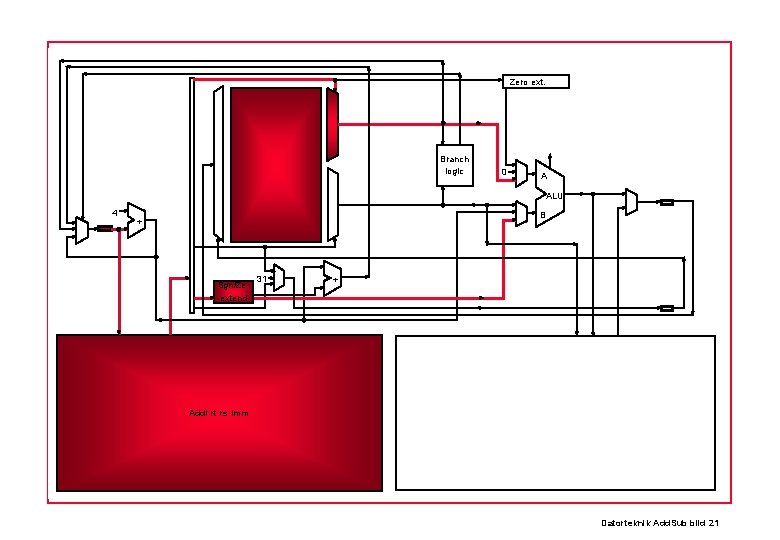

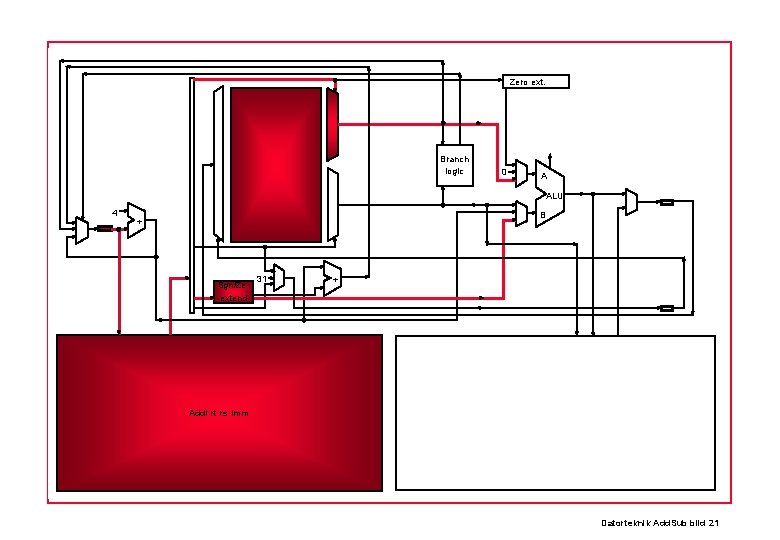

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Addi rt rs Imm Datorteknik Add. Sub bild 21

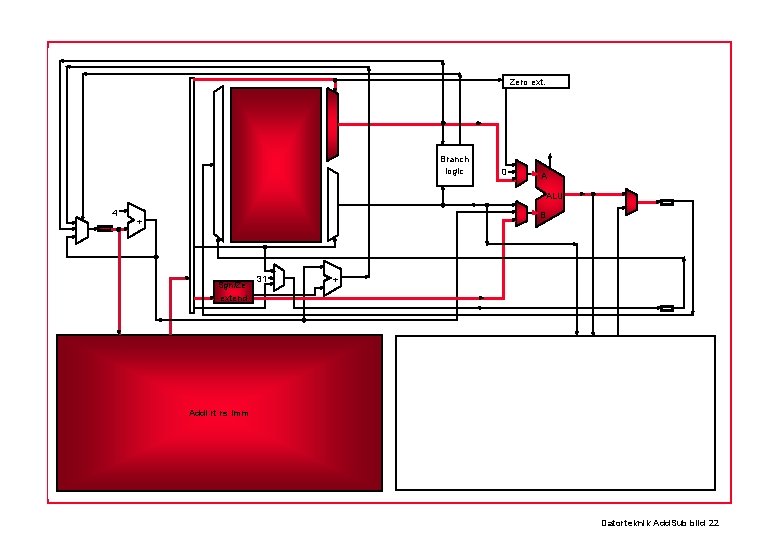

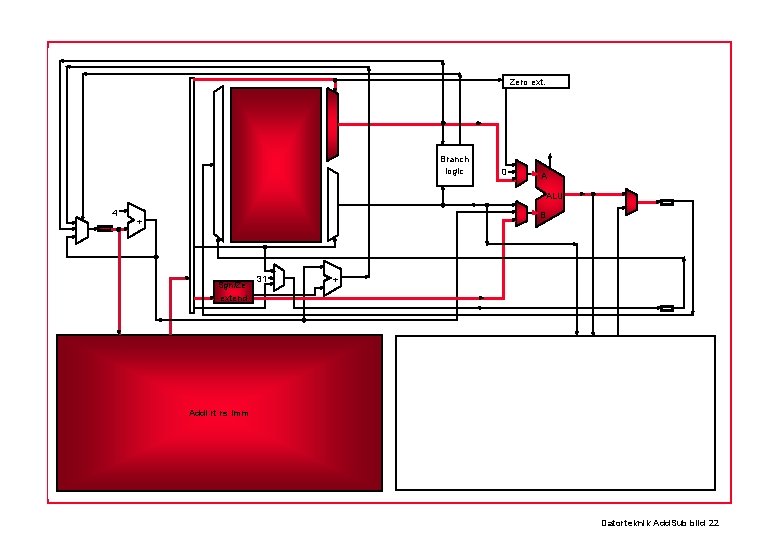

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Addi rt rs Imm Datorteknik Add. Sub bild 22

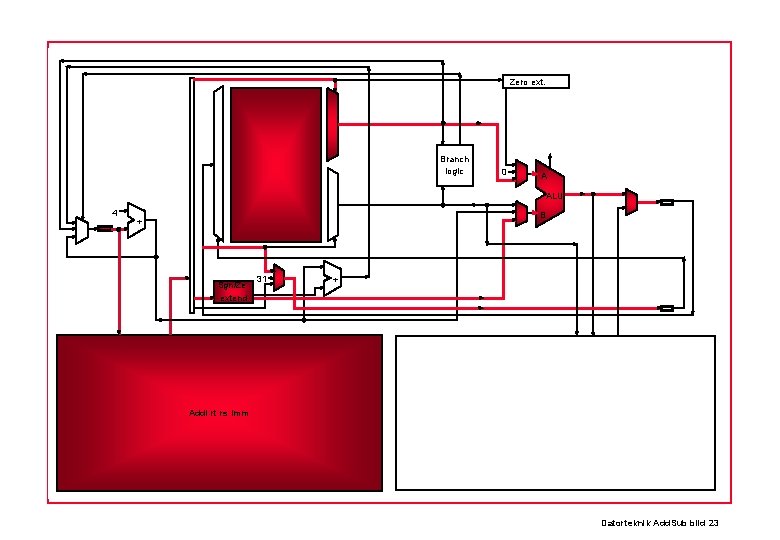

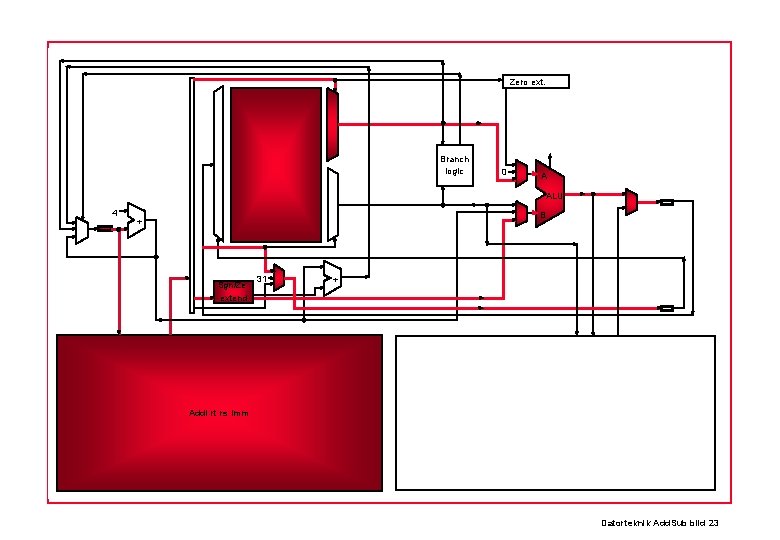

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Addi rt rs Imm Datorteknik Add. Sub bild 23

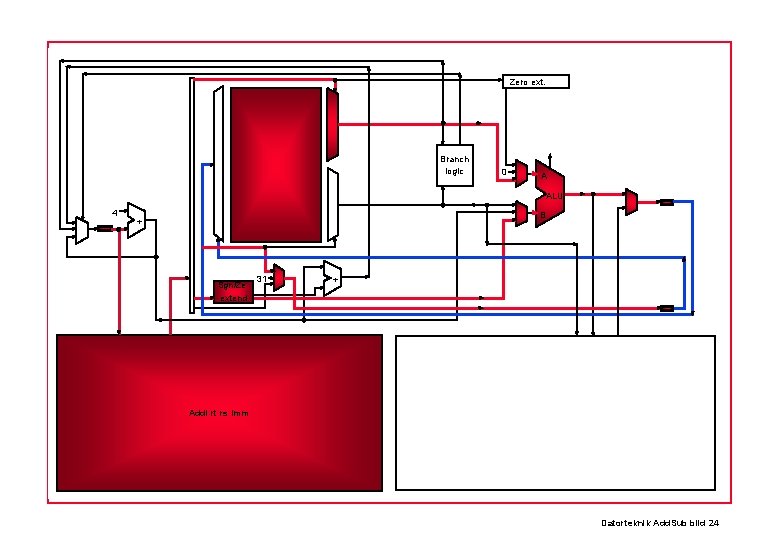

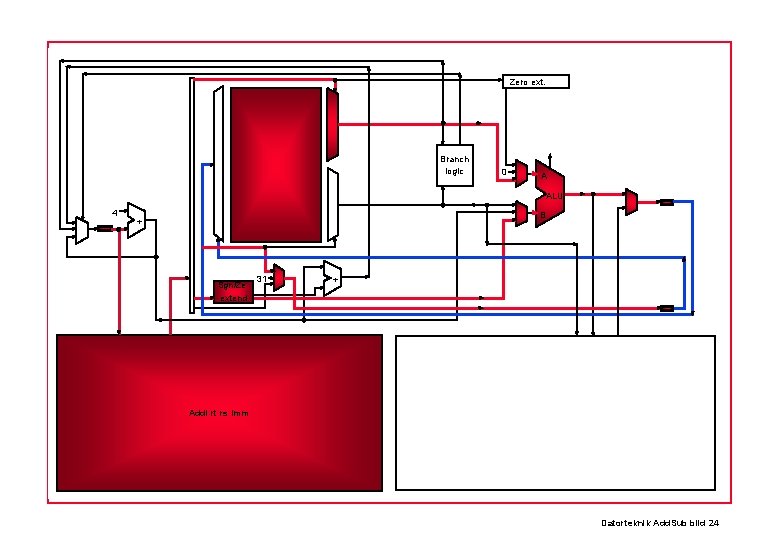

Zero ext. Branch logic 0 A ALU 4 B + Sgn/Ze extend 31 + Addi rt rs Imm Datorteknik Add. Sub bild 24