The Processor Lecture 3 3 Singlecycle Implementation 1

![R-type Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] R-type Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0]](https://slidetodoc.com/presentation_image_h/1d6acff042d111ae0bf72f3cf59cf507/image-4.jpg)

![Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0]](https://slidetodoc.com/presentation_image_h/1d6acff042d111ae0bf72f3cf59cf507/image-11.jpg)

![Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0]](https://slidetodoc.com/presentation_image_h/1d6acff042d111ae0bf72f3cf59cf507/image-12.jpg)

![Adding the Jump Operation Instr[25 -0] Shift left 2 26 28 1 32 0 Adding the Jump Operation Instr[25 -0] Shift left 2 26 28 1 32 0](https://slidetodoc.com/presentation_image_h/1d6acff042d111ae0bf72f3cf59cf507/image-14.jpg)

- Slides: 15

The Processor Lecture 3. 3: Single-cycle Implementation 1

Learning Objectives q Identify the data flow when executing an instruction q Determine the values of control signals when executing an instruction 2

Coverage q Chapter 4. 4, Page 264 -272 3

![Rtype Instruction DataControl Flow 0 Add ALUOp Reg Dst PC Read Address Instr31 0 R-type Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0]](https://slidetodoc.com/presentation_image_h/1d6acff042d111ae0bf72f3cf59cf507/image-4.jpg)

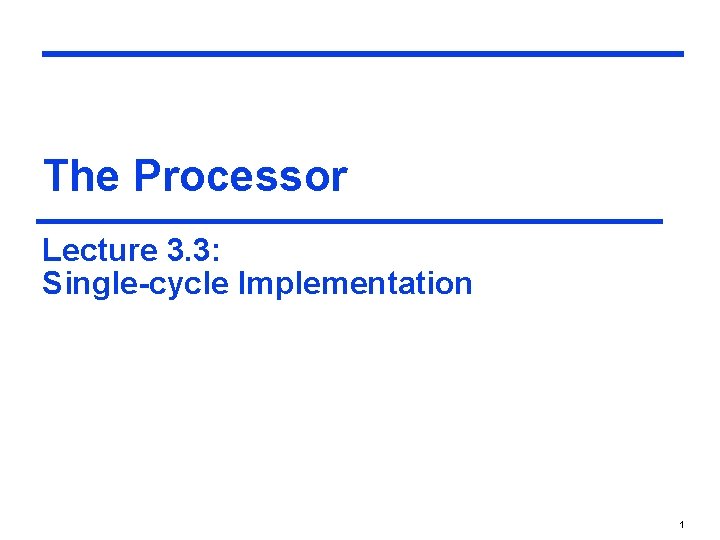

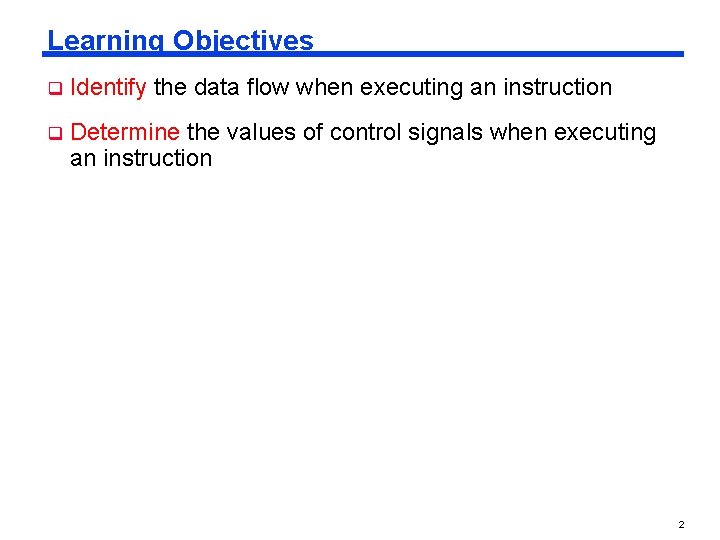

R-type Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 4

R-type Instruction Data/Control Flow (alt. ) 5

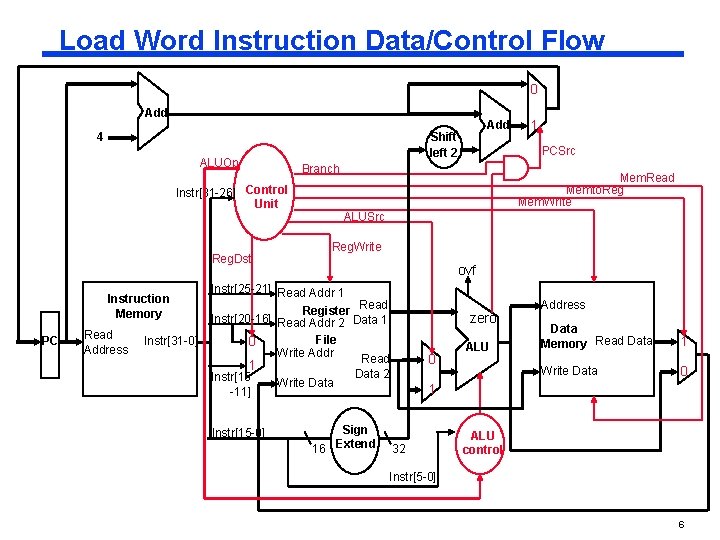

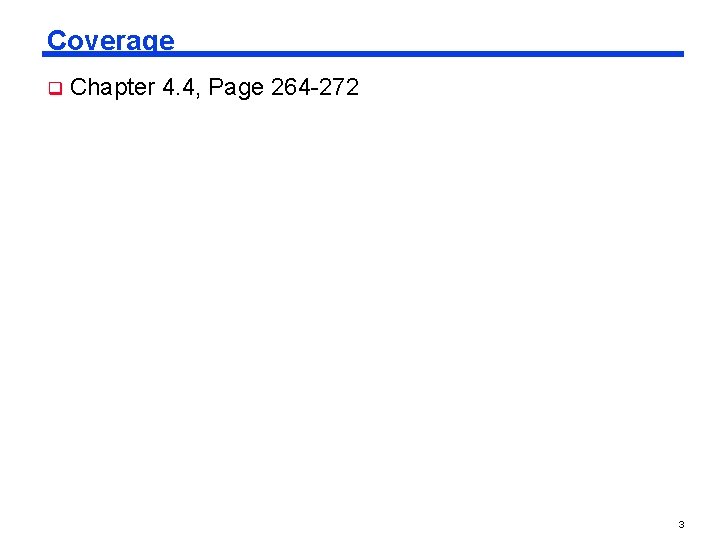

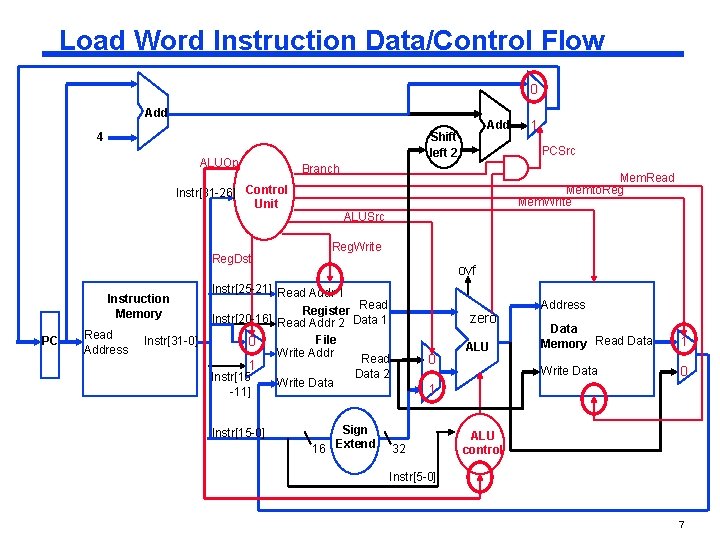

Load Word Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Sign 16 Extend Address Data Memory Read Data 1 Write Data 0 1 32 ALU control Instr[5 -0] 6

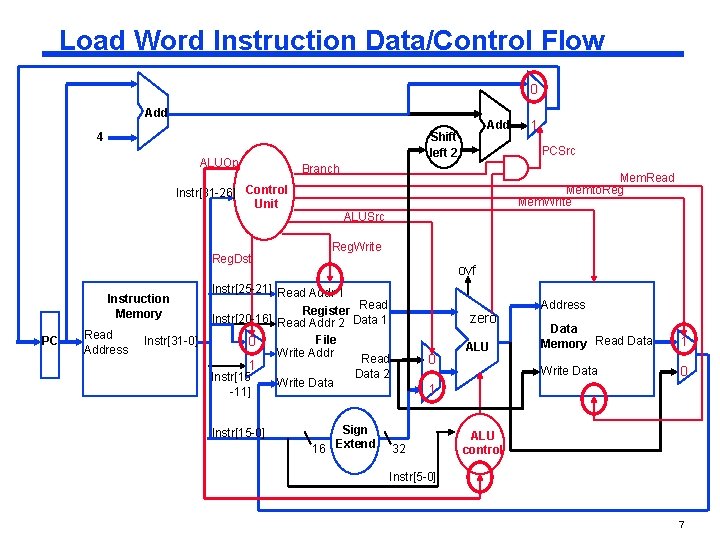

Load Word Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Sign 16 Extend Address Data Memory Read Data 1 Write Data 0 1 32 ALU control Instr[5 -0] 7

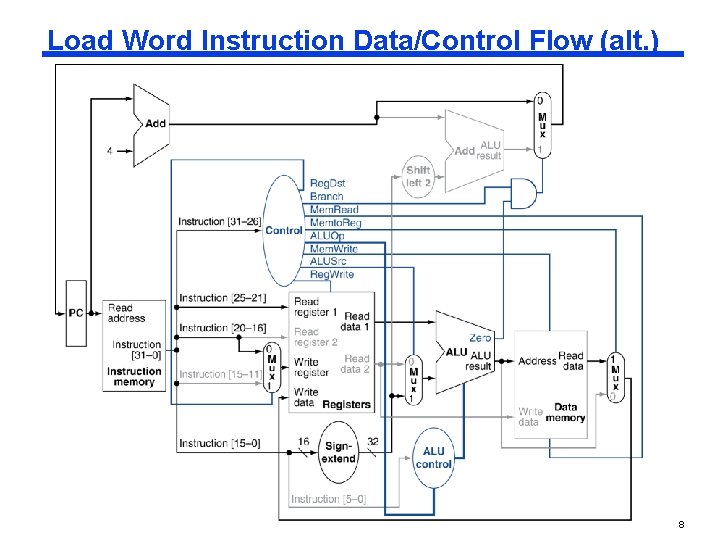

Load Word Instruction Data/Control Flow (alt. ) 8

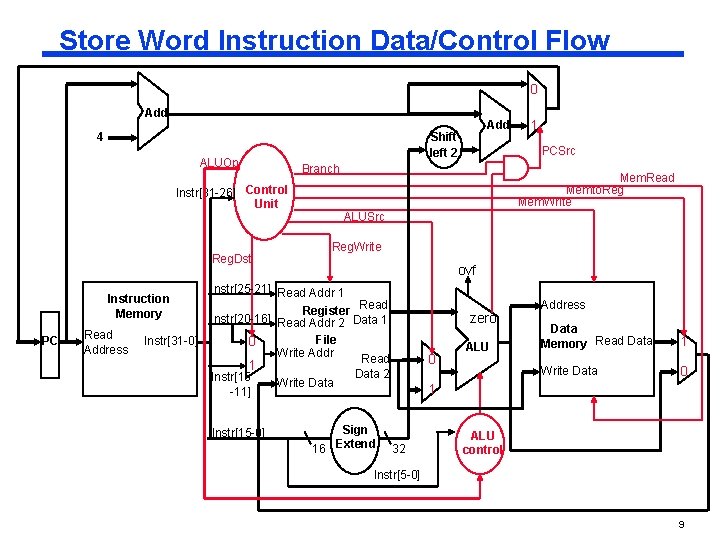

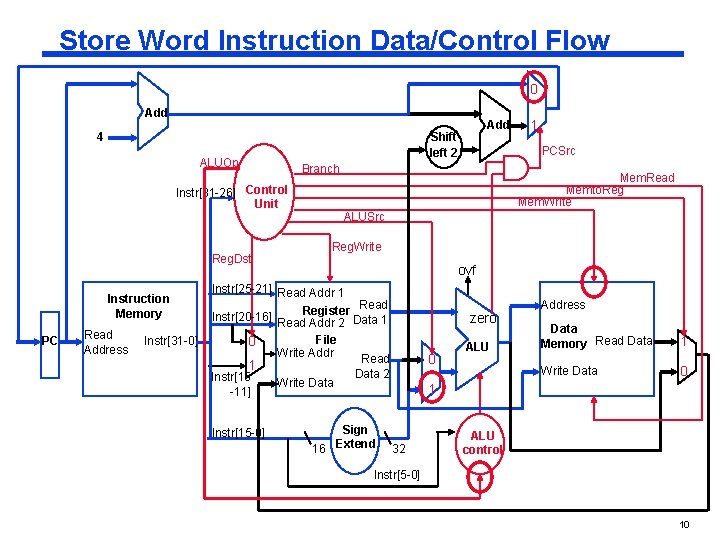

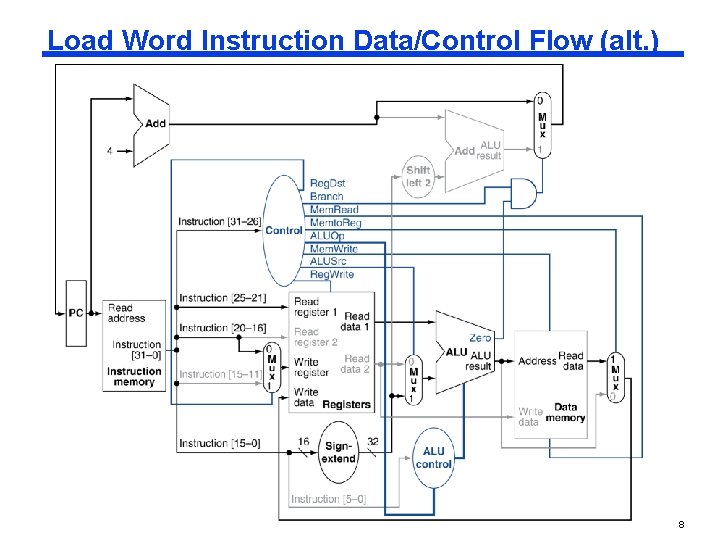

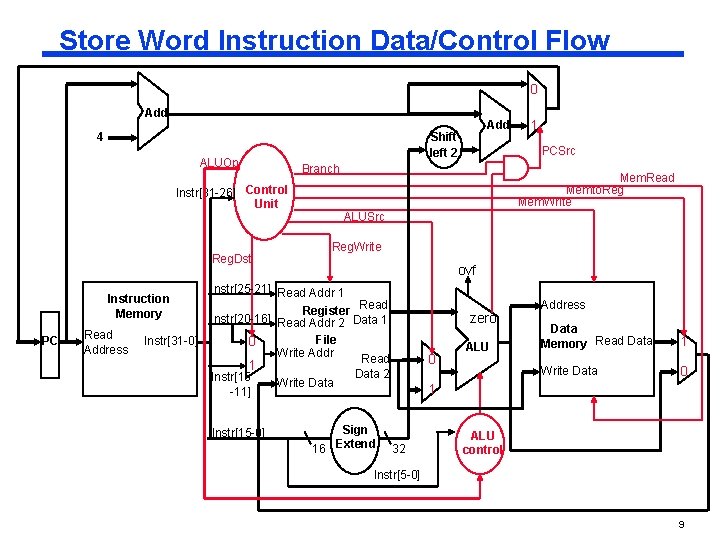

Store Word Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 9

Store Word Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 10

![Branch Instruction DataControl Flow 0 Add ALUOp Reg Dst PC Read Address Instr31 0 Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0]](https://slidetodoc.com/presentation_image_h/1d6acff042d111ae0bf72f3cf59cf507/image-11.jpg)

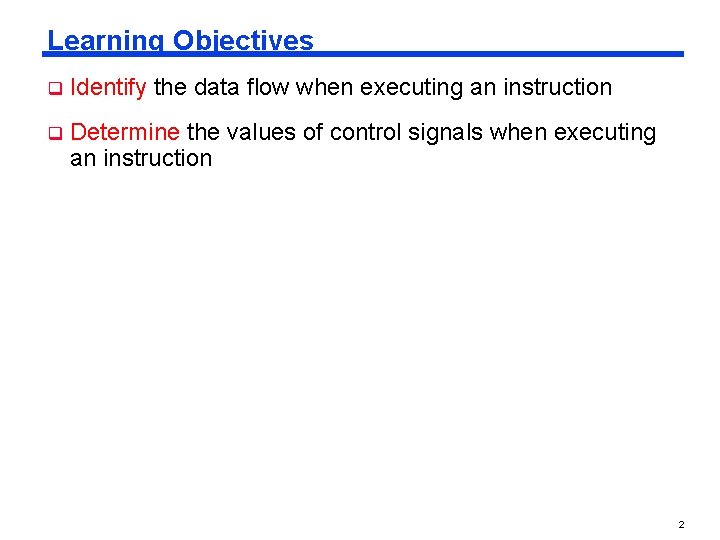

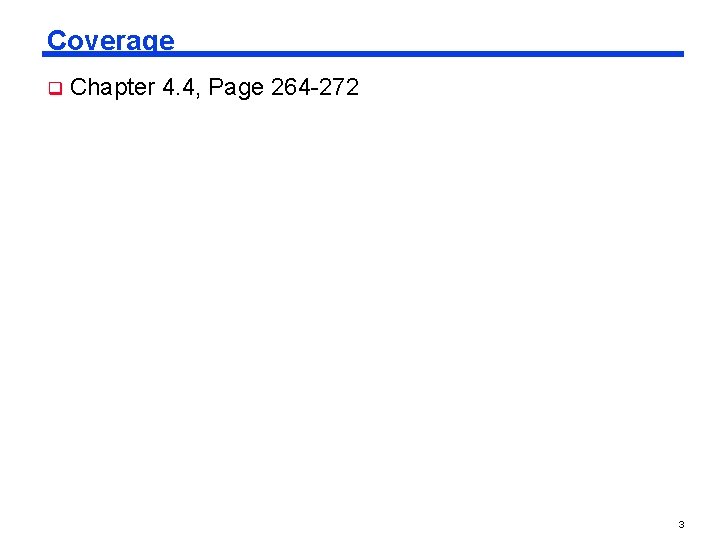

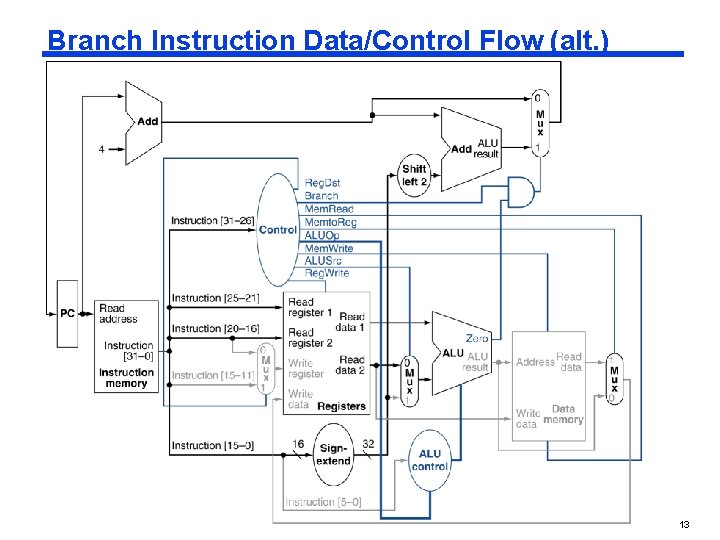

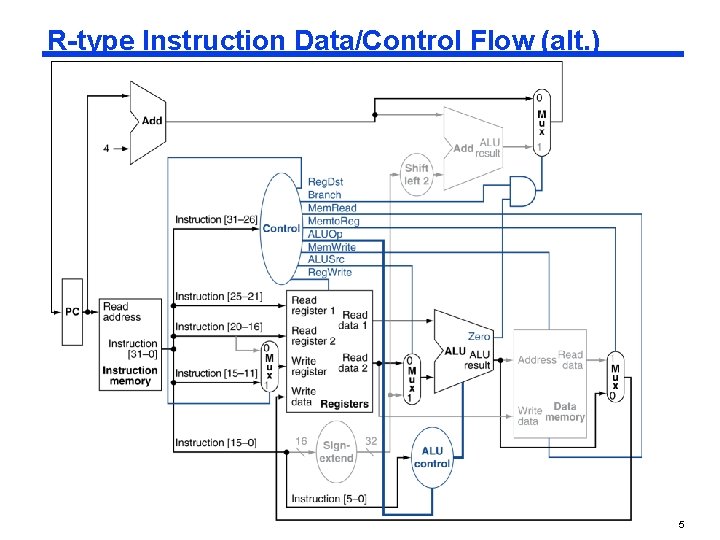

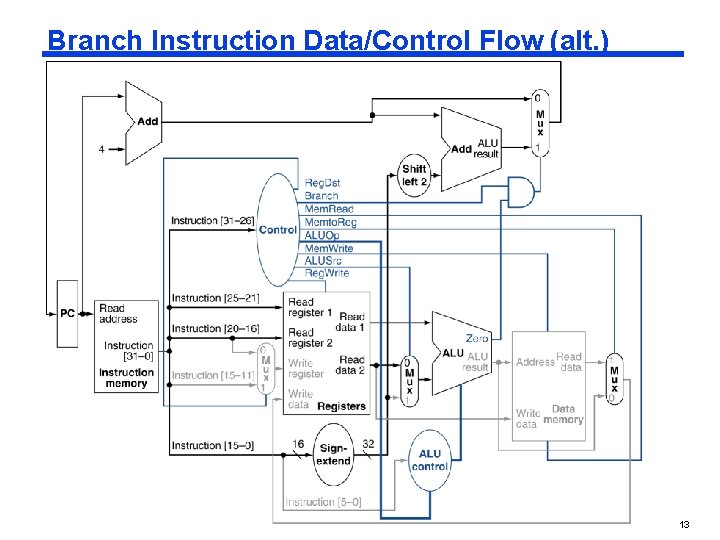

Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 11

![Branch Instruction DataControl Flow 0 Add ALUOp Reg Dst PC Read Address Instr31 0 Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0]](https://slidetodoc.com/presentation_image_h/1d6acff042d111ae0bf72f3cf59cf507/image-12.jpg)

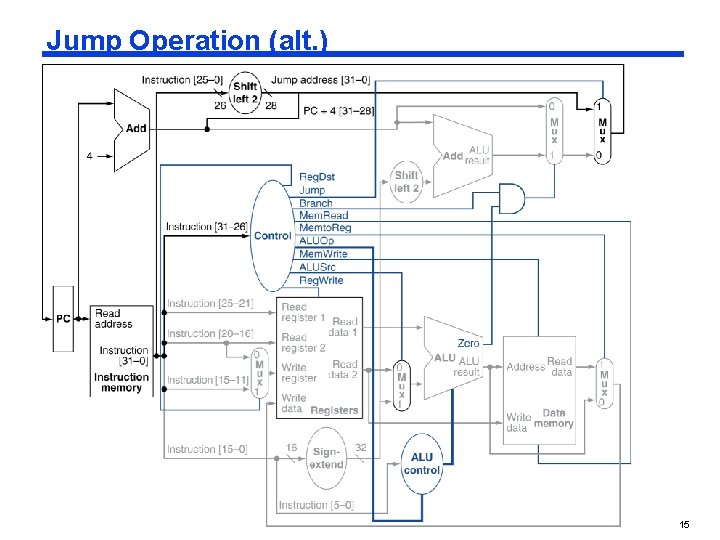

Branch Instruction Data/Control Flow 0 Add ALUOp Reg. Dst PC Read Address Instr[31 -0] Mem. Read Memto. Reg Mem. Write ALUSrc Reg. Write ovf Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read 1 Instr[15 -11] Instr[15 -0] 1 PCSrc Branch Instr[31 -26] Control Unit Instruction Memory Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 12

Branch Instruction Data/Control Flow (alt. ) 13

![Adding the Jump Operation Instr25 0 Shift left 2 26 28 1 32 0 Adding the Jump Operation Instr[25 -0] Shift left 2 26 28 1 32 0](https://slidetodoc.com/presentation_image_h/1d6acff042d111ae0bf72f3cf59cf507/image-14.jpg)

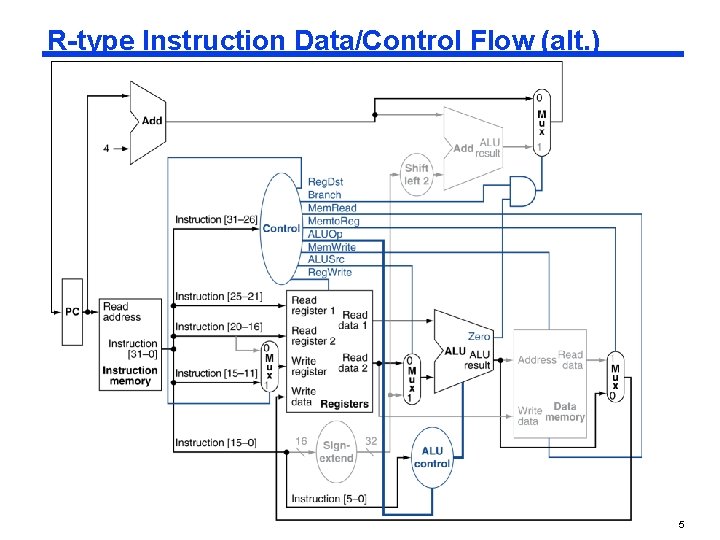

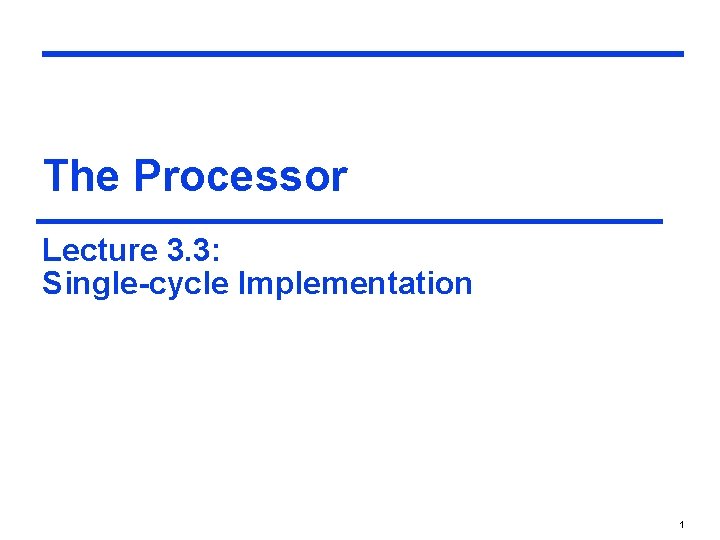

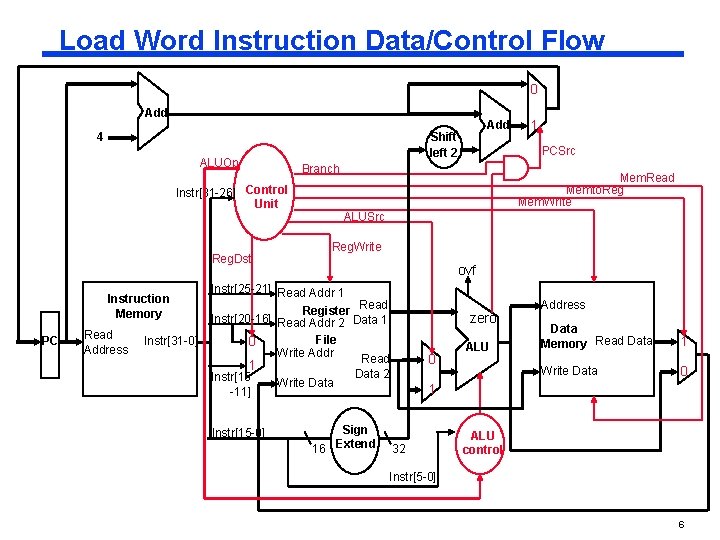

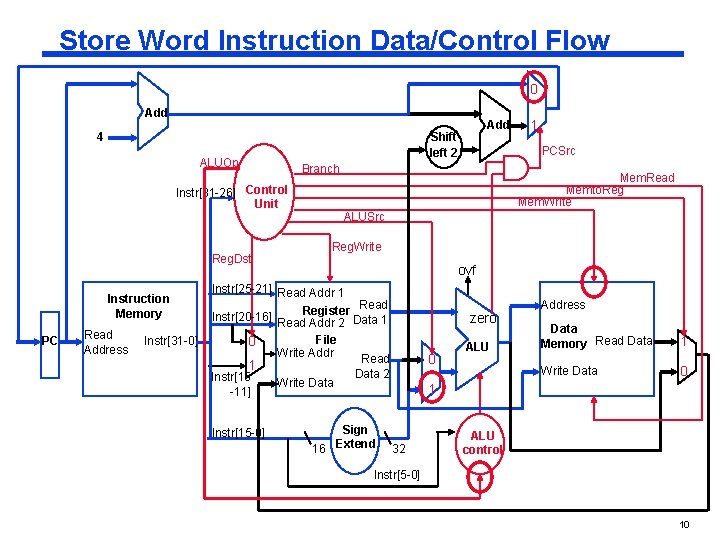

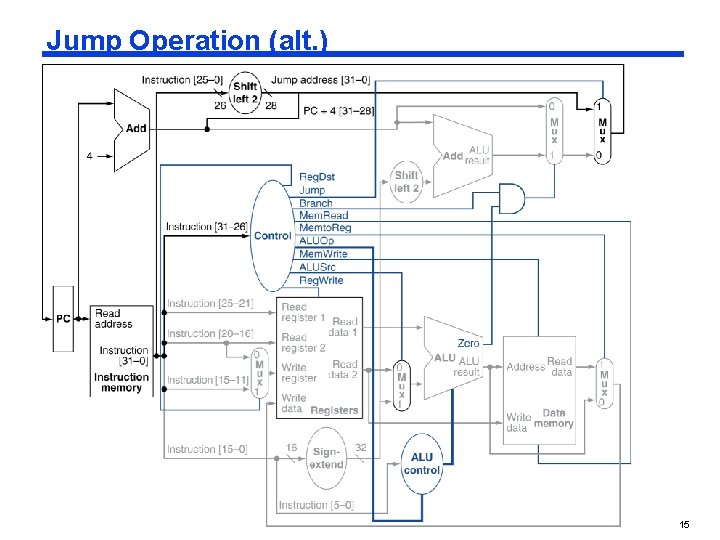

Adding the Jump Operation Instr[25 -0] Shift left 2 26 28 1 32 0 PC+4[31 -28] 0 Add ALUOp Branch Instr[31 -26] Control Unit Reg. Dst Instruction Memory PC Read Address Instr[31 -0] Jump PCSrc ALUSrc Reg. Write ovf 1 Instr[15 -0] 1 Mem. Read Memto. Reg Mem. Write Instr[25 -21] Read Addr 1 Register Read Instr[20 -16] Read Addr 2 Data 1 File 0 Write Addr Read Instr[15 -11] Add Shift left 2 4 Write Data zero 0 ALU Data 2 Address Data Memory Read Data 1 Write Data 0 1 Sign 16 Extend 32 ALU control Instr[5 -0] 14

Jump Operation (alt. ) 15