The pixel research activities at SDU Jian LIU

- Slides: 30

The pixel research activities at SDU Jian LIU (刘剑) Shandong University liuj@hepg. sdu. edu. cn IHEP, Beijing, 27 Apr 2017

Outline • Study of HV/HR CMOS sensors for the ATLAS ITk collaborating with CPPM, Marseille • Research progress of the CMOS sensors for the CEPC silicon detectors and future plan • Conclusion and perspectives 27/04/2017 J. LIU 2

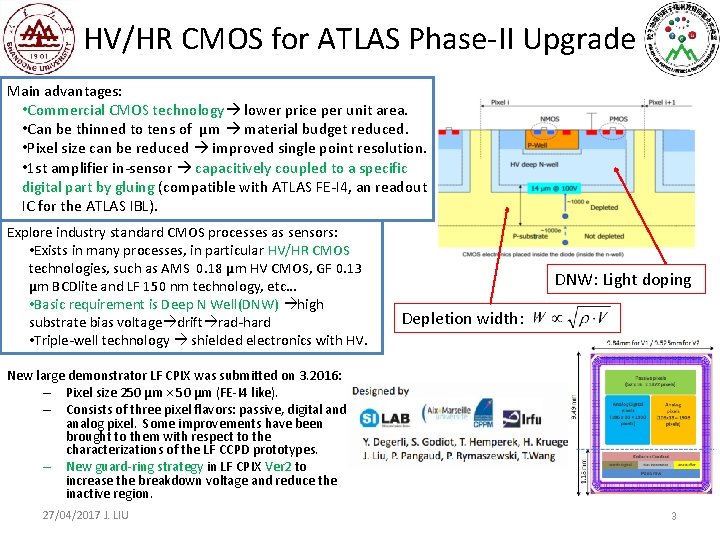

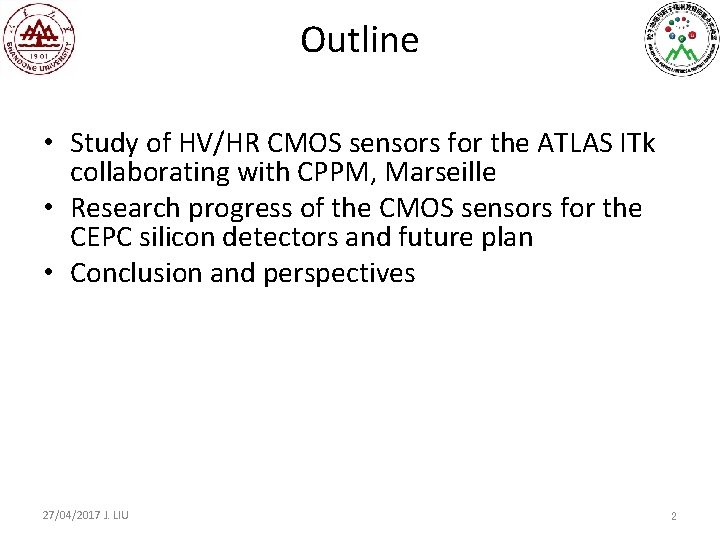

HV/HR CMOS for ATLAS Phase-II Upgrade Main advantages: • Commercial CMOS technology lower price per unit area. • Can be thinned to tens of µm material budget reduced. • Pixel size can be reduced improved single point resolution. • 1 st amplifier in-sensor capacitively coupled to a specific digital part by gluing (compatible with ATLAS FE-I 4, an readout IC for the ATLAS IBL). Explore industry standard CMOS processes as sensors: • Exists in many processes, in particular HV/HR CMOS technologies, such as AMS 0. 18 µm HV CMOS, GF 0. 13 µm BCDlite and LF 150 nm technology, etc… • Basic requirement is Deep N Well(DNW) high substrate bias voltage drift rad-hard • Triple-well technology shielded electronics with HV. DNW: Light doping Depletion width: New large demonstrator LF CPIX was submitted on 3. 2016: – Pixel size 250 µm × 50 µm (FE-I 4 like). – Consists of three pixel flavors: passive, digital and analog pixel. Some improvements have been brought to them with respect to the characterizations of the LF CCPD prototypes. – New guard-ring strategy in LF CPIX Ver 2 to increase the breakdown voltage and reduce the inactive region. 27/04/2017 J. LIU 3

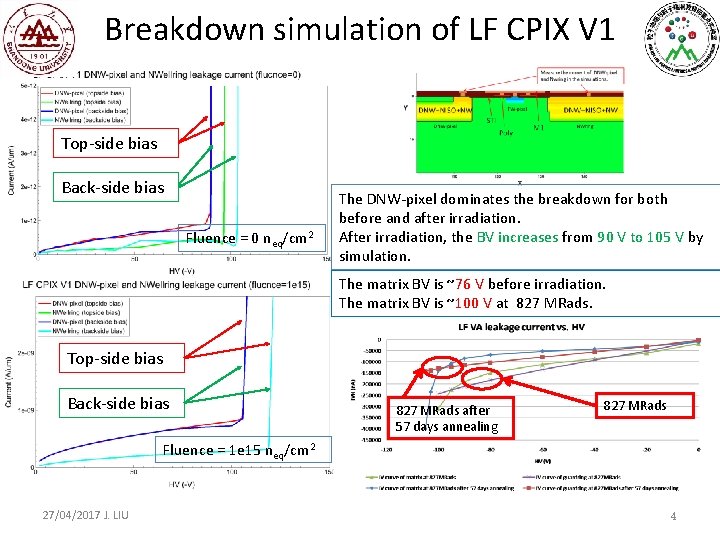

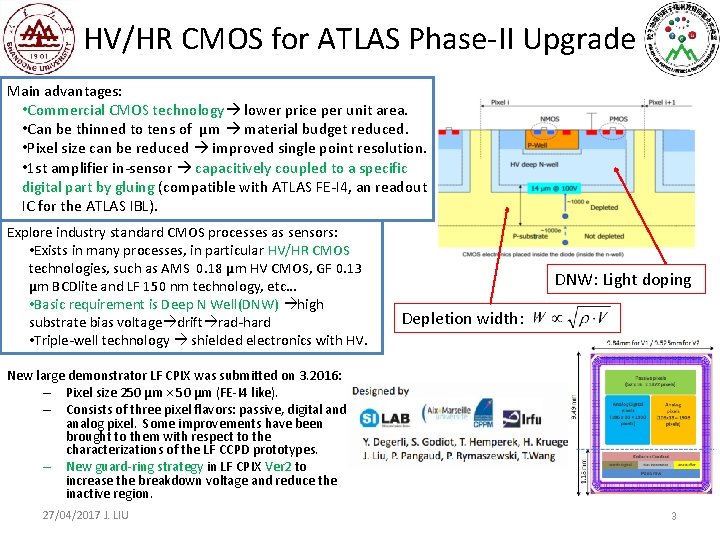

Breakdown simulation of LF CPIX V 1 Top-side bias Back-side bias Fluence = 0 neq/cm 2 The DNW-pixel dominates the breakdown for both before and after irradiation. After irradiation, the BV increases from 90 V to 105 V by simulation. The matrix BV is ~76 V before irradiation. The matrix BV is ~100 V at 827 MRads. Top-side bias Back-side bias 827 MRads after 57 days annealing 827 MRads Fluence = 1 e 15 neq/cm 2 27/04/2017 J. LIU 4

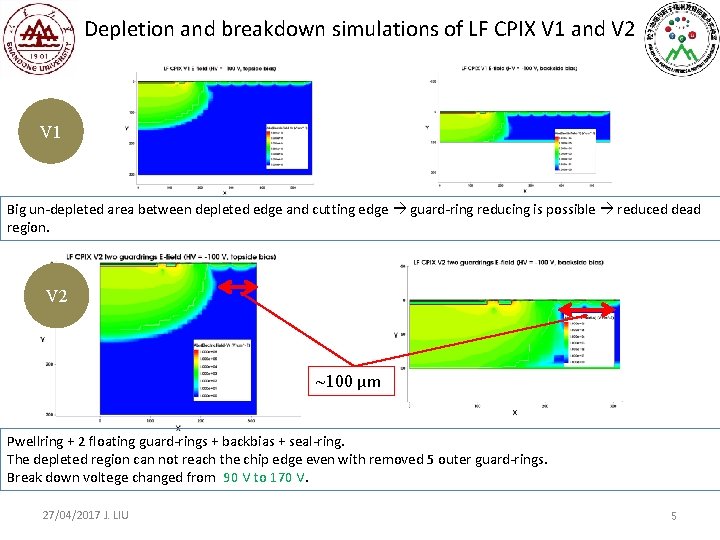

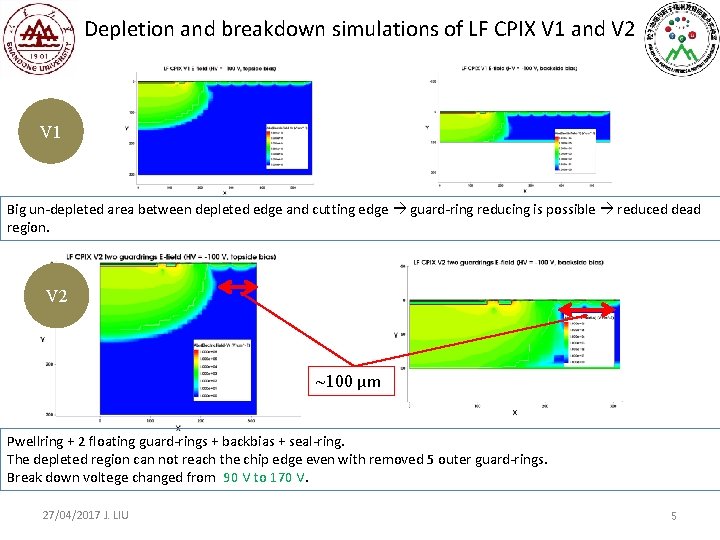

Depletion and breakdown simulations of LF CPIX V 1 and V 2 V 1 Big un-depleted area between depleted edge and cutting edge guard-ring reducing is possible reduced dead region. V 2 ~100 µm Pwellring + 2 floating guard-rings + backbias + seal-ring. The depleted region can not reach the chip edge even with removed 5 outer guard-rings. Break down voltege changed from 90 V to 170 V. 27/04/2017 J. LIU 5

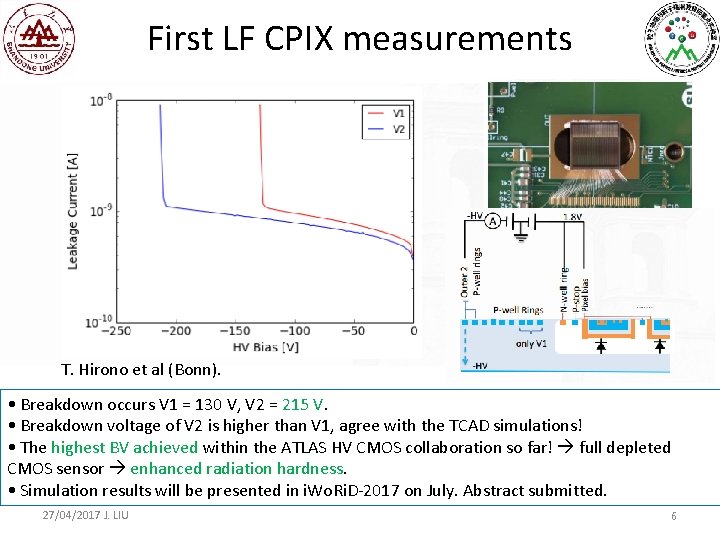

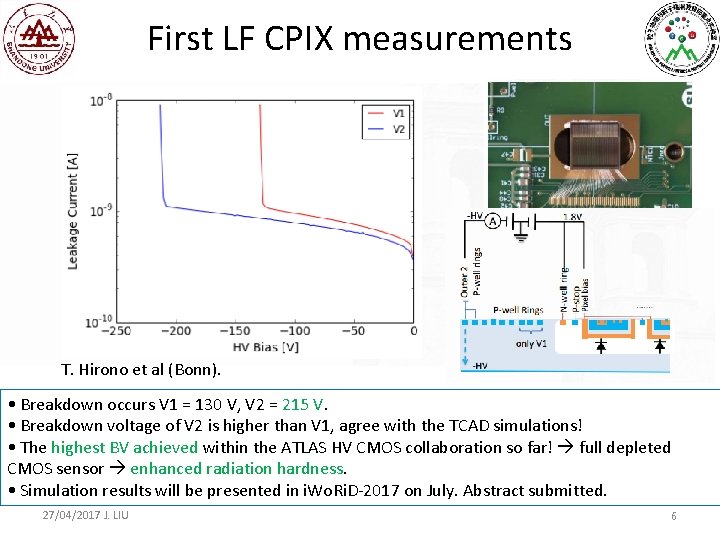

First LF CPIX measurements T. Hirono et al (Bonn). • Breakdown occurs V 1 = 130 V, V 2 = 215 V. • Breakdown voltage of V 2 is higher than V 1, agree with the TCAD simulations! • The highest BV achieved within the ATLAS HV CMOS collaboration so far! full depleted CMOS sensor enhanced radiation hardness. • Simulation results will be presented in i. Wo. Ri. D-2017 on July. Abstract submitted. 27/04/2017 J. LIU 6

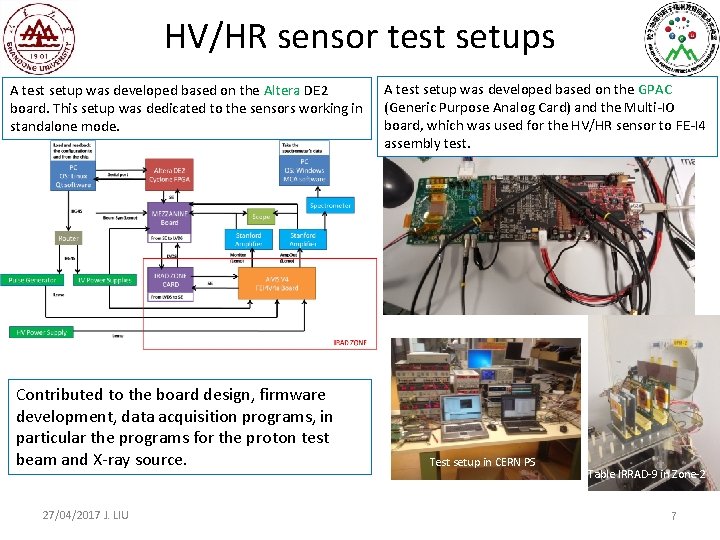

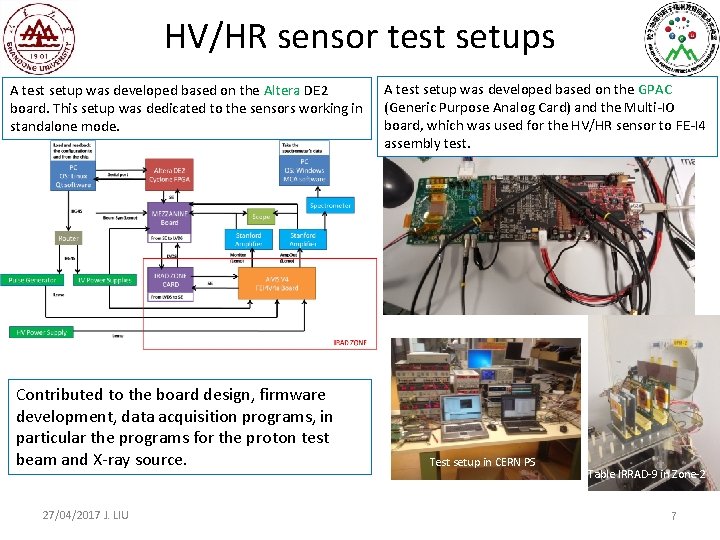

HV/HR sensor test setups A test setup was developed based on the Altera DE 2 board. This setup was dedicated to the sensors working in standalone mode. Contributed to the board design, firmware development, data acquisition programs, in particular the programs for the proton test beam and X-ray source. 27/04/2017 J. LIU A test setup was developed based on the GPAC (Generic Purpose Analog Card) and the Multi-IO board, which was used for the HV/HR sensor to FE-I 4 assembly test. Test setup in CERN PS Table IRRAD-9 in Zone-2 7

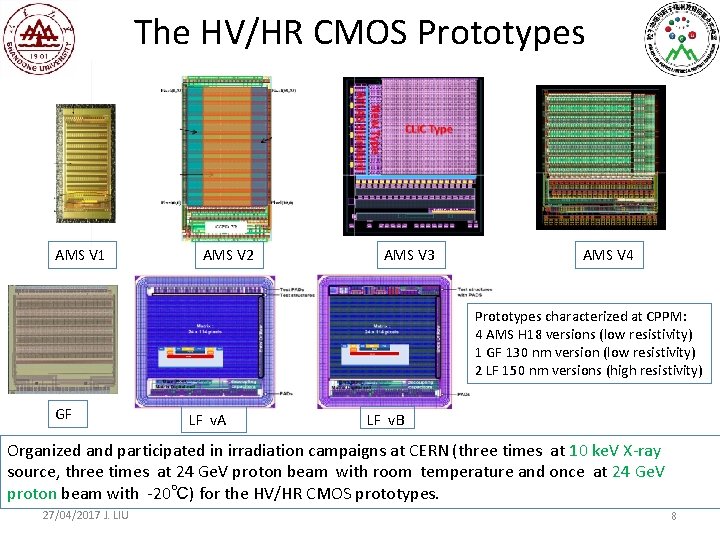

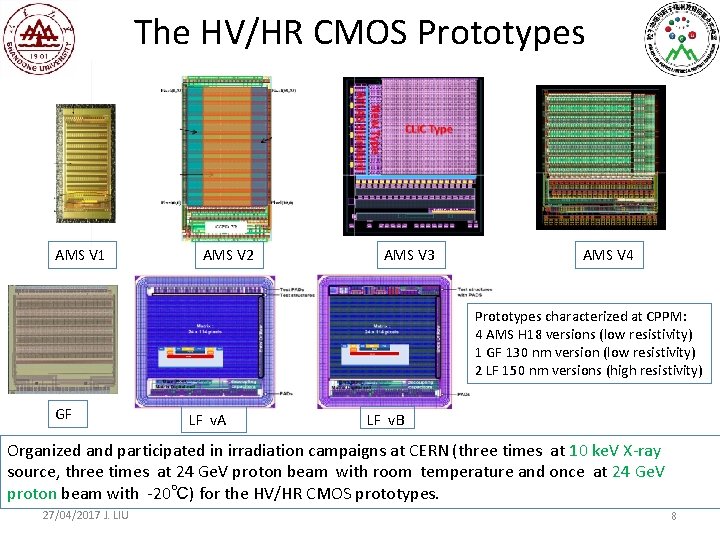

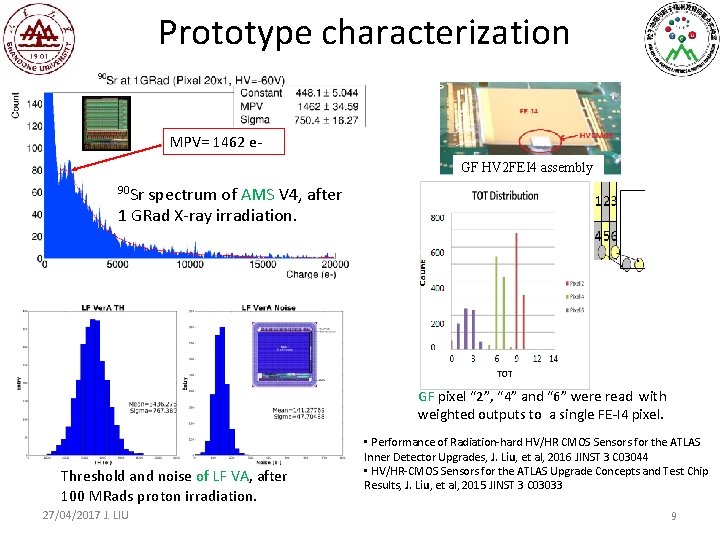

The HV/HR CMOS Prototypes AMS V 1 AMS V 2 AMS V 3 AMS V 4 Prototypes characterized at CPPM: 4 AMS H 18 versions (low resistivity) 1 GF 130 nm version (low resistivity) 2 LF 150 nm versions (high resistivity) GF LF v. A LF v. B Organized and participated in irradiation campaigns at CERN (three times at 10 ke. V X-ray source, three times at 24 Ge. V proton beam with room temperature and once at 24 Ge. V proton beam with -20℃) for the HV/HR CMOS prototypes. 27/04/2017 J. LIU 8

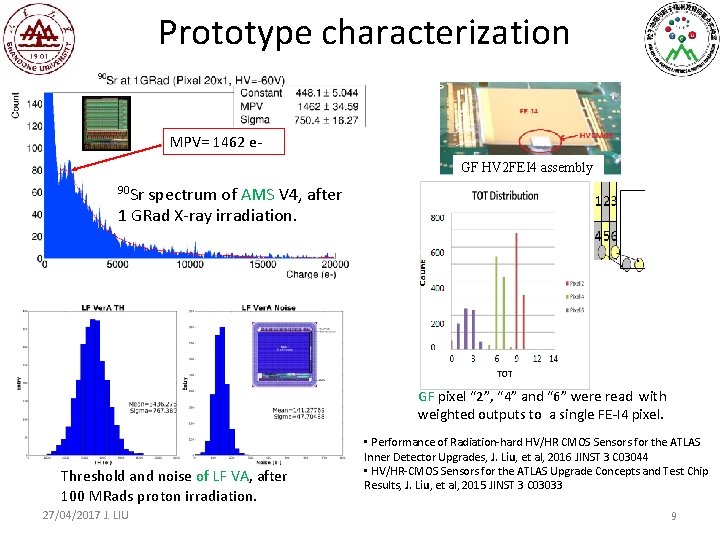

Prototype characterization MPV= 1462 e. GF HV 2 FEI 4 assembly 90 Sr spectrum of AMS V 4, after 1 GRad X-ray irradiation. GF pixel “ 2”, “ 4” and “ 6” were read with weighted outputs to a single FE-I 4 pixel. Threshold and noise of LF VA, after 100 MRads proton irradiation. 27/04/2017 J. LIU • Performance of Radiation-hard HV/HR CMOS Sensors for the ATLAS Inner Detector Upgrades, J. Liu, et al, 2016 JINST 3 C 03044 • HV/HR-CMOS Sensors for the ATLAS Upgrade Concepts and Test Chip Results, J. Liu, et al, 2015 JINST 3 C 03033 9

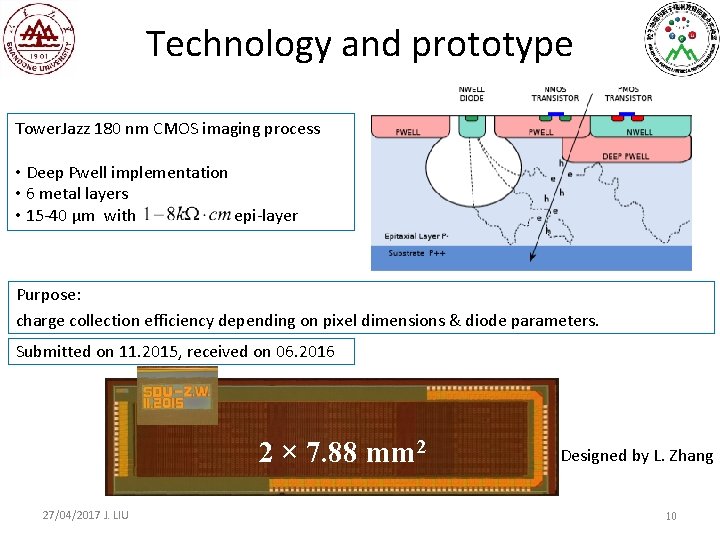

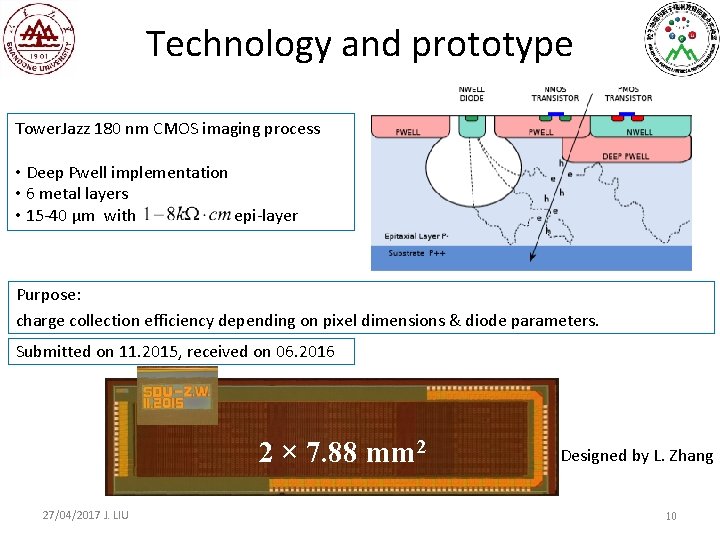

Technology and prototype Tower. Jazz 180 nm CMOS imaging process • Deep Pwell implementation • 6 metal layers • 15 -40 µm with epi-layer Purpose: charge collection efficiency depending on pixel dimensions & diode parameters. Submitted on 11. 2015, received on 06. 2016 2 × 7. 88 mm 2 27/04/2017 J. LIU Designed by L. Zhang 10

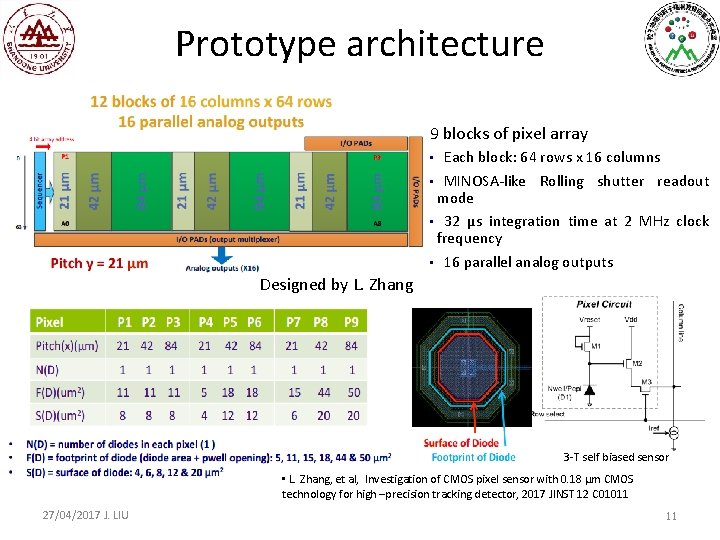

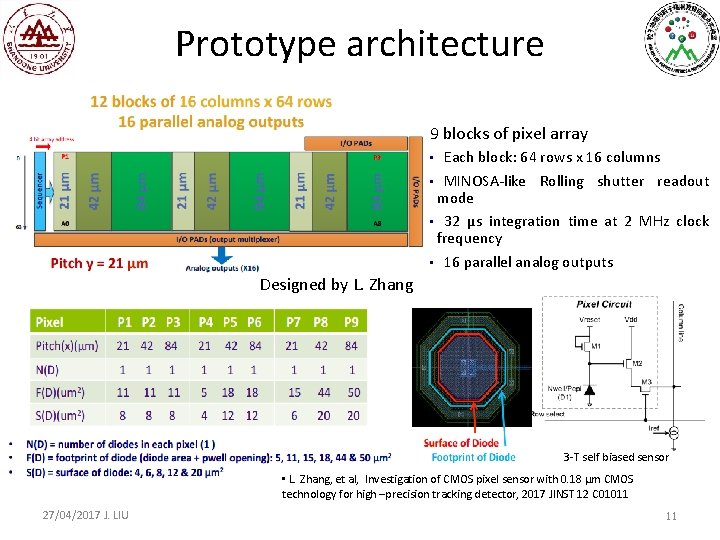

Prototype architecture 9 blocks of pixel array Each block: 64 rows x 16 columns • MINOSA-like Rolling shutter readout 2 mode • 32 µs integration time at 2 MHz clock frequency • 16 parallel analog outputs • 2 × 7. 88 mm Designed by L. Zhang 3 -T self biased sensor • L. Zhang, et al, Investigation of CMOS pixel sensor with 0. 18 µm CMOS technology for high –precision tracking detector, 2017 JINST 12 C 01011 27/04/2017 J. LIU 11

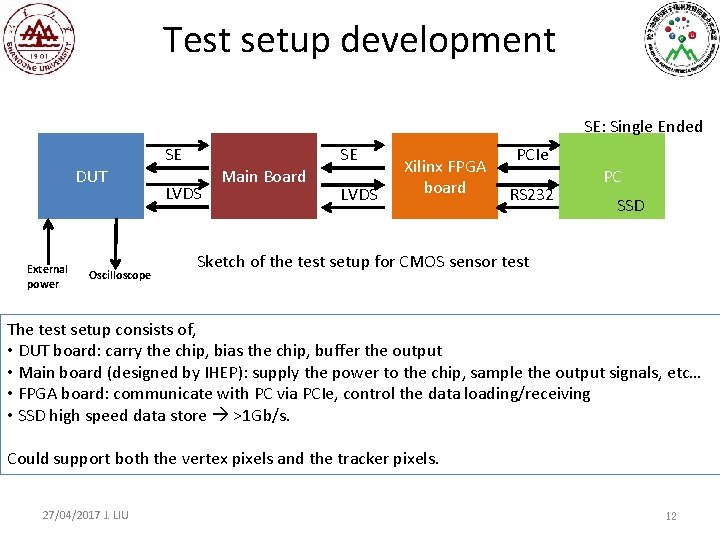

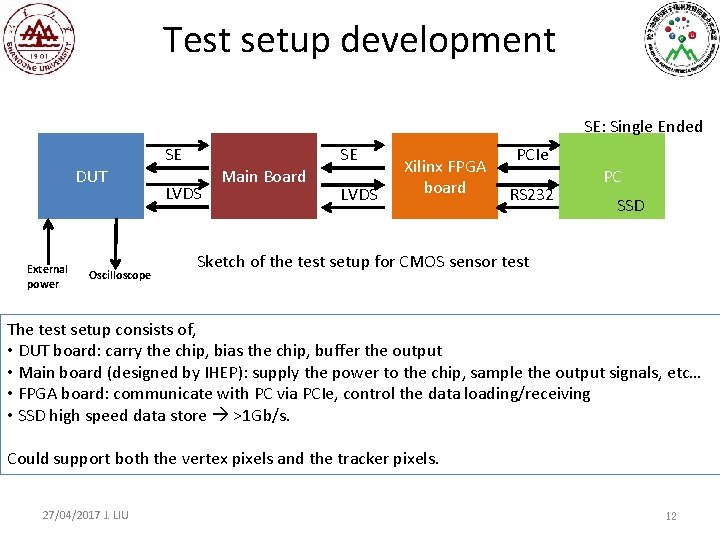

Test setup development SE: Single Ended SE DUT External power Oscilloscope SE LVDS Main Board LVDS Xilinx FPGA board PCIe RS 232 PC SSD Sketch of the test setup for CMOS sensor test The test setup consists of, • DUT board: carry the chip, bias the chip, buffer the output • Main board (designed by IHEP): supply the power to the chip, sample the output signals, etc… • FPGA board: communicate with PC via PCIe, control the data loading/receiving • SSD high speed data store >1 Gb/s. Could support both the vertex pixels and the tracker pixels. 27/04/2017 J. LIU 12

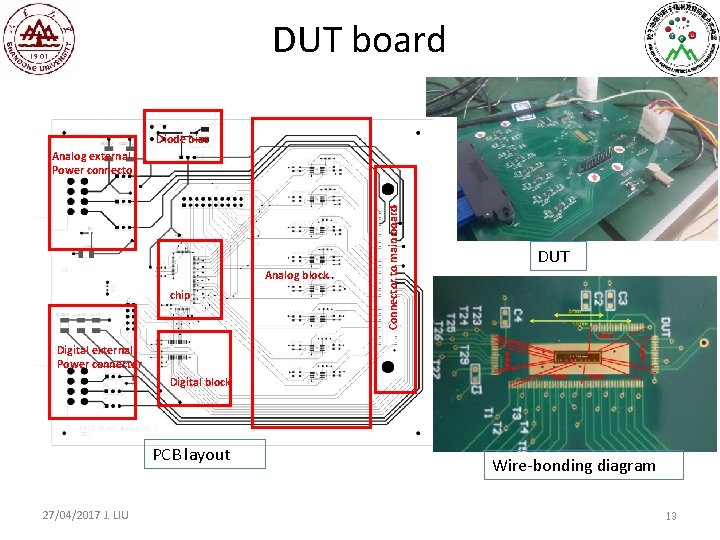

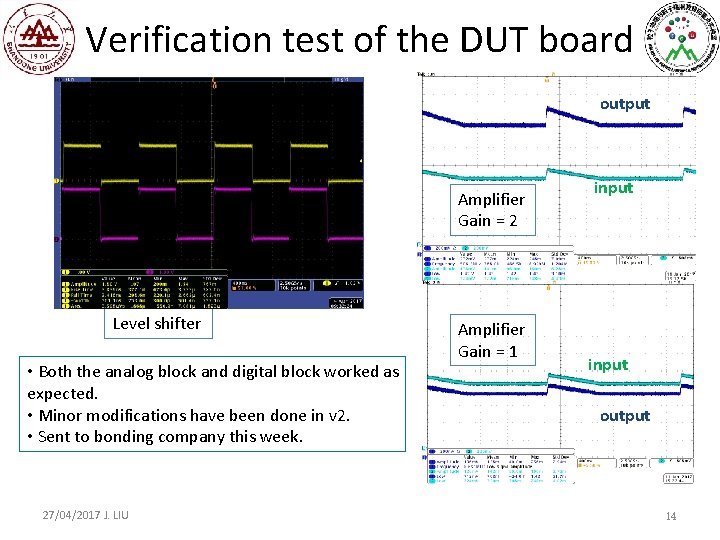

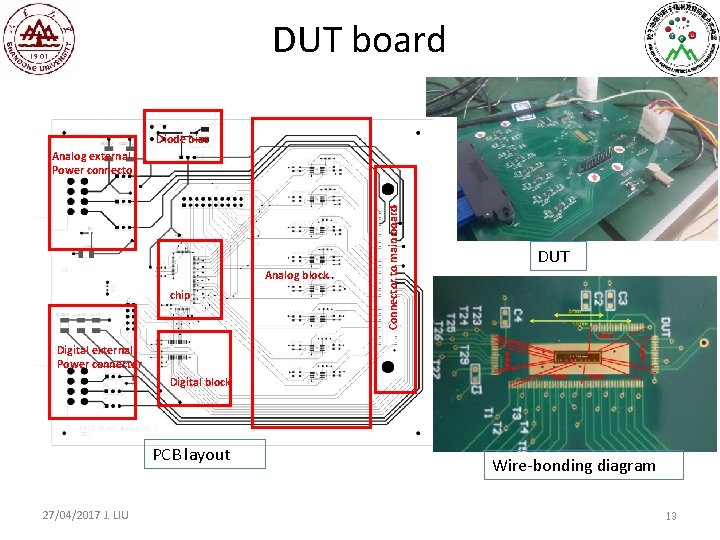

DUT board Diode bias Analog block chip Connector to main board Analog external Power connector DUT Digital external Power connector Digital block PCB layout 27/04/2017 J. LIU Wire-bonding diagram 13

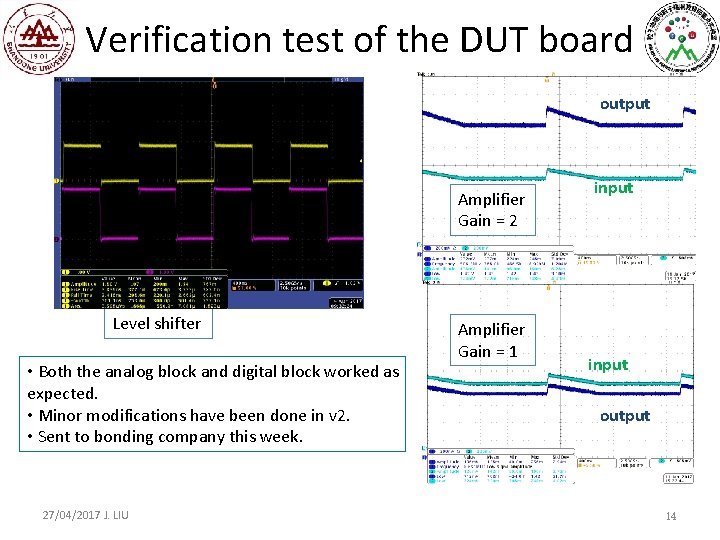

Verification test of the DUT board output Amplifier Gain = 2 Level shifter • Both the analog block and digital block worked as expected. • Minor modifications have been done in v 2. • Sent to bonding company this week. 27/04/2017 J. LIU Amplifier Gain = 1 input output 14

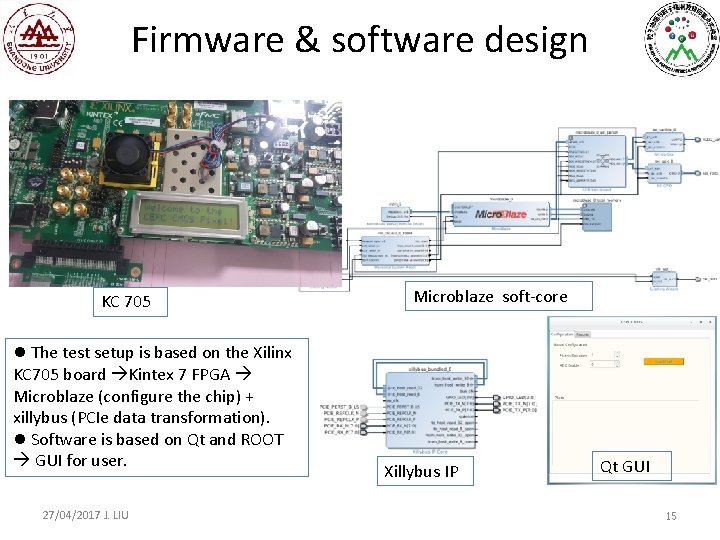

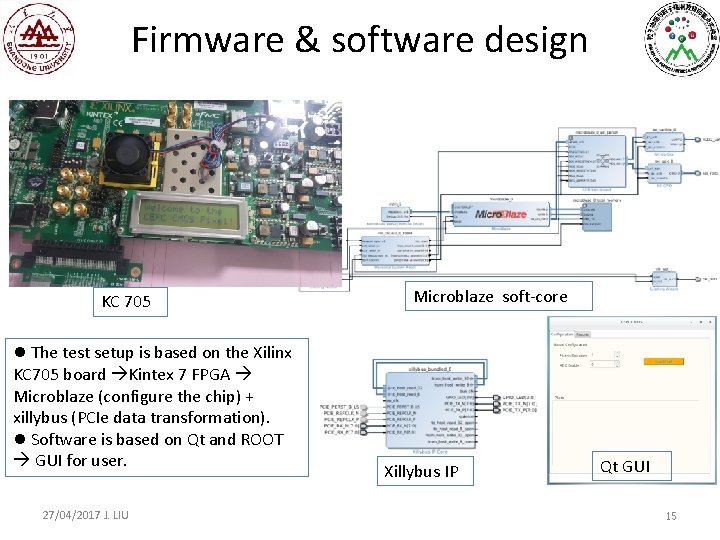

Firmware & software design KC 705 l The test setup is based on the Xilinx KC 705 board Kintex 7 FPGA Microblaze (configure the chip) + xillybus (PCIe data transformation). l Software is based on Qt and ROOT GUI for user. 27/04/2017 J. LIU Microblaze soft-core Xillybus IP Qt GUI 15

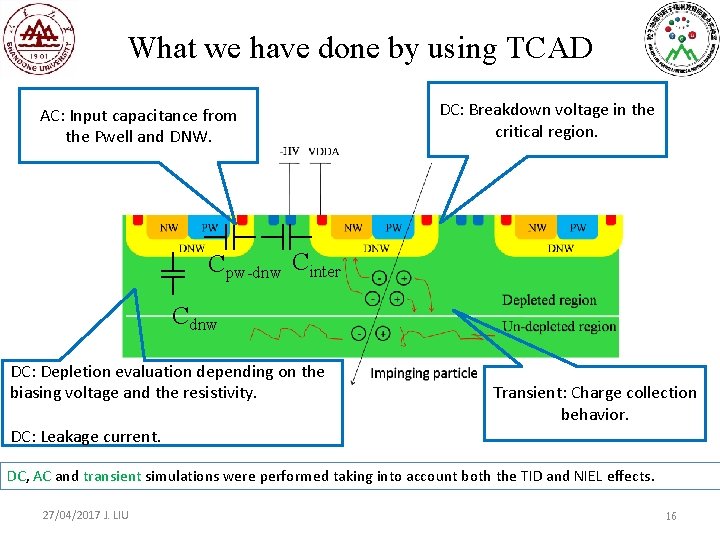

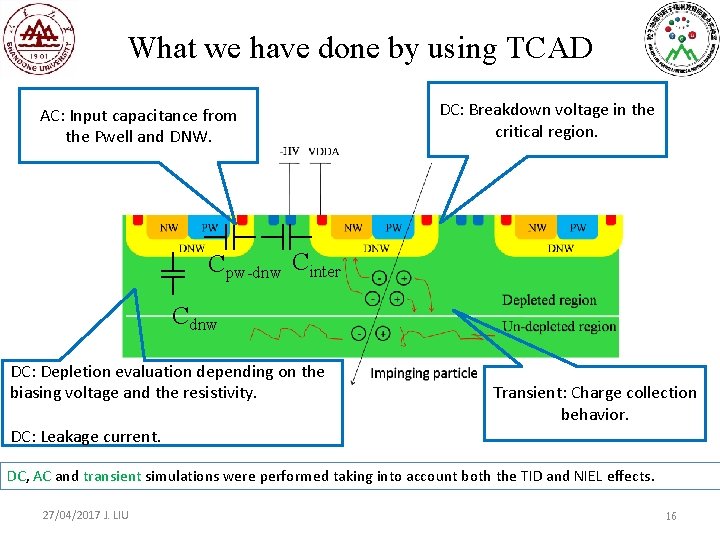

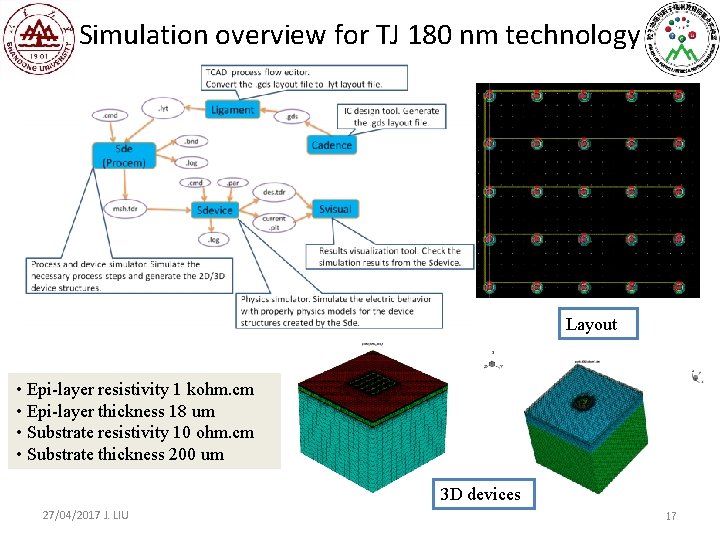

What we have done by using TCAD AC: Input capacitance from the Pwell and DNW. DC: Breakdown voltage in the critical region. Cpw-dnw Cinter Cdnw DC: Depletion evaluation depending on the biasing voltage and the resistivity. DC: Leakage current. Transient: Charge collection behavior. DC, AC and transient simulations were performed taking into account both the TID and NIEL effects. 27/04/2017 J. LIU 16

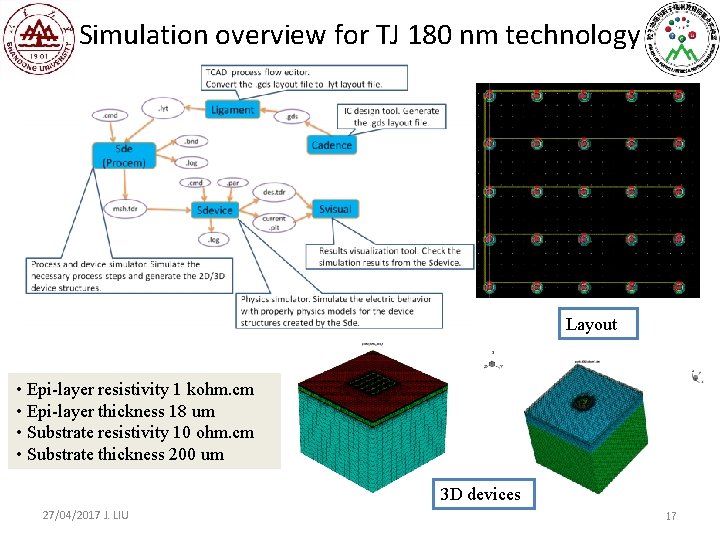

Simulation overview for TJ 180 nm technology Layout • Epi-layer resistivity 1 kohm. cm • Epi-layer thickness 18 um • Substrate resistivity 10 ohm. cm • Substrate thickness 200 um 3 D devices 27/04/2017 J. LIU 17

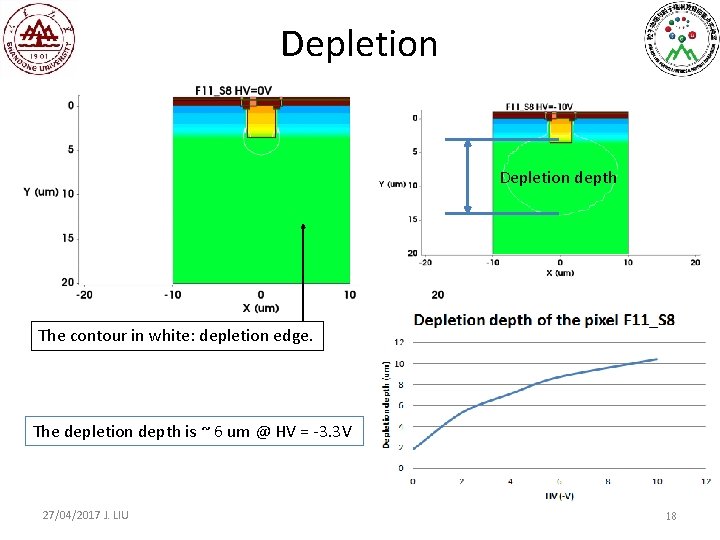

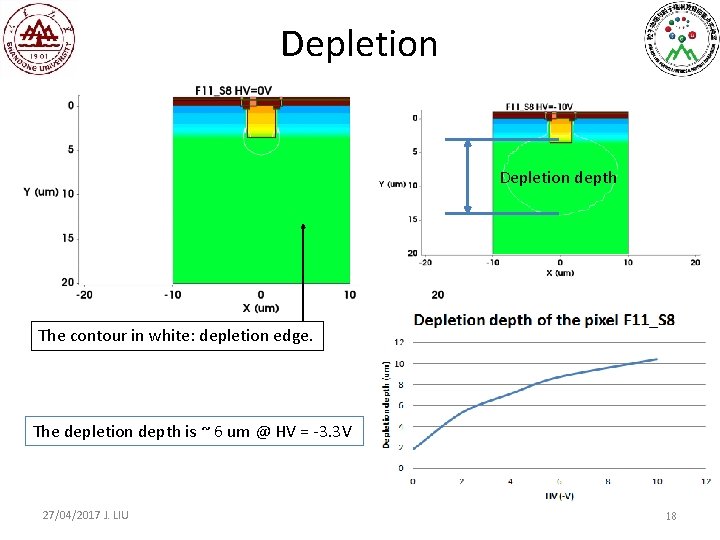

Depletion depth The contour in white: depletion edge. The depletion depth is ~ 6 um @ HV = -3. 3 V 27/04/2017 J. LIU 18

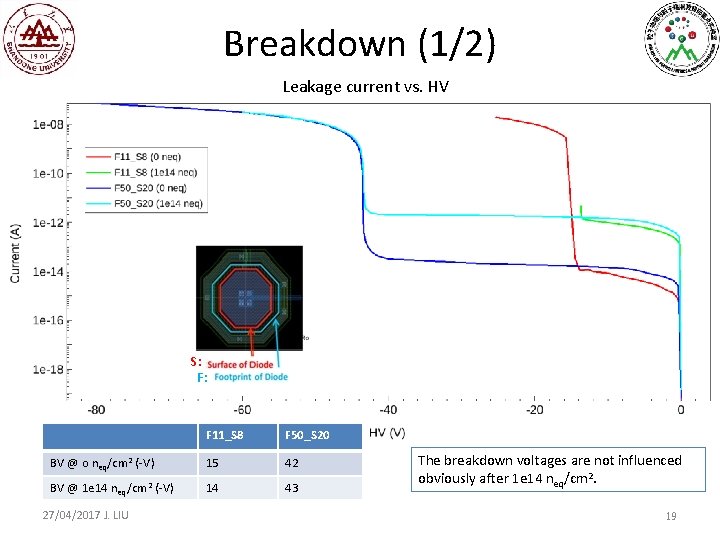

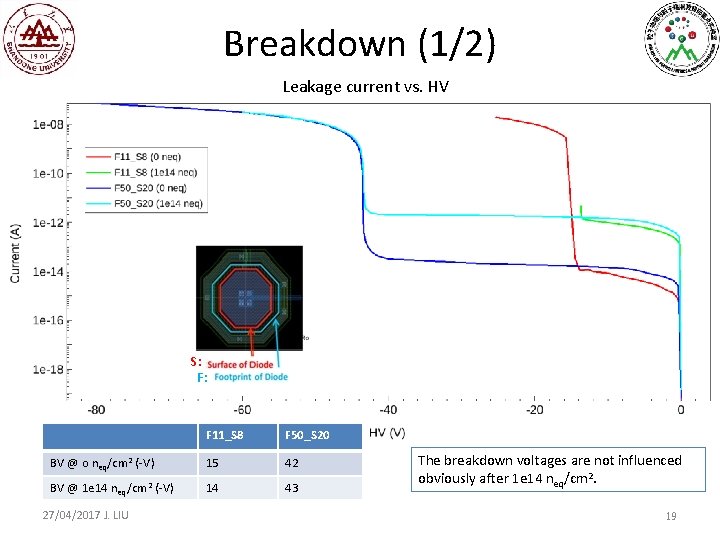

Breakdown (1/2) Leakage current vs. HV S: F: F 11_S 8 F 50_S 20 BV @ o neq/cm 2 (-V) 15 42 BV @ 1 e 14 n eq/cm 2 (-V) 14 43 27/04/2017 J. LIU The breakdown voltages are not influenced obviously after 1 e 14 neq/cm 2. 19

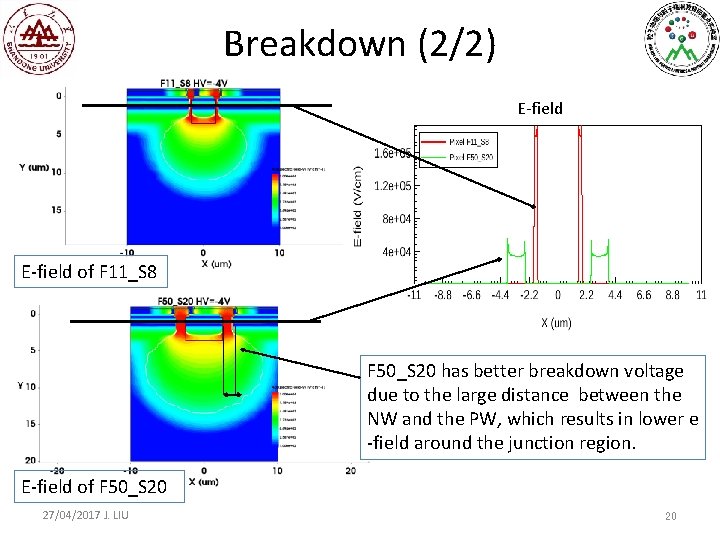

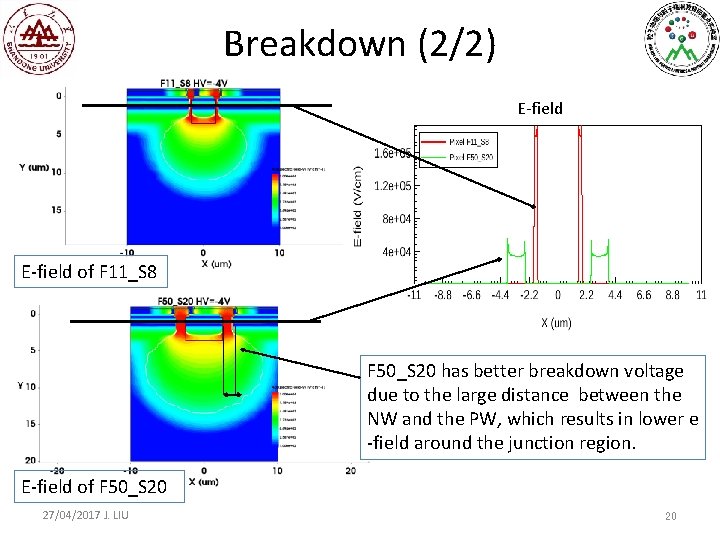

Breakdown (2/2) E-field of F 11_S 8 F 50_S 20 has better breakdown voltage due to the large distance between the NW and the PW, which results in lower e -field around the junction region. E-field of F 50_S 20 27/04/2017 J. LIU 20

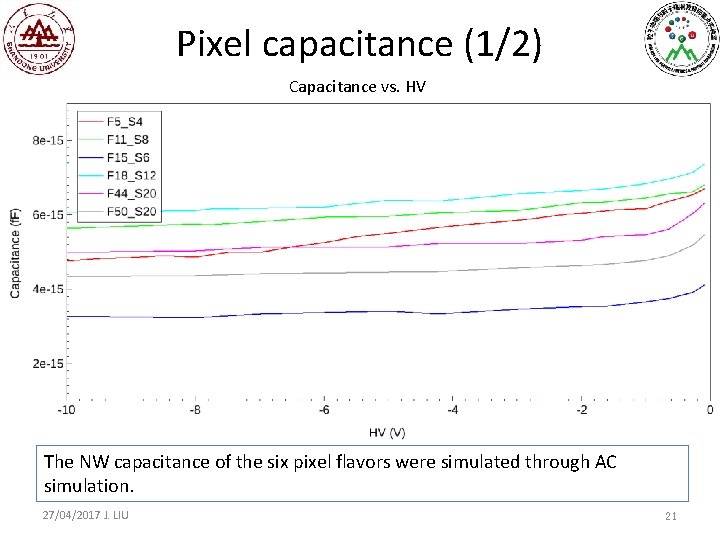

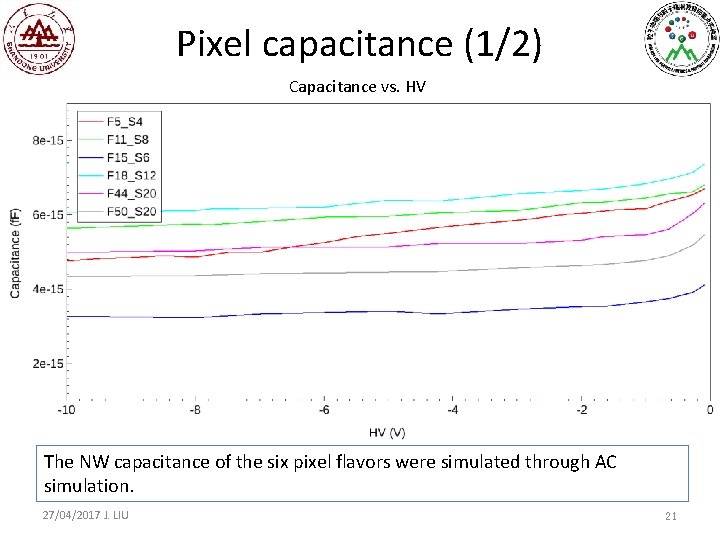

Pixel capacitance (1/2) Capacitance vs. HV The NW capacitance of the six pixel flavors were simulated through AC simulation. 27/04/2017 J. LIU 21

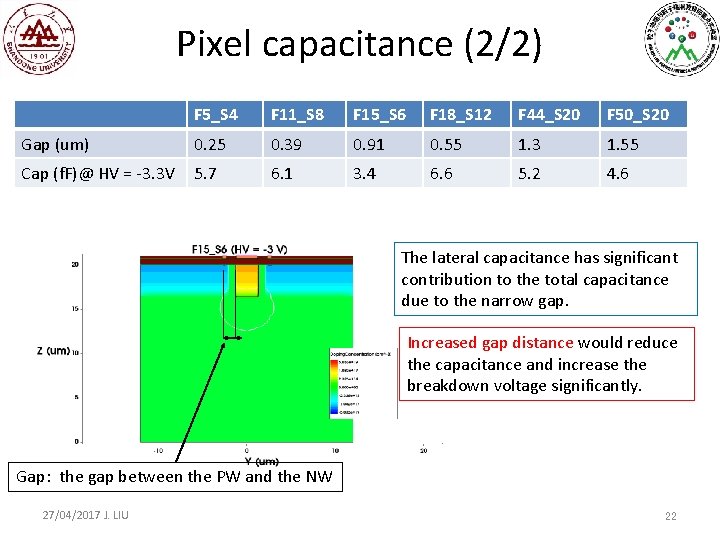

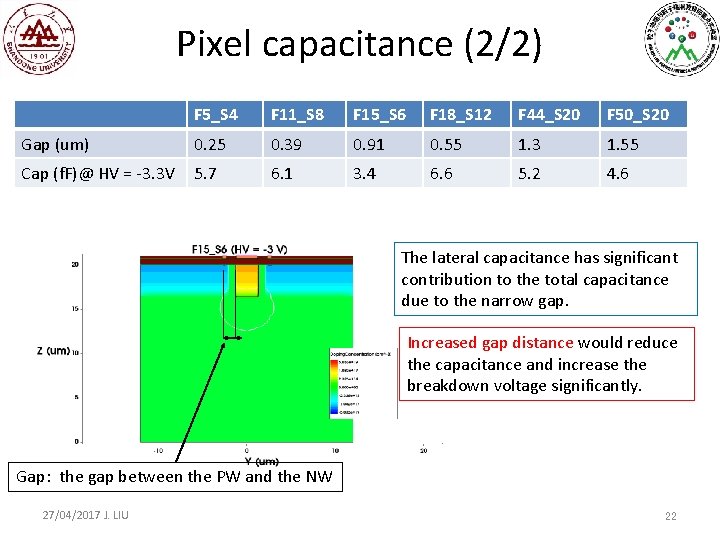

Pixel capacitance (2/2) F 5_S 4 F 11_S 8 F 15_S 6 F 18_S 12 F 44_S 20 F 50_S 20 Gap (um) 0. 25 0. 39 0. 91 0. 55 1. 3 1. 55 Cap (f. F)@ HV = -3. 3 V 5. 7 6. 1 3. 4 6. 6 5. 2 4. 6 The lateral capacitance has significant contribution to the total capacitance due to the narrow gap. Increased gap distance would reduce the capacitance and increase the breakdown voltage significantly. Gap: the gap between the PW and the NW 27/04/2017 J. LIU 22

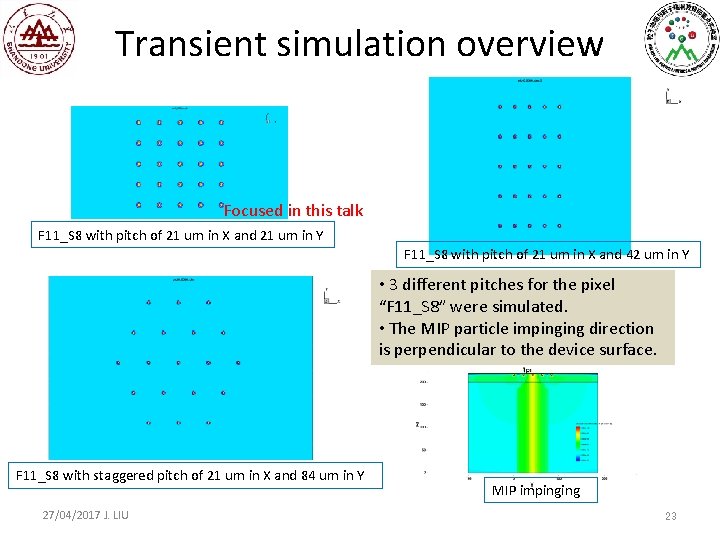

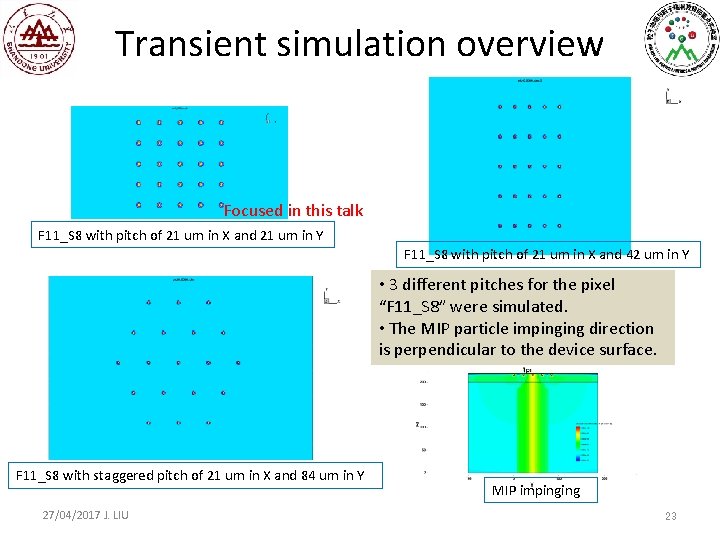

Transient simulation overview Focused in this talk F 11_S 8 with pitch of 21 um in X and 21 um in Y F 11_S 8 with pitch of 21 um in X and 42 um in Y • 3 different pitches for the pixel “F 11_S 8” were simulated. • The MIP particle impinging direction is perpendicular to the device surface. F 11_S 8 with staggered pitch of 21 um in X and 84 um in Y 27/04/2017 J. LIU MIP impinging 23

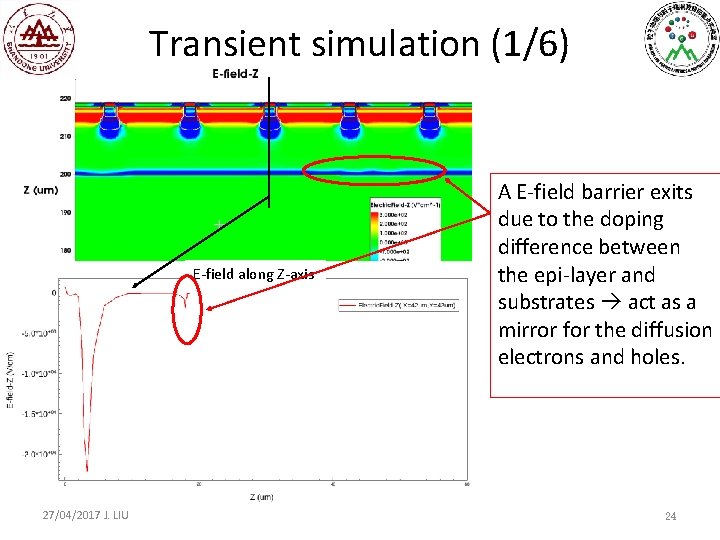

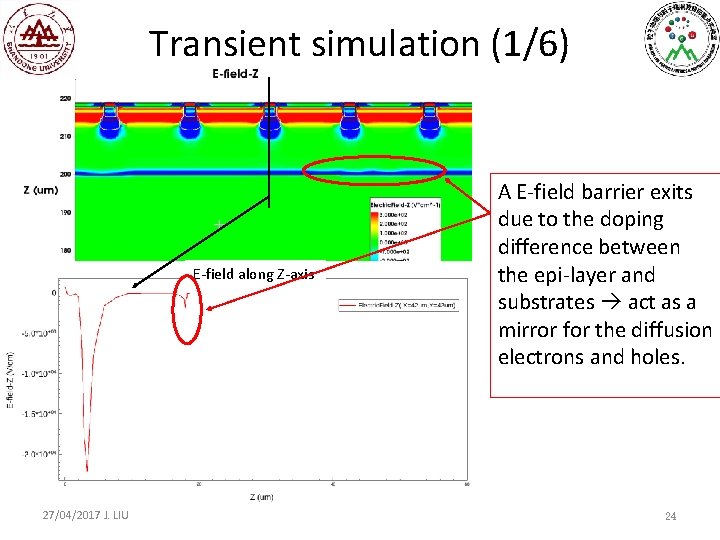

Transient simulation (1/6) E-field along Z-axis 27/04/2017 J. LIU A E-field barrier exits due to the doping difference between the epi-layer and substrates act as a mirror for the diffusion electrons and holes. 24

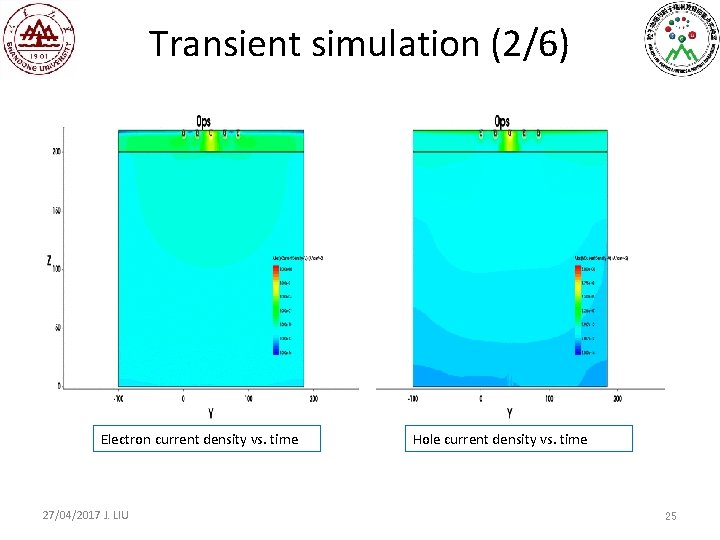

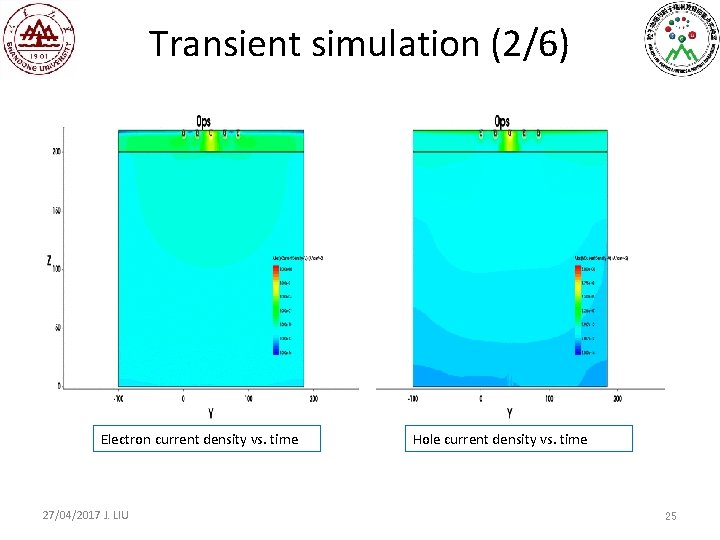

Transient simulation (2/6) Electron current density vs. time 27/04/2017 J. LIU Hole current density vs. time 25

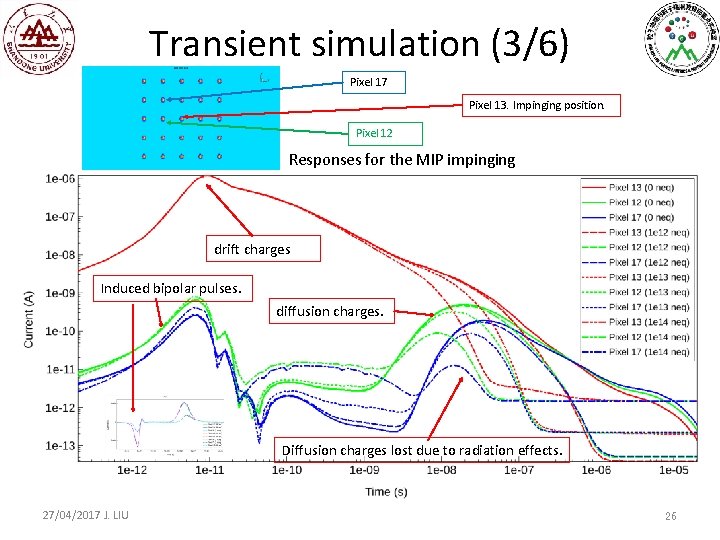

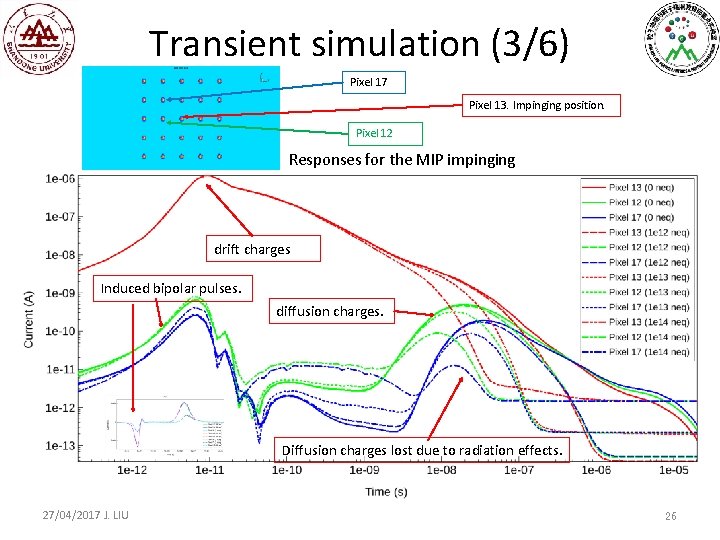

Transient simulation (3/6) Pixel 17 Pixel 13. Impinging position. Pixel 12 Responses for the MIP impinging drift charges Induced bipolar pulses. diffusion charges. Diffusion charges lost due to radiation effects. 27/04/2017 J. LIU 26

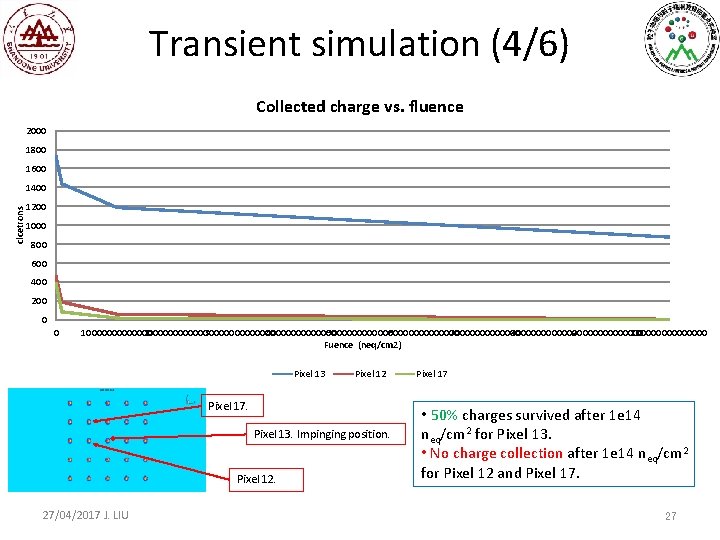

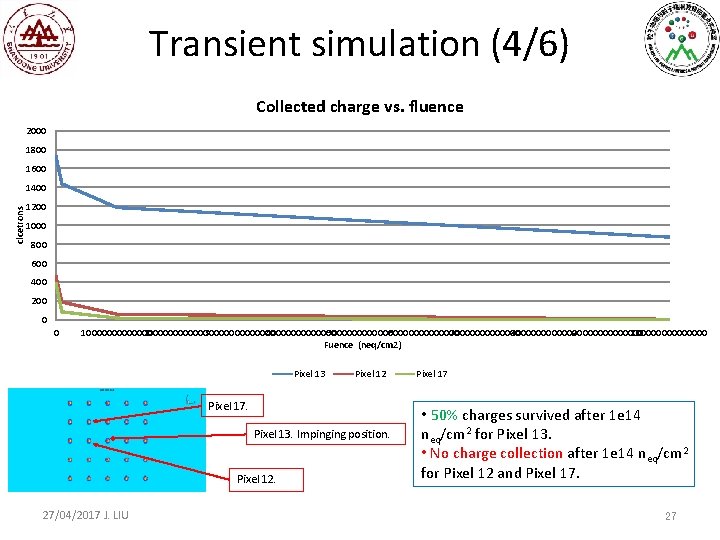

Transient simulation (4/6) Collected charge vs. fluence 2000 1800 1600 clcetrons 1400 1200 1000 800 600 400 200 0 0 10000000 20000000 30000000 40000000 50000000 60000000 70000000 80000000 90000000 10000000 Fuence (neq/cm 2) Pixel 13 Pixel 12 Pixel 17. Pixel 13. Impinging position. Pixel 12. 27/04/2017 J. LIU Pixel 17 • 50% charges survived after 1 e 14 neq/cm 2 for Pixel 13. • No charge collection after 1 e 14 neq/cm 2 for Pixel 12 and Pixel 17. 27

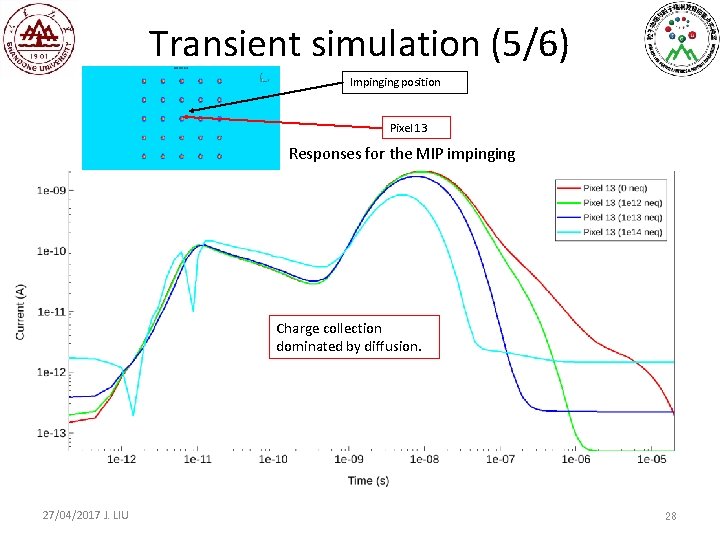

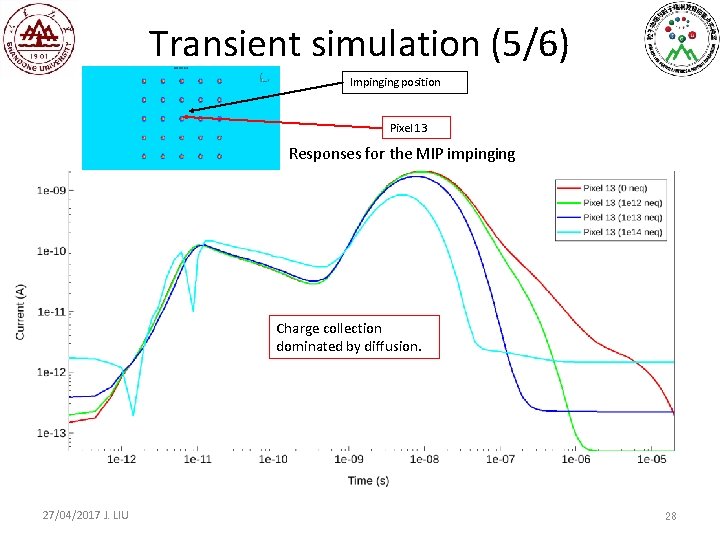

Transient simulation (5/6) Impinging position Pixel 13 Responses for the MIP impinging Charge collection dominated by diffusion. 27/04/2017 J. LIU 28

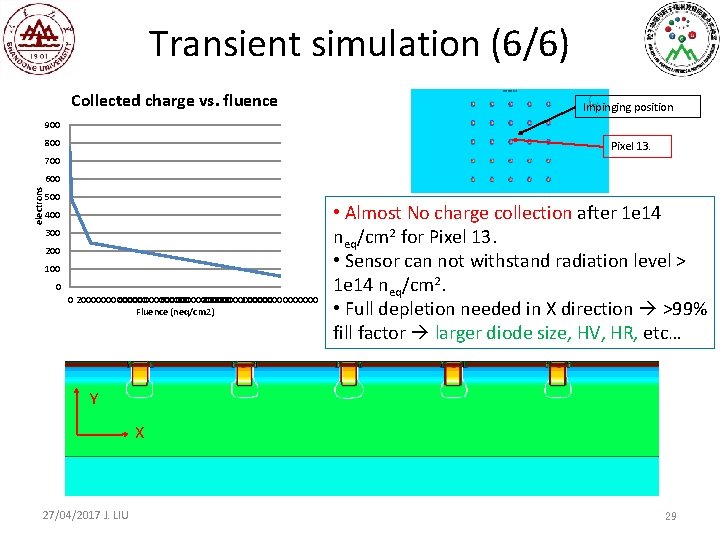

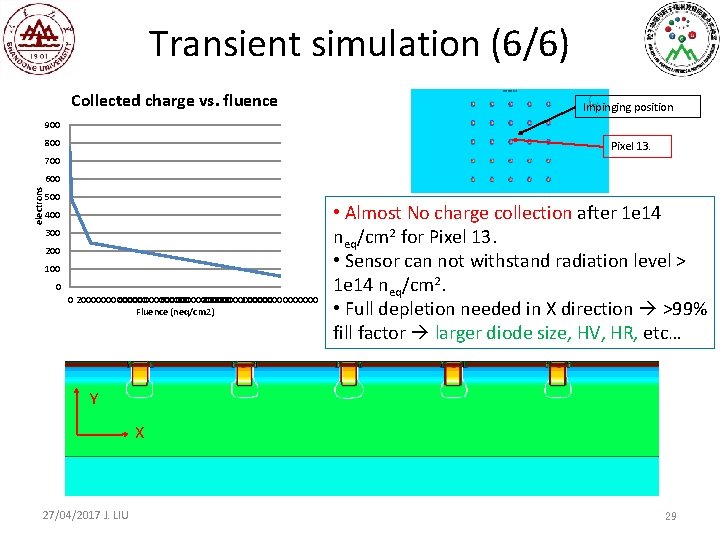

Transient simulation (6/6) Collected charge vs. fluence Impinging position 900 800 Pixel 13. 700 electrons 600 500 400 300 200 100 0 0 20000000 40000000 60000000 80000000 10000000 Fluence (neq/cm 2) • Almost No charge collection after 1 e 14 neq/cm 2 for Pixel 13. • Sensor can not withstand radiation level > 1 e 14 neq/cm 2. • Full depletion needed in X direction >99% fill factor larger diode size, HV, HR, etc… Y X 27/04/2017 J. LIU 29

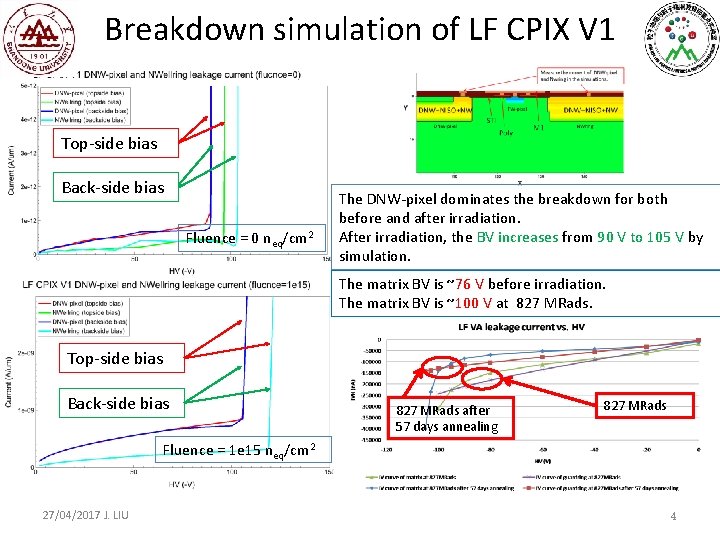

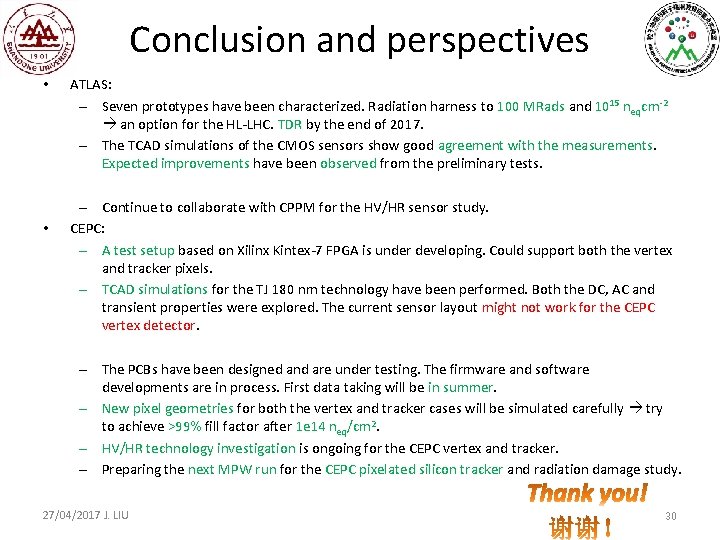

Conclusion and perspectives • • ATLAS: – Seven prototypes have been characterized. Radiation harness to 100 MRads and 1015 neqcm-2 an option for the HL-LHC. TDR by the end of 2017. – The TCAD simulations of the CMOS sensors show good agreement with the measurements. Expected improvements have been observed from the preliminary tests. – Continue to collaborate with CPPM for the HV/HR sensor study. CEPC: – A test setup based on Xilinx Kintex-7 FPGA is under developing. Could support both the vertex and tracker pixels. – TCAD simulations for the TJ 180 nm technology have been performed. Both the DC, AC and transient properties were explored. The current sensor layout might not work for the CEPC vertex detector. – The PCBs have been designed and are under testing. The firmware and software developments are in process. First data taking will be in summer. – New pixel geometries for both the vertex and tracker cases will be simulated carefully try to achieve >99% fill factor after 1 e 14 neq/cm 2. – HV/HR technology investigation is ongoing for the CEPC vertex and tracker. – Preparing the next MPW run for the CEPC pixelated silicon tracker and radiation damage study. 27/04/2017 J. LIU 30